# System Solutions Towards High-Precision Visual Computing at Low Power

by

Venkatesh Kodukula

# A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved June 2023 by the Graduate Supervisory Committee:

Robert LiKamWa, Chair Chaitali Chakrabarti John Brunhaver Akshay Nambi

ARIZONA STATE UNIVERSITY

August 2023

#### ABSTRACT

Efficient visual sensing plays a pivotal role in enabling high-precision applications in augmented reality and low-power Internet of Things (IoT) devices. This dissertation addresses the primary challenges that hinder energy efficiency in visual sensing: the bottleneck of pixel traffic across camera and memory interfaces and the energy-intensive analog readout process in image sensors.

To overcome the bottleneck of pixel traffic, this dissertation proposes a visual sensing pipeline architecture that enables application developers to dynamically adapt the spatial resolution and update rates for specific regions within the scene. By selectively capturing and processing high-resolution frames only where necessary, the system significantly reduces energy consumption associated with memory traffic. This is achieved by encoding only the relevant pixels from the commercial image sensors with standard raster-scan pixel read-out patterns, thus minimizing the data stored in memory. The stored rhythmic pixel region stream is decoded into traditional frame-based representations, enabling seamless integration into existing video pipelines. Moreover, the system includes runtime support that allows flexible specification of the region labels, giving developers fine-grained control over the resolution adaptation process. Experimental evaluations conducted on a Xilinx Field Programmable Gate Array (FPGA) platform demonstrate substantial reductions of 43-64% in interface traffic, while maintaining controllable task accuracy.

In addition to the pixel traffic bottleneck, the dissertation tackles the energy intensive analog readout process in image sensors. To address this, the dissertation proposes aggressive scaling of the analog voltage supplied to the camera. Extensive characterization on off-the-shelf sensors demonstrates that analog voltage scaling can significantly reduce sensor power, albeit at the expense of image quality. To mitigate this trade-off, this research develops a pipeline that allows application developers to adapt the sensor voltage on a frame-by-frame basis. A voltage controller is integrated into the existing Raspberry Pi (RPi) based video streaming pipeline, generating the sensor voltage. On top of that, the system provides a software interface for vision applications to specify the desired voltage levels. Evaluation of the system across a range of voltage scaling policies on popular vision tasks demonstrates that the technique can deliver up to 73% sensor power savings while maintaining reasonable task fidelity.

#### ACKNOWLEDGMENTS

I would like to express my heartfelt gratitude to Dr. Robert LiKamWa for his exceptional mentorship and unwavering guidance throughout my challenging yet rewarding graduate school journey. His rigorous training and insightful feedback have significantly contributed to my academic growth and professional development.

I am immensely grateful to my teammates, particularly Mason Manetta, for his invaluable collaboration and contributions to the Squint project. Additionally, I would like to extend my appreciation to Alexander Shearer, Van Nguyen, and Srinivas Lingtula for their involvement in the Rhythmic Pixel Regions project. Together, we have achieved significant milestones and advancements in our research.

I would also like to acknowledge the positive and enjoyable work environment fostered by my lab mates at Meteor Studio. Their camaraderie and engaging conversations have made my time there truly memorable.

I am thankful to the members of my Ph.D. committee, Dr. Chaitali Chakrabarti, Dr. John Brunhaver, and Dr. Akshay Nambi, for their valuable insights and feedback.

My heartfelt appreciation goes out to my friends and roommates for making my social life outside the lab vibrant and fulfilling.

I would like to extend my deepest gratitude to my parents, Latha Kodukula and Nageswararao Kodukula, for their unwavering support and for encouraging me to pursue my dreams since childhood. I am deeply grateful to my sister, Vandana Kodukula, for believing in me and for supporting my decision to pursue Ph.D.

Finally, I would like to acknowledge the School of Electrical, Energy, and Computer Engineering, the School of Arts and Media Engineering at Arizona State University, and the National Science Foundation for their academic and financial support, which has been instrumental in enabling me to pursue and complete my graduate studies.

| $Pa_{\xi}$                                                | ge  |

|-----------------------------------------------------------|-----|

| LIST OF TABLES v                                          | rii |

| LIST OF FIGURES vi                                        | ii  |

| CHAPTER                                                   |     |

| 1 INTRODUCTION                                            | 1   |

| 2 RHYTHMIC PIXEL REGIONS: MULTI-RESOLUTION VISUAL         |     |

| SENSING SYSTEM TOWARDS HIGH-PRECISION VISUAL COM-         |     |

| PUTING AT LOW POWER                                       | 5   |

| 2.1 Introduction                                          | 6   |

| 2.2 Background and Related Work 1                         | 1   |

| 2.3 Visual Computing with Rhythmic Pixel Regions 1        | 6   |

| 2.3.1 Developer-Specified Region Labels                   | 7   |

| 2.3.2 Encoded Frame 1                                     | 7   |

| 2.3.3 Metadata: Per-Row Offset, Encoding Mask (EncMask) 1 | 8   |

| 2.3.4 A Case Study Around ORB-SLAM 1                      | 9   |

| 2.4 Design                                                | 21  |

| 2.4.1 Rhythmic Pixel Encoder Architecture                 | 22  |

| 2.4.2 Rhythmic Pixel Decoder Architecture                 | 25  |

| 2.4.3 Developer Support for Rhythmic Pixel Regions 2      | 28  |

| 2.5 Implementation 3                                      | 82  |

| 2.5.1 FPGA-Based Encoder and Decoder Integration          | 82  |

| 2.5.2 Runtime 3                                           | 33  |

| 2.5.3 Workloads 3                                         | 34  |

| 2.6 Evaluation 3                                          | 39  |

|   |       | 2.6.1  | The Use of Rhythmic Pixel Regions Is Flexible                  | 39 |

|---|-------|--------|----------------------------------------------------------------|----|

|   |       | 2.6.2  | The Use of Rhythmic Pixel Regions Is Memory Friendly           | 40 |

|   |       | 2.6.3  | The Hardware Extensions Are Lightweight and Scalable           | 42 |

|   | 2.7   | Futur  | e Directions                                                   | 44 |

| 3 | SQUI  | INT: A | A FRAMEWORK FOR DYNAMIC VOLTAGE SCALING                        |    |

|   | OF II | MAGE   | SENSORS TOWARDS LOW POWER IOT VISION                           | 47 |

|   | 3.1   | Intro  | luction                                                        | 48 |

|   | 3.2   | Backg  | ground and Motivation                                          | 52 |

|   |       | 3.2.1  | Analog Readout Is The Bottleneck for Sensor Energy-            |    |

|   |       |        | Efficiency                                                     | 52 |

|   |       | 3.2.2  | Effects of Analog Voltage Variations on Image Sensor Circuitry | 53 |

|   |       | 3.2.3  | Analog Voltage Scaling for Energy-Efficiency                   | 54 |

|   |       | 3.2.4  | Motivational Observations                                      | 61 |

|   | 3.3   | Desig  | n                                                              | 62 |

|   |       | 3.3.1  | Programmable Voltage Controller                                | 64 |

|   |       | 3.3.2  | Developer Support                                              | 65 |

|   | 3.4   | Imple  | mentation                                                      | 69 |

|   |       | 3.4.1  | RPi-based System Integration                                   | 69 |

|   |       | 3.4.2  | Workloads                                                      | 70 |

|   | 3.5   | Evalu  | ation                                                          | 76 |

|   |       | 3.5.1  | The Usage of Squint Is Flexible, Seamless, and Performant      | 76 |

|   |       | 3.5.2  | The Usage of Squint Is Energy-Efficient                        | 79 |

|   |       | 3.5.3  | The Hardware and Software extensions Are Lightweight           | 81 |

|   | 3.6   | Relat  | ed Work                                                        | 82 |

| CHAPTER                         | Page |

|---------------------------------|------|

| 3.7 Future Directions           | . 85 |

| 4 CONCLUSION                    | . 87 |

| BIBLIOGRAPHY                    | . 88 |

| APPENDIX                        |      |

| A FRAME STACKS AND ENERGY MODEL | . 96 |

# LIST OF TABLES

| Ta | able                                                                        | Page |

|----|-----------------------------------------------------------------------------|------|

| 1. | Opportunities for Rhythmic Pixel Regions                                    | 9    |

| 2. | System Components in the Video Pipeline                                     | 32   |

| 3. | Vision Tasks and Benchmarks                                                 | 34   |

| 4. | Observed Statistics of Task and Benchmark                                   | 38   |

| 5. | Resource Utilization for Different Encoder Designs                          | 43   |

| 6. | Characterized Image Sensors. Sensors Can Be Undervolted Way Beyond the      |      |

|    | Voltage Specification Mentioned in Their Datasheets                         | 54   |

| 7. | System Components in the IoT Streaming Pipeline                             | 69   |

| 8. | Energy-Per-Pixel of Various Components in the Vision Pipeline. As Is Widely |      |

|    | Acknowledged, Communication Cost Is At Least Three Orders of Magnitude      |      |

|    | More Than Compute Cost                                                      | 98   |

# LIST OF FIGURES

| Fig | gure                                                                      | Page |

|-----|---------------------------------------------------------------------------|------|

| 1.  | Traditional Frame-Based Computing Captures and Processes Entire Frames.   |      |

|     | ROI-Based Computing Samples Regions of Interest, but at Uniform Spatial   |      |

|     | and Temporal Resolution. With Rhythmic Pixel Regions, Different Regions   |      |

|     | Are Captured at Different Spatio-Temporal Resolutions.                    | . 6  |

| 2.  | The Process of Encoding and Decoding. The Encoder Packs Pixels Within     |      |

|     | the Regions from the Original Image, Maintaining Raster-Scan Order. The   |      |

|     | Decoder Reconstructs Data from the Encoded Frame, Per-Row Offsets, and    |      |

|     | Encoding Mask                                                             | . 16 |

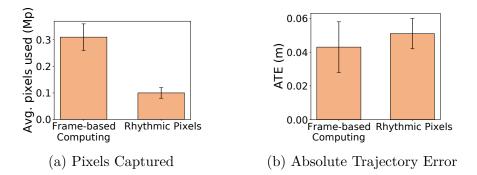

| 3.  | For ORB-SLAM, Rhythmic Pixel Regions Can Discard Irrelevant Pixels        |      |

|     | Early in the Pipeline for Memory Efficiency, While Preserving Relevant    |      |

|     | Regions at Sufficient Resolutions for Accuracy                            | . 18 |

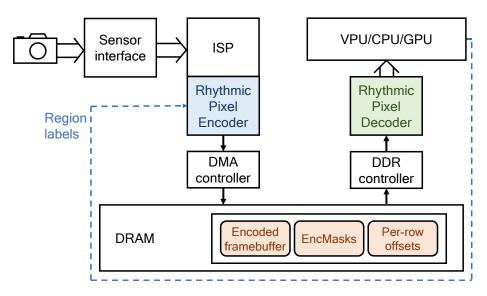

| 4.  | System Design. The Rhythmic Encoder Decimates the Incoming Pixel          |      |

|     | Stream from Camera and Encodes Only Region-Specified Pixels into Mem-     |      |

|     | ory. The Rhythmic Decoder Decodes the Pixels for Use with the Vision      |      |

|     | Algorithms.                                                               | . 22 |

| 5.  | Encoder Intercepts the Incoming Pixel Stream and Only Forwards Pixels     |      |

|     | That Match the Stride and Skip Specifications of Any Region               | . 24 |

| 6.  | Decoder Fulfills Pixel Requests from the Vision App in Two Steps. (a) The |      |

|     | Pixel MMU Performs Address Translation to Fetch the Right Set of Pixel    |      |

|     | Regions from Encoded Frame. (B) The FIFO Sampling Unit Reconstructs       |      |

|     | the Original Pixel Regions from Encoded Pixel Regions and Metadata        | . 26 |

| 7.  | With Rhythmic Pixel Regions, Policies Can Define How Different Regions   |    |

|-----|--------------------------------------------------------------------------|----|

|     | in the Image Can Be Captured at Non-Uniform Spatial and Temporal         |    |

|     | Resolutions. In This Illustrated Policy, Regions Shaded in Black Are     |    |

|     | Not Sampled. To Track Objects Entering/Leaving the Scene, the System     |    |

|     | Performs a Full-Frame Capture on a 'Cycle Length' Periodicity            | 30 |

| 8.  | Rhythmic Pixel Regions Reduces Pixel Memory Traffic by Generating        |    |

|     | Sparser Pixel Streams and Reduces the Memory Footprint by Generating     |    |

|     | Smaller Frame Buffers. The Reduction Is More with Higher Cycle Lengths.  | 36 |

| 9.  | There Is a Trade-Off Between Cycle Length and Task Accuracy. In V-SLAM,  |    |

|     | We Observe High Standard Deviation. This Indicates Future Opportunity    |    |

|     | to Adaptively Reduce Cycle Length to Improve Accuracy for Scenes with    |    |

|     | High Motion.                                                             | 36 |

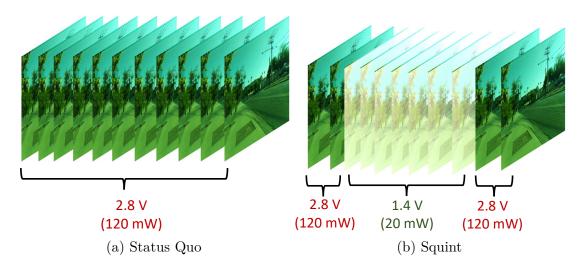

| 10. | Existing Systems Supply a Fixed Voltage to the Image Sensor Regardless   |    |

|     | of the Frame. Squint Adapts the Camera Supply Voltage per Frame for      |    |

|     | Energy-Efficiency.                                                       | 48 |

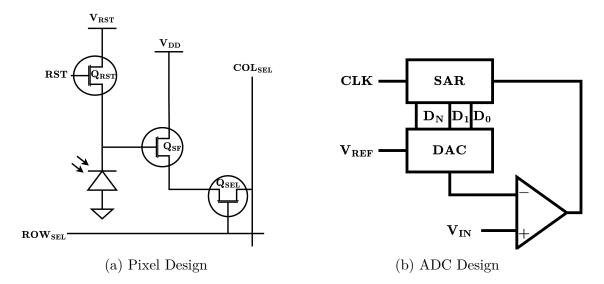

| 11. | Analog Voltage Variation Affects Pixel and ADC Circuits. A Lower Voltage |    |

|     | (VDD) for Pixels Would Affect Transistor Settling Times, Resulting in    |    |

|     | Noise. A Lower Reference Voltage (VREF) for ADC Would Decrease the       |    |

|     | Dynamic Range, Resulting in Reduced Contrast.                            | 52 |

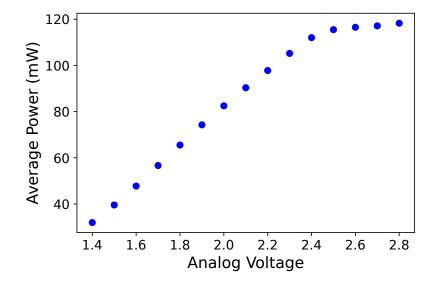

| 12. | Sensor Power Significantly Reduces by Lowering Its Supply Voltage. The   |    |

|     | Flat Portion Above 2.4 V Is Due to Strong Voltage Regulation Inside the  |    |

|     | Sensor                                                                   | 56 |

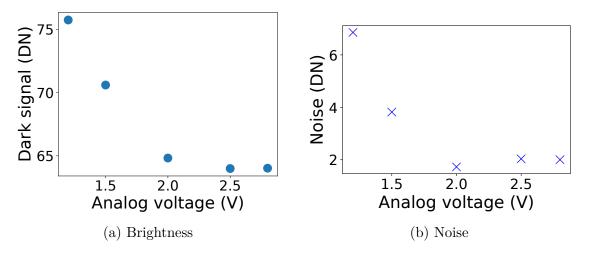

| 13. | Sensor's Brightness and Noise Levels Increase with Lower Analog Voltage.    |    |

|-----|-----------------------------------------------------------------------------|----|

|     | Increased Brightness Is Due to Decreased ADC Output Swing and Increased     |    |

|     | Noise Due to Elevated Shot Noise Levels.                                    | 57 |

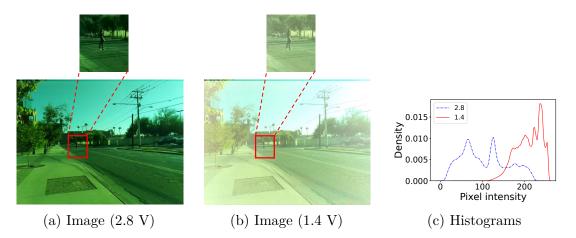

| 14. | Images Captured at Different Sensor Voltages and Their Histograms. Low      |    |

|     | Voltage Image Is Brighter and Grainier Than Its High Voltage Counterpart.   |    |

|     | This Is Also Reflected in the Shift in Mean and Variance Width in the       |    |

|     | Histogram. Images Appear More Greenish Because They Are Captured            |    |

|     | RAW Turning Off White Balance                                               | 57 |

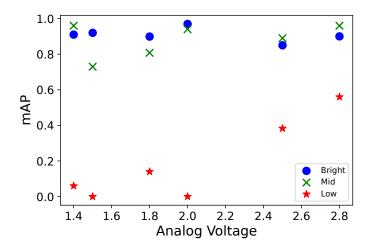

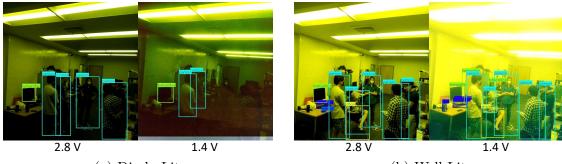

| 15. | Brighter and Noisier Images Do Not Significantly Affect Task Fidelity of    |    |

|     | Vision Applications in Well-Lit Scenes.                                     | 58 |

| 16. | High Fidelity Is Still Needed for Precise Object Detection in Challenging   |    |

|     | Scenarios. Low Fidelity Would Suffice Otherwise                             | 59 |

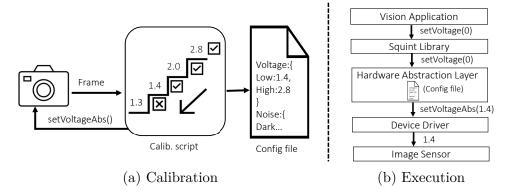

| 17. | Phases of Squint. During Calibration, Squint Sweeps Voltage Supplied to     |    |

|     | the Camera to Determine the Undervolting Limit as Well as to Profile Noise, |    |

|     | and This Information Is Stored in a Configuration File. During Execution,   |    |

|     | the System Uses the Configuration File to Translate Developer's High-Level  |    |

|     | Fidelity Input to Actual Low-Level Camera Voltage Using Standard Camera     |    |

|     | System Stack                                                                | 59 |

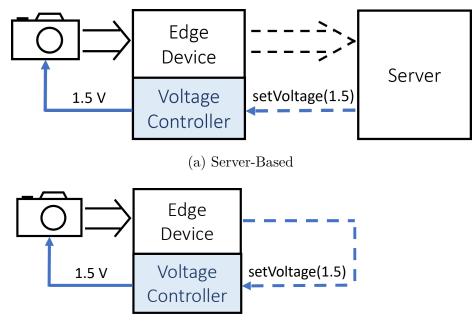

| 18. | Different System Incarnations for Squint. In Server-Based, Vision Apps      |    |

|     | Running on Server Issue Voltage Request to the Voltage Controller, Whereas  |    |

|     |                                                                             |    |

|     | in Edge-Based, Vision Apps Run on the Edge Device Itself and Directly       |    |

Page

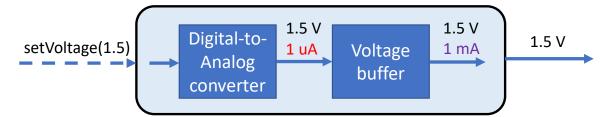

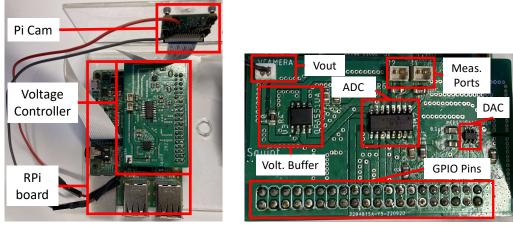

| 19. | Voltage Controller Comprises a DAC to Translate Digital Voltage Requests    |    |  |

|-----|-----------------------------------------------------------------------------|----|--|

|     | into Corresponding Analog Voltage, and a Voltage Buffer to Generate         |    |  |

|     | Sufficient Current Flow for Reliable Camera Operation                       | 65 |  |

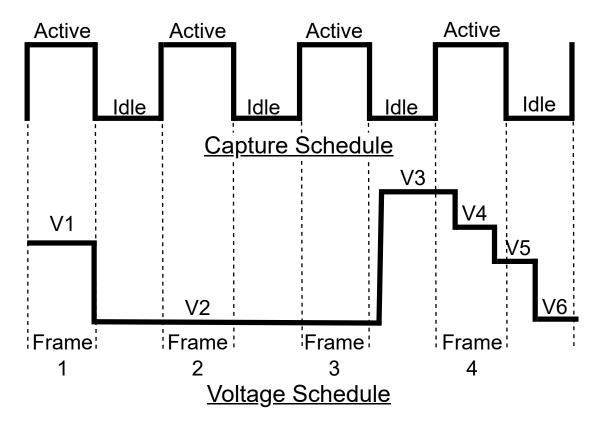

| 20. | Timing Different Voltages in Tandem with Camera Capture Schedule Leads      |    |  |

|     | to Different Fidelity Patterns Across the Frames and Within a Frame         | 66 |  |

| 21. | Our System Setup                                                            | 69 |  |

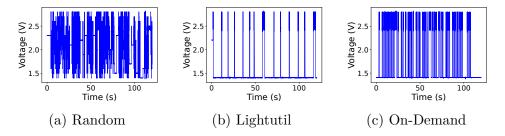

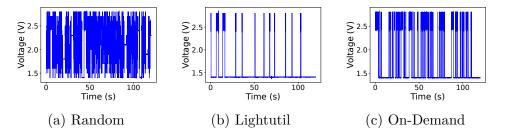

| 22. | Bright Light Voltage Schedules Generated by Different Policies for Entrance |    |  |

|     | Detection Dataset.                                                          | 73 |  |

| 23. | Bright Light Voltage Schedules Generated by Different Policies for Person   |    |  |

|     | Tracking Dataset.                                                           | 73 |  |

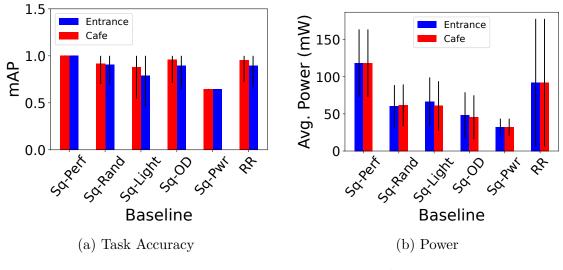

| 24. | People Detection Task                                                       | 76 |  |

| 25. | Camera Pose Detection Task                                                  | 78 |  |

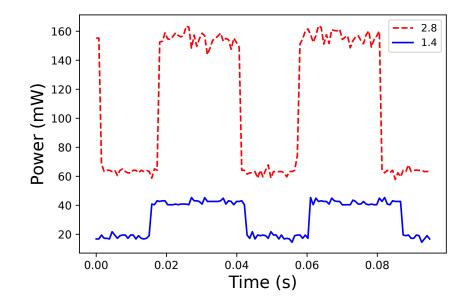

| 26. | Power Trace for Different Sensor Voltage Modes                              | 80 |  |

| 27. | Task: Visual SLAM; Benchmark: TUM Freiburg1-Xyz                             | 97 |  |

| 28. | Task: Visual SLAM; Benchmark: TUM Freiburg1-Floor                           | 97 |  |

| 29. | Task: Visual SLAM; Benchmark: TUM Freiburg2-360-Kidnap-Secret               | 97 |  |

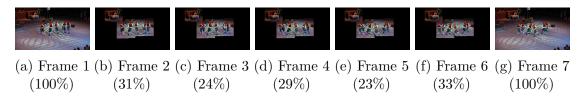

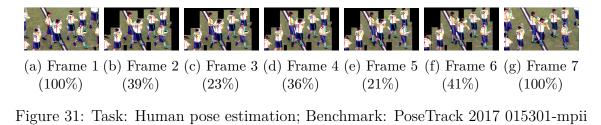

| 30. | Task: Human Pose Estimation; Benchmark: PoseTrack 2017 024575-Mpii .        | 97 |  |

| 31. | Task: Human Pose Estimation; Benchmark: PoseTrack 2017 015301-Mpii .        | 98 |  |

| 32. | Task: Face Detection; Benchmark: Chokepoint Dataset P2E-S5                  | 98 |  |

#### Chapter 1

# INTRODUCTION

The rapid advancement of visual computing systems has revolutionized the way we interact with the world through cameras, enabling a wide range of applications in the mobile devices, e.g., Oculus Quest, and Internet of Things (IoT). These systems have the remarkable ability to detect faces, understand spatial scene geometry, capture high-resolution images and videos, and provide security through video surveillance. With the continuous improvement of image sensor technology, such as higher resolutions and faster frame rates, the precision and capabilities of visual systems have significantly improved, opening up new possibilities for augmented reality, navigation, and other visually intensive applications.

While higher resolutions and faster frame rates enable high precision visual computing, they also pose challenges to visual systems on mobile and IoT devices in terms of energy-efficiency. Specifically, higher resolution captures result in high pixel traffic across memory interfaces, which hampers energy-efficiency. Additionally, higher resolution captures require more sensor power due to the costly analog readout process. To mitigate power consumption, existing systems often reduce the spatial resolution and frame rate of image capture, leading to energy savings but sacrificing visual precision and task accuracy. This tradeoff between power consumption and task fidelity highlights the need for innovative approaches that can enhance the capabilities of continuous mobile vision systems while optimizing energy efficiency.

This dissertation addresses the energy-efficiency challenge by proposing two novel approaches: Rhythmic Pixel Regions and Squint Imaging. These approaches aim to trasnform visual computing systems by offering improved precision, energy efficiency, and task adaptability, while taking into account the unique characteristics of different visual features and the power limitations of mobile and IoT devices.

The first approach, Rhythmic Pixel Regions, challenges the traditional paradigm of capturing and processing entire image frame streams at uniform spatial resolutions and frame rates. Instead, it introduces the concept of region-specific spatiotemporal resolutions, allowing for fine-grained configurability based on the properties of visual features. By leveraging encoded data representations, this approach enables the simultaneous capture of hundreds of rhythmic pixel regions, each with its own independently defined resolution. This selective configurability empowers developers to allocate higher spatiotemporal resolution to regions requiring precise visual features, such as augmented reality overlays or facial recognition, while allocating lower resolution to other parts of the frame. By dynamically adjusting the resolution based on task requirements, the rhythmic pixel region architecture eliminates the wasteful processing and memory traffic associated with unproductive pixels, leading to significant energy savings without compromising overall task accuracy.

The second approach, Squint, focuses on the dynamic voltage scaling (DVS) of image sensors to achieve energy savings. Image sensors are known to consume a significant amount of power in visual computing systems, and DVS allows for the adaptive variation of the analog voltage supplied to the sensor on a frame-by-frame basis. The Squint framework addresses the challenge of maintaining imaging fidelity in the face of voltage scaling by thoroughly characterizing the energy and fidelity implications on commercial off-the-shelf image sensors. This characterization reveals that, in most situations, the degradation in imaging fidelity caused by aggressive voltage scaling does not significantly impact the accuracy of modern neural network-based vision workloads. However, precise scene feature detection, especially in challenging conditions such as low-light or crowded scenes, still benefits from higher fidelity. To enable dynamic voltage scaling, the Squint framework introduces a lightweight and fully programmable voltage controller hardware interface, complemented by a runtime system that seamlessly integrates with vision applications. This integration empowers application developers to specify voltage schedules directly, allowing for precise control over power consumption while balancing imaging fidelity requirements.

By combining the Rhythmic Pixel Regions based architecture and the Squint framework, this dissertation presents a comprehensive solution to enhance the capabilities and energy efficiency of visual computing systems. The Rhythmic Pixel Regions architecture enable developers to finely tune spatiotemporal resolutions based on the specific requirements of different visual features, offering an unprecedented level of task adaptability while optimizing power consumption. Meanwhile, the Squint framework provides a dynamic voltage scaling mechanism for image sensors, enabling significant power savings without compromising overall imaging fidelity.

Through extensive evaluations, the proposed approaches have demonstrated remarkable improvements in energy efficiency, extending the battery life of mobile and IoT devices. By striking a delicate balance between task accuracy, power consumption, and imaging fidelity, these approaches pave the way for advanced mobile and IoT vision applications with prolonged operation times.

In summary, this dissertation introduces two groundbreaking approaches to address the challenges of energy efficiency and imaging fidelity in visual computing systems.

• Rhythmic Pixel Regions offers a new paradigm for selective spatiotemporal resolution configurations for AR/VR use-cases

- Squint enables dynamic voltage scaling in image sensors to leverage image quality

- power trade-offs for IoT and XR use-cases

The rest of the dissertation is organized as follows. §2 presents Rhythmic Pixel Regions, §3 presents Squint framework, and §4 concludes this work.

#### Chapter 2

# RHYTHMIC PIXEL REGIONS: MULTI-RESOLUTION VISUAL SENSING SYSTEM TOWARDS HIGH-PRECISION VISUAL COMPUTING AT LOW POWER

High spatiotemporal resolution can offer high precision for vision applications, which is particularly useful to capture the nuances of visual features, such as for augmented reality. Unfortunately, capturing and processing high spatiotemporal visual frames generates energy-expensive memory traffic. On the other hand, low resolution frames can reduce pixel memory throughput, but reduce also the opportunities of high-precision visual sensing. However, our intuition is that not all parts of the scene need to be captured at a uniform resolution. Selectively and opportunistically reducing resolution for different regions of image frames can yield high-precision visual computing at energy-efficient memory data rates.

To this end, we develop a visual sensing pipeline architecture that flexibly allows application developers to dynamically adapt the spatial resolution and update rate of different "rhythmic pixel regions" in the scene. We develop a system that ingests pixel streams from commercial image sensors with their standard raster-scan pixel read-out patterns, but only encodes relevant pixels prior to storing them in the memory. We also present streaming hardware to decode the stored rhythmic pixel region stream into traditional frame-based representations to feed into standard computer vision algorithms. We integrate our encoding and decoding hardware modules into existing video pipelines. On top of this, we develop runtime support allowing developers to flexibly specify the region labels. Evaluating our system on a Xilinx FPGA platform over three vision workloads shows 43 - 64% reduction in interface traffic and memory footprint, while providing controllable task accuracy.

## 2.1 Introduction

Through the lens of their cameras, mobile devices can visually observe a user's environment for detecting faces, understanding spatial scene geometry, and capturing images and videos. This has yielded a wide range of benefits, especially as image sensors have grown to support increasingly higher resolutions and frame rates. With such precision, it is now possible to position augmented reality (AR) overlays over users' faces or spatial living environments for social entertainment. Virtual AR media can also annotate physical environmental surfaces, including for navigational guidance for walking directions Google (2019). Wirelessly connected camera devices on the Internet-of-Things can provide home security, such as through video doorbells.

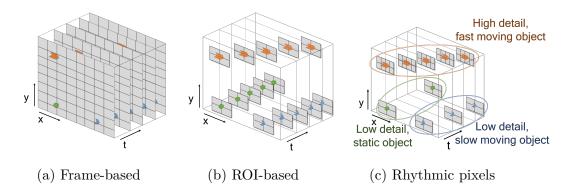

Figure 1: Traditional Frame-Based Computing Captures and Processes Entire Frames. ROI-Based Computing Samples Regions of Interest, but at Uniform Spatial and Temporal Resolution. With Rhythmic Pixel Regions, Different Regions Are Captured at Different Spatio-Temporal Resolutions.

Unfortunately, visual systems on mobile systems are limited in their spatial precision, computational performance, and energy efficiency while performing continuous visual tasks. Mobile systems are constrained by their small form factors with limited battery sizes and heat management requirements. To reduce the power consumption, recently proposed systems reduce the spatial resolution and frame rate of image capture LiKamWa *et al.* (2013); Hu *et al.* (2018) to receive commensurate energy savings, especially by reducing the memory traffic of the DRAM-based frame buffers. Thus, resolution provides a tradeoff mechanism to dynamically configure systems for low power consumption or high visual task fidelity. However, downscaling or windowing a frame forces the application to reduce the resolution of the entire frame. Reducing the frame rate similarly reduces the temporal resolution of the entire frame stream. This reduced spatiotemporal resolution across the entire frame stream can lead to suboptimal visual precision.

This work aims to improve the capabilities of continuous mobile vision systems, based on a key insight: The precision, performance, and efficiency of visual computing systems are limited by the current pattern of capturing and processing entire image frame streams at **uniform** spatial resolutions and **uniform** frame rates. This assumption of frame-based computing (Fig. 1a) presents an inflexibly coarse granularity of tradeoff between task accuracy and energy efficiency. Most natural scenes do not have the same resolution needs across the entire image frame. Precise AR placement requires high spatial resolution for visual features on tracked surfaces, but would suffice with a relatively lower resolution for the rest of the frame. The detection and tracking of faces, hands, and objects could use a higher temporal resolution to capture quick motions, while the rest of a relatively static scene would suffice with a lower frame rate. Such tradeoffs are unavailable with the current model of frame-based computing. To address this, we present a fundamental shift away from frame-based visual computing and towards *rhythmic pixel regions* (Fig. 1c), which we define as neighborhoods of pixels with region-specific spatiotemporal resolutions. Unlike visual computing based on a few Regions-of-Interest (ROIs) Iqbal *et al.* (2020), rhythmic pixel regions leverage encoded data representations that scalably allow for the capture of hundreds of regions, with independently defined spatiotemporal resolutions. By supporting the simultaneous capture of a diversity of rhythmic pixel regions, our visual computing architecture allows the developer to selectively specify regions where higher spatiotemporal resolution is needed and where lower spatiotemporal resolution will suffice (Table 1), e.g., dynamically guided by the properties of the visual features. The fine-grained configurability will allow developers to extend their existing visual computing algorithms and applications for high energy efficiency. This creates the illusion of high spatiotemporal resolution capture at low power consumption by eliminating the wasteful DRAM traffic of unproductive pixels.

To design the rhythmic pixel region abstraction and the architecture to support it, we introduce two hardware sensor data interfaces: an encoder to selectively reduce sets of pixels before they are stored in memory, and a decoder to reconstruct the pixels from memory into traditional frame-based addressing for standard application use. Together, the rhythmic pixel region encoder and decoder work to reduce the significant DRAM traffic of writing and reading visual data, leading to system energy savings. These interfaces, which integrate into the System-on-Chip, support existing and future high-resolution image sensors, allowing for a revolutionary upgrade to evolutionary mass-market-scale image sensors.

To evaluate our system, we design our implementation on a Xilinx ZCU102 FPGA SoC platform. We support various visual workloads, including hardware-

|                     | Trad. uniform frame-based vision          | Rhythmic pix region-based vision          |

|---------------------|-------------------------------------------|-------------------------------------------|

|                     | If any part of the frame needs to be      | Regions with small, detailed, and/or      |

| Spatial Decalution  | captured at a high resolution, e.g., to   | distant features can be captured with     |

| Spatial Resolution  | resolve complex texture or distant ob-    | the precision of high resolution. Frame   |

|                     | jects, the entire frame will need to be   | regions with large, static, close visual  |

|                     | captured at a high resolution.            | features can be captured with the effi-   |

|                     |                                           | ciency of low resolution.                 |

|                     | If any part of the frame needs to be      | Regions can be captured at different      |

| Temporal Resolution | captured at a high frame rate, e.g., to   | intervals. The entire frame can be        |

| Temporal Resolution | track substantial motion, the system      | scanned to update spatial understand-     |

|                     | will need to capture a sequence of entire | ing at a lower rate, e.g., 1 fps. Regions |

|                     | frames of pixels at high frame rate.      | of moving objects/surfaces can be cap-    |

|                     |                                           | tured at higher rates, e.g., 60 fps.      |

Table 1: Opportunities for Rhythmic Pixel Regions

accelerated neural network processing for face and object tracking, and OpenCV-based visual simultaneous localization and mapping (V-SLAM). Through our evaluation, we demonstrate the opportunity of rhythmic pixel regions to decrease pixel memory traffic by 43 - 64% while only minimally degrading the visual task accuracy, e.g., only increasing absolute trajectory error of V-SLAM from  $43 \pm 1.5$  mm to  $51 \pm 0.9$  mm in our case study. Through reduction in memory traffic, rhythmic pixel region based techniques can significantly increase the energy-efficiency of battery-backed mobile systems.

In summary, we make the following contributions:

- To the best of our knowledge, we are the first to propose a visual computing paradigm where different parts of the scene are captured at different spatiotemporal resolutions – before the frame enters memory – for overall system energy-efficiency while respecting task needs.

- We develop two *lightweight and scalable* IP blocks rhythmic pixel encoder and decoder which decimates the incoming pixel stream while writing to memory and reconstructs the pixel stream on-the-fly while reading from memory.

- We develop a library and runtime to coordinate vision tasks with encoder/decoder operation.

- We augment our architecture and runtime support on top of an existing commercial mobile vision pipeline built around a FPGA platform. We evaluate the augmented architecture on a variety of vision tasks to demonstrate significant reduction in memory traffic with controllable accuracy loss.

#### 2.2 Background and Related Work

A primer on vision pipelines: The ecosystem of visual computing sensors, devices, systems, and algorithms on mobile devices have rapidly evolved to provide high-performance platforms for multitude of vision tasks such as augmented reality on smartphones, tablets, and headsets Höllerer and Feiner (2004).

Image sensors collect digital readings of visual pixels in a frame Richard Szeliski (2010). The sensor sends values over a streaming MIPI interface, which enacts a serial transmission over multiple lanes MIPI Alliance (2020). The MIPI receiver inside the SoC receives the frame information from camera. In the sensor or on the system-on-chip, there is often an image signal processor (ISP) inserted into the visual computing pipeline, performing image improvement operations, e.g., white balance, and format changes, e.g., YUV conversion. Regardless of the placement and operation of the ISP, the visual hardware pipeline eventually writes the frame into DRAM and signals to the operating system that a frame is ready for readout from the memory.

Data movement across the off-chip MIPI and DDR interfaces entails significant energy consumption Ghose *et al.* (2018). While tasks such as AR could significantly benefit from high spatiotemporal resolutions, e.g., 4K at 60 fps, these resolutions generate high datarates across the camera and memory interfaces. For example, the system expends 2.8 nJ to move a pixel Pandiyan and Wu (2014); Ho *et al.* (2001); Raghunathan *et al.* (2003); Magen *et al.* (2004); Meindl *et al.* (2002) across the DDR interface, whereas it expends only 4.6 pJ for performing a multiply-and-accumulate (MAC) operation Hameed *et al.* (2010) around that pixel.

For AR, the software processes the frame through visual computing frameworks, extracting visual features to feed into SLAM algorithms Mur-Artal, Raúl, Montiel, J. M. M. and Tardós, Juan D. (2015). These algorithms form a spatial understanding of the scene to estimate the pose of the camera. The pose of the virtual camera is precisely updated to the estimated pose of the physical camera. This allows the system to overlay virtual objects over the physical environment, achieving the AR illusion.

Multi-ROI sensors: Many image sensors are capable of selecting a region-ofinterest (ROI) for readout ximea (2019). There are also sensors that allow for multiple ROIs to be read out Stemmer Imaging (2019). As region selection is performed at the sensor level, it offers efficiency and speed by reducing sensor readout time. However, there are significant limitations to adopting these sensors for mobile systems. In particular, the expressiveness of sensor-based region selection is limited by the footprint of additional circuitry. For example, in one such sensor, the region selection is limited to 4 regions, regions cannot overlap, and only full resolution and frame rate are available ximea (2019). In contrast, our support for rhythmic pixel regions provides extensive configurability and composability through the inherent scalability of the encoded data representation. This allows a much larger number of regions (hundreds), and grants each region independent resolution and rhythm/interval control. Moreover, we implement region selection in the SoC, which allows any conventional image sensor to employ multi-ROI benefits, including emerging high resolution and high framerate sensors.

**Event-driven cameras:** Event-driven cameras, also known as dynamic vision sensors, focus their sampling on pixels that change their value Gallego, Guillermo and Delbruck, Tobi and Orchard, Garrick and Bartolozzi, Chiara and Taba, Brian and Censi, Andrea and Leutenegger, Stefan and Davison, Andrew and Conradt, Jörg and Daniilidis, Kostas and others (2019). This allows for a significant reduction in sensor

bit rate and allows microsecond time resolution. However, the circuitry is spatially expensive due to per-pixel motion detection module, reducing frame resolution, e.g., to 128 x 128 pixels. This limits the scalability of these sensors to support high resolutions. More fundamentally, the logic of deciding what pixels to read out is limited at hardware design time, disallowing high-level and/or semantic knowledge from governing the pixel selection process. Thus, while our work shares similar motivations and inspirations – reducing data rate for efficiency and performance – we uniquely allow the expressive ability to dynamically use knowledge of visual feature extraction needs to selectively sample pixels as needed.

Image/Video Compression: Decades of work in image processing has gone towards compressing images and videos to reduce the bit rate of storing and transmitting media. Many of these techniques are inspiring to this work. For example, JPEG and other image compression standards reduce information at spatial frequencies with less perceptual priority Richard Szeliski (2010). MPEG-H Part 2 / HEVC / H.265 reduce redundant information by leveraging estimated motion information from frame-to-frame Iaian Richardson (2004). However, such entropy-coding compression techniques require the frame – or multiple copies of the frame – in memory before compression can be done. This incurs the memory overhead of visual computing that rhythmic pixel regions strives to avoid; we perform encoding *before* the frame enters the DRAM. Traditional video codecs also employ sophisticated techniques such as discrete cosine transform (DCT) and motion compensation for data reduction, increasing their design complexity. In contrast, we use simple pixel discard based strategy for data reduction.

**Foveated Rendering:** To improve graphical rendering capabilities under limited computing resources, foveated rendering focuses rendering effort where users are likely

to notice. Foveated rendering Wikipedia (2020) uses eye tracking to estimate user gaze and renders content near the gaze target at higher spatial resolutions. We apply similar motivation, increasing spatiotemporal resolution where it is needed, but with a distinctly different goal: to only capture necessary visual information. Among other differences, our work involves multiple simultaneous regions, as opposed to the singular region in foveated rendering.

Flexible spatio-temporal sampling algorithms: Computer vision researchers propose different algorithms that modulate different regions in an image with different spatio-temporal resolutions for computational photography and video prediction usecases. Flexible voxels Gupta *et al.* (2010) proposes an efficient space-time sampling scheme that enables per-pixel temporal modulation and a motion-aware reconstruction scheme for artifact-free videography. More advanced techniques Reddy *et al.* (2011) have been proposed for space-time sampling and interpolation for video compressive sensing and high-speed imaging.

More recently, researchers proposed neural networks Lu *et al.* (2017) to generate high frame rate videos from low frame rate counterparts. These networks analyze spatiotemporal patterns across frames in a video to create interpolated frames. While we use similar spatiotemporal sampling mechanisms, we focus on providing the architecture and runtime support to enable spatiotemporal rhythmic capture on an embedded system.

Energy-efficient visual systems To reduce energy consumption and bandwidth utilization, some systems offload only interesting frames to the cloud, discarding the rest Chen *et al.* (2015). Determining which frames to discard itself is often an expensive task. To this end, other systems Naderiparizi *et al.* (2017) implement a dedicated hardware/software subsystem using an array of gating sensors and imagers. Other hardware-software co-design techniques reuse computation for energy-efficient visual computing. Euphrates Zhu *et al.* (2018) reuses the motion vector information from the ISP to extrapolate bounding box results for object detection to avoid extraneous vision processing on certain frames.  $EVA^2$  Buckler *et al.* (2018) exploits temporal redundancy between frames and uses motion compensation techniques to approximate CNN results. ASV Feng *et al.* (2019) applies stereo-specific algorithmic and computational optimizations to increase the performance with minimum error rate. Instead of approximating computation, our work primarily focuses on reducing the memory traffic of sensing by discarding pixels early in the vision pipeline. As such, rhythmic pixel regions can be complementary to the aforementioned visual processing techniques, with approximate computing filling in the visual gap of unsampled pixel data.

(b) Experimental Example Data with ORB-SLAM-Based Regions

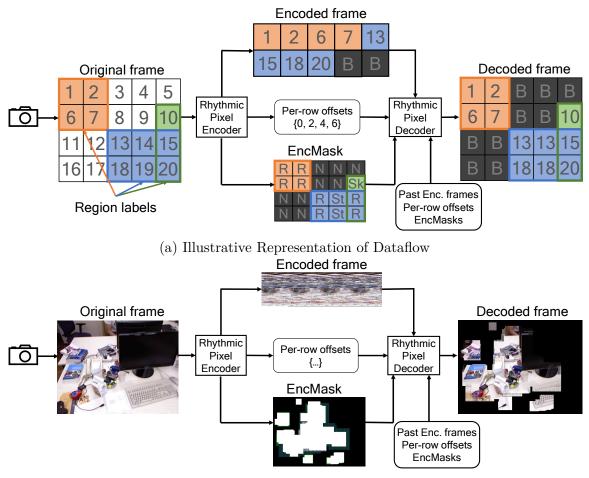

Figure 2: The Process of Encoding and Decoding. The Encoder Packs Pixels Within the Regions from the Original Image, Maintaining Raster-Scan Order. The Decoder Reconstructs Data from the Encoded Frame, Per-Row Offsets, and Encoding Mask.

# 2.3 Visual Computing with Rhythmic Pixel Regions

The overarching concept of rhythmic pixel regions is to encode visual information captured by conventional sensors such that the encoded visual data: (i) meets realtime visual requirements specified by application developers, (ii) reduces the pixel memory throughput and footprint of pixel stream data into DRAM, and (iii) can be reconstructed into visual frames for application usage. Here, we introduce key data structures that specify the region labels, the encoded pixels, and associated meta-data, and how these data structures are used to perform pixel sampling and interpolation to satisfy visual needs. We also illustrate the effect of this new paradigm on a case study based on visual SLAM.

# 2.3.1 Developer-Specified Region Labels

To mark the regions to be captured, as well as their spatiotemporal qualities, the system allows developers to specify a set of region labels (Fig. 2a) to define a capture workload. Each region label includes the following attributes:

- The coordinates of the top-left corner of the region

- The width and height of the region

- The stride resolution of the region, i.e., the density of pixels

- The skip rate, i.e., the time interval of consecutive sampling

We do not yet support movement, resize, or other temporal dynamics of regions in this work.

## 2.3.2 Encoded Frame

The encoder uses the region labels to selectively store a reduced set of pixels into memory, forming the encoded frame. Pixels within any of the region labels are stored in original raster-scan order, while omitting any pixels that do not fall within regions, or are not within the rhythm of the stride or skip. This results in a tightly packed encoded frame (Fig. 2a).

Figure 3: For ORB-SLAM, Rhythmic Pixel Regions Can Discard Irrelevant Pixels Early in the Pipeline for Memory Efficiency, While Preserving Relevant Regions at Sufficient Resolutions for Accuracy.

Notably, traditional ROI-based computing typically adopts a different memory representation, storing each region of pixels as a grouped sequence in memory. For the small number of regions that ROI-based computing typically supports, this may suffice, but when scaled to hundreds of regions, this creates unfavorable random access patterns into DRAM and/or buffering of large portions of the frame into local SRAM when writing pixels into memory. Furthermore, overlapping regions will duplicate the storage of pixels that appear in multiple regions. Instead, by preserving raster scan order, the rhythmic encoded frame representation instead retains sequential write patterns. This allows for highly efficient scalability to raised number of regions with minimal resource overhead.

# 2.3.3 Metadata: Per-Row Offset, Encoding Mask (EncMask)

To service pixel requests from the vision applications, the decoder will need to translate pixel addresses in the original frame into pixel offsets in the encoded frame before retrieving the pixel value. However, this would limit decoder scalability, as the complexity of the search operation quickly grows with additional regions.

Thus, instead of using region labels, we propose an alternative method that uses two forms of metadata for the decoder to reconstruct the original pixel stream (Fig. 2a).

First, a per-row offset counts the number of encoded pixels prior to that row in the image. Second, an encoding sequence bitmask (EncMask) helps the decoder to reconstruct a pixel stream without the need for region labels. For each pixel in the original (pre-encoding) frame, the EncMask uses a two-bit status that indicates how a pixel is sampled in space and time:

N(00): Non-regional pixel

St (01): Regional pixel but strided

Sk (10): Regional pixel but temporally skipped

R (11): Regional pixel

Together, the per-row offset and EncMask allow the decoder to find the relevant pixel address in the encoded frame, and access the appropriate values from the current encoded frame or previous encoded frames to decode the pixel. We provide more information about this process in Section 2.4.2.

## 2.3.4 A Case Study Around ORB-SLAM

ORB-SLAM Mur-Artal, Raúl, Montiel, J. M. M. and Tardós, Juan D. (2015) is a popular real-time V-SLAM algorithm, highly centered around tracking visual "features", creating a map of localized features, and finding matches to previously mapped features for continual positioning. Visual features – key for scene understanding – are scattered throughout a scene and carry different spatiotemporal needs. While running ORB-SLAM for augmented reality, for example, the feature extractor routinely detects several hundreds of features (e.g., 1500 features in a 1080p frame) at varying distances from the camera. This motivates the need to sample hundreds of regions around hundreds of features with need-specific resolutions. Features can be grouped into a smaller number of regions, but this reduces task accuracy and memory efficiency, as we demonstrate in §3.5.

In the context of rhythmic pixel regions, ORB features will be located in the decoded pixel streams. Regions covering the entire frame can be captured at a slower skip rate to maintain coverage of features as the device moves around the space. In between full captures, detected features in both full and partial captures can guide region label selection for the subsequent frame, defining regions around feature locations and with properties based on feature characteristics. Specifically, our policy uses the feature's "size" attribute to guide the width and height of the region. Along similar lines, it uses other feature attributes such as "octave" for stride and feature movement between frames for temporal rate. The encoder uses these feature-based region labels to selectively store pixels of interest and metadata into memory. The decoder uses these to reconstruct the frames for the algorithm to access and use for ORB-SLAM and further region selection.

We evaluate the efficacy over the TUM dataset Sturm *et al.* (2012) of 480p videos, capturing full frames every 10 frames and feature-based regions for other frames. As shown in Fig. 3, we find that using rhythmic pixel regions can eliminate the memory storage of 66% of the pixels of the original stream, while only increasing absolute trajectory error from 43  $\pm$  1.5 mm to 51  $\pm$  0.9 mm. We further explore the applicability of rhythmic pixel regions to visual workloads in our evaluation.

#### 2.4 Design

The rhythmic pixel region architecture centers around the idea of: (i) encoding pixel streams to reduce the pixel data stored in memory, and (ii) decoding the pixel streams for vision application usage. Here, we outline the design aspirations that guide our architecture. We then describe the design of two hardware units – a rhythmic pixel encoder and a rhythmic pixel decoder – and their integration with the existing mobile SoC vision pipeline, as shown in Fig. 4. We also discuss the software runtime for vision application developers to leverage these hardware extensions through policy specification.

**Design aspirations:** We set four goals that guide the design of our hardware and software extensions.

- Lightweight: Our encoding/decoding techniques should be lightweight (unlike traditional video codecs) so that they can be designed and integrated with minimal resource overhead.

- Scalable: Our system should scale to support the capture of many regions with minimal resource overhead.

- Memory friendly: Our hardware extensions should perform encoding/decoding tasks with efficient memory access patterns and minimal DRAM traffic

- Flexible: Our runtime should allow developers to flexibly and independently specify resolution and update rate needs on a per-region basis.

Figure 4: System Design. The Rhythmic Encoder Decimates the Incoming Pixel Stream from Camera and Encodes Only Region-Specified Pixels into Memory. The Rhythmic Decoder Decodes the Pixels for Use with the Vision Algorithms.

# 2.4.1 Rhythmic Pixel Encoder Architecture

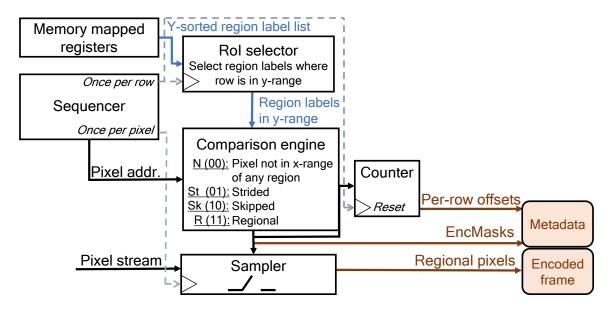

The rhythmic pixel encoder module, shown in Fig. 5, intercepts the incoming pixel stream from an image sensor pipeline and uses developer-specified region labels to encode pixels into an encoded frame. The encoder also generates associated metadata (per-row offset is a count of the number of regional pixels in a row, and EncMask is the output of the region comparison process), which is stored with the encoded frame in DRAM. The app specifies region labels using the designed runtime support in Section 2.4.3.

We design our encoder as a fully streaming based module that avoids the need for partitions to store individually addressed regions. Instead, our encoder directly operates on a dense raster-scan based pixel stream, produces a sparse encoded stream based on the region labels, and writes the encoded stream to the DRAM, all with *on-the-fly* streaming operation.

## 2.4.1.1 Raster-Scan Optimized Sampling:

The sampling block operates on the pixel stream and decides whether to sample a pixel in space and time based on whether the pixel is in any of the regions or not. A naive approach could sequentially compare a pixel's location against every region label. This would be time consuming and would hinder pipeline performance. Although parallelizing the region label checking process would solve performance issues, we find that this exponentially increases the number of resources to support more regions, limiting encoder scalability.

Instead, our approach is to exploit the raster-scan patterns of the incoming pixel stream to reduce and reuse the work of the region search. The Sequencer keeps track of row and pixel location. For a given row, there is a smaller subset regions that are relevant – where the y-index of the pixel is inside of the y-range of the region and matches the vertical stride. The RoI Selector performs this search space reduction, i.e., converting from the region list to a sublist, once per row. Then, from pixel to pixel, the encoder's Comparison Engine only needs to check whether the x-index of the pixel is inside any of the regions in the sublist and matches the horizontal stride. As the sublist is much smaller than the original list, this design choice substantially reduces the level of region-based parallelism needed for the Comparison Engine, saving hardware complexity.

In addition, we perform further optimizations for the comparison engine based on spatial locality. Within a row, if we find that if a pixel belongs to a region, the Sampler can apply the same comparison result for the next *region width* number of pixels. We also simplify the process of finding relevant regions for a row through

Figure 5: Encoder Intercepts the Incoming Pixel Stream and Only Forwards Pixels That Match the Stride and Skip Specifications of Any Region.

sorting the regions by their y-indices. This can be done by the rhythmic pixel region app runtime.

## 2.4.1.2 Integration with ISP Output

The placement of the encoder has implications on the efficiency of the visual capture. The most energy-efficient integration of the encoder would be on the sensor itself, reducing pixel traffic over the sensor interface and potentially reducing ISP computations. However, this would need a re-design of the ISP, which conventionally expects pixels in frame-based ordering in its algorithms. Thus, for this work, we instead integrate the encoder at the output of the ISP to seamlessly work with existing commercial ISPs.

As with typical ISP operation, the encoder collects a line of pixels before committing a burst DMA write to a framebuffer in the DRAM for efficient and performant memory transaction. Using a framebuffer allows asynchronous access to frame pixels. In the case of the rhythmic pixel architecture, the framebuffer also allows the system to collect multiple frames of data, which the decoder can use to extrapolate regional pixels over a sequence of frames for regions with temporal skip rate. The metadata (per-row offset and EncMask) of the frame is also stored alongside the framebuffer in DRAM. As the EncMask occupies 2 bits per pixel, we note that it occupies 8% of the original frame data (e.g., 500 KB for a 1080p frame). As explored in our evaluation, this amounts to a minimal memory overhead compared to the memory savings.

# 2.4.2 Rhythmic Pixel Decoder Architecture

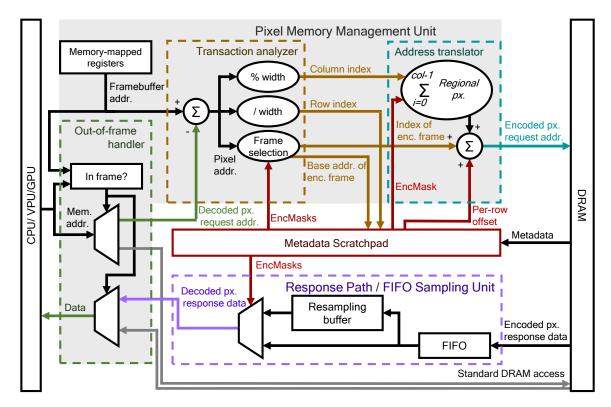

The rhythmic pixel decoder fulfills pixel requests from the vision app, which seek groups of sequential pixels from a decoded framebuffer. While the app forms its request around pixel locations in the decoded address space, the decoder uses the metadata and encoded frames to translate decoded pixel addresses to the DRAM addresses of the encoded frame pixels. This request path is managed by a pixel memory management unit (PMMU), as described below and shown in Fig. 6.

The response path returns the pixel values to the vision application through a FIFO Sampling Unit. If required by spatial stride or temporal skip situations, the FIFO Sampling Unit interpolates encoded data to create decoded pixel values, which it provides to the requesting processor. Otherwise, the decoder returns the pixel value, or a black pixel, if the pixel was not within any of the specified region labels. As described below, the metadata is used to make such determinations.

Figure 6: Decoder Fulfills Pixel Requests from the Vision App in Two Steps. (a) The Pixel MMU Performs Address Translation to Fetch the Right Set of Pixel Regions from Encoded Frame. (b) The FIFO Sampling Unit Reconstructs the Original Pixel Regions from Encoded Pixel Regions and Metadata.

# 2.4.2.1 Pixel Memory Management Unit for Pixel Address Translation:

The PMMU works in the same spirit as a traditional memory management unit (MMU); while MMUs perform virtual to physical address conversion, our PMMU translates pixel transactions from decoded to encoded space. Similar to the exception handler of an MMU, the PMMU's Out-of-Frame Handler examines a memory request and determines if it is a valid pixel request, i.e., if the requested memory address is in the decoded framebuffer address space. The Out-of-Frame Handler forwards the transaction if it's a pixel-based one; otherwise, it will bypass for standard memory access.

Meanwhile, the Metadata Scratchpad loads the per-row offset and EncMask information pertaining to the transaction for the four most recent encoded frames. The Transaction Analyzer analyzes the EncMasks of the transaction and generates different sub-requests based on where the encoded pixels are present. Based on the stride (St) and skip (Sk) values of the EncMask bits, the pixel may be in the most recent encoded frame, or one of the recently stored encoded frames. Thus, similar to a virtual memory request, translation of these pixel requests creates sub-requests that are characterized by a base address (of the encoded frame), offset (row and column), and a tag index of which frame hosts the desired pixels.

These sub-requests are fed to a translator. For intra-frame requests, the base address remains the same, whereas for inter-frame requests, the translator modifies it to the appropriate base address. The per-row offset is read from the metadata. The column offset is the count of the number of full regional pixels from the start of the row until that pixel (The number of "11" entries in the EncMask). The translator sums this information to generate the new encoded pixel request corresponding to each sub-request, which will be sent to DRAM.

#### 2.4.2.2 FIFO Sampling Unit:

A FIFO buffers data packets received from a pixel-based DRAM transaction. To prepare a pixel value to service the original request, the engine either dequeues pixel data from the FIFO, re-samples the previous pixel (in the case of stride), or samples a black pixel, based on the EncMask. The unpacker also relays the RLAST control signal to indicate the last transfer in the transaction for proper handshake with the processing unit for the memory request. We integrate the decoder module with the existing DDR controller inside the SoC. By doing so, the decoder can intercept memory traffic coming from any processing element and service requests.

# 2.4.3 Developer Support for Rhythmic Pixel Regions

From the point of view of the processing unit – CPU, visual processing unit, or GPU – the rhythmic pixel region architecture preserves the addressing scheme of the original frame-based computing through the decoded framebuffer address. This allows fully transparent use of existing software libraries and hardware accelerators, with no modification needed.

We develop runtime support to allow the developers to flexibly specify region labels. This consists of a RegionLabel struct and a SetRegionLabels() function for developers to set a list of regions. Region label lists can be set on a per-frame basis or persist across frames. A runtime service receives these calls to send the region label list to the encoder.

```

struct RegionLabel {

int x, y, w, h, stride, skip;

};

SetRegionLabels(list<RegionLabel>);

```

#### 2.4.3.1 Policy-Based Usage of Rhythmic Pixel Regions

Developers can build various policies that autonomously guide the region selection, in the similar spirit to issuing frame configurations with the Frankencamera API Adams *et al.* (2010) or Android's Camera API Android (2019). Policies can incur different system overheads, leading to system trade-offs. A policy should predict region progression with time as well as a region quality requirements to maximize task performance. A feature-based policy (such as that in our case study of Section 2.3.4) can use proxies, such as feature scale and feature displacement to estimate spatial and temporal resolutions of regions. Developers can also introduce improved applicationspecific proxies with other prediction strategies, e.g., with Kalman filters Iqbal *et al.* (2020).

The process of policy generation and modifying the app around that policy could be cumbersome for an app developer. To reduce the burden, we propose two tiers of developers

*Policy Makers:* The first tier of developers can specialize in policy development. They can write a wide variety of policies that employ a feature-based approach and/or sophisticated motion-vector based techniques, such as those found in Euphrates or  $EVA^2$  to guide region selection.

*Policy Users:* The second tier of developers could select a policy directly from a pool based on their app needs.

This dichotomy of policy makers/users follows a typical stratified development paradigm, where high-level developers can simply employ domain-specific libraries (e.g., cuDNN, cuFFT, cuBLAS) that are developed to take advantage of architectural complexity (e.g., with CUDA) by a different set of low-level developers.

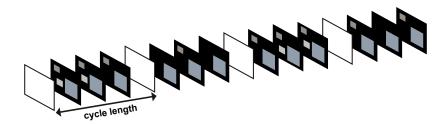

Figure 7: With Rhythmic Pixel Regions, Policies Can Define How Different Regions in the Image Can Be Captured at Non-Uniform Spatial and Temporal Resolutions. In This Illustrated Policy, Regions Shaded in Black Are Not Sampled. To Track Objects Entering/Leaving the Scene, the System Performs a Full-Frame Capture on a 'Cycle Length' Periodicity.

**Example policy:** As described in the case study, policies can center rhythmic pixel regions around features, ensuring that features are captured at sufficient resolution. We define an example policy (Fig. 7) around the concept of a *cycle length*, which is the number of consecutive frames between two full frame captures. These occasional full frame captures can provide contextual information of the entire scene at a slower temporal rate, while feature-based region tracking in the intermediate frames can provide continual coverage of important regions.

The visual features processed by the app – readily available in memory – can be used to determine the pixel regions for the next subsequent frame, centering around the features. For example, as discussed in §2.3.4, an ORB feature's "size" (or scale) attribute OpenCV (2015) can guide the width and height of its corresponding region, ensuring that the meaningful neighborhood of pixels around the feature is captured (with extra margin to allow for frame-to-frame feature displacement). Furthermore, the "octave"OpenCV (2015) attribute, which describes the texture of the feature, can determine the stride (resolution) parameter for each region. Through the displacement of matched features from frame to frame and measuring the displacement, the system can estimate the movement of a region. The policy can use this feature velocity to determine the temporal rate parameter of pixel regions, sampling fast moving regions more frequently and slow-moving regions less frequently.

We use and adapt this example policy to various visual workloads in our implementation and evaluation. We evaluate different cycle lengths, finding that as the cycle length increases, system efficiency improves, but the errors due to tracking inaccuracy also accumulate, and vice-versa. Cycle length thus becomes an important parameter to govern the tradeoff to meet application needs. The cycle length could also be adaptive, for example, by using the motion in the frame or other semantics to guide the need for more frequent or less frequent full captures. We envision that future policies developed by a wider community of policy makers could substantially improve the opportunities of rhythmic pixel regions.

| Component | Specification                                     |

|-----------|---------------------------------------------------|

| Camera    | Sony IMX274, 4K $@$ 60 fps                        |

| ISP       | Demosaic and Gamma correction, 2 Pixels Per Clock |

| CPU       | ARM Cortex-A53 quad-core                          |

| GPU       | ARM Mali-400 MP2                                  |

| NPU       | Deephi DNN co-processor                           |

| DRAM      | 4-channel LPDDR4, 4 GB, 32-bit                    |

Table 2: System Components in the Video Pipeline

2.5 Implementation

#### 2.5.1 FPGA-Based Encoder and Decoder Integration

**Platform:** We use Xilinx's reVISION stack platform Xilinx (2018) which implements a end-to-end video pipeline that emulates a standard mobile embedded vision pipeline. As shown in Table 7, we use Sony's IMX274 camera, a mobile class imager used in many smartphones for high fidelity capture, i.e., 4K @ 60fps. For the ISP, we use Xilinx's IP modules for performing demosaicing, gamma correction, and color-space conversion. These ISP blocks operate at a throughput of 2 pixels per clock for real-time performance. The processing subsystem comprises heterogeneous set of computing elements, similar to a mobile SoC. Specifically, the device contains an ARM Cortex-A53 quad-core CPU and an ARM Mali-400 MP2 graphics processing unit (GPU). In addition, we integrate a Deephi DNN co-processor Xilinx (2020b) into the FPGA fabric to emulate a neural network accelerator. Finally, the entire system is provisioned with 4 GB LPDDR4 DRAM in the processing subsystem, which we partially leverage for frame buffer capacity. The fully functional pipeline delivers real-time performance of up to 60 fps for video pass-through and up to 30 fps for certain vision tasks, such as face detection. We build our system around Xilinx's reVISION platform Xilinx (2018), which implements an end-to-end video pipeline with major components shown in Table 7.

Encoder and Decoder: We design our encoder IP module with Vivado HLS as a fully-streaming block with AXI-stream interfaces. In our encoder, input/output buffers are FIFO structures with a depth of 16. We find that this depth is enough to meet the 2 pixel-per-clock performance to match ISP performance and to avoid any pipeline stalls.

We also design our decoder with Vivado HLS, utilizing AXI memory-mapped interfaces on the input and output for integration with controllers and processing units. Our decoder operates within the timing budget without introducing extra latency. Both encoder and decoder functionally work in HLS simulations and the entire video pipeline passes Vivado FPGA post-layout timing. In addition to the hardware decoder, we design a software decoder using C++ and OpenCV. The software decoder runs in real-time for a 1080p video stream.

As Xilinx packages the system DDR controller as a part of its Zynq CPU IP module, we could not integrate the decoder between the DDR controller and the xPU as shown in Fig. 4. Instead, we integrate our decoder as a memory-mapped peripheral slave to Zynq SoC. In this integration, the system passes the pointers to the encoded frame and metadata to the decoder to reconstruct the original frame.

# 2.5.2 Runtime

Our runtime comprises a standard software stack with a user-space API, a kernelspace driver, and a set of low-level physical registers. We implement region parameters as registers in the encoder/decoder modules inside the SoC. Upon invoking any setter

| Task       | Algorithm                                                           | Resolution | Benchmark  | #Frames |  |

|------------|---------------------------------------------------------------------|------------|------------|---------|--|

| Visual     | ORB-                                                                | 4K@        | In-house   | 6000    |  |

| SLAM       | SLAM2 Mur-Artal, Raúl, Montiel, J. M. M. and Tardós, Juan D. (2015) | 30  fps    | dataset    | aset    |  |

| Pose       | DeceNet Coo et al. $(2010)$                                         | 720p@      | PoseTrack  | 3792    |  |

| estimation | PoseNet Cao <i>et al.</i> (2019)                                    | 30  fps    | 2017       | 0192    |  |

| Face       | RetinaNet 1996scarlet (1996)                                        | SVGA@      | ChokePoint | 22099   |  |

| detection  | termanet 1990scarlet (1990)                                         | 30  fps    | dataset    | 22099   |  |

Table 3: Vision Tasks and Benchmarks

function from the application, the user-space API passes parameters to the kernelspace driver. The driver then writes these parameters to the appropriate registers in the hardware units over an AXI-lite interface.

# 2.5.3 Workloads

We study three widely-used vision tasks: (i) Visual SLAM, determining camera position with respect to its surroundings while constructing the map of surroundings. (ii) Human pose estimation, tracking person movement. (iii) Face detection, tracking faces over time. For each task, as shown in Table 3, we choose state-of-the-art algorithms with different input, memory, and computational requirements.

Notably real-time performance of the V-SLAM workload is not attainable on the FPGA's CPU due to the compute-intensive nature of ORB-SLAM2. Therefore, we resort to a simulation-based approach where we run the V-SLAM workload on a desktop computer, generate the region labels, and feed them to the encoder. That said, there are commercial V-SLAM IP cores Synopsys (2020); EETimes (2020) available in the market that offer real-time performance. We plan to integrate them into our FPGA platform for future studies.

**Benchmarks:** We use popular publicly available benchmarks for each of these tasks to evaluate their accuracy. Each of these datasets comprise videos with different

visual attributes, including illumination variation and occlusion that mimic the realtime scenarios in the wild. In addition, these videos cover a wide range of settings, e.g., indoor/outdoor, crowded/dispersed, and fast/slow motion of objects making them realistic candidates for evaluating rhythmic pixel regions.

To evaluate the potential of rhythmic pixel regions on high-precision visual computing, we also evaluate visual SLAM on a 4K dataset. Since there are no ready-made 4K datasets available for visual SLAM, we create a dataset of 6000 frames spanning a total of 7 indoor video sequences with varying user movement. For portability, we use the 4K camera on a Microsoft Azure Kinect DK Microsoft (2020). We use an HTC Vive tracker setup to obtain the ground truth pose. The obtained ground truth pose has an offset compared to the original pose since the tracker is at a different location from the camera. We use the information from Kinect's IMU sensor to correct the offset.

For human pose estimation, we use the famous PoseTrack Max Planck Institute for Informatics, University of Bonn (2018) with 3792 frames across all video sequences. Finally, for face detection, we use the ChokePoint NICTA (2015) dataset which comprise 20 video sequences and 22,099 face images.

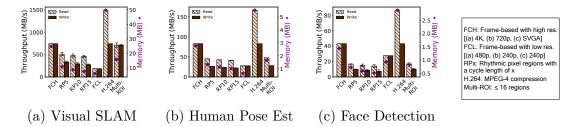

**Baselines:** We tested the workloads against the following baselines. (a) Framebased computing: The system captures frames at high resolution (FCH: 4K for V-SLAM) or low resolution (FCL: 1080p for V-SLAM) (b) Rhythmic pixel regions (RPx): The system implements rhythmic pixel regions of cycle length "x" (c) Multi-ROI cameras: The system simulates off-the-shelf multi-ROI cameras (d) H.264: The system performs H.264 video compression with the "Baseline" profile and the "5.2 (2160p60)" level for the codec.

Figure 8: Rhythmic Pixel Regions Reduces Pixel Memory Traffic by Generating Sparser Pixel Streams and Reduces the Memory Footprint by Generating Smaller Frame Buffers. The Reduction Is More with Higher Cycle Lengths.

As far as we've seen, commercial multi-ROI cameras only support up to 16 regions, likely due to architectural unscalability. For workloads that use more regions, we combine smaller regions into 16 larger regions through k-means clustering. To accurately represent the capabilities of multi-ROI cameras, we do not implement stride or skip adaptations. As an H.264 compression implementation is inaccessible on our FPGA board, we instead use a codec datasheet to form estimations Xilinx (2020a). As compression needs multiple frames to be stored in the memory, the pixel memory footprint and throughput scale accordingly.

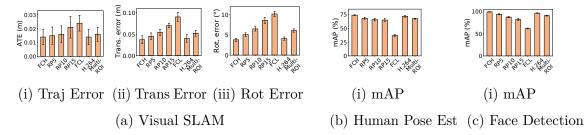

Figure 9: There Is a Trade-Off Between Cycle Length and Task Accuracy. In V-SLAM, We Observe High Standard Deviation. This Indicates Future Opportunity to Adaptively Reduce Cycle Length to Improve Accuracy for Scenes with High Motion.

#### 2.5.3.1 Metrics:

Here we discuss about different evaluation metrics.

**Task Accuracy:** We choose standard accuracy metrics from computer vision literature for all of our tasks. For visual SLAM, we use absolute trajectory error and relative pose error metrics as discussed in §2.3.4. For human pose estimation/face detection, we use the intersection over union (IoU) score as the metric. IoU measures the amount of overlap between the predicted and ground truth bounding boxes. A detection is a true positive (TP) if the IoU score is greater than a certain threshold; otherwise, it is considered as a false positive (FP). Final detection accuracy is the number of true positives among all detections, i.e., TP/(TP + FP), across all the frames, which is known as mean average precision (mAP).

**Datarate and Memory Footprint:** We build a throughput simulator which takes the region label specification per frame from the application and uses it to generate the memory access patterns of pixel traffic. The simulator counts the number of pixel transactions and directly reports the read/write pixel throughput in bytes/sec. For memory footprint, we measure the size of encoded frame buffers over time.

**Overhead:** We use Xilinx Vivado Xilinx (2019a) to determine the area and power overhead of our encoder and decoder modules. We use the resource utilization from the post-layout design as a proxy to report the area overhead; For power overhead, we use the numbers from Vivado power analysis tool.

| Task       | Avg. Number<br>of regions | Region size  | Stride | Rate                  |

|------------|---------------------------|--------------|--------|-----------------------|

| Visual     | 973                       | Min: 70x70   | Min: 1 | Min: $100 \text{ ms}$ |

| SLAM       | 915                       | Max: 230x230 | Max: 4 | Max: $33 \text{ ms}$  |

| Face       | 3                         | Min: 70x63   | Min: 1 | Min: $67 \text{ ms}$  |

| detection  | 3                         | Max: 270x228 | Max: 2 | Max: $33 \text{ ms}$  |

| Human Pose | 4                         | Min: 161x248 | Min: 2 | Min: 100 ms           |

| estimation | 4                         | Max: 324x512 | Max: 4 | Max: $33 \text{ ms}$  |

Table 4: Observed Statistics of Task and Benchmark

2.5.3.2 Policy/Parameter Choices:

We outline our choices below.

**Region selection:** As outlined in §2.4.3, we use feature characteristics to guide the selection of region labels to evaluate our tasks. For V-SLAM, region size is derived directly from the feature size attribute, while spatial and temporal resolutions are derived from the octave attribute and feature displacement respectively. We use face trajectory for face detection and skeletal pose joints for human pose estimation for determining the regions. Spatial and temporal resolutions are calculated based on the region's size and motion, respectively.

**Cycle length:** We evaluate the effectiveness of the example cycle-based policy with cycle lengths of CL=5, 10, and 15.

#### 2.6 Evaluation

# 2.6.1 The Use of Rhythmic Pixel Regions Is Flexible

Our runtime successfully allows apps to express region labels without any restrictions on the number, size, and resolution of the regions, as shown in Table 4. The size of these regions vary based on the semantics, e.g., nearness/farness of a face with respect to the camera. These regions are also sampled at different spatio-temporal resolutions based on their content.

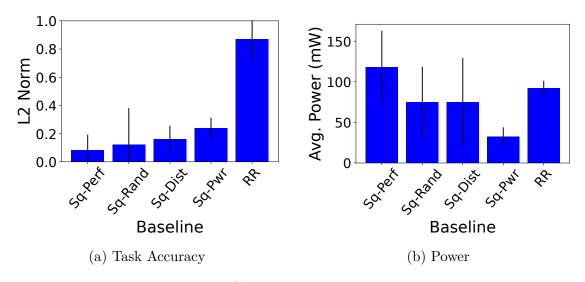

Algorithms/Apps are still reliable: With flexible region specification, the app now deals with only the pixels within the regions as opposed to the pixels in the entire frame. As shown in Fig. 9, we find that apps can still reliably perform their tasks with a slight accuracy loss compared to frame-based computing at high resolutions on uncompressed (FCH) or compressed (H.264) frames. Comparatively, frame-based computing at low resolutions (FCL) performs poorly, with significantly raised errors for all of the visual workloads.