## System-Level Synthesis of Dataplane Subsystems for MPSoCs

by

Glenn Leary

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved May 2013 by the Graduate Supervisory Committee:

Karamvir Chatha, Chair Sarma Vrudhula Aviral Shrivastava Rudy Beraha

ARIZONA STATE UNIVERSITY

August 2013

### ABSTRACT

In recent years we have witnessed a shift towards multi-processor systemon-chips (MPSoCs) to address the demands of embedded devices (such as cell phones, GPS devices, luxury car features, etc.). Highly optimized MPSoCs are well-suited to tackle the complex application demands desired by the end user customer. These MPSoCs incorporate a constellation of heterogeneous processing elements (PEs) (general purpose PEs and application-specific integrated circuits (ASICS)). A typical MPSoC will be composed of a application processor, such as an ARM Coretex-A9 with cache coherent memory hierarchy, and several application sub-systems. Each of these sub-systems are composed of highly optimized instruction processors, graphics/DSP processors, and custom hardware accelerators. Typically, these sub-systems utilize scratchpad memories (SPM) rather than support cache coherency. The overall architecture is an integration of the various sub-systems through a high bandwidth system-level interconnect (such as a Network-on-Chip (NoC)). The shift to MPSoCs has been fueled by three major factors: demand for high performance, the use of component libraries, and short design turn around time. As customers continue to desire more and more complex applications on their embedded devices the performance demand for these devices continues to increase. Designers have turned to using MPSoCs to address this demand. By using pre-made IP libraries designers can quickly piece together a MPSoC that will meet the application demands of the end user with minimal time spent designing new hardware. Additionally, the use of MPSoCs allows designers to generate new devices very quickly and thus reducing the time to market. In this work, a complete MPSoC synthesis design flow is presented.

We first present a technique [23] to address the synthesis of the interconnect architecture (particularly Network-on-Chip (NoC)). We then address the synthesis of the memory architecture of a MPSoC sub-system [24]. Lastly, we present a co-synthesis technique to generate the functional and memory architectures simultaneously. The validity and quality of each synthesis technique is demonstrated through extensive experimentation.

# DEDICATION

To my wife, Amanda, for enduring this long road with me. I Love You.

To my sweet little angel, Lauren, you have changed my life forever.

And to my Zoey. You were truly a Man's best friend. I will forever miss you.

$\begin{array}{c} {\rm Zoey} \\ 8.1.2011 - 1.18.2013 \end{array}$

### **ACKNOWLEDGEMENTS**

First I would like to give my thanks to my graduate advisor Dr. Karam Chatha for directing me throughout my Ph.D. study. It was his guidance that led me into the field of embedded systems. His knowledge and expertise has given me the guidance to overcome the obstacles that I encountered during my study. His help and insight has contributed to almost all of my research and the papers that I have published. I am honored to have had the opportunity to work with Dr. Chatha during the 6+ years (that's a long time) of my Ph.D. study. His wisdom will continue to guide me and help me throughout my professional career.

Secondly, I would like to thank my committee members for agreeing to join my committee. I sincerely appreciate their time and guidance. I would like to thank Dr. Vrudhula for his active participation in discussions and his dedication to the Embedded Systems Consortium. I would like to thank Dr. Shrivastava for his active role and contributions to the computing systems research lab. I would like to thank Dr. Beraha at Qualcomm Inc. for his professional insight into embedded devices. I consider myself lucky to have such a kind and knowledgable committee.

I would like to thank all of the lab members that I have spent time with, discussed research problems with, conducted projects with me, collaborated on papers with me, and who have made the process more enjoyable. I would like to thank Michael Baker for discussing research problems with me, working on projects with me, traveling the globe with me, and making life more enjoyable in and out of the lab. I would like to thank Sushu Zhang for her support at

the beginning when I was freshly starting my journey. I would like to thank Weijia Che for his help with the problems I had with Cell BE and StreamIT. I would like to thank Amrit Panda for his knowledge and the discussions we have had. I would to thank Jyothi Swaroop for his collaboration on SystemC. There have been many other lab members that have been of great help: Nikhil Ghadge, HaeSeung Lee, Krishna Mehta, and many others. They have all helped me in one way or another and I would like to thank them for their time and commitment.

I would like to thank the support I have received from outside of Arizona State University. In particular, the collaboration with the IUCRC has given me insight into the industry world and introduced me to many people. The collaboration with Qualcomm Inc. has been a great help in both leading me technically and supporting my study financially. The task of developing a Network-on-Chip synthesis technique for their IP has given me insight into a part of the industry I was blind to prior. The collaborations with the industry partners not only helped me be successful during my academic studies but also helped lay the foundation for a bountiful future after my graduation.

Last but not least, I would like to thank my family. I would like to thank my parents, brother, and sister for always being there for me when I needed it the most. I can not express in words what it has meant to have you all by my side. I would also like to thank my wife for sticking by me through it all. It has been a long and tenuous journey but you were always there for me. I love you and I am so happy to have you at my side as we begin the next chapter in our life together.

# TABLE OF CONTENTS

|     |      |        |                                        | Page |

|-----|------|--------|----------------------------------------|------|

| LIS | ST O | F TAB  | BLES                                   | . X  |

| LIS | ST O | F FIG  | URES                                   | . xi |

| СН  | APT  | ER     |                                        |      |

| 1   | INT  | RODU   | CTION                                  | . 1  |

|     | 1.1  | Contr  | ibutions                               | . 5  |

| 2   | THE  | E SYN' | THESIS OF THE NETWORK-ON-CHIP ARCHITEC | !_   |

|     | TUF  | RE     |                                        | . 6  |

|     | 2.1  | Motiv  | ration                                 | . 7  |

|     | 2.2  | Proble | em description                         | . 8  |

|     | 2.3  | Relate | ed Work                                | . 10 |

|     | 2.4  | NoC S  | Synthesis Technique                    | . 11 |

|     |      | 2.4.1  | Design flow                            | . 11 |

|     |      | 2.4.2  | Basic approach to topology synthesis   | . 12 |

|     |      | 2.4.3  | Deadlock avoidance                     | . 14 |

|     |      | 2.4.4  | Communication requirements             | . 19 |

|     |      | 2.4.5  | Port arity constraints                 | . 23 |

|     |      | 2.4.6  | Multiple use cases                     | . 25 |

|     |      | 2.4.7  | Algorithm Time Complexity Analysis     | . 25 |

| Cł | CHAPTER |        |                                            | Page |

|----|---------|--------|--------------------------------------------|------|

|    | 2.5     | Exper  | imental Results                            | . 26 |

|    |         | 2.5.1  | Experimentation set-up                     | . 26 |

|    |         |        | Benchmark designs                          | . 26 |

|    |         |        | Existing approaches                        | . 27 |

|    |         |        | Evaluation metrics                         | . 28 |

|    |         | 2.5.2  | Comparisons with existing approaches       | . 29 |

|    |         |        | Comparison with ILP for $S1 \ldots \ldots$ | . 29 |

|    |         |        | Comparison with GT for $S2 \ldots \ldots$  | . 31 |

|    |         |        | Summary of comparisons with ILP and GT     | . 33 |

|    |         | 2.5.3  | Impact of port arity                       | . 37 |

|    |         | 2.5.4  | Impact of increasing bandwidth             | . 38 |

|    |         | 2.5.5  | Degree of transaction interference         | . 41 |

|    |         | 2.5.6  | Deadlock avoidance analysis                | . 43 |

|    | 2.6     | Summ   | nary                                       | . 44 |

| 3  | THE     | E SYNT | THESIS OF THE MEMORY ARCHITECTURE          | . 47 |

|    |         | 3.0.1  | Motivation                                 | . 47 |

|    | 3.1     | Proble | em Definition                              | . 52 |

|    | 3.2     | Relate | ed Work                                    | . 54 |

|    | 3.3     | Syster | m-level memory synthesis                   | . 56 |

| CI | НАРТ | ER     |                                       | Page |

|----|------|--------|---------------------------------------|------|

|    |      | 3.3.1  | Data memory minimization              | . 58 |

|    |      | 3.3.2  | Code memory minimization              | . 60 |

|    |      | 3.3.3  | Time Complexity Analysis              | . 62 |

|    | 3.4  | Exper  | imental Results                       | . 63 |

|    |      | 3.4.1  | Comparison against Baseline Solution  | . 63 |

|    |      | 3.4.2  | Impact of Code Overlay Optimization   | . 66 |

|    |      | 3.4.3  | Comparison with Existing Approach     | . 67 |

|    |      | 3.4.4  | Impact of Area Constraint             | . 69 |

|    | 3.5  | Summ   | nary                                  | . 70 |

| 4  | THE  | E SYNT | THESIS OF THE FUNCTIONAL ARCHITECTURE | . 71 |

|    | 4.1  | Motiva | $\operatorname{ation}$                | . 71 |

|    | 4.2  | Proble | em Definition                         | . 75 |

|    | 4.3  | Relate | ed Work                               | . 76 |

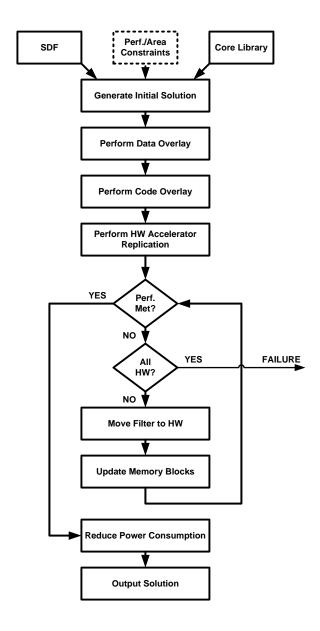

|    | 4.4  | Functi | ional Architecture Synthesis          | . 80 |

|    |      | 4.4.1  | Initial Solution                      | . 80 |

|    |      | 4.4.2  | Data Memory Minimization              | . 83 |

|    |      | 4.4.3  | Code Memory Minimization              | . 86 |

|    |      | 4.4.4  | Hardware Accelerator Replication      | . 89 |

|    |      | 4.4.5  | Iterative Transition to HW-SW Design  | . 90 |

| CHAPTER                                                   |      |      |  |

|-----------------------------------------------------------|------|------|--|

| 4.5 Experimental Results                                  |      | . 93 |  |

| 4.5.1 High Level Synthesis of Hardware Accelerator Librar | ry . | . 94 |  |

| 4.5.2 DCT Comparison                                      |      | 95   |  |

| 4.5.3 FFT Comparison                                      |      | . 98 |  |

| 4.5.4 Impact of Overlay                                   |      | 102  |  |

| 4.6 Extended Results                                      |      | 107  |  |

| 4.7 Summary                                               |      | 128  |  |

| 5 CONCLUSION AND FUTURE WORK                              |      | 129  |  |

| 5.0.1 Virtual Platform                                    |      | 130  |  |

| 5.0.2 RTL Generation                                      |      | 131  |  |

| REFERENCES                                                |      | 132  |  |

|                                                           |      |      |  |

| APPENDIX                                                  |      |      |  |

| A NETWORK-ON-CHIP SYNTHESIS                               |      | 137  |  |

| B MEMORY ARCHITECTURE SYNTHESIS                           |      | 145  |  |

| C FUNCTIONAL ARCHITECTURE SYNTHESIS                       |      | 151  |  |

# LIST OF TABLES

| Tab | ${ m le}$                                | Page  |

|-----|------------------------------------------|-------|

| 2.1 | Categories of synthetic benchmarks       | . 26  |

| 3.1 | Benchmark Specifications                 | . 62  |

| 4.1 | Minimum Buffer PASS Generation Sequence  | . 81  |

| 4.2 | Least Switching PASS Generation Sequence | . 82  |

| 4.3 | Data Inteference Table                   | . 85  |

| 4.4 | Code Inteference Table                   | . 87  |

| 4.5 | Hardware Accelerators Before Replication | . 89  |

| 4.6 | Hardware Accelerators After Replication  | . 90  |

| 4.7 | Benchmark Specifications                 | . 93  |

| 4.8 | Benchmark Constraints                    | . 94  |

| 4.9 | Single Software Core Comparison (FFT)    | . 105 |

# LIST OF FIGURES

| Figu | re                                          | Page |

|------|---------------------------------------------|------|

| 1.1  | Generic MPSoC Architecture                  | 2    |

| 1.2  | System-Level Synthesis Flow                 | 2    |

| 2.1  | Transaction level specification             | 9    |

| 2.2  | Overall design flow                         | 12   |

| 2.3  | Shortest path graphs                        | 13   |

| 2.4  | NoC Topology Synthesis                      | 14   |

| 2.5  | Example of a Deadlock                       | 15   |

| 2.6  | Deadlock Example - SPGs                     | 15   |

| 2.7  | Deadlock Example - Global SPG               | 16   |

| 2.8  | Deadlock Example - Global CDG               | 17   |

| 2.9  | Deadlock Example - Updated SPGs             | 18   |

| 2.10 | Pseudocode for deadlock avoidance           | 19   |

| 2.11 | Bandwidth violation                         | 20   |

| 2.12 | Transaction interference                    | 21   |

| 2.13 | Pseudocode for trace conflict resolution    | 22   |

| 2.14 | Router arity constraints                    | 23   |

| 2.15 | Pseudocode for router port arity resolution | 24   |

| 2.16 | Power/Router for ILP                        | 29   |

| 2.17 | Avg. packet latency                         | 30   |

| 2.18 | Avg. standard deviation                     | 31   |

| 2.19 | Power/Router for GT                         | 32   |

| 2.20 | Avg. packet latency                         | 33   |

| 2.21 | Avg. standard deviation                     | 34   |

| 2.22 | Power/router comparisons                    | 35   |

| Figu | Ire I                                                            | Page |

|------|------------------------------------------------------------------|------|

| 2.23 | Latency/std. dev. comparisons                                    | 36   |

| 2.24 | Power/Routers versus Port Arity                                  | 37   |

|      | Power Consumption with Increasing Bandwidth                      | 38   |

| 2.26 | Required Routers with Increasing Bandwidth                       | 39   |

| 2.27 | Reduction in latency and standard deviation                      | 40   |

| 2.28 | Normalized Power and Routers with Increasing Transaction Overlap | 41   |

| 2.29 | Average Packet Latency with Increasing Transaction Overlap       | 42   |

| 2.30 | Average Standard Deviation with Increasing Transaction Overlap   | 43   |

| 2.31 | Application specification                                        | 44   |

| 2.32 | ILP solution                                                     | 45   |

| 2.33 | Our solution                                                     | 45   |

| 3.1  | Generic MPSoC architecture                                       | 48   |

| 3.2  | System-level design flow                                         | 49   |

| 3.3  | Architecture of MPSoC sub-system                                 | 50   |

| 3.4  | Top-level view of memory synthesis                               | 55   |

| 3.5  | Data memory minimization pseudo-code                             | 58   |

| 3.6  | Clique partitioning pseudo-code                                  | 59   |

| 3.7  | Code memory minimization pseudo-code                             | 61   |

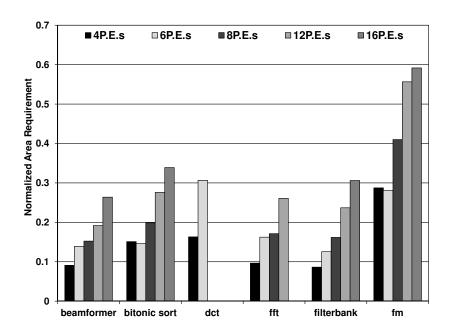

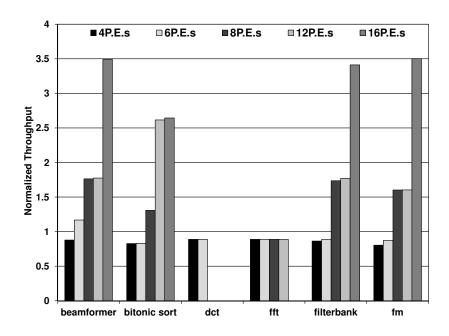

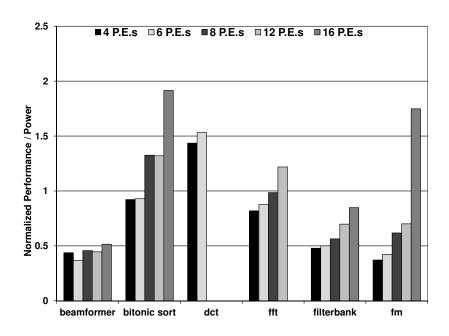

| 3.8  | Normalized area                                                  | 64   |

| 3.9  | Normalized throughput                                            | 65   |

| 3.10 | Normalized Perf./Watt                                            | 66   |

| 3.11 | Impact of code overlay                                           | 67   |

| 3.12 | Existing approach                                                | 68   |

| 3.13 | Area impact                                                      | 69   |

| Figu | re                                               | Page |

|------|--------------------------------------------------|------|

| 4.1  | Generic MPSoC architecture                       | . 72 |

| 4.2  | System-level design flow                         |      |

| 4.3  | Architecture of MPSoC sub-system                 |      |

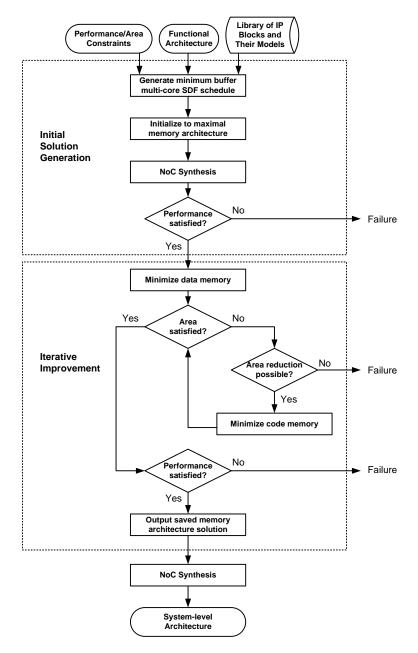

| 4.4  | Functional Architecture Synthesis Flowchart      |      |

| 4.5  | Example SDF Specification                        |      |

| 4.6  | Data Memory Minimization Pseudo-code             |      |

| 4.7  | Example Data Lifetimes                           |      |

| 4.8  | Data Overlay Schedule                            |      |

| 4.9  | Code Memory Minimization Pseudo-code             | . 87 |

| 4.10 | Example SDF Specification                        |      |

| 4.11 | Least Switching Schedule                         | . 88 |

| 4.12 | Hardware Accelerator Replication Pseudo-code     | . 88 |

| 4.13 | Iterative Transition to HW-SW Design Pseudo-code | 90   |

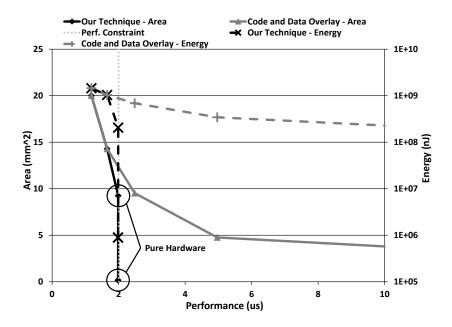

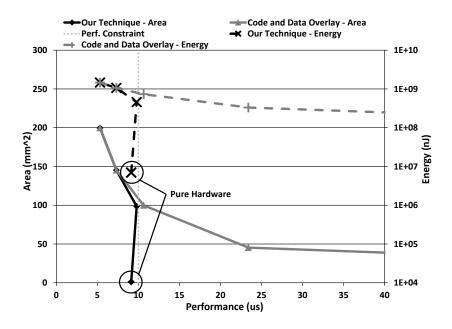

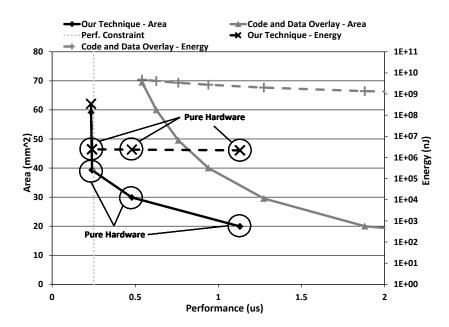

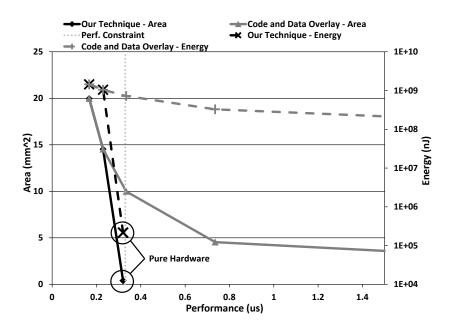

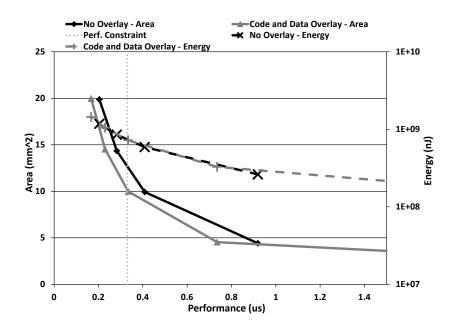

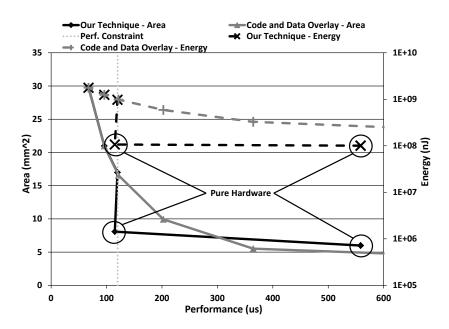

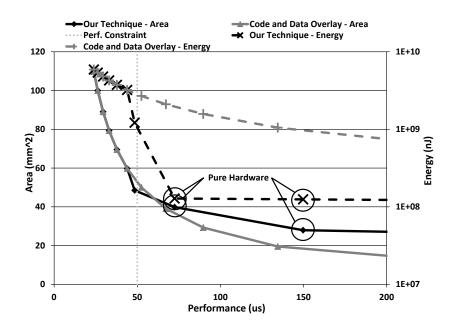

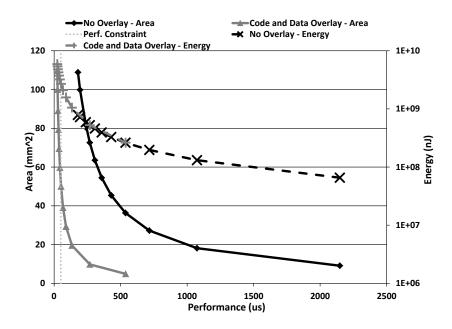

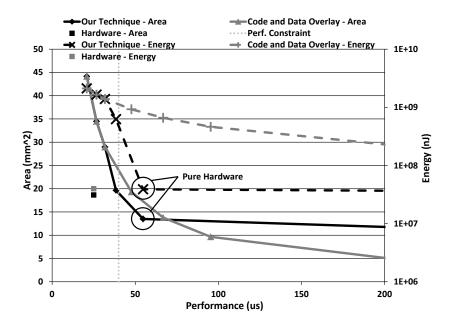

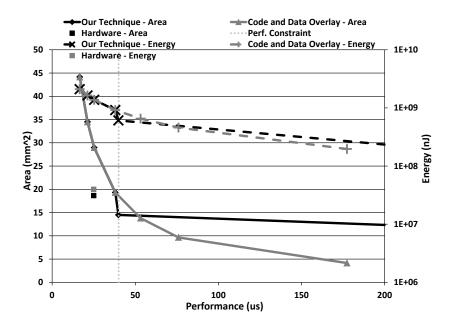

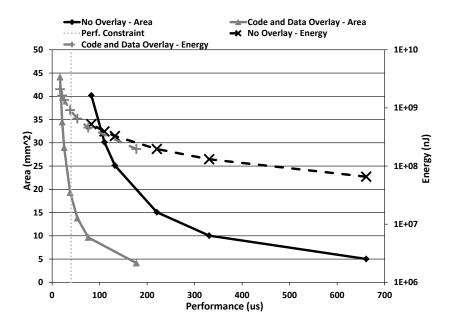

| 4.14 | DCT Area vs. Perf. vs. Energy (sb)               | . 96 |

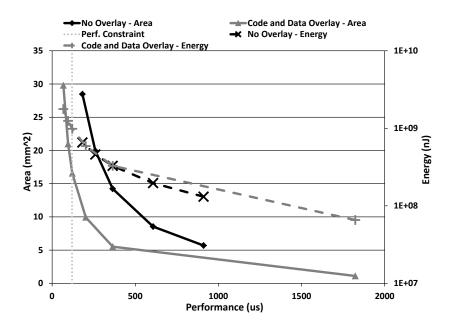

| 4.15 | DCT Area vs. Perf. vs. Energy (sb)               | 97   |

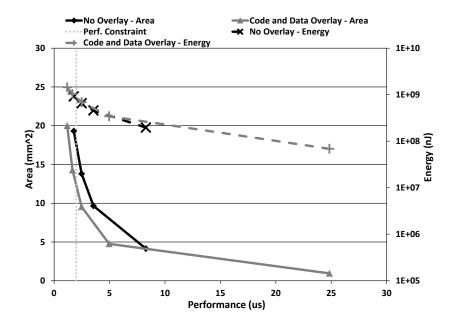

| 4.16 | DCT Area vs. Perf. vs. Energy (ls)               | . 98 |

| 4.17 | DCT Area vs. Perf. vs. Energy (ls)               | 99   |

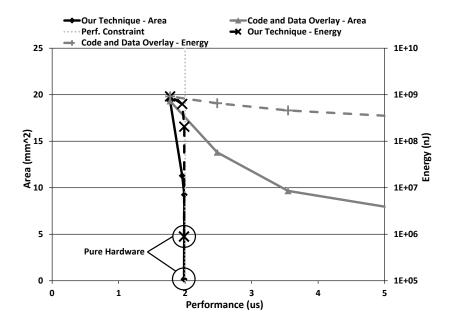

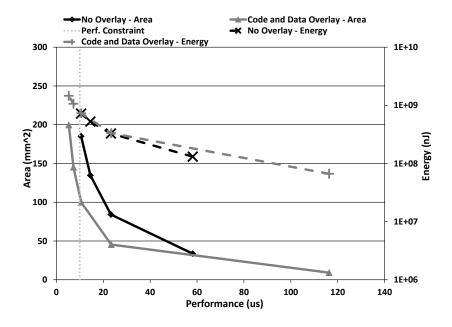

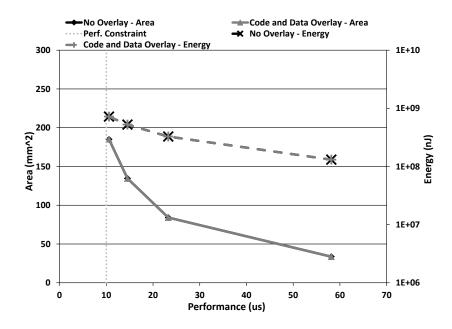

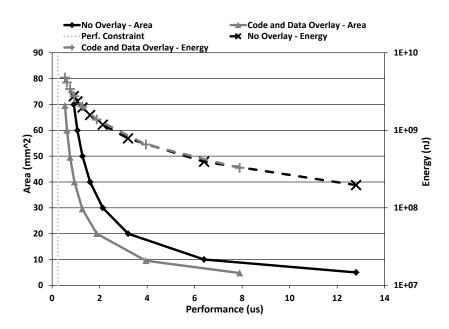

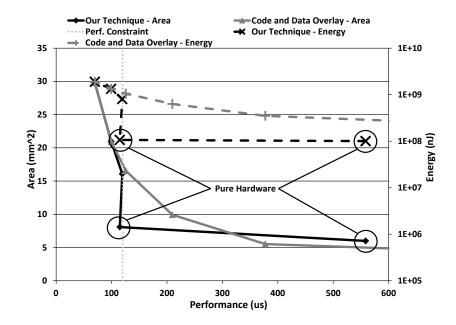

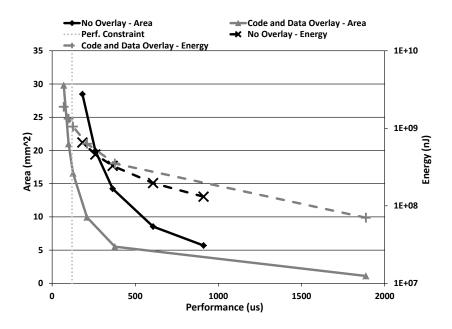

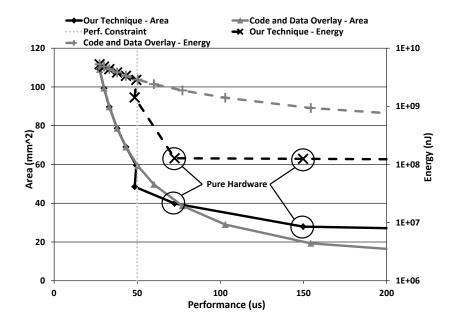

|      | FFT Area vs. Perf. vs. Energy (sb)               |      |

|      | FFT Area vs. Perf. vs. Energy (sb)               |      |

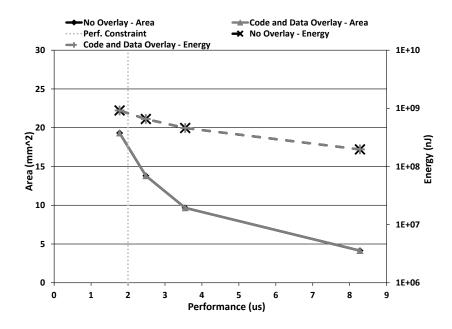

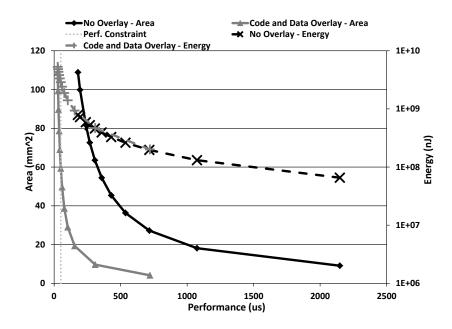

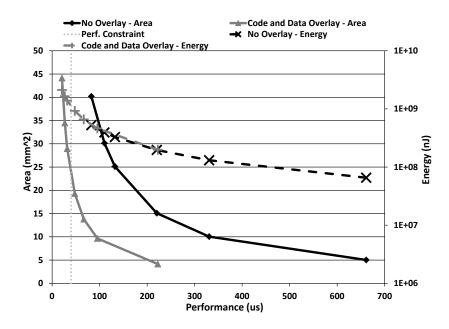

| 4.20 | FFT Area vs. Perf. vs. Energy (ls)               | 102  |

| 4.21 | FFT Area vs. Perf. vs. Energy (ls)               | 103  |

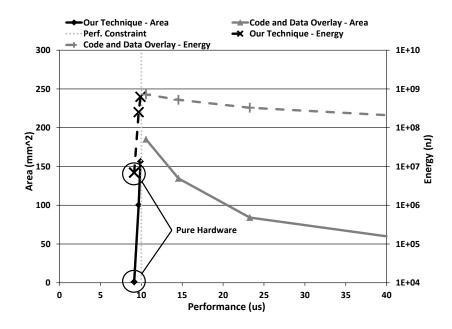

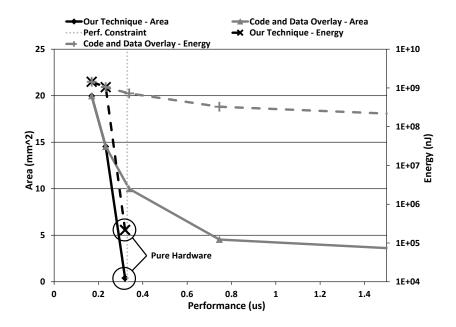

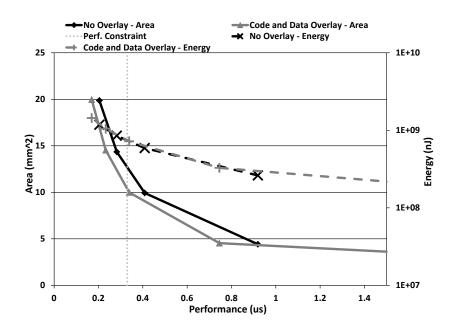

| 4.22 | DCT Overlay Impact (sb)                          | 104  |

| 4.23 | DCT Overlay Impact (ls)                          | 105  |

| 4.24 | beamformer Area vs. Perf. vs. Energy (sb)        | 108  |

| Figure                                             | Page |

|----------------------------------------------------|------|

| 4.25 beamformer Area vs. Perf. vs. Energy (sb)     | 109  |

| 4.26 beamformer Area vs. Perf. vs. Energy (ls)     | 110  |

| 4.27 beamformer Area vs. Perf. vs. Energy (ls)     | 111  |

| 4.28 bitonic-sort Area vs. Perf. vs. Energy (sb)   | 112  |

| 4.29 bitonic-sort Area vs. Perf. vs. Energy (sb)   | 113  |

| 4.30 bitonic-sort Area vs. Perf. vs. Energy (ls)   | 114  |

| 4.31 bitonic-sort Area vs. Perf. vs. Energy (ls)   | 115  |

| 4.32 channelvocoder Area vs. Perf. vs. Energy (sb) | 116  |

| 4.33 channelvocoder Area vs. Perf. vs. Energy (sb) | 117  |

| 4.34 channelvocoder Area vs. Perf. vs. Energy (ls) | 118  |

| 4.35 channelvocoder Area vs. Perf. vs. Energy (ls) | 119  |

| 4.36 filterbank Area vs. Perf. vs. Energy (sb)     | 120  |

| 4.37 filterbank Area vs. Perf. vs. Energy (sb)     | 121  |

| 4.38 filterbank Area vs. Perf. vs. Energy (ls)     | 122  |

| 4.39 filterbank Area vs. Perf. vs. Energy (ls)     | 123  |

| 4.40 fm Area vs. Perf. vs. Energy (sb)             | 124  |

| 4.41 fm Area vs. Perf. vs. Energy (sb)             | 125  |

| 4.42 fm Area vs. Perf. vs. Energy (ls)             | 126  |

| 4.43 fm Area vs. Perf. vs. Energy (ls)             | 127  |

### Chapter 1

#### INTRODUCTION

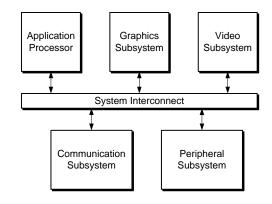

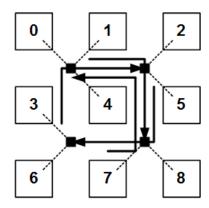

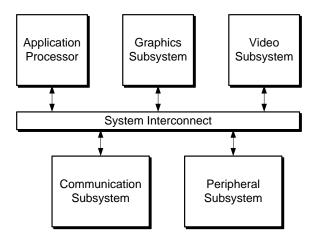

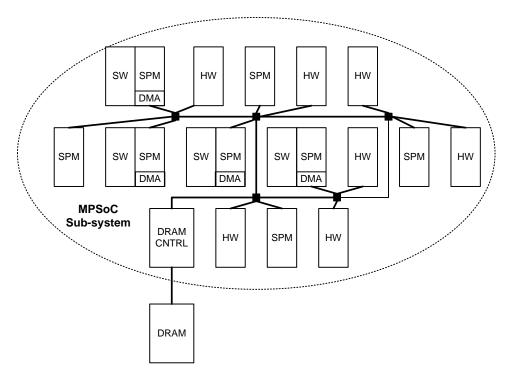

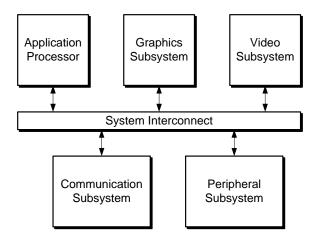

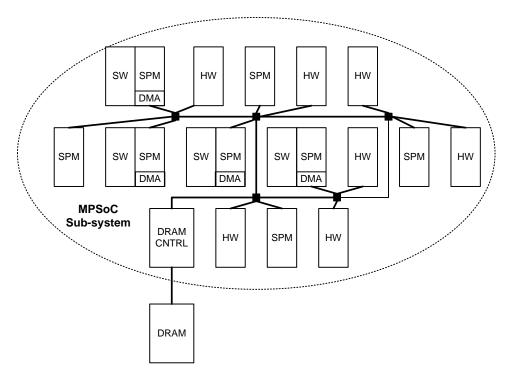

In recent years, multi-processor system-on-chips (MPSoCs) have emerged as the architecture of choice in embedded devices (such as cell phones, GPS devices, luxury car features, etc.) to address the complex applications desired by the end user customer. These MPSoCs incorporate a constellation of heterogeneous processing elements (PEs) (general purpose PEs and application-specific integrated circuits (ASICS)). As an example, Figure 1.1 depicts the top-level view of a generic architecture for a MPSoC. The application processor is a general purpose processor such as an ARM Cortex-A9 that supports a cache coherent memory hierarchy. The other application sub-systems are composed of highly optimized instruction processors, graphics/DSP processor, and custom hardware accelerators. Typically, the non-application sub-systems do not support a cache hierarchy and instead utilize scratchpad memories. The overall architecture is an integration of the various sub-systems through a high bandwidth system-level interconnect (such as an Network-on-Chip (NoC)).

The shift from single processor designs to MPSoCs has been fueled by three major factors: demand for high performance, the use of component libraries, and short design turn around time. As customers continue to desire more and more complex applications on their embedded devices the performance demand for these devices continues to increase. This increasing performance demand has become difficult for single core architectures to meet. Whereas, an MPSoC architecture is well suited to meet the performance

Figure 1.1: Generic MPSoC Architecture

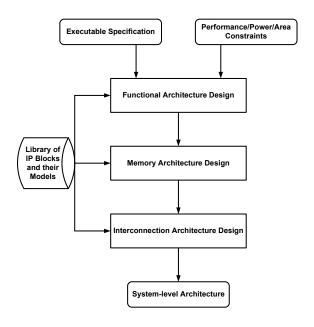

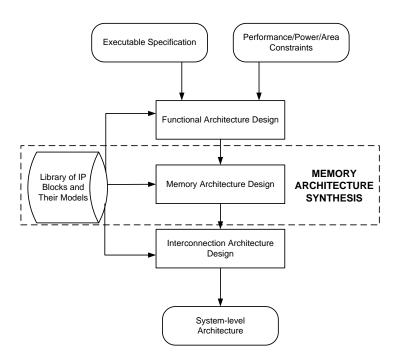

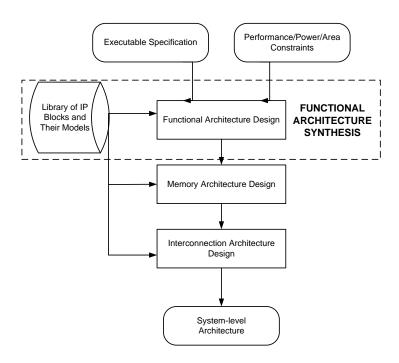

Figure 1.2: System-Level Synthesis Flow

demand through the use of several high-performance sub-systems and concurrent on-chip communication.

The second factor leading to the shift to MPSoCs is the re-use of IP blocks by device designers. Designing new IP blocks takes a lot of time and money. With a single processor design this would be required far more often than with a MPSoC architecture. With a MPSoC approach, designers maintain a library of their available IP blocks. Designers then pick and choose from the IP blocks in order to build the sub-systems for new devices and to meet the performance demand. This therefore, reduces the frequency of the development of new IP.

The final factor leading to the shift towards MPSoCs is the short turn around time on embedded devices. This short turn around time is the direct result of the competitive environment of the industry. Each member in the industry is striving to maintain their edge over their competition. In order to achieve this, and meet consumer demands, companies are required to produce new higher performing devices at rapid rates. Due to designers using libraries of IP blocks and MPSoC architectures, they are able to build new devices with very quick turn around times.

Figure 1.2 illustrates the major stages in the system-level MPSoC design flow. The inputs to the design flow are an executable specification), a set of constraints (performance, power, and area), and a library of characterized IP blocks (performance, power, and area models). The design flow of the system architecture consists of three major stages: functional design, memory design, and interconnection design. During the functional architecture design stage the required processing elements (PEs) are selected and the functionality is mapped to these PEs. During the memory architecture design stage the number and configuration (size, number of ports, etc.) of the various mem-

ory elements are selected. And lastly, during the interconnection architecture design stage the underlying topology for the interconnect is specified.

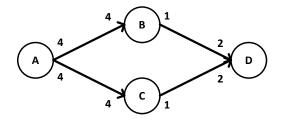

Typically several sub-systems of a MPSoC (graphics, multimedia, communication, etc.) exhibit classic streaming behavior. Therefore, it is a natural choice to describe these sub-systems by utilizing stream programming formats. For the purpose of this work we assume that the functionality of the applications are described by a synchronous dataflow (SDF) specification [22]. A typical SDF specification will be represented through a graph consisting of nodes and arcs. Each node represents an actor and each arc represents the passing of data between actors through tokens. Each actor represents a section of the applications functionality (typically one or more filters within a streaming application). Each token in the graph represents a block of data. Each arc will be annotated with the number of tokens produced by the actor at the head of the arc and the number of tokens consumed by the actor at the tail of the arc.

As the complexity and performance demands of the applications on embedded devices continues to increase, it is becoming more difficult for designers to meet the imposed constraints within the short design turn around time with a manual design approach. In order to help with the design of the MPSoCs, designers have began to explore the automation of the process. The focus of this dissertation is on the automation of the complete system-level MPSoC design flow.

#### 1.1 Contributions

The contributions of this dissertation are summarized as follows:

- 1. We present a novel technique for the synthesis of application specific Network-on-Chip (NoC) interconnect architectures (Chapter 2). The technique includes several design requirements: mixed communication traffic (cumulative/transactional), port arity constraints, deadlock avoidance, and multiple use-cases. The technique generates superior architectures than other existing techniques in terms of power consumption, area, and latency.

- 2. We present a novel technique for the synthesis of the memory architecture for a MPSoC sub-system for a given SDF specification (Chapter 3). The technique makes smart decisions to reduce both the code and data memory area with minimal performance degradation. The technique generates superior memory architectures than other existing techniques in terms of performance, area, and energy consumption.

- 3. We present a novel technique for the co-synthesis of the functional and memory architectures for a MPSoC sub-system for a given SDF specification (Chapter 4). The technique generates HW-SW designs that provide a desirable balance between the flexibility of software and the performance of hardware. The technique also simultaneously generates a memory architecture for the sub-system that makes smart decisions to reduce code and data memory area. The technique is shown to generate highly optimized and efficient designs in terms of performance, area, and energy consumption.

### Chapter 2

#### THE SYNTHESIS OF THE NETWORK-ON-CHIP ARCHITECTURE

Application specific Network-on-Chip (NoC) architectures have emerged as a leading technology to address the communication woes of multi-processor System-on-Chip architectures. Synthesis approaches for custom NoC must address several requirements including cumulative bandwidth and transaction level (TL) communication requirements, multiple application use-cases, deadlock avoidance, and router port bandwidth and arity constraints. In this chapter we present a holistic algorithm for NoC synthesis which is able to address all these requirements together in an integrated manner. The approach is able to generate designs that consume minimum dynamic power consumption, and at most twice the number of routers (and leakage power) as an optimal solution. In terms of performance the technique is able to generate NoC designs with very low average communication latencies (verified by actual simulations) and equally low standard deviation (jitter) while utilizing simple best effort routers. We evaluated the effectiveness and quality of the proposed technique by comparisons with two existing approaches. Extensive experimental results are presented for synthetic/realistic multiple use case applications, cumulative/transaction traffic requirements, increasing application bandwidth requirements, and different port arity constraints.

In the next section we motivate the problem. Section 2.2 formally formulates the problem definition. We discuss related work in Section 2.3. We present the synthesis technique in Section 2.4. In Section 2.5 we present our experimental results. Lastly, we summarize the chapter in Section 2.6.

### 2.1 Motivation

Network-on-Chip (NoC) has been emerging as the solution of choice to address the challenge of designing the interconnection architecture for such hundred core MPSoCs. MPSoC implement a heterogeneous computation platform (consisting of programmable processors, application specific integrated circuits, re-configurable fabric) where each core supports a limited set of application domain functionality. For such designs, custom NoC architectures with optimized topologies have been shown to be superior to regular topologies (such as mesh or tori) in terms of power consumption and required NoC router resources. This work addresses the problem of synthesizing custom NoC architectures with the following considerations:

- Communication requirements: The communication requirements between the cores are typically specified by cumulative bandwidth (such as 10 Mbps). However, many MPSoC aimed at embedded domains implement streaming applications which demonstrate regular periodic transactions between the cores. Such communication patterns can be specified by transaction level (TL) specifications (described in the following section).

- Multiple use cases: In a current day high performance MPSoC only a subset of applications is active at any given time. The NoC synthesis approach should be able to effectively exploit the use case information to generate a topology that maximizes the resource sharing between the various use cases.

- IP library constraints: The NoC router and network to core interface library places constraints in terms of supported traffic classes, bandwidth constraints on ports, and arity constraints on routers.

- Deadlock avoidance: A key requirement of the synthesized NoC topology and routing scheme is that it must not result in deadlocks.

- Quality of results: The NoC synthesis approach must be able to effectively overcome the design complexity while generating solutions with guaranteed quality.

This chapter presents a holistic synthesis approach that is able to effectively address the above design requirements (communication, multiple use-cases and deadlock avoidance) and library constraints. Further, the approach is able to generate topologies with shortest path routes (demonstrating minimal latencies) and requiring minimum (optimum) dynamic power consumption, while consuming at most twice the number of router resources (and leakage power consumption) as the optimal solution.

### 2.2 Problem description

The inputs to the NoC design stage include the communication requirements of the cores in the MPSoC, the multiple use cases, floorplan information of the MPSoC computation architecture, and a library of (performance/power) characterized NoC IP blocks (routers and network interfaces).

The communication requirements for a MPSoC can be specified by graph G(V, E) where  $v \in V$  is the set of cores in the MPSoC and the set of directed edges  $e(u, v) \in E$  denotes the communication requirements between

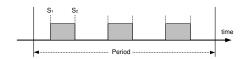

Figure 2.1: Transaction level specification

cores u and v. The edge e is either annotated with cumulative bandwidth requirement  $\omega(e)$  (for example  $\omega(e) = 10$  Mbps) between the cores or TL requirement  $\lambda(e)$ . The TL requirements are specified by  $\lambda(e) = (p, L)$  where p is the period of the transaction specification and L is the list of transactions. Each transaction  $l \in L$  is specified by a time range  $l = [s_1, s_2]$  that denotes the potential start times for the transaction relative to the period. Figure 2.1 depicts the TL specification for an edge. Data dependent application behavior may cause the start time of the transaction to vary from one period to another and therefore we specify it as a range. Without loss of generality the size of all transactions (bit width and flit length) are assumed to be equal. The multiple use cases can be specified by a graph  $G(V, E_1, E_2, ...E_n)$  where each set of edges  $E_i$  denotes the communication requirements for a particular use case.

We consider a simple NoC router architecture that only supports best effort traffic. The router components in the NoC library are characterized by the number of ports  $(\eta)$  and leakage power consumption, maximum arity or number of ports for any router in the library  $(\eta_{max})$ , maximum bandwidth supported on any one port  $(\Omega)$ , and the power consumed per unit bandwidth  $(\psi_r)$  to pass communication traffic through the router. The physical links are characterized by the power consumed per unit bandwidth of communication per unit length of the link  $(\psi_l)$ . The objective of the NoC synthesis technique is to generate an optimized topology with shortest path routes (consequently minimum dynamic power consumption) for each edge such that the communication latency is minimized. In addition to latency and dynamic power minimization, router resource reduction and thus leakage power minimization are also desirable objectives which are considered as secondary goals.

#### 2.3 Related Work

Benini et al. [1] gives an excellent survey of the existing techniques for synthesizing custom NoC architectures. Existing approaches [2][7][8][3] only consider cumulative bandwidth requirements. Our approach is also able to consider transaction level specifications and exploit them for synthesizing NoC designs with low communication latency and jitter while using only best effort routers. Hansson et al. [4] and Murali et al. [5][6] proposed heuristic approaches for NoC synthesis with multiple application use cases. The communication requirements are specified by cumulative bandwidth requirements. The proposed approach that is based on an extension of Chatha et al. [2] approximation algorithm is able to synthesize NoC architectures for multiple use case while giving guarantees on quality bound. Further, the technique is also able to address both cumulative bandwidth and transaction level communication requirements for multiple use cases. Further, existing techniques [2][4] avoid deadlocks by including a post-synthesis step that introduces virtual channels at specific routers. While this approach is effective it does result in router IP modification which may not be desirable under all circumstances. This chapter presents an approach that is able to synthesize NoCs which do not contain deadlocks. Finally, in contrast to existing techniques, the proposed approach is able to address several NoC design requirements (cumulative bandwidth, transaction level specifications, multiple use cases, deadlock avoidance, router arity) in a holistic manner and give guarantees on design quality.

The proposed approach is based on a technique by Chatha et al. [2]. Their approach does not consider transaction level specifications, multiple use cases, bandwidth and port arity constraints, and deadlock avoidance. The bandwidth constraints and deadlock avoidance are addressed in a post NoC synthesis step in their approach. They are unable to incorporate port arity constraints in their basic approach (at least one variable greater than 0.5 no longer holds) and present an alternative strategy. Our approach is able to address all the shortcomings of Chatha et al. while utilizing their technique at the basic level. Thus, we are able to give near same quality guarantees as Chatha et al. while incorporating several additional requirements.

### 2.4 NoC Synthesis Technique

### 2.4.1 Design flow

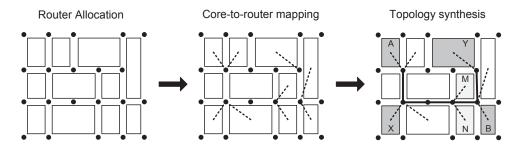

We adapt the overall design flow proposed by Chatha et al. [2] for custom NoC synthesis (see Figure 2.2). The design flow begins by allocating routers at the corners of the channel intersection graph (CIG) of the MPSoC floorplan. The next step in the design flow is the core to router mapping stage. Chatha et al. [2] assumes that the cores are attached to one of the four routers located at its corner. They present an optimal approach (in terms of estimated dynamic power consumption and communication latency) for mapping the cores to the routers. We utilize their optimal core to router mapping algorithm. Figure 2.2

Figure 2.2: Overall design flow

depicts core to router mapping by dotted lines from the center of the core to the neighboring router. The final step in the NoC design flow adds the physical links between the various routers to construct the NoC topology and routes the communication transactions over the topology. The objective of the topology and router synthesis stage is to route each trace by minimum dynamic power consumption (thus also minimum latency) while utilizing minimum router resources (thus also leakage power consumption).

### 2.4.2 Basic approach to topology synthesis

Consider the topology synthesis stage shown in Figure 2.2. In the example we consider two communication traces between cores (A, B) and (X, Y), respectively. There are at least two potential shortest paths available for routing the traces. One which utilizes the routers on the top half and the other which utilizes the routers in the lower half of the layout. The synthesized topology utilizes the paths on the lower half of the layout as it requires fewer additional routers (note that the router connected to cores M and N is required to be in the NoC topology). Chatha et al. [2] present a polynomial time NoC synthesis algorithm that is able to route each trace by shortest path routes (optimum dynamic power consumption) while consuming at most twice the router resources as the optimal solution.

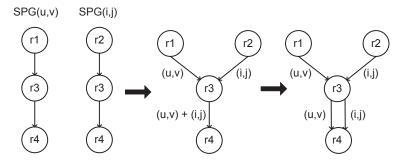

Figure 2.3: Shortest path graphs

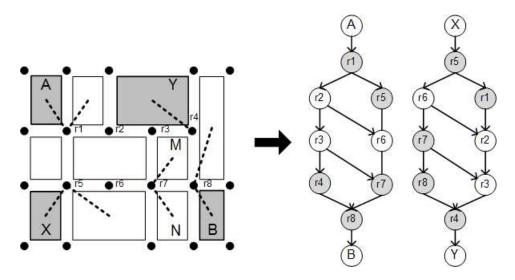

Their approach relies on construction of shortest path graphs (SPG) as shown in Figure 2.3. The two graphs on the right show the SPG for cores (A, B) and (X, Y). The edges (r2, r6) and (r3, r7) denote alternative shortest paths created by over the cell routing of physical links. In the graph the routers that must be utilized (as cores are attached to them) in the synthesized NoC are shaded. Notice that the SPGs of the two cores share routers amongst them. Their technique minimizes the number of routers in the NoC subject to the constraint that a route exists from source to destination for each SPG. As the routes are selected from SPG they are all shortest path routes which minimize dynamic power consumption and communication latency.

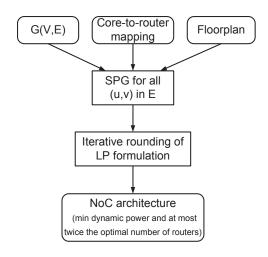

The existing approach generates a SPG for every (u, v) in E. Essentially, the technique considers all possible shortest path routes for every communication requirement and generates a NoC design. It synthesizes a solution by utilizing a LP rounding based approach (see Figure 2.4). They prove that in each iteration the LP solution has at least one variable (that denotes a router

Figure 2.4: NoC Topology Synthesis

is utilized in the NoC) above a 0.5 which is then rounded to 1. They also prove that such a rounding strategy generates a solution where the number of routers utilized in the NoC are at most twice the optimal. Thus, their approach converges to a solution in polynomial time with the above mentioned quality guarantees.

In the following sections we present extensions to SPG construction that can accommodate several NoC design requirements. Thus, we are able to give the same quality guarantees (shortest paths, minimum dynamic power, at most twice the optimal number of routers) on the solution as Chatha et al.

### 2.4.3 Deadlock avoidance

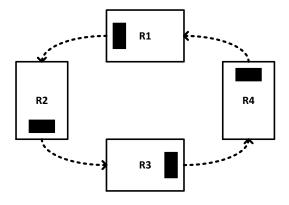

A deadlock is when no packets can progress further through the network or portion of the network. A deadlock is caused by routers forming a cycle and waiting on the resources of the next router in a cycle. This type of deadlock is typically referred to as a circular wait. Figure 2.5 illustrates an example of a deadlock. In the figure, the register(s) of each router are occupied with

Figure 2.5: Example of a Deadlock

Figure 2.6: Deadlock Example - SPGs

contents attempting to be routed to the next router in the cycle. Since, the register(s) are filled no packets are able to transfer. Therefore, a deadlock has occurred.

Potential deadlocks can occur in the synthesized NoC if there are cycles in the channel dependency graph [9]. A channel dependency graph (CDG) can be obtained by transformation from the synthesized NoC. In the CDG the physical links of the NoC are denoted by nodes, and a directed edge between

Figure 2.7: Deadlock Example - Global SPG

two nodes  $(u, v) \in CDG$  denotes that a communication requirement is routed from node u to v (both u and v represent physical links in the NoC). Deadlocks in a NoC can be alleviated by introduction of additional virtual channels (or buffers) in the routers, and breaking the cycles [9]. However, such an approach does lead to modification of the routers. An alternative strategy that is presented here would be to generate a NoC that does not have cycles in its CDG.

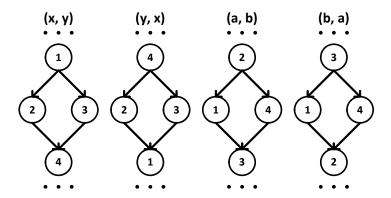

The approach is based on the modification of the SPGs. We first find the shortest path graphs (SPGs) for each communication trace in the design. A SPG represents all of the shortest routes (# of routers) for a communication trace. As an example, Figure 2.6 illustrates four communication traces and their corresponding SPGs. After each of the individual shortest path graphs have been found, all of the SPGs are combined into a globel shortest path

Figure 2.8: Deadlock Example - Global CDG

graph  $(SPG_G)$ . The global shortest path for our example is illustrated in Figure 2.7. Each edge in the  $SPG_G$  is annotated with the traces that are routed along the edges.

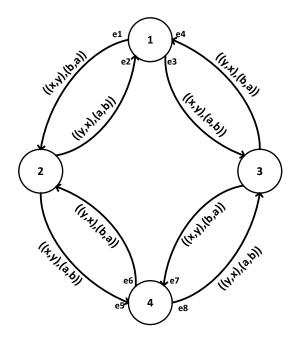

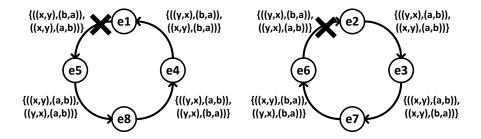

After the  $SPG_G$  is generated the graph is transformed into a  $CDG_G$ . A  $CDG_G$  is a global Channel Dependency Graph (CDG). In the  $CDG_G$  a vertex represents an edge in the  $SPG_G$ . An edge  $(e_1, e_2) \in CDG_G$  if and only if a path is present in the  $SPG_G$  that contains edges  $e_1$  and  $e_2$ . Figure 2.8 illustrates the  $CDG_G$  for the  $SPG_G$ . Each edge in the figure is annotated with the traces that have paths through the edges. After the  $CDG_G$  is generated we find all of the strongly connected components (SCCs). In a SCC there is a path from each node to every other node in the SCC. Therefore, a SCC in the  $CDG_G$  represents a potential cycle in the network and thus a potential deadlock. By removing an edge(s) from the SCCs we will break all possible cycles and therefore ensure that no deadlocks are possible. In the  $CDG_G$  in Figure 2.8, there are two SCCs as easily seen in the figure. If we remove an edge from each of the SCCs we will break the cycles. For instance, assume we eliminate the edge between nodes  $e_1$  and  $e_5$  and the edge between nodes  $e_2$  and  $e_6$ . After the edges have been removed the changes are reflected back into the individual SPGs.

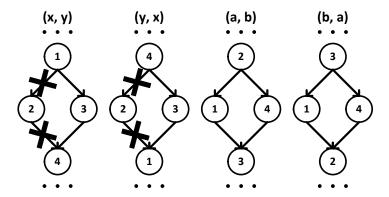

Figure 2.9: Deadlock Example - Updated SPGs

Figure 2.9 illustrates how the removal of the edges from the  $CDG_G$  is reflected back onto the SPGs. In the figure, trace (x, y) has had the edges from node 1 to node 2 to node 4 removed. This is from the edge in the  $CDG_G$  from node  $e_1$  to  $e_5$  being eliminated. Addionally, in Figure 2.9 the trace (y, x) has had the edges from node 4 to node 2 to node 1 removed. This is from the edge in the  $CDG_G$  from node  $e_2$  to  $e_6$  being eliminated. With these changes to the SPGs there is no longer any risk of circular wait deadlocks in the final synthesized network.

The pseudo code for modifying SPGs for deadlock avoidance shown in Figure 2.10. The above discussion addressed the problem in the context of a single use case. The same identical steps can be followed for multiple use cases to avoid deadlocks in each of them. The for loop in line 2 iterates through all the use cases. Line 3 and 4 generate the  $SPG_G$  and  $CDG_G$  structures, respectively. Line 5 finds all the SCC in  $CDG_G$ , and the for loop of Line 6 removes back edges in each of them to eliminate cycles. Finally, Line 10 reflects the changes on the individual SPGs by removing appropriate edges.

```

\begin{tabular}{ll} deadlock\_avoidance() \\ for each use-case $UC$ do \\ generate\_global\_SPG() \\ convert\_SPG\_to\_CDG() \\ find\_SCCs() \\ for each $SCC$ do \\ find\_back\_edges() \\ remove\_back\_edges() \\ end for \\ update\_SPGs() \\ end for \\ \end for \\

```

Figure 2.10: Pseudocode for deadlock avoidance

The complexity of  $deadlock\_avoidance()$  is dominated by Line 3 that generates  $SPG_G$ . Let U denote the number of use cases in the application, and let R denote the number of routers allocated to the floorplan. We utilize Dijkstra's shortest path algorithm to generate the SPG for a single trace which has a complexity of  $O(R^2)$ .  $SPG_G$  construction in Line 3 has a complexity of  $O(TR^2)$  where T denotes the maximum number of traces over all use cases of the application. The overall complexity of Line 3 is  $O(UTR^2)$  when the for loop of Line 2 is taken into account.

#### 2.4.4 Communication requirements

Cumulative bandwidth requirements: We first consider cumulative bandwidth requirements and then discuss transaction level specifications. The basic SPG construction (as described in Chatha et al.) assumes that when routes are shared between two communication traces (in order to minimize router resources) there is no violation of port bandwidth constraints. However, violations could exist and we address them by splitting the traces across differ-

Figure 2.11: Bandwidth violation

ent router ports. Figure 2.11 depicts partial SPGs of two traces (u, v) and (i, j) that could potentially be routed through routers r3 and r4. However,  $\omega(u, v) + \omega(i, j) > \Omega$ . We avoid the bandwidth violation by routing (u, v) and (i, j) on different ports of r3 and r4 as shown in the figure. Thus, if router r3 and r4 were to be utilized for routing (u, v) and (i, j) in the final design, they would be routed on different ports of r3 and r4. We incorporate this information in the SPG by annotating it on router r3.

Transaction level specifications: Inclusion of transaction level specifications in the communication requirements gives us an opportunity to avoid conflicts or interference between the various transactions. We capture transaction interference by first traversing each transaction from source router (connected to the initiating core) to the sink router (connected to the target core) along each shortest path. As the transaction traverses a router the range of its start time is delayed by the router switching delay. Thus, we know the range of start times of each transaction at every router along all its shortest paths.

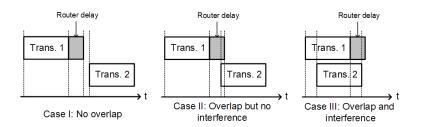

We consider three cases for interference between two transactions that wish to access the same output port of a router (see Figure 2.12). The rectangles for transactions 1 and 2 denote the range of their start times. The shaded

Figure 2.12: Transaction interference

box represents the minimum transmission delay for a transaction through a router. In Case I transactions 1 and 2 do not interfere with each other as there is no overlap between their ranges of start times. In Case II if transaction 1 starts at its latest possible time, and transaction 2 starts at it earliest possible time, then the two transactions overlap as transaction 1 is being switched through the network. However, we permit such overlaps to happen. Finally, in Case III if transaction 1 starts at its latest possible time, transaction 2 could delay transaction 1 if it starts earlier. We treat the latest start time of the transaction plus the router switching delay as the deadline for the transaction. Hence, Case III could potentially cause a deadline violation on transaction 1, and we avoid such scenarios.

We avoid interference between two transactions (Case III) by adopting a similar approach as that for bandwidth violation. The two transactions are assigned to two different ports that are connected with the same neighboring router. Thus, both the transactions can traverse to the same neighboring router without interfering with each other.

Cumulative and transaction specifications: Finally, we also avoid conflicts between communication requirements that are specified by cumulative bandwidth and those that are specified by transaction specifications. We do permit

```

1: trace conflict resolution()

2: for each router R do

for each use-case UC do

3:

for each trace T1 placed on router R do

4:

for each trace T2 placed on router R do

5:

if T1 \neq T2 then

6:

7:

if conflicts exist(T1, T2) then

resolve conflict(R, T1, T2)

8:

end if

9:

end if

10:

end for

11:

end for

12:

end for

13:

14: end for

```

Figure 2.13: Pseudocode for trace conflict resolution

cumulative bandwidth and transaction specifications originating from the same core to share the same route.

The pseudocode for the trace conflict resolution algorithm is shown in Figure 2.13. The algorithm iterates through each router, R, in the topology (line 2) for each use case, UC (line 3). The algorithm then compares each trace, T1, on the router R with every other trace, T2, (lines 4-7) also on the router. The two traces are compared to see if they are routed through the same port, and if they are whether a conflict exists (line 7). If a conflict is found between the two traces the conflict is resolved as discussed above (line 8). The complexity of  $trace\_conflict\_resolution()$  algorithm is determined by the for loops of Lines 2, 3, 4 and 5, and it is  $O(RUT^2)$ .

Figure 2.14: Router arity constraints

The addition of ports to avoid bandwidth violations and transaction interferences can potentially lead to router arity constraint violations whose alleviation is discussed in the next section.

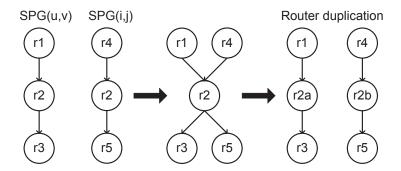

### 2.4.5 Port arity constraints

Figure 2.14 depicts port arity constraint alleviation. The left hand side of the figure shows partial SPGs belonging to communication requirements between cores (u, v) and (i, j). We assume the port arity constraint is 3. If in the final NoC topology both the communication requirements are routed through r2 they would cause a port arity constraint violation. We avoid such a violation by introducing a duplicate router at the same location as r2. Thus, there are now two routers r2a and r2b located very close to each other. The SPGs are modified to utilize r2a for (u, v) and r2b for (i, j).

The pseudocode for router port arity resolution algorithm is shown in Figure 2.15. The algorithm begins by iterating through each router, R, and each use-case, UC (lines 2 and 3). Each router R has its port arity compared with  $MAX\_PORTS$  which denotes the port arity constraint (line 4). If router R has too many ports the algorithm finds the set of routers, Z, connected to

```

1: port_arity_resolution()

2: for each router R do

for each use-case UC do

3:

if port\_arity(R) > MAX\_PORTS then

4:

Z \leftarrow \text{set of routers connected to router } R

5:

T \leftarrow \text{set of traces passing through router } R

6:

for each combination K_i \in C^Z_{MAX\_PORTS} do

7:

S = duplicated\_router(R)

8:

connect routers (S, K_i)

9:

for each trace t in T do

10:

11:

if t has a path through R using routers in K_i then

add \ edges()

12:

13:

end if

end for

14:

end for

15:

16:

remove\_router(R)

end if

17:

18:

end for

19: end for

```

Figure 2.15: Pseudocode for router port arity resolution

router R as well as the set of traces, T, passing through the router (lines 5 and 6). For each combination  $K_i \in C_{MAX\_PORTS}^Z$  of routers from Z, the algorithm creates a new router S by duplicating the router R (lines 7 and 8). Next, the  $K_i$  combination of routers are connected to the new router (line 9). The algorithm then iterates through each trace t in the set of traces T (line 10). If trace t has a path through router R using the routers in  $K_i$ , the algorithm introduces edges between S and appropriate routers in  $K_i$  (lines 11 and 12). After each combination of routers from T have been processed the algorithm removes the initial router T (line 16). The algorithm terminates after each use-case has had all of its routers processed.

The complexity of  $port\_arity\_resolution()$  algorithm is dominated by for loop of Line 7 which has an overall complexity of  $O(TR^{MAX}\_PORTS+2)$ . The overall complexity of the algorithm is  $O(TUR^{MAX}\_PORTS+3)$  or  $O(TUR^8)$  if  $MAX\_PORTS$  is assumed to be equal to 5.

# 2.4.6 Multiple use cases

The basic approach [2] to topology synthesis (Section 2.4.2) creates a set of SPGs (each SPG is associated with one  $(u,v) \in E$ ) from G(V,E). A set of SPGs associated with an edge set E is denoted by SPG(E). We can address multiple use cases by creating multiple sets of distinct sets of  $SPG(E_i)$  associated with each use case  $E_i \in G(V, E_1, \ldots, E_i)$ . The bandwidth and transaction interference constraints imposed by  $E_i$  are only addressed in individual  $SPG(E_i)$ . The bandwidth, transaction interference and deadlock avoidance constraints are only applied on individual  $SPG(E_i)$ . The port arity constraints are imposed on all  $SPG(E_i)$ . All the  $SPG(E_i)$  are then input to the LP rounding based technique. Consequently, the resulting solution has shortest routes for each communication requirement, and minimizes the number of routers across all use cases. Thus, the approach is able to effectively minimize the resource usage across all use cases.

### 2.4.7 Algorithm Time Complexity Analysis

The algorithm time complexity for constructing the SPGs utilized by our approach is dominated by the algorithm,  $port\_arity\_resolution()$ , which is  $O(TUR^8)$  (if  $MAX\_PORTS$  is assumed to be equal to 5). The iterative NoC synthesis step utilizes approach identical to Chatha et al. which is polynomial. Thus, the overall time complexity of can be considered to be  $O(TUR^8)$ .

Table 2.1: Categories of synthetic benchmarks

|                   | Bandwidth specification |             |       |

|-------------------|-------------------------|-------------|-------|

|                   | Cumulative              | Transaction | Mixed |

| Multiple use case | S1                      | S2          | S3    |

### 2.5 Experimental Results

### 2.5.1 Experimentation set-up

Benchmark designs We performed extensive experimentation to evaluate our technique. We considered several categories of synthetic benchmarks and a realistic benchmark application. A description of the various categories of synthetic benchmarks is given in Table 2.1. All the synthetic benchmark categories considered multiple use cases and had 10 designs within each category. The synthetic benchmarks in S1 were generated by randomizing the number of cores (ranging from 10 to 50 cores), number of traces, bandwidth per trace and number of use cases. In the case of benchmarks in category S2, the randomization on bandwidth was replaced by randomization on the period of transactions associated with a trace (instead of bandwidth), number of transactions within the period, amount of data in each transaction, and the start window of the transactions. Finally, synthetic benchmarks in category S3 were generated by an additional randomization on type of a trace (cumulative versus transaction).

Our realistic benchmark modeled a real-world multimedia application comprising of video recording, video playback, and wireless communication. The application consisted of 21 cores broken into memories, processing units, as well as application specific cores. The benchmark consisted of three applications and three use-cases: a use-case with only video playback and wireless

communication, a use-case with video recording and wireless communication, and a use-case with video playback and recording and wireless communication. Each application of the benchmark was given as a transaction level specification.

In our experiments with both synthetic and benchmark traffic we considered a port arity constraint of 5. We also present experimental results that evaluate our approach by varying the port constraints from 3 to 10.

Existing approaches We compared the technique against two existing approaches: an integer linear programming approach (referred to as "ILP" for the remainder of the chapter) by Srinivasan et al. [3] and a heuristic synthesis technique rhat generates NoC with guaranteed throughput router architectures by Hansson et al. [4] (hence forth referred to as "GT"). Both these approaches consider only cumulative bandwidth specifications and do not support transaction level traffic specifications. The ILP synthesizes designs with best effort routers, and therefore is a good representative of many other existing NoC design approaches. Similar to the other approaches ILP also does not consider multiple use cases, port arity constraints, and deadlock avoidance. ILP addresses multiple use cases by generating a NoC architecture for the worst case scenario. The worst case scenario is one in which all the applications are active simultaneously. We compared our approach with ILP for synthetic benchmarks that include cumulative bandwidth traffic (S1 and S3) and the realistic application.

The GT approach heuristically searches for shortest paths to route a trace subject to bandwidth constraints on the intermediate router. The GT approach uses a specialized router architecture that assigns guaranteed bandwidth to each trace flowing through the router. Thus, GT is a good representative of existing NoC synthesis approaches that consider guaranteed throughput traffic. The bandwidth guarantees are achieved by including a table at each port in the router. The base GT approach is able to handle multiple use cases, but does not consider port arity constraints. We extended the base GT approach [4] to account for port arity constraints. We compared our approach with GT for synthetic benchmarks that include transaction level traffic specification (S2 and S3) and the realistic application.

Evaluation metrics We compared against the existing approaches by evaluating the power consumption, router requirements, and performance of the generated designs. The power consumption included both dynamic (due to routers and physical links) and leakage (due to routers) power for the designs. The power consumption numbers were generated through RTL synthesis using a 65nm lower power process. The average packet latency was determined through simulation using a transaction level simulator. The simulations included a warm up period before the performance data was recorded. In the case of designs that included transaction-level traffic information, the transactions were launched uniformly at random within their start time window. The cumulative bandwidth traffic was also generated by launching flits uniformly random within a specified period (reciprocal of bandwidth). The simulations recorded the latency of each transaction along with the number of hops it traversed as it traveled through the network. Thus, we could calculate the average latency and standard deviation for every packet hop distance. In all our charts that compare the average latency of the various approaches we also

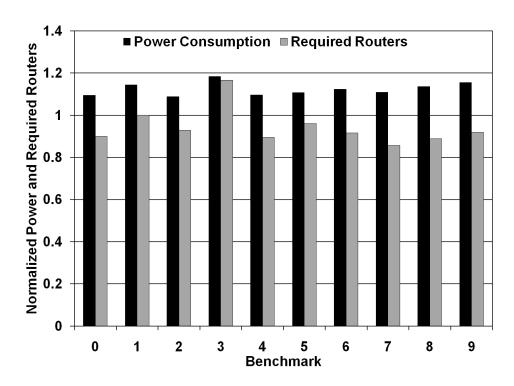

Figure 2.16: Power/Router for ILP

plot the lower bound of the latency. The lower bound is calculated as the minimum latency for a flit to traverse the specified number of hops with no interference from any other trace.

We also performed additional experiments that evaluated the quality of the designs as the bandwidth was increased, port arity constraint was varied (only for our approach), allowable transaction interference was increased (only for our approach), and an application with deadlock possibility was considered.

# 2.5.2 Comparisons with existing approaches

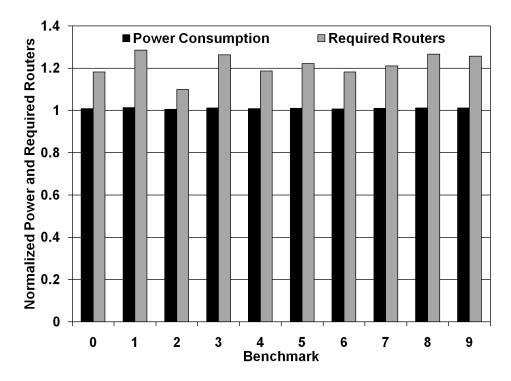

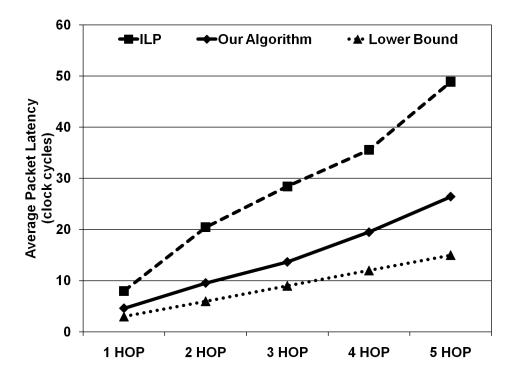

Comparison with ILP for S1 We begin the discussion by presenting results that compare our approach with ILP for the synthetic benchmark category S1. Figure 2.16 plots the normalized power consumption and router require-

Figure 2.17: Avg. packet latency

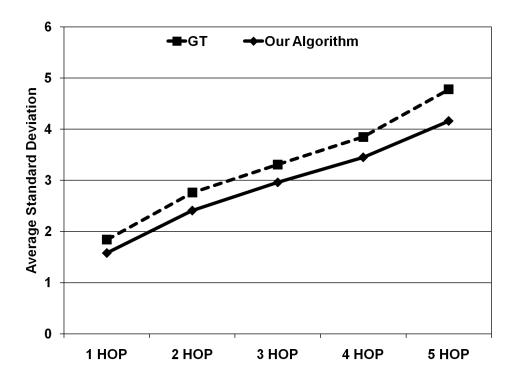

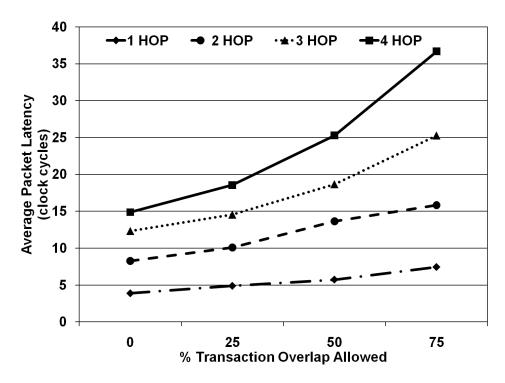

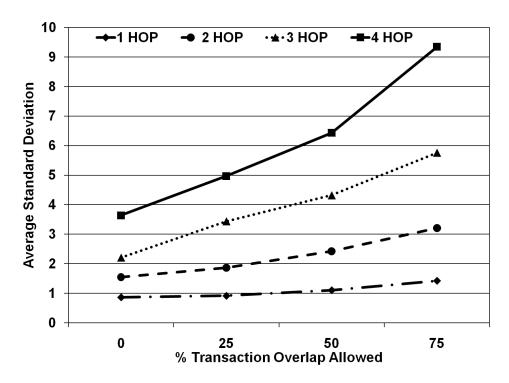

ments for the NoC designs generated by ILP technique with respect to our approach. As can be seen from the plot the power consumption of the designs are comparable while ILP designs require a lot more routers. It is to be expected as the ILP approach does not optimize for multiple use cases and instead generates a NoC design for the worst case scenario. Further, we would also like to point out the ILP approach did not honor port arity constraints in any of the synthesized NoC designs. Figures 2.17 and 2.18 plot the hop wise latency and standard deviation, respectively of the designs generated by ILP and our approach. Figure 2.17 includes a plot for the lower bound on packet latency for each hop assuming no interference. It can be seen from the plots the designs generated by our technique demonstrate much lower packet latencies and standard deviation with respect to the designs synthesized by

Figure 2.18: Avg. standard deviation

ILP. The designs synthesized by ILP do not honor port arity constraints and utilize routers with very large number of ports. Consequently, there is a lot of interference between the various traffic traces that traverse such a large port arity router leading to higher average packet latency and standard deviation.

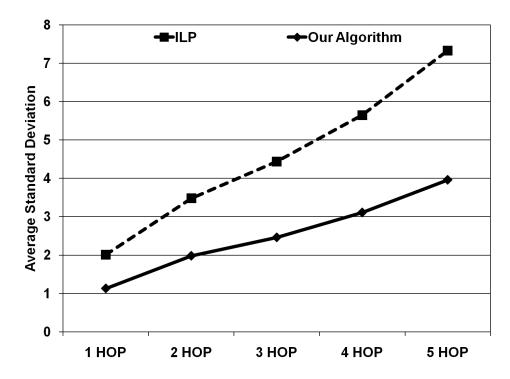

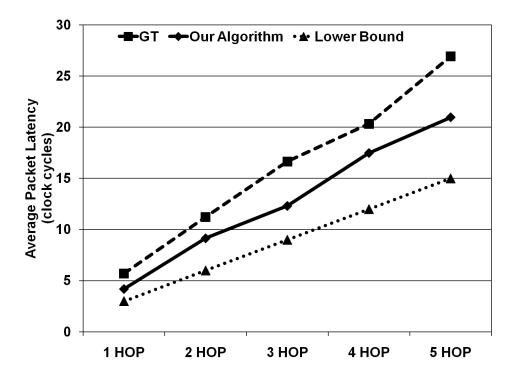

Comparison with GT for S2 We next present experimental results that compare our approach against GT with synthetic benchmarks in category S2. Figure 2.19 plots the normalized power consumption and router requirements for the designs generated by GT in comparison to our approach. It can be observed from the figure that the GT designs utilize higher power in all cases. However, the router resource requirement is lower for the GT approach. The higher power consumption requirement is attributed to the complex router

Figure 2.19: Power/Router for GT

architecture utilized by the GT approach. In contrast our technique utilizes simple best effort routers. The higher router requirement of our approach is due to the transaction conflict avoidance measures taken by our technique. Our approach utilizes more routers in an effort to generate alternative paths in the NoC that lower conflict between various transactions. Figures 2.20 and 2.21 plot the per hop latency and standard deviation, respectively for the designs synthesized by GT and our approach. As can be seen from the figures, our designs demonstrate lower average latency and standard deviation with respect to the GT designs. This is significant as our designs are based on simple best effort routers as opposed to the GT designs that utilize complex guaranteed throughput designs. Therefore, although our technique generates designs that require more routers, the designs demonstrate lower power consumption and superior performance.

Figure 2.20: Avg. packet latency

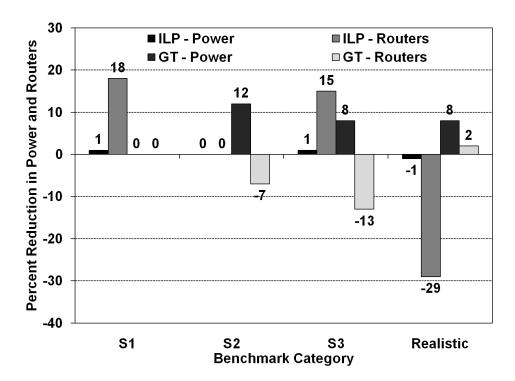

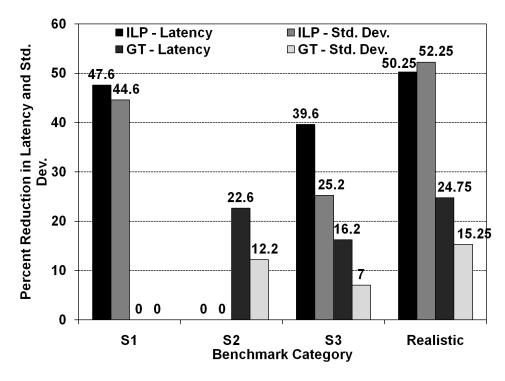

Summary of comparisons with ILP and GT—In this section we summarize the comparisons with ILP and GT approaches for the synthetic benchmarks and the realistic application. Figure 2.22 gives the average percentage reduction in routers and power consumption due to our technique in comparison with both ILP and GT. The X-axis of the plot depicts the improvements for the three synthetic benchmark categories and the realistic application. We compared only against ILP for category S1, and category S2 was used for comparison only with GT. Figure 2.23 gives the average percentage reduction in latency and standard deviation due to our approach. The conclusions of the study are summarized below:

1. Category S1: The ILP generated designs that required comparable power consumption, almost 20% additional routers and that demonstrated about

Figure 2.21: Avg. standard deviation

45% higher average latency and standard deviation. The ILP performed poorly because it does not optimize for multiple use cases, and does not consider port arity constraints.

- 2. Category S2: The GT generated designs that required over 10% additional power consumption, 5% lower router resources and whose average latency and standard deviation were higher by over 20% and 10%, respectively. This result is significant as our technique is able to generate high quality designs while using best effort routers as opposed to GT that utilized higher complexity guaranteed throughput routers.

- 3. Category S3: Synthetic benchmarks in this category modeled applications with both mixed cumulative and transaction traffic specifications.

Designs synthesized by our approach demonstrated superior performance

Figure 2.22: Power/router comparisons

in comparison to the solutions of ILP and GT approaches. The trends in power consumption and router resource requirements observed for the previous two categories are repeated for category S3 for precisely the same reasons.

4. Realistic application: The realistic application consisted of transaction level traffic specifications. Designs generated by ILP do not consider interference avoidance between transactions and therefore require fewer router resources. The fewer router resources also result in lower power consumption of the ILP design because of reduced leakage power consumption. However, the average latency and standard deviation in latency is very large for ILP design. The GT approach generates a design that requires higher power consumption and comparable router

Figure 2.23: Latency/std. dev. comparisons

resources. The higher power consumption is primarily because of the complexity of the guaranteed throughput router architecture. The performance of the GT design showed a similar trend as that observed with S2 synthetic benchmarks.

The run times of the various approaches were compared for large 50 core synthetic benchmarks. The ILP approach had to be timed out at 12 hours to generate the solutions. The GT approach took 5 minutes on average while our approach took 45 minutes. It must be noted that our approach is able to give very tight bounds on the quality of the solutions (shortest path routes, minimum dynamic power consumption, at most twice the number of routers and leakage power consumption as optimal solution) while addressing multiple design requirements (multiple use cases, cumulative and transaction traffic specification, port arity constraints and deadlock avoidance).

Figure 2.24: Power/Routers versus Port Arity

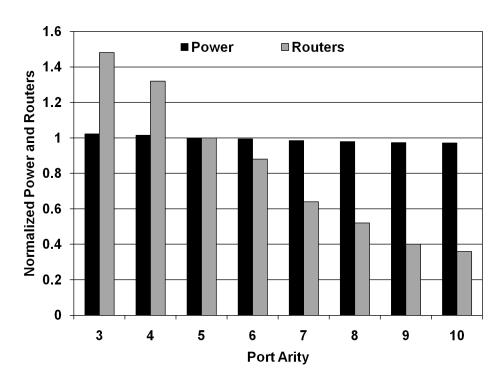

# 2.5.3 Impact of port arity

We examined the impact of maximum port arity on the power consumption and required router resources for our technique. We utilized the set-top box benchmark from Srinivasan et al. [3]. We first generated solutions for the benchmark using our technique with the default maximum port arity setting of 5 ports. We then varied the maximum port arity from 3 ports to 10 ports and generated solutions for each constraint. The results for power consumption and required router resources are shown in Figure 2.24. The plotted values have been normalized to the solution given by our technique for a maximum port arity of 5 ports. Increasing the port arity reduces both the power consumption and required router resources. The reduction in router resources is

Figure 2.25: Power Consumption with Increasing Bandwidth

quite substantial. The reduced router resources are also responsible for the nominal decrease in power consumption due to lower leakage power consumption.

### 2.5.4 Impact of increasing bandwidth

We also studied the impact of increasing the bandwidth of an application on the generated NoC architecture. We consider a synthetic single use case benchmark consisting of 14 cores, and 45 traces (specified at transaction level). The total bandwidth flowing through the traces was 31000 Mbps (with 13 Mbps and 720 Mbps as minimum and maximum trace bandwidth, respectively). The supported bandwidth at a router port was 4200 Mbps. We increased the bandwidth of each trace in steps of 10% of initial bandwidth till the bandwidth of a

Figure 2.26: Required Routers with Increasing Bandwidth

trace was doubled (100% increase). We compared the NoC designs generated by our technique against the ILP and GT solutions.

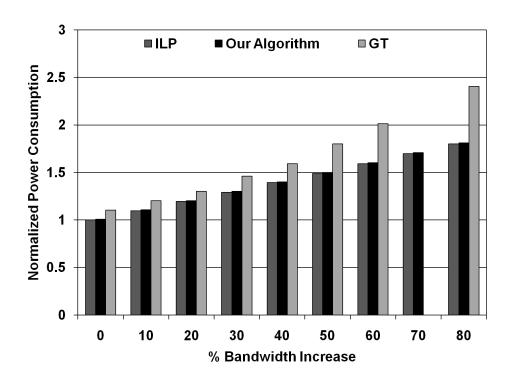

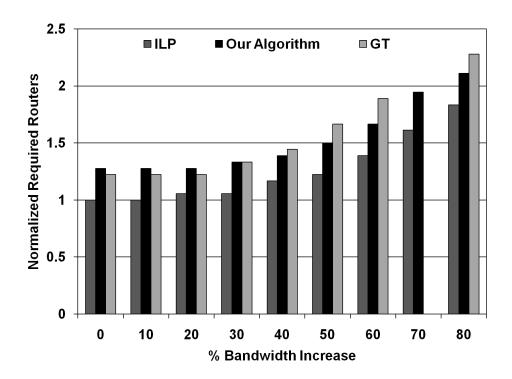

Figures 2.25 and 2.26 plot the power consumption and required routers for the various designs normalized to the solution generated by ILP for original design (0% bandwidth increase). It can be observed that as the bandwidth is increased the power consumption of the designs increases. The power consumption of the solutions generated by our approach are comparable to those generated by ILP while the GT designs utilize considerably higher power. Further, the power consumption of the GT designs increases at a faster rate with increase in bandwidth in comparison to solutions of ILP and our approach.

The router requirements of the designs remain more or less constant for bandwidth increases of up to 30%. Beyond 30% the number of routers begin

Figure 2.27: Reduction in latency and standard deviation

to increase with bandwidth for the solutions of the three approaches. The ILP solutions utilize lower router resources than GT and our approach. At lower bandwidth requirements the router requirements of GT are comparable to our approach. However, at higher bandwidth requirements GT solutions utilize markedly higher router resources. The GT approach failed to generate solutions for inputs with 70%, 90% and 100% increase in bandwidth. The ILP approach failed for inputs with 90% and 100% bandwidth increases. Both the GT and ILP approaches consider an initial allocation of routers, and if they are unable to generate the NoC design with the initial allocation they declare failure. Our approach replicates routers as required, and therefore was able to generate valid solutions for all inputs.

Figure 2.28: Normalized Power and Routers with Increasing Transaction Overlap

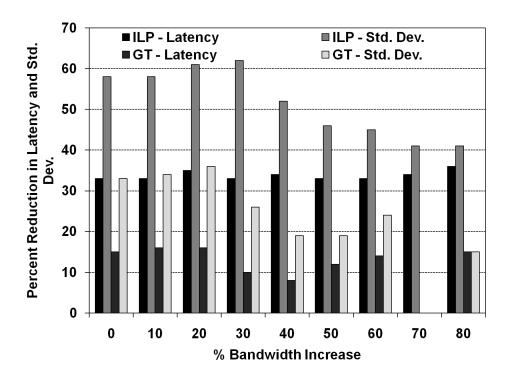

Figure 2.27 plots the percentage reduction in average latency and standard deviation due to our approach in comparison with ILP and GT solutions. The percentage reductions in both average latency and standard deviation are higher for ILP than GT solutions. The average latency reductions remain more or less constant even as the bandwidth is increased. Although, the standard deviation reductions reduce slightly as the bandwidth is increased, they are still quite large (40% for ILP and 15% for GT) for NoC designs with 80% higher bandwidth.

# 2.5.5 Degree of transaction interference

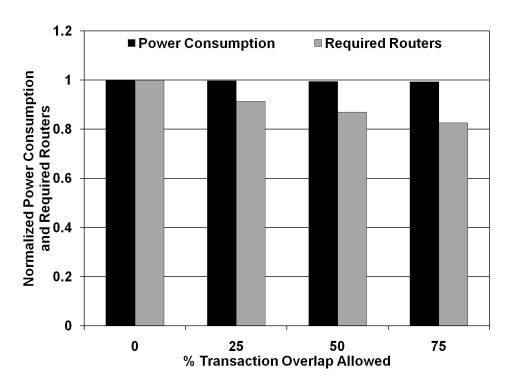

We also analyzed the impact on the quality of the designs as the degree of transaction interference was varied. The degree of transaction interference

Figure 2.29: Average Packet Latency with Increasing Transaction Overlap

is specified as the percentage of overlap between the start time windows of two transactions. The percentage overlap is measured with respect to the transaction that has the smaller start time window. We considered the same benchmark as the previous example. We generated designs with 0%, 25%, 50% and 75% permitted overlaps between the transactions. Figure 2.28 plots the power consumption and router requirements of the 4 designs normalized to the 0% overlap design. As observed from the figure, the router requirement reduces with increase in overlap. Our approach avoids transaction interference by introducing additional routers and constructing alternative routes. Thus, an increase in permitted interference leads to a decrease in router resources. The router resource reduction also leads to a marginal decrease in power consumption due to reduced leakage power.

Figure 2.30: Average Standard Deviation with Increasing Transaction Overlap

Figure 2.29 plots the average hop latency for each design. The average per hop latency does not show much increase with 25% overlap. However, the average latency increases sharply for larger percentages of the overlap. The average standard deviation plotted in Figure 2.30 shows a similar trend. Thus, we can consider 25% overlap to be a good trade-off between achievable performance and associated router requirements.

### 2.5.6 Deadlock avoidance analysis

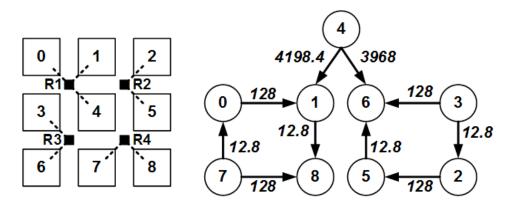

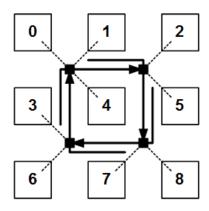

In this section we present an application example (Figure 2.31) to illustrate the benefit of having deadlock alleviation integrated with synthesis. On the left side of the figure is the floorplan with router allocation and core to router mapping. The layout consists of 9 cores arranged in a 3-by-3 mesh. On the right

Figure 2.31: Application specification

side of the figure is the communication graph for the application. Each arrow denotes a uni-direction communication trace. Each communication trace is annotated with its bandwidth requirement. There is a high potential for deadlock to exist in the the synthesized NoC due to the cyclical communication pattern (1->8,5->6,7->0,3->2). The solution generated by the ILP approach (which was identical to the one generated by GT) is shown in Figure 2.32. The directed edges in the figure denote the routes for the following traces 1->8,5->6,7->0, and 3->2. The potential for deadlock exists in the ILP solution as there is a cycle (due to the cyclical routes of the traces shown in the figure) in the CDG of the NoC. Our approach synthesized the NoC design shown in Figure 2.33 whose CDG does not have any cycles, and therefore is deadlock free.

### 2.6 Summary

We presented a holistic technique for custom NoC synthesis that can address cumulative bandwidth and transaction level communication requirements, deadlock avoidance, multiple use cases, and router port arity con-

Figure 2.32: ILP solution

Figure 2.33: Our solution

straints. The solutions generated by the approach use shortest path routes for all communication requirements (minimum dynamic power consumption), and utilize at most twice the number of routers (and leakage power consumption) as the optimal solution.

The experimental results demonstrated that in comparison to ILP and GT techniques our approach is able to generate NoC designs that demonstrate markedly lower average packet latencies and standard deviation with comparable power consumption requirements. The run times of our approach for large benchmarks was 45 mins while ILP and GT required 12 hours (with time out) and 5 mins, respectively. The solutions of our approach demonstrate a reduction in router resource requirements while the power consumption remains comparable as the port arity constraints are increased. As the bandwidth requirements of a design are increased in proportion to the port bandwidth constraint, our approach is able to successfully synthesize NoC designs that show superior performance characteristics, and similar power consumption in comparison to the designs generated by the GT and ILP approaches. We analyzed the impact of degree of overlap permitted between two transactions on

the NoC performance, and it was found that 25% overlap gave a good trade-off between the performance of the solution and associated router requirements. Finally, we showed that for input specifications that could result in synthesis of a deadlock susceptible NoC, our approach is successfully able to generate a NoC design which is deadlock free.

# Chapter 3

#### THE SYNTHESIS OF THE MEMORY ARCHITECTURE

Many embedded processor chips aimed at high performance and low power application domains are implemented as multi-processor System-on-Chip (MP-SoC) devices. The multi-media and communication sub-systems of an MP-SoC perform some of the most computation intensive and performance critical tasks, and are key determinants of the system-level performance and power consumption. This chapter presents an automated technique for synthesizing the system-level memory architecture (both code and data) for the streaming sub-systems of an embedded processor. The experimental results evaluate effectiveness of the proposed technique by synthesizing the system-level memory architecture for benchmark stream processing applications and comparisons against an existing approach.

In the next section we motivate the problem. Section 3.1 formally formulates the problem definition. In Section 3.2 we discuss related work. We present our synthesis technique in Section 3.3. In Section 3.4 present our experimental results and lastly, we conclude the chapter with a summary in Section 3.5.

#### 3.0.1 Motivation

The past decade has seen the emergence of smart mobile devices (smart phones, tablets) as the new technology drivers. Present day versions of these devices support a multitude of applications with voice/data communication, camera, media player, geographical position system (GPS), HD video, and 3D displays on the same device. The processors aimed at such devices must sup-

Figure 3.1: Generic MPSoC architecture

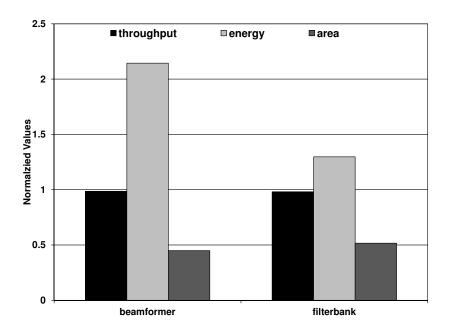

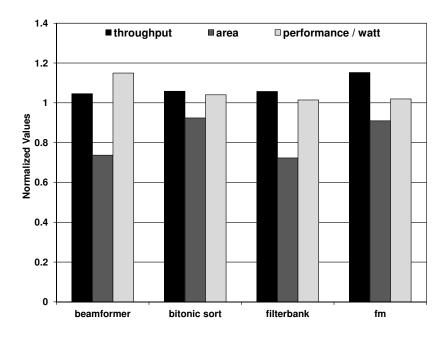

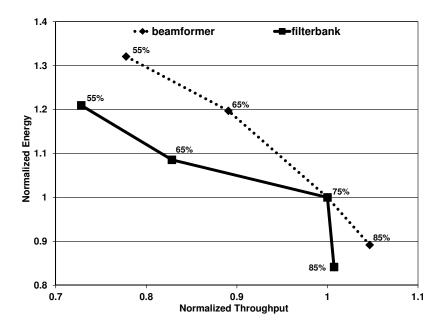

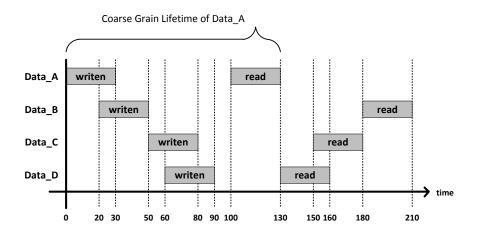

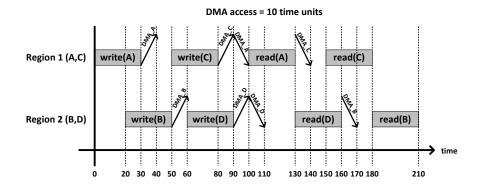

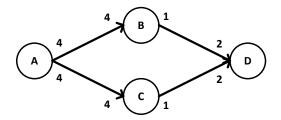

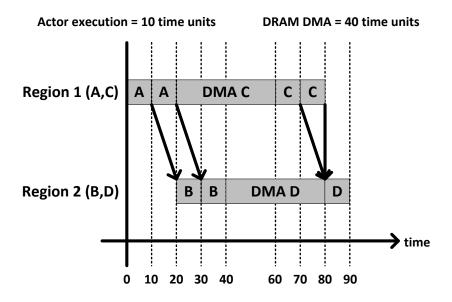

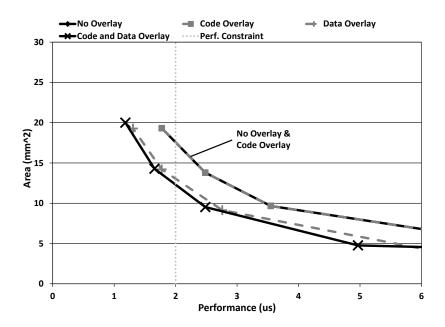

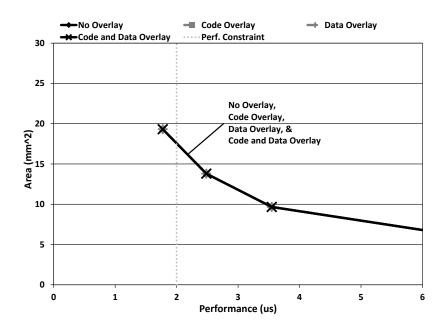

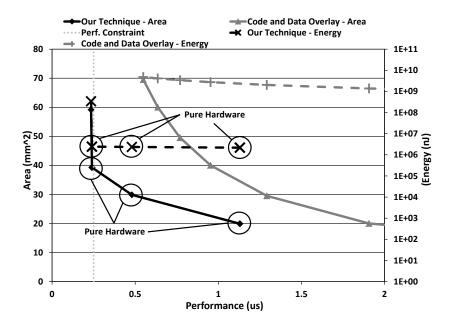

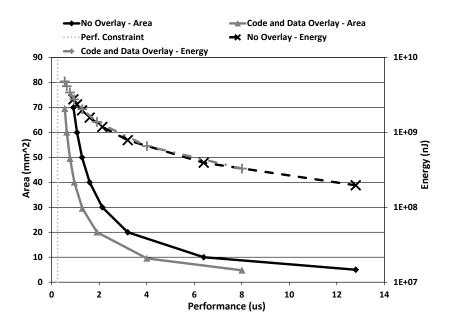

port the desired performance while literally "sipping" energy from the battery pack. Further, as smart devices fall in the realm of embedded computing the processors must be designed with a short turn around time. Consequently, chip designers have adopted a heterogeneous System-on-Chip architecture for these processors where each sub-system (application, graphics/media, communication, peripheral) is designed with an optimal constellation of processors, hardware accelerators, memory hierarchy and interconnection network.