Novel Low Temperature Processing for Enhanced Properties of

Ion Implanted Thin Films and Amorphous Mixed Oxide Thin Film Transistors

by

Rajitha Vemuri

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved April 2013 by the Graduate Supervisory Committee:

Terry L Alford, Chair N David Theodore Michael Goryll

ARIZONA STATE UNIVERSITY

May 2013

©2013 Rajitha Neeha Priyanka Vemuri All Rights Reserved

#### ABSTRACT

This research emphasizes the use of low energy and low temperature post processing to improve the performance and lifetime of thin films and thin film transistors, by applying the fundamentals of interaction of materials with conductive heating and electromagnetic radiation. Single frequency microwave anneal is used to rapidly recrystallize the damage induced during ion implantation in Si substrates. Volumetric heating of the sample in the presence of the microwave field facilitates quick absorption of radiation to promote recrystallization at the amorphous-crystalline interface, apart from electrical activation of the dopants due to relocation to the substitutional sites. Structural and electrical characterization confirm recrystallization of heavily implanted Si within 40 seconds anneal time with minimum dopant diffusion compared to rapid thermal annealed samples. The use of microwave anneal to improve performance of multilayer thin film devices, *e.g.* thin film transistors (TFTs) requires extensive study of interaction of individual layers with electromagnetic radiation.

This issue has been addressed by developing detail understanding of thin films and interfaces in TFTs by studying reliability and failure mechanisms upon extensive stress test. Electrical and ambient stresses such as illumination, thermal, and mechanical stresses are inflicted on the mixed oxide based thin film transistors, which are explored due to high mobilities of the mixed oxide (indium zinc oxide, indium gallium zinc oxide) channel layer material. Semiconductor parameter analyzer is employed to extract transfer characteristics, useful to derive mobility, subthreshold, and threshold voltage parameters of the transistors. Low temperature post processing anneals compatible with polymer substrates are performed in several ambients (oxygen, forming gas and vacuum) at 150 °C as a preliminary step. The analysis of the results pre and post low temperature anneals using device physics fundamentals assists in categorizing defects leading to failure/degradation as: oxygen vacancies, thermally activated defects within the bandgap, channel-dielectric interface defects, and acceptor-like or donor-like trap states. Microwave anneal has been confirmed to enhance the quality of thin films, however future work entails extending the use of electromagnetic radiation in controlled ambient to facilitate quick post fabrication anneal to improve the functionality and lifetime of these low temperature fabricated TFTs.

# DEDICATION

To my parents Lakshmi and Shashi, who have loved and supported me through all my unconventional decisions, my sister Malini who makes me want to be a better person, my grandparents who brought me up and cared for me like parents, and my in-laws who feel a sense of pride and joy for my success, just as they do for their son's achievements.

To my eternal best friend & husband Shantanu, and my closest friend over the decades Divya Paruchuri, for being the truest friends, for correcting me when I was wrong, for guiding me when I was distracted, and for always reminding me that I am capable of being better than what others think of me.

#### ACKNOWLEDGMENTS

I am greatly indebted to Dr. Terry Alford for his continual support and guidance throughout my graduate study, and the trust he placed in me. I can't thank enough students from Dr. Alford's group: Anil Indluru, Aritra Dhar, Chia-Ling Fang, Hyung Woo Choi, Joe Carptenter III, Karthik Sivaramakrishnan, Mandar Gadre, Muhammad Ruhul Hasin, Pai Liu, Sayantan Das, Sebastian Husein, Shengke Zhang, Zhao Zhao, and Andrew Knight, for their inspiration and support, not to forget the great times we spent as a group. I express my gratitude to Dr. David Theodore and Dr. Michael Goryll for being my committee members, and taking the time and interest for evaluating my work. I am extremely grateful to Late Ms. Yolanda Murphy, the department academic advisor, who was always around to help me, and to Late Prof. Dieter K. Schroder whose way of life, dedication to science and humble demeanor will serve as a life lesson to me.

I thank my friends and well-wishers from Hyderabad and Tempe for their support, positive criticism and for being a part of my life, and most of all the good times during these years at ASU. My heartfelt gratitude to Pastor Sanghoon Yoo and Mrs. Yoo-Kyung Yoo, who played an undeniable role in reviving my personality, and encouraged me to make decisions leading me through this path.

I acknowledge the support of National Science Foundation (C. Ying, Grant No. DMR-0602716) who partially funded this research, and the staff at Flexible Display Center at ASU Research Park for providing wafers crucial for this work.

iv

# TABLE OF CONTENTS

|                 |        | Page                                               |

|-----------------|--------|----------------------------------------------------|

| LIST OF TABLES. |        | viii                                               |

| LIST OF FIGURES | S      | ix                                                 |

| CHAPTER         |        |                                                    |

| 1 INTRO         | DUCTIC | DN1                                                |

| 1.1             | lon Im | plantation1                                        |

|                 | 1.1.a  | Damage1                                            |

|                 | 1.1.b  | Complications                                      |

|                 | 1.1.c  | Thin films and shallow depth transistors4          |

|                 | 1.1.d  | Microwaves technology and loss mechanisms6         |

|                 | 1.1.e  | High Z materials9                                  |

| 1.2             | Metal  | oxide based thin film transistors10                |

| 1.3             | Sumn   | nary11                                             |

| 2 EXPER         |        | AL PROCEDURE13                                     |

| 2.1             | Samp   | le preparation13                                   |

| 2.2             | Mater  | ial Characterization15                             |

|                 | 2.2.a  | Raman Spectroscopy15                               |

|                 | 2.2.b  | Rutherford Backscattering Spectrometry17           |

|                 | 2.2.c  | Sheet Resistance measurement19                     |

|                 | 2.2.d  | Hall measurements21                                |

|                 | 2.2.e  | Cross-section Transmission Electron Microscopy and |

|                 |        | Focussed Ion Beam Milling25                        |

# CHAPTER

| Page |

|------|

|------|

|   |        | 2.2.f Secondary Ion Mass Spectroscopy27                   | 7 |

|---|--------|-----------------------------------------------------------|---|

|   | 2.3    | Device Characterization (Thin Film Transistor Analysis)29 | 9 |

| 3 | DOPAN  | T ACTIVATION AND DIFFUSION PROFILE OF As                  |   |

|   | IMPL   | ANTED Si                                                  | 1 |

|   | 3.1    | Introduction                                              | 1 |

|   | 3.2    | Experimental Procedure32                                  | 2 |

|   | 3.3    | Results                                                   | 4 |

|   | 3.4    | Discussion4                                               | 1 |

|   | 3.5    | Conclusion48                                              | 5 |

| 4 | RECRY  | STALLIZATION OF As AND as-IMPLANTED Si46                  | 6 |

|   | 4.1    | Introduction46                                            | 6 |

|   | 4.2    | Structural Characterization49                             | 9 |

|   | 4.3    | Results                                                   | 1 |

|   | 4.4    | Discussion                                                | 5 |

|   | 4.5    | Conclusion                                                | 7 |

| 5 | KINETI | STRESS TESTING AND INFLUENCE OF LONG TIME                 |   |

|   | ANN    | EALS ON THE BEHAVIOR OF IZO TFTs                          | 8 |

|   | 5.1    | Introduction                                              | 8 |

|   | 5.2    | Experimental Details60                                    | C |

|   | 5.3    | Results and Discussion67                                  | 1 |

|   | 5.4    | Conclusion                                                | 6 |

|   | 5.5    | Appendix                                                  | 7 |

| 6 II     | NVEST | IGATION OF DEFECT GENERATION AND ANNIHILATION                |

|----------|-------|--------------------------------------------------------------|

|          | IN IO | GZO TFTS DURING PRACTICAL STRESS CONDITIONS:                 |

|          | ILLU  | MINATION AND ELECTRICAL BIAS                                 |

|          | 6.1   | Introduction79                                               |

|          | 6.2   | Experimental Procedure80                                     |

|          | 6.3   | Results83                                                    |

|          | 6.4   | Discussion90                                                 |

|          | 6.5   | Conclusion97                                                 |

| 7 5      | SUMMA | ARY                                                          |

|          | 7.1   | Introduction                                                 |

|          | 7.2   | Materials Characterization100                                |

|          | 7.3   | Dopant Activation and Dopant Diffusion of As IMPLANTED Si    |

|          |       |                                                              |

|          | 7.4   | Recrystallization of As Implanted Si and as Implanted Si102  |

|          | 7.5   | Kinetic Stress Testing and Influence of Long Time Anneals on |

|          |       | Behavior of IZO TFTs103                                      |

|          | 7.6   | Investigation of Defect Generation and Annihilation in IGZO  |

|          |       | TFTs During Practical Stress Conditions: Illumination and    |

|          |       | Electrical Bias104                                           |

|          | 7.7   | Conclusion105                                                |

|          | 7.8   | Future Work107                                               |

| REFERENC | ES    |                                                              |

# LIST OF TABLES

| Table | Page                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------|

| 1.    | Sheet Resistance measurements vs Anneal times                                                                     |

| 2.    | Hall measurements of <b>A</b> : 30 keV $1 \times 10^{15}$ As <sup>+</sup> cm <sup>-2</sup> and <b>B</b> : 180 keV |

|       | $1 \times 10^{15} \text{As}^+ \text{cm}^{-2}$ implanted Si                                                        |

# LIST OF FIGURES

| Figure | Page                                                                        |

|--------|-----------------------------------------------------------------------------|

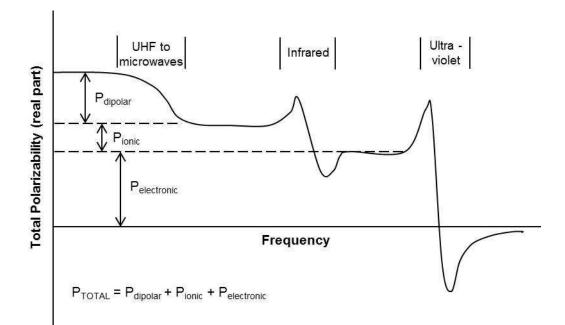

| 1.1.   | Frequency dependence of the several contributions to the                    |

|        | polarizability schematic                                                    |

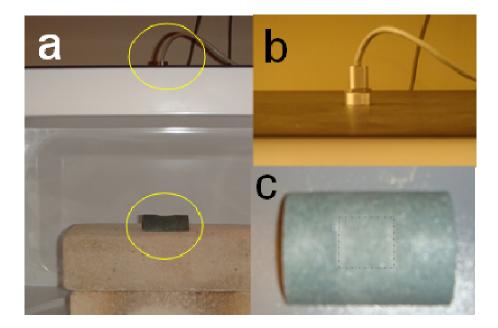

| 2.1.   | a) The microwave pyrometer-susceptor setup; b) pyrometer to                 |

|        | measure in-situ temperature; c) SiC-Al susceptor with a 1.5 cm $\times$ 1.5 |

|        | cm groove to mount the sample to provide uniform heating 14                 |

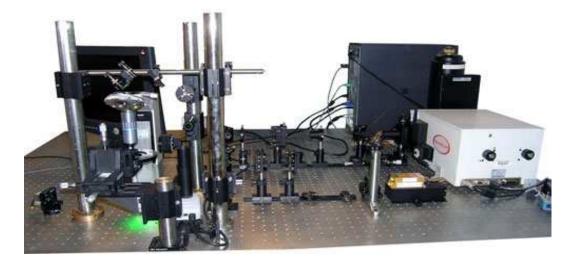

| 2.2.   | Raman Spectrometer used to examine crystalline structure of the             |

|        | samples 16                                                                  |

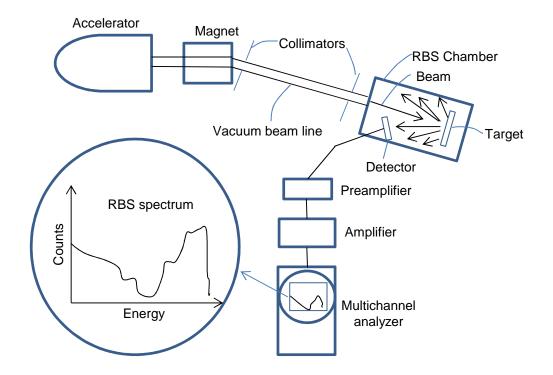

| 2.3.   | Schematic of a typical Rutherford backscattering system. A General          |

|        | Ionex 1.7 MV Tandetron accelerator was used for RBS at ASU 18               |

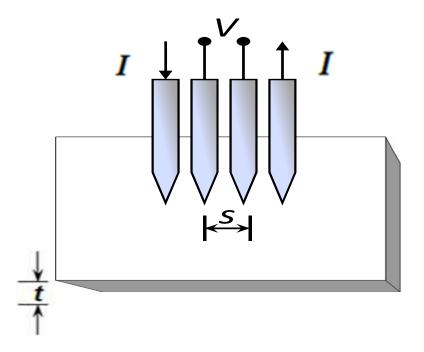

| 2.4.   | Layout of atypical four-point probe setup. Measurements taken at            |

|        | ASU had a probe spacing of 2 mm. Where $S =$ spacing between the            |

|        | probes, and t = thickness of the sample 20                                  |

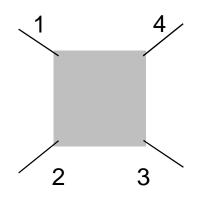

| 2.5.   | Sample labeling for the contacts made to perform Van der Pauw Hall          |

|        | measurements                                                                |

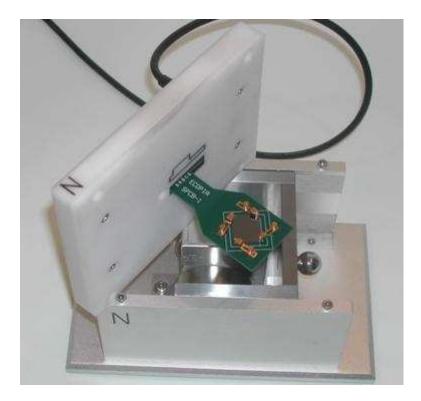

| 2.6.   | Ecopia HMS-3000 Hall Effect Measurement System used at ASU 25               |

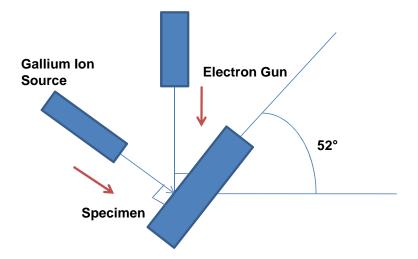

| 2.7.   | FEI 835 focused-ion beam tool with a Ga ion-source                          |

| 2.8.   | Philips CM200 FEG TEM used at ASU                                           |

| 2.9.   | Mechanism of SIMS analyzer                                                  |

| 2.10.  | Mechanism of SIMS analyzer                                                  |

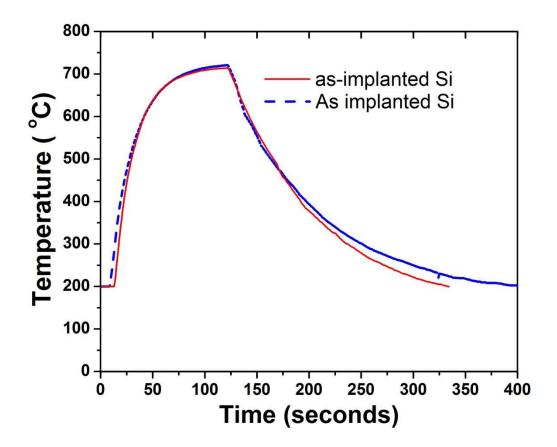

| 3.1.   | Temperature vs Time profile of As implanted Si with and without             |

|        | Susceptor                                                                   |

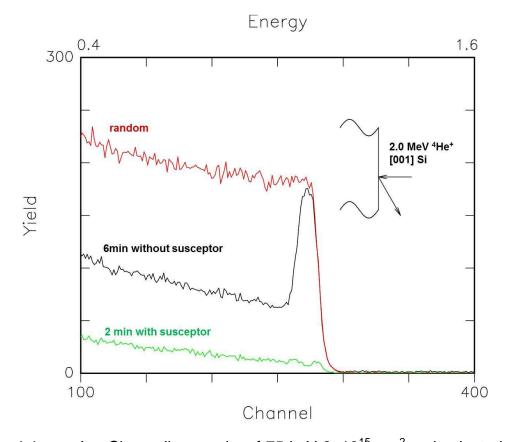

| 3.2. Ion channeling results of As <sup>+</sup> implanted Si                                     |

|-------------------------------------------------------------------------------------------------|

| 3.3. Sheet Resistance measurements of the different dosage and                                  |

| implantation energy As implanted Si at different anneal times 39                                |

| 3.4. SIMS profile of 180 keV $1 \times 10^{15}$ As <sup>+</sup> impanted Si annealed unde       |

| different conditions 41                                                                         |

| 4.1. Temperature vs time profile of As implanted Si and as-implanted S                          |

| without a susceptor 47                                                                          |

| 4.2. Temperature vs time profile of As implanted Si and as-implanted S                          |

| witht a susceptor 48                                                                            |

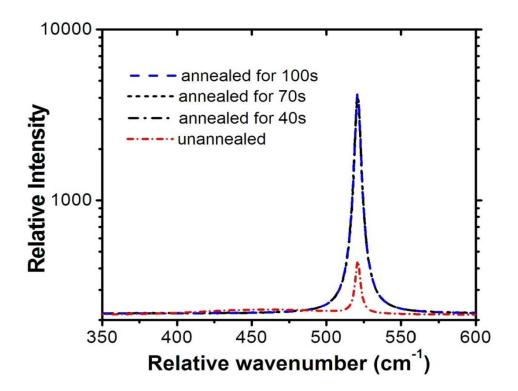

| 4.3. Raman Spectra of 30 keV 1×10 <sup>15</sup> cm <sup>-2</sup> As implanted Si after differen |

| anneal times51                                                                                  |

| 4.4. Ion Channeling results of 75 keV 2×10 <sup>15</sup> cm <sup>-2</sup> as-implanted Si after |

| microwave annealing with and without susceptor                                                  |

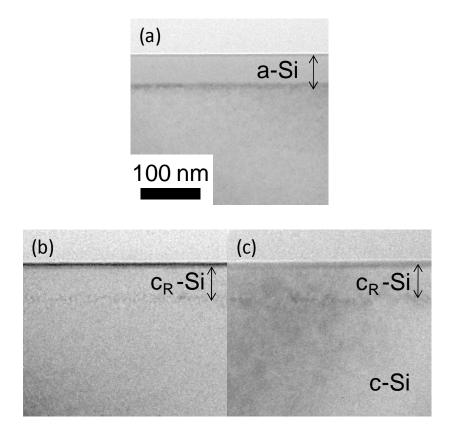

| 4.5. XTEM images of Si implanted with 30 keV $1x10^{15}$ As <sup>+</sup> cm <sup>-2</sup> after |

| different anneal times 54                                                                       |

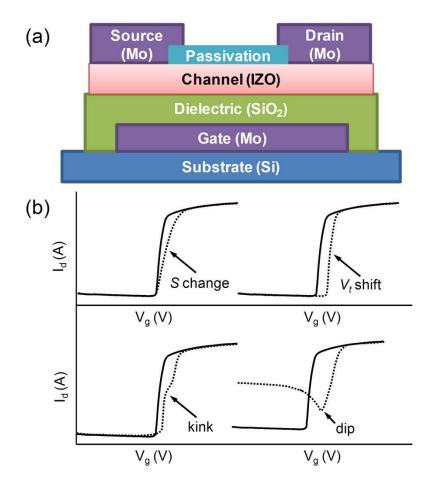

| 5.1. a) Schematic of the TFTs detailing b) subthreshold degradation                             |

| threshold voltage shift, kink, and dip in the transfer characteristics                          |

| with respect to unstressed TFT behavior                                                         |

| 5.2. XTEM images of Si implanted with 30 keV $1x10^{15}$ As <sup>+</sup> cm <sup>-2</sup> after |

| different anneal times 63                                                                       |

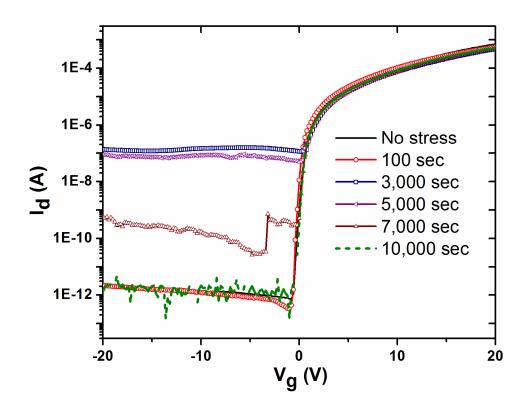

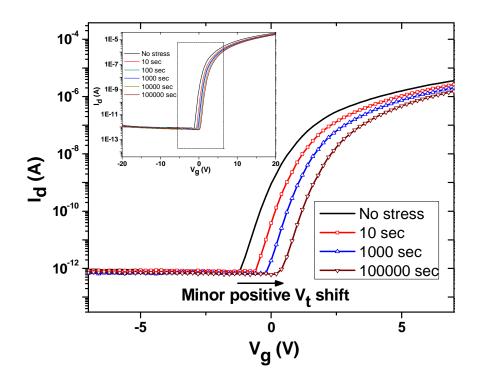

| 5.3. Transfer characteristics of TFT under 50 °C thermal stress                                 |

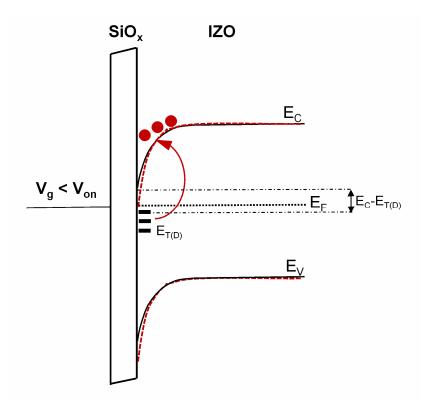

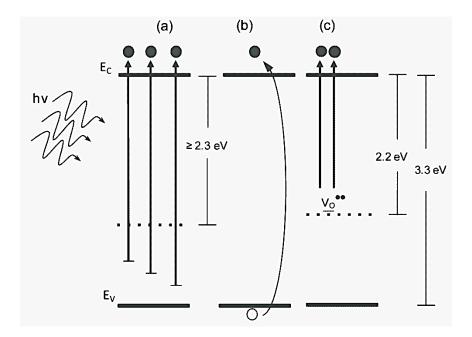

| 5.4.  | Band diagram representation of barrier lowering for increased hole                                |

|-------|---------------------------------------------------------------------------------------------------|

|       | and electron transport under prolonged thermal stresses                                           |

| 5.5.  | Transfer characteristics of TFT under 80 °C thermal stress                                        |

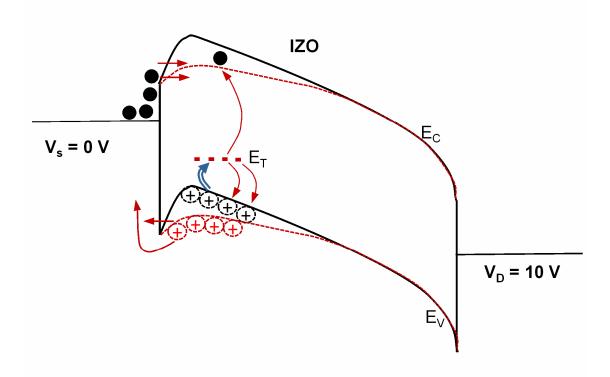

| 5.6.  | Band diagram representation of thermal excitation of deep level donor                             |

|       | like trap states ( $E_{T(D)}$ ) at 80 °C                                                          |

| 5.7.  | Transfer characteristics of TFT under 50 ° C thermal stresses and 20                              |

|       | V gate stress 69                                                                                  |

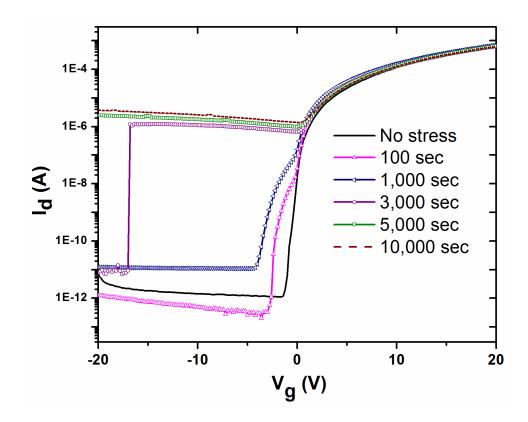

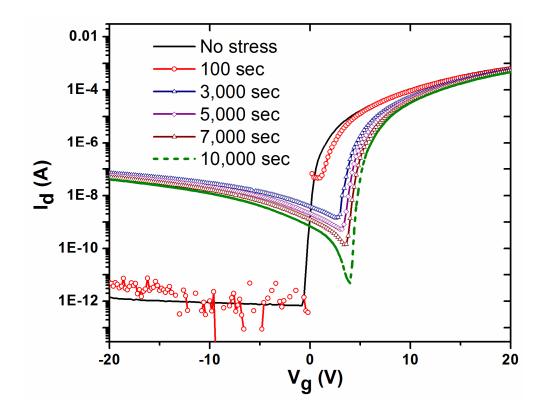

| 5.8.  | Transfer characteristics of TFT under 80 ° C thermal stresses and 20                              |

|       | V gate stress70                                                                                   |

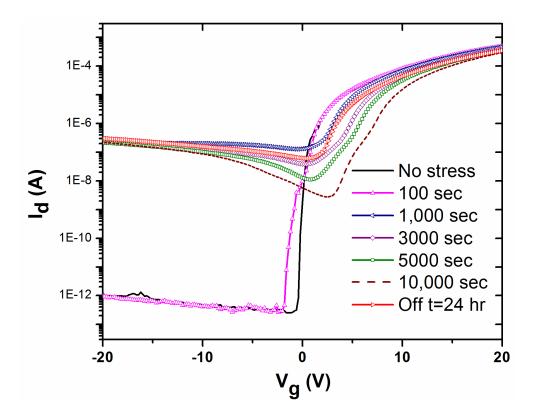

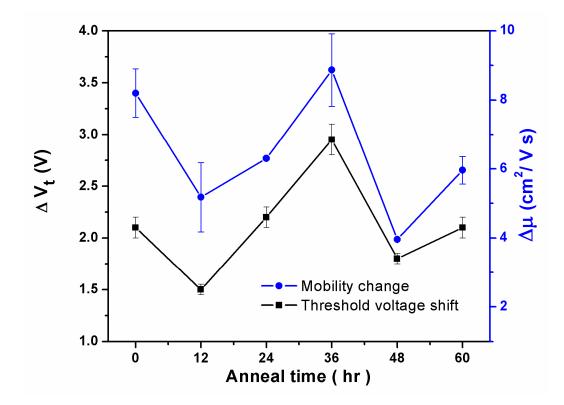

| 5.9.  | Field effect mobility shift and threshold voltage shift of the annealed                           |

|       | TFTs, before and after 10,000 seconds of bias stress                                              |

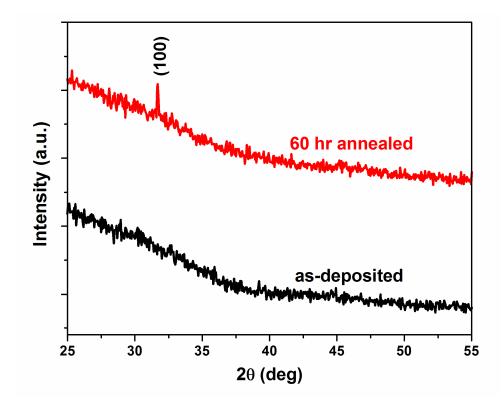

| 5.10. | XRD patterns of as-deposited and 150 $^{\rm C}$ an nealed IZO thin films . 72                     |

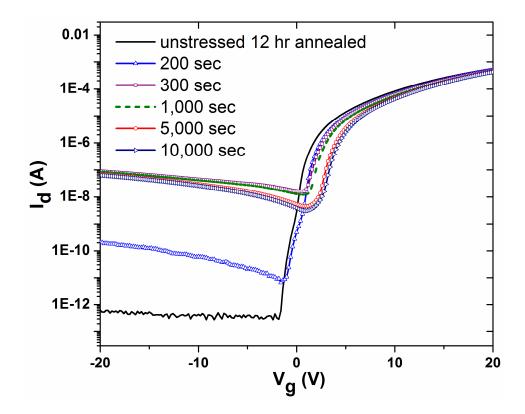

| 5.11. | Transfer characteristics of the 12 hr annealed TFTs under kinetic                                 |

|       | stresses at 50 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

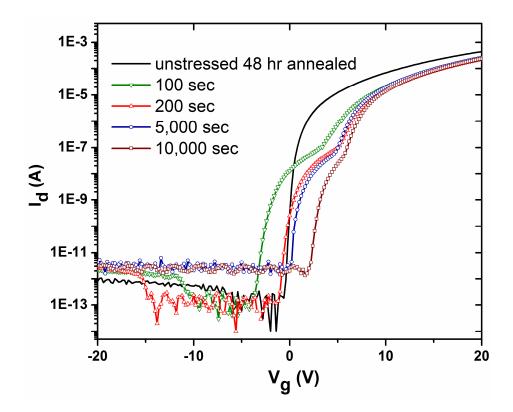

| 5.12. | Transfer characteristics of the 48 hr annealed TFTs under kinetic                                 |

|       | stresses at 50 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

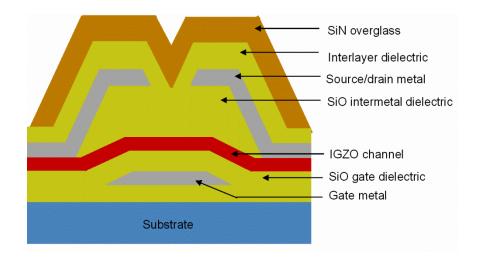

| 6.1.  | IGZO TFT Cross-section                                                                            |

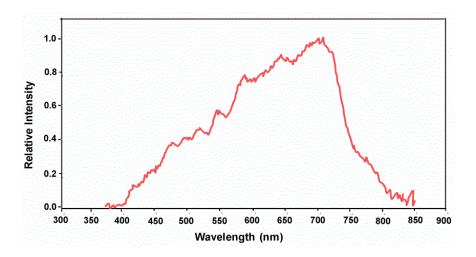

| 6.2.  | Spectrum of a standard EKE 3200 lamp source used for illumination                                 |

|       |                                                                                                   |

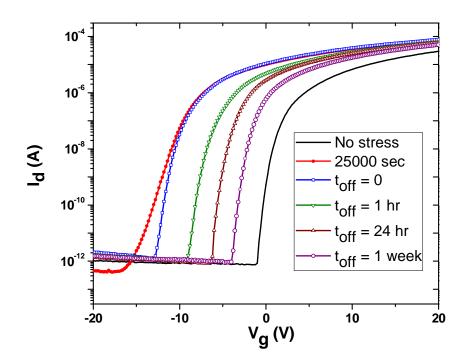

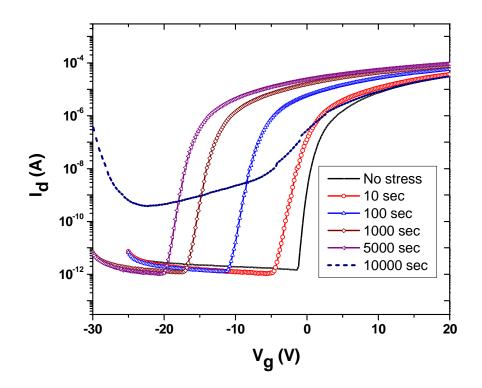

| 6.3.  | Transfer characteristics of IGZO TFTs near the transistor on-off                                  |

|       | transition under Vg= -20 V and Vd=0 V bias stress; Inset: Full range                              |

|       | transfer characteristics of the TFTs under stress                                                 |

# Figure

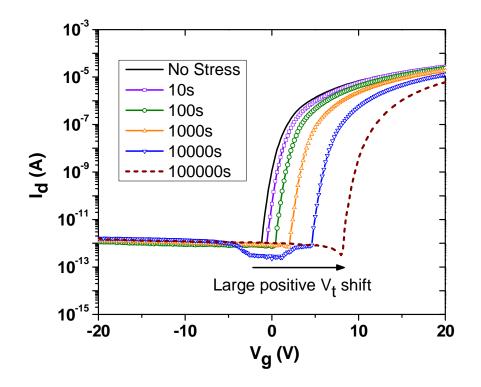

| 6.4. IGZO under Vg=20 V, Vd=0 V bias stress for 100,000 seconds                                                                                           | 35        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

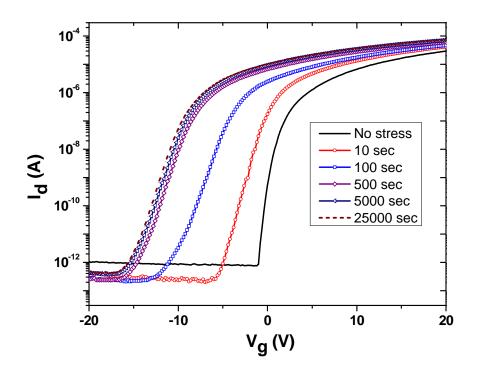

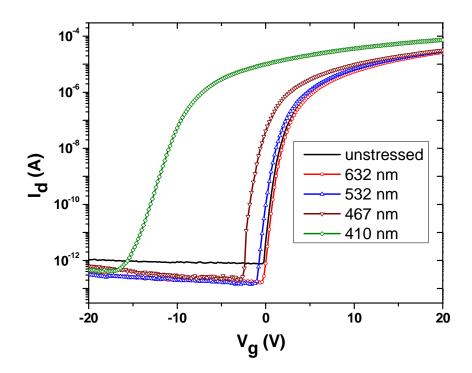

| 6.5. IGZO under 410 nm light illumination stress for 25,000 seconds                                                                                       | 36        |

| 6.6. IGZO TFT recovery after 410 nm light turned off                                                                                                      | 38        |

| 6.7. Illumination stress testing for the shortest to longest wavelengths                                                                                  | 38        |

| 5.8. Transfer characteristics under 410 nm illumination along with -20                                                                                    | V         |

| gate bias                                                                                                                                                 | 90        |

|                                                                                                                                                           |           |

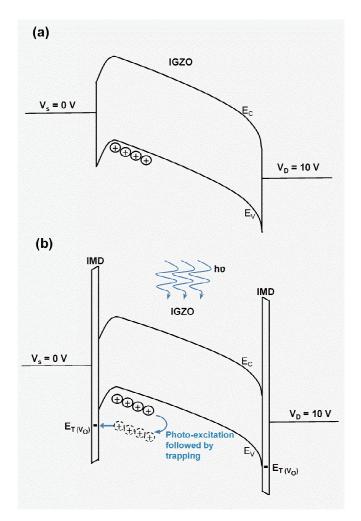

| 6.9. Band diagram for hole transport during reverse bias ( $V_g < 0 V$ , $V_d = 1$                                                                        |           |

| 5.9. Band diagram for hole transport during reverse bias ( $V_g < 0 V$ , $V_d = 1 V$ ) at metal-channel interface under a) cases of no illumination or wi | 10        |

|                                                                                                                                                           | 10<br>ith |

#### Chapter 1

#### INTRODUCTION

#### 1.1 Ion Implantation

Semiconductor materials require impurities to be added to them, to increase their conductivity. Impurities intentionally added to the materials, such as As or B in silicon, are called dopants. Ion implantation is the most practical technique used in the industry to introduce dopants into silicon, since it is controllable and reproducible [1]. Various other methods used to introduce dopants, such as solid-source or gas diffusion have been found to be difficult to control and unreliable. An additional limitation to these methods is that they can incorporate dopants only upto the solid solubility level. However using ion implantation, dopants can be introduced at concentration levels above thermal equilibrium solid solubility values.

#### 1.1.a Damage

Ion implantation is performed by vaporizing and ionizing a source of the desired dopant. The ionized atoms are filtered using a mass analyzer and act as a highly pure source for ions used for implantation. These ions, then under a strong electric field, are directed through a beam which is focused onto the Si surface. Before the dopants are directed onto the surface, there is an exchange

of energy that occurs between atoms and the electrons due to collisions, and also the atoms come to rest under the Si surface due to loss of energy [2]. The loss of energy of the ions could be due to nuclear stopping and electronic stopping. The elastic scattering between the ions and the nuclei determine nuclear stopping, and the inelastic scattering due to the ion interaction with the electron cloud determines the electron stopping. Ionization of the implanted ions and Si atoms in the target, and excitation of valence band and conduction band electrons can be caused due to these events.

The total distance that the dopant ions travel inside the silicon is calculated by using the two stopping methods used above. The depth at which the dopants reside below the target surface is also determined by the angle of implantation and the energy. The implantation dosage which is the number of dopant atoms incorporated into the silicon per unit surface area is determined by the beam current and implant time. The important parameters of ion implantation are the projected range and projected straggle, which are the average depth of penetration of the dopants, and the deviation from the projected depth, respectively.

Collision of the dopant atoms with the silicon lattice displaces the silicon atoms, removing the long range order of the lattice. Displaced atoms with sufficient energy can then collide with other atoms causing them to be displaced and creating a damage profile. The mass of the dopant atoms also impacts the

2

doping profile [3], apart from the dosage and implantation energy, implying heavier atoms create a greater damage profile at the same velocity. If the long range order is destroyed by a great extent, the silicon surface changes from being crystalline to amorphous.

# 1.1.b. Complications

Silicon (001) wafers have been used in this study as substrate materials. For a (001) Si wafer, a zero degree implantation angle against the normal to the sample results in maximum channeling [4]. While ion implanting the surface, a 7 degree shift from the normal is done to ensure that the dopant atoms such as boron, phosphorous or arsenic are not channeling, or the channeling is minimized. Reducing the implant energy to reduce the damage profile leads to implications such as increased concentration of inactivated dopants due to increased dopant-vacancy clusters [5]. It is necessary for the dopants to have lower energies for a shallow implant region, but the energy is required to be high enough so that the dopant atoms penetrate the Si surface. These conditions set a limit to the minimum energy that can be used for implantation. However, if the implant dose is high, low energies are also sufficient to amorphize the surface.

### 1.1.c. Thin Film and Shallow Depth Transistors

Thin crystalline Si film structures have gained increased importance in semiconductor industry since the advent of thin film transistors (TFTs) in the 1980s. Crucial regions such as drain/source in ultra-shallow transistors require thin crystalline layers that are highly doped [6, 7] in order to provide the necessary conductivity in these regions. However, heavy implantation damages the surface to the extent of amorphization [8]. It is necessary to repair this damage to make the films crystalline, and to electrically activate the dopants for the devices to function as desired. However, any post implant process should not cause extensive dopant diffusion. Different types of post implantation annealing methods were successful earlier in obtaining solid phase epitaxy (SPE) [9, 10], most widely used of which are laser annealing [11], rapid thermal annealing (RTA) [12, 13], and metal induced crystallization (MIC) [14]. A temperature of above 600°C [15] is required to achieve high quality crystalline Si, which takes long hours under conventional furnace annealing. Laser annealing, though extensively used earlier, provides uneven heating of the sample [11]. During laser annealing, a laser beam is focused onto the sample, and the photons that comprise the beam provide energy to the lattice. The lattice reorders itself and makes a long range order crystalline material. But this process transfers heat from layer to layer in a conductive manner, and provides uniform heating across the depth of the sample. Furthermore, the high energy beam might create high temperatures at the surface causing the sample to melt, for instance a temperature of over 1100 °C can melt the silicon sample, and recrystallizes it off of the single crystal lattice of the substrate material forming polycrystalline. The MIC anneal is known to crystallize Si at lower temperatures and shorter duration: but, it is susceptible to contamination of the ultra-shallow film leading to failure of the device [16]. Metals such as aluminum and gold are called eutectic forming metals. They have been primarily used as added impurities in the amorphous semiconductor layer to provide local heating sites for the surrounding atoms since the metal atoms heat quicker than the remaining structure. Also, some metals like Ni used in MIC are called silicide forming metals, which are used as capping on the amorphous silicon layer forming silicides upon heating. Recrystallization of the amorphous Si is induced by the silicide seed, and the misfit between NiSi<sub>2</sub> and Si and the chemical potential difference between the NiSi<sub>2</sub>/a-Si and NiSi<sub>2</sub>/c-Si interfaces [ref]. But with ultra-sensitive channel layers the minimum amounts of the impurities also cause high channel leakage currents undesired for the functioning of the device.

Rapid thermal anneals (RTA) provide high temperatures in short time durations that provides heating across the depth of the material and bring about recrystallization and dopant activation necessary to provide conductive layers. This technique has been effective till the 100 nm technology node where the excessive heat supplied to the dopant atoms not only allows it to settle in the substitutional sites of the lattice, but also forces it deeper into the substrate by a few nanometers. As we continue to scale and approach the 17 nm node, the dopant diffusion through RTA would produce junctions which are no longer shallow and void their effectiveness.

Hence, as the technology is scaled to smaller dimensions of technology nodes and the feature sizes, the pre and post implantation processing of materials also need attention. The technology of assisted microwave annealing aims at incorporating the physics behind the quick recrystallization that some of the processing techniques offer but without contaminating the sample, or using extremely high or non-uniform heating.

# 1.1.d. Microwaves Technology and Loss Mechanisms

Methods that activate dopants without causing diffusion are the requirement of the industry in order to meet ITRS predictions. In this work, we have explored the potential use of low temperature microwave annealing (by use of a Fe<sub>2</sub>O<sub>3</sub> infused SiC-Al<sub>2</sub>O<sub>3</sub> susceptor/ assistor) as a post implantation technique to achieve solid phase epitaxy (SPE) and dopant activation in ion implanted Si. Microwaves function based on the loss mechanisms that depend on the dielectric properties of the samples/objects being heated/annealed.

The sample heating when subjected to microwave radiation occurs as a result of ionic conduction and dipole polarization losses [17]. These losses vary

with frequency, and hence the heating profile of the sample varies with different frequencies. In ionic materials, ionic conduction losses or vibrational losses are prominent. Different responses can be observed when ionic materials are subjected to an electric field. In presence of an electric field, electrons move freely inside conductors resulting in electric current. In dielectrics materials, electrons do not move freely and instead, reorientation of induced dipoles gives rise to heating.

lons move between vacant sites and interstitial positions within the lattice network, leading to space charge effects. But at higher frequencies, vibration losses from the vibration of ions become important, and the frequency dependence of the losses decreases, and becomes more temperature dependent [18]. In the presence of an electric field, the electron cloud in the atom can be displaced with respect to the nucleus, leaving negative charges at one side, and the positive charges at the other side of the atom. An electric dipole moment is created as a result of the displacement of the uncompensated charges. The summation of the dipoles gives the polarization *P* over a unit volume. In a molecular scale, displacement of charged ions with respect to one another gives rise to dipole moments in in the molecule that comprise the atomic and ionic polarizations.

7

Fig. 1.1 Frequency dependence of different components of polarizability[18]

The ability of a material to absorb electrical potential energy or the microwave field is determined by its complex permittivity. The real part of the permittivity,  $\in$ ', the depth of penetration of the microwaves into the material can be given, and,the loss factor,  $\in$  " [19], indicates the material's ability to store the energy. *tan* $\delta$  is described as the loss tangent that suggests the capability of material to convert the field or energy absorbed into heat.

# 1.1.e. High Z Materials

In the past, microwave anneal technology has been used to anneal boron implanted Si with much success [20]. This study is unique compared to other such work done due to the dopant activated is a higher Z material such as arsenic implanted Si. Due to the higher Z nature of the dopant, greater activation energy would be required to electrically activate the dopant. To provide energy through heat to facilitate this action, the microwave field generated by a 1300 W, 2.45 GHz magnetron is insufficient. The Si sample by means of having a low dielectric constant is heated by the microwave radiation by volumetric heating, due to larger depth of penetration. With a high depth of penetration,  $D_{\rm P}$ , the sample is incapable of being raised to high temperatures required for recrystallization, 600 °C being the temperature for Si. The use of a high dielectric assistor material called as a susceptor has been suggested. In this study, the susceptor is a cylindrical structure made of Fe<sub>2</sub>O<sub>3</sub> infused SiC surrounding alumina. The composite structure has a high dielectric constant, and when tested as stand-alone substance being subjected to the microwave radiation, it exhibits rapid heating rate, indicating surface heating by means of low depth of penetration, instead of volumetric heating that provides high depth of penetration. The idea is to supply the heat to the Si sample in a conductive manner so that the sample reaches the temperatures required for recrystallization, and undergoes uniform damage repair due to the uniform absorption of microwaves.

9

#### **1.2 METAL OXIDE BASED THIN FILM TRANSISTORS**

In the past, amorphous or polycrystalline Si:H layer have been commonly used as channel layers for most conventional TFTs in flat panel displays. However, these TFTs have a lot of disadvantages such as low mobility (<1 cm<sup>2</sup>/V-s), and are sensitive to light [21]. As a result of which they have poor efficiency of light transmittance and brightness. To obtain a TFT with high mobility requires relatively high process temperature (> 300 °C), which makes it difficult to fabricate them on flexible polymer substrates.

With this in mind most of the research is moving from silicon based TFTs to amorphous metal-oxide semiconductors as channel layer and source/drain electrodes [22]. These TFTs attract much attention due to their advantages such as high mobility, and high transmittance [23-25]. A number of metal-oxide based TFTs such as zinc oxide (ZnO), zinc tin oxide (ZlO), indium gallium oxide (IGO), and indium gallium zinc tin oxide (IGZSO) have demonstrated high mobilities even for room temperature fabrication [26,27]. Many TFTs were reported using crystalline ZnO [28,29], or polycrystalline SnO<sub>2</sub> [30], and In<sub>2</sub>O<sub>3</sub> [31].

Recently the transparent electronics has emerged a new field of technology. However to realize the transparent TFTs for flexible electronics, amorphous films are more suitable than crystalline type, because amorphous oxide films have added advantages such as low temperature deposition, good film smoothness, low compressive stress, large area deposition by sputtering, and uniformity of device 12 characteristics [32-34]. The fabrication of lowtemperature TFTs allows for flexible large area electronic devices such as electronic paper and flexible display which are lightweight, flexible, and shock resistant. However the fabrication of low temperature amorphous metal-oxide TFTs results in a number of defects in the channel layer, insulator and interface. The presence of these TFTs can be a latent problem (*e.g.*, poor performance and thermal instability). Hence, it becomes very important to improve the performance/stability of these TFTs. In addition, it would be very useful to understand the role of these defects on the performance and stability of these metal-oxide TFTs. We have improved the performance of these TFTs by low temperature long anneals. Low temperatures are preferred due to the compatibility of the post fabrication process with flexible polymer substrates targeted for flexible large area electronics.

# 1.3 SUMMARY

This comprehensive report presents the work done in achieving novel processing techniques for thin films and thin film transistors. The characterization techniques employed in understanding material and device properties before and after various anneal techniques are discussed in chapter 2. Chapters 3 and 4 describe the low energy and shorter duration microwave processing of arsenic-doped silicon compared to conventional anneal methods. An attempt is made to understand the mechanism of microwave annealing of heavily ion implanted

silicon. Shorter processing times have been achieved with susceptor-assisted hybrid microwave heating of the ion-implanted silicon. Ceramic composite susceptors, made of alumina and silicon carbide (SiC), have been used to achieve the required temperatures for repairing the lattice damage caused by As doping and for the electrical activation of the dopants.

Chapter 5 presents a detail investigation of the performance of IZO TFTs under thermal and bias stress tests. The effect of post process anneals and the enhanced stability of the devices under thermal stresses as a result, is also discussed in this chapter.

Chapter 6 discusses an in-depth study on the effect of illumination stresses and degradation in performance of IGZO TFTs. Failure conditions have been identified along with the corresponding nature of defects which assists in suggesting suitable post fabrication processes.

Chapter 7 presents a comprehensive summary of the work done, and suggests a future plan of work where detailed study of nature of defects in the metal oxide based TFTs will be performed. Suitable post processing methods including microwave anneal will be suggested based on the type of defects encountered in this work.

12

#### Chapter 2

# EXPERIMENTAL PROCEDURE

# 2.1. Sample Preparation

The base samples are *p*-type boron doped, 100  $\Omega$ -cm (100) orientated silicon wafers cleaned using the Radio Corporation of America procedure. Eaton Nova NV10-180 batch process ion implanter was used to implant the cleaned Si wafers. Ion implantation was performed while orienting the wafers at 7° with respect to the normal to the incident beam and with a 45° plane twist, so that ion channeling can be minimized. One set of wafers was implanted at room temperature (RT) using 30 keV As<sup>+</sup> ions and a dose of 5×10<sup>14</sup> As<sup>+</sup> cm<sup>-2</sup>. Another set of wafers was implanted using 30 keV As<sup>+</sup> ions and a dose of 1×10<sup>15</sup> As<sup>+</sup> cm<sup>-2</sup> dosage. The last set of samples was implanted with a dose of 180 keV 1×10<sup>15</sup> As<sup>+</sup> cm<sup>-2</sup> ions.

Microwave annealing of different dosage arsenic implanted Si samples was done in a single-frequency (2.45 GHz),  $2.8 \times 10^4$  cm<sup>3</sup> cavity applicator microwave system equipped with a 1300 Watt magnetron source. The anneal times ranged between 40-100 seconds for each sample type. A Raytek Compact MID series pyrometer with a spectral response of 8–14 µm was used to monitor the near surface temperature. The emissivity for the samples was adjusted by careful calibration of the temperature read by the pyrometer against the temperature monitored by a thermocouple.

The Fig. 2.1 shows the microwave setup involving the pyrometer for in-situ temperature measurements of the sample in the cavity. The arsenic implanted Si cannot raise to a temperature needed for recrystallization of Si, hence a susceptor is used. The susceptor being a cylindrical structure needed to be carved for a 1.5 cm  $\times$  1.5 cm groove in the center to mount the sample in order to provide uniform surface heating for the sample from underneath.

Fig. 2.1 a) The microwave pyrometer-susceptor setup; b) pyrometer to measure in-situ temperature; c) SiC-Al susceptor with a 1.5 cm × 1.5 cm groove to mount the sample to provide uniform heating.

### 2.2. Material Characterization

With the use of a susceptor to provide additional heating mechanism, the surface temperatures of the arsenic implanted Si ranged between 620-680 °C. The as-implanted As<sup>+</sup> and the microwave annealed samples were characterized using several methods to test for dopant activation and film recrystallization. In addition to characterizing pre and post anneal samples for the aforementioned criterion, the microwave annealed samples were compared against 30 second rapid thermal annealed (RTA) samples, annealed at 900°C for the extent of dopant diffusion. Microwave losses coupled with hybrid volumetric and surface heating of the sample through microwave power absorption and susceptor heating are the mechanisms behind recrystallization of the arsenic implanted Si.

#### 2.2.a Raman Spectroscopy

A Raman line scan was performed to determine the structure of the As<sup>+</sup> implanted Si pre and post microwave annealing. Raman spectroscopy is one of the most common vibrational spectroscopies to assess the molecular motion. An argon laser with an excitation wavelength of 532 nm is focused onto the samples mounted underneath the optical microscope, through an Olympus 100×0.8 NA objective. The spectra from the sample are reflected into a Sopra 2000 2m double spectrometer by a 50% beam-splitter. A 532 nm notch filter blocks any scattered light from the laser. The spectrum is dispersed and collected into a

Princeton CCD Camera with an energy dispersion of 60pixels/cm. The Raman spectra collected from the CCD is calibrated as a function of intensity that depends on the time of exposure, against the relative wavenumber [35]. High energy beam samples damage the sample surface, but in the Raman spectroscopy, care is taken to avoid usage of high energy beams. The maximum power of a beam used in Raman spectroscopy is 100 mW. In our setup, a 4 mW power beam was used, which goes through a series of beam splitters, at the end of which the beam power hitting the sample is as low as 1 mW which doesn't alter the characteristics of the sample. The setup of the Raman spectroscopy is as seen in Fig. 2.2 below.

Fig. 2.2 Raman Spectrometer used for characterizing the samples to observe the crystalline structure (Courtesy: Center for Solid State Sciences, CSSS, ASU)

### 2.2.b Rutherford Backscattering Spectrometry

Rutherford backscattering spectrometry (RBS) is a non-destructive characterization technique. It is used to analyze the atomic composition of the sample like diffusion and interaction between the copper and ruthenium thin films and to estimate the sample thickness using very high energy (MeV) beam of low ion mass. It is also used for quantitative depth profiling, areal density measurements, and determination of crystal lattice quality. RBS utilizes Tandetron accelerator to generate a MeV ion beam. After entering the evacuated beam line, the ions are then collimated and focused. There are bending magnets which after mass selection geometrically disperse ions according to their mass. Finally the beam raster-scans over the specimen and back scattered ions are analyzed by a Si barrier detector. The electronic pulses are then amplified and sorted according to the voltage amplitude by a multichannel analyzer to yield the resulting RBS spectrum [36]. RBS was performed using a General lonex 1.7 MV tandem accelerator with He<sup>2+</sup> ions at energy of 2.8 or 3.5 MeV as shown in Fig. 2.3.

Ion implantation with concentrations and energies such as of the samples in our study causes implant damage. Ion channeling experiments were conducted to compare the damage in unannealed samples as opposed to processed samples, and to ascertain if the microwave annealing could repair damage of this extent. Rutherford backscattering spectrometry (RBS) was used to quantify the implant damage, and a 2.0 MeV He<sup>+</sup> analyzing beam for ion channeling. Samples were analyzed in random and [001] channeled orientations. He<sup>+</sup> ions were collected using a solid state detector, positioned 13° from the incident beam. The software program RUMP was used to simulate layer thicknesses from RBS data.

Fig. 2.3 Schematic of a typical Rutherford backscattering Spectrometry instrumentation system.

### 2.2.c Sheet Resistance Measurement

Sheet resistance of the sample is measured using a typical in line fourpoint probe configuration as shown in Fig. 2.4. In this method there are totally four probes. The spacing between the probes is 2 nm. Current passes through the outer probes in order to avoid contact resistance and the two inner probes sense the voltage and voltage drop between the two inner probes is measured. Each probe has probe resistance  $R_{p}$ , a probe contact resistance  $R_{cp}$  and a spreading resistance  $R_{sp}$  associated with it. However, these parasitic resistances can be neglected for the two voltage probes because the voltage is measured with high impedance voltmeter, which draws very little current. Thus the voltage drops across these parasitic resistances are insignificantly small. The voltage reading from the voltmeter is approximately equal to the voltage drop across the material sheet resistance. The sheet resistance is calculated from the measured values of the voltage and the current by dividing the voltage by the current and multiplying this by the correction factor which depends on the probe spacing, film thickness and the probe distance from the edge of the sample. The sheet resistance expressions can be expressed as follows:

$$R_{s} = (V/I) \times CF$$

(1)

where CF = Correction factor and V/I is the reading from the monitor, V is the voltage drop and I is the current driven through the sample.,

The resistivity of the material is calculated by using the following expression:

$$\rho = R_{\rm s} \, {\rm x} \, {\rm t} \tag{2}$$

where t = thickness of the material. This measurement was of particular interest to verify that the resistance of the alloy films after annealing was comparable to that of the as-deposited sample.

Fig. 2.4 Layout of atypical four-point probe setup. Measurements taken at ASU had a probe spacing of 2 mm. Where S = spacing between the probes, and t = thickness of the sample.

### 2.2.d Hall Measurements

In order to determine if there was any carrier inversion that occurred after microwave annealing, Hall measurement testing was performed over the samples before and after annealing.using Van der Pauw method. To do so, the samples were mounted onto a printed circuit board by making aluminum deposits for contacts, and using copper wires and silver paste to establish contacts.

The Van der Pauw method is the most common technique used to accurately measure electrical properties of a sample such as the resistivity, doping of the material whether it is p-type or n-type doped, the mobility of the majority carriers, and the sheet carrier densities. To be able to use the Van der Pauw method, the sample thickness needs to be much less than the length and width of the sample, which means, the sample needs to be 2 dimensional. To reduce errors in the measurement, the sample should be made symmetrical, most often a square shaped one. The contacts for the measurement need to be made appropriately too, and the material for contact should be chosen in such a way that an ohmic contact can be made. Silver is used to make contact with between the copper wires and the sample material. But for silicon substrates, silver cannot make an ohmic contact directly, hence aluminum was deposited using an evaporator system and masks, just at the corners of the sample, and silver can then be used to make the contact with copper wires.

21

In order to use the Van der Pauw method, the sample thickness must be much less than the width and length of the sample. In order to reduce errors in the calculations, it is preferable that the sample is symmetrical. There must also be no isolated holes within the sample. From the top left corner of the sample, if the contacts are numbered 1 to 4 in a counter-clockwise direction as seen in Fig. 2.5, current is made to flow along one edge of the sample (along the 1-2 side), and voltage is noted on the other edge (along the 3-4 side).

Fig. 2.5 Sample labeling for the contacts made to perform van der Pauw Hall measurements.

The ratio of the voltage  $V_{34}$  and  $I_{12}$  gives the resistance in the material

$$R = \frac{V_{34}}{I_{12}}$$

(3)

Hall measurements, as the name suggests, make use of the Hall effect in electrical characterization of the material. When electrons flow through a magnetic field, a force called Lorentz force is exerted on them which depends on the velocity of their motion in the field. The force is maximum when the field is perpendicular to the motion of the electrons, and is given by

$$F_{L} = q.\upsilon.B \tag{4}$$

where q = the charge on the particle in coulombs

$\upsilon = velocity$

B = the strength of the magnetic field (Wb/cm<sup>2</sup>)

Applying current on a semiconductor material results in a steady state flow of electrons within the material, with a velocity given by

$$\upsilon = \frac{1}{n_m \, \mu_m \, q} \tag{5}$$

where n = electron density

*A* = cross-sectional area of the material

$q = 1.6 \times 10^{-19}$  coulombs

The force leads to accumulation of charges along an edge and creates an electric field induced produce accumulation of electrons along an edge, and the hall voltage can be directly extracted from this field, given by

$$V_{\rm H} = \omega \in$$

(6)

=  $\frac{IB}{\rm nqd}$  d=depth of the material

=  $\frac{IB}{\rm n_s q}$

Hence, we can obtain the sheet density  $n_s$  from the hall voltage. From previously obtained resistivity measurements, sheet resistance of the material is known from which the mobility of the material is given by

$$\mu = \frac{1}{n_s q R_s} \tag{7}$$

Finally the resistivity of the material is given by

$$\rho = \frac{1}{n_m \, \mu_m \, q} \tag{8}$$

where  $n_m$  = doping level of majority carrier

$\mu_m$  = mobility of the majority carrier

Seen in Fig. 2.6 below is the setup for the Ecopia HMS 3000 Hall measurement system used in our characterization methods, for which a magnet of 0.98 Tesla was used. To recover the measurements, the magnet was aligned in N-S, S-N directions.

Fig. 2.6 Ecopia HMS-3000 Hall Effect Measurement System used at ASU (Courtesy: CSSS, ASU).

# 2.2.e Cross-section Transmission Electron Microscopy and Focused Ion Beam Milling

Focused Ion Beam milling or FIB milling was performed on the samples, to lift off a nanoscale dimension of the specimen before performing a cross-section transmission electron microscopy (XTEM) on them. Highly energetic ion beams are impinged onto the sample, at an angle of 52°. The beam has sufficient energy to lift off a portion of the sample to create a nanospecimen. The equipment has an electron gun that ensures that the properties of the material are not altered. Highly energy Ga is used to form the focused ion beam. The mechanism can be programmed to ensure which part of the sample needs to be sputtered out to form a specimen sample. The facility has an inbuilt scanning electron microscope to monitor the lift off process in real time [37]. The schematic of the FEI 835 focused-ion beam tool with a gallium ion-source is seen in the Fig.2.7.

Fig. 2.7 FEI 835 focused-ion beam tool with a Ga ion-source used at ASU

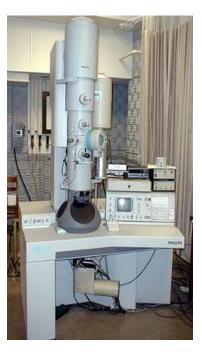

A Philips CM200 FEG TEM operated at a voltage of 200 kV was used to perform cross-sectional transmission electron microscopy on the specimen sample to observe the structure of the material. Seen below is a picture of the TEM available at Arizona State University..

Fig. 2.8 Philips CM200 FEG TEM used at ASU (courtesy CSSS)

# 2.2.f Secondary Ion Mass Spectroscopy

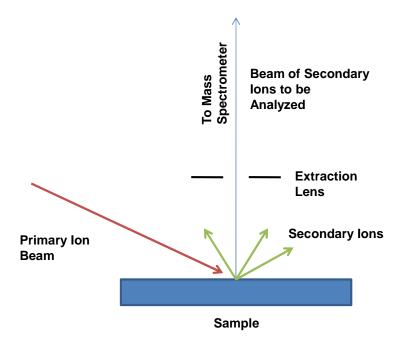

Secondary ion mass spectrometry (SIMS) is a surface analysis technique that can help determine the composition of materials. A primary ion beam is focused onto the sample, and secondary ions ejected are collected. These secondary ions are analyzed are captured by a mass spectrometer to determine the composition of the surface. The yield in terms of time collected by the analyzer is calibrated in terms of concentration of atoms across the depth of the sample. Seen below is a schematic of the direction of focused beam, and placement of the analyzer with respect to the sample surface, to capture the secondary ions.

Fig. 2.9 Mechanism of SIMS analyzer

Due to the interaction of the beams with the surface, the upper layers of the sample can get amorphized, some of the atoms of the primary beam can get implanted in the surface of the sample, apart from secondary particles being ejected from the sample. The samples ejected can be neutral as well as positively and negatively ionized. The secondary ions from the sample are extracted by an electric field applied in the region between the sample and an extraction lens. The ions get accelerated in the presence of this field towards a calibrated mass spectrometer. The ions are sorted based on the mass and energy and pass through an ion detector which can be a Faraday cup, where the yield count is obtained. The rate of the yield can provide information about the composition of the material. The SIMS technique is useful for all elements except noble gases since they don't ionize easily.

### 2.3. Device Characterization (Thin Film Transistor Analysis)

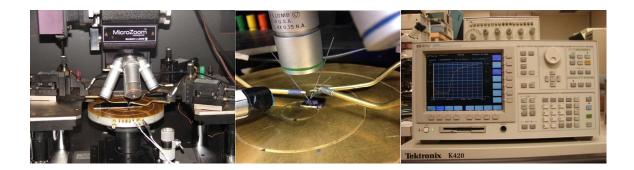

Device characteristics such as drain current *vs.* gate voltage (transfer characteristics), and drain current *vs.* drain voltage (output characteristics) can be obtained by the HP 4155 B Semiconductor Parameter Analyzer. Setup connected A three probe station in a light tight setup and a stage with thermal control are employed for aging the TFT (under light, temperature, and bias stresses). The setup used can be seen in Fig. 2.10 below.

# Fig. 2.10 Probe station, thermally controlled stage, and HP 4155 B Semiconductor Parameter Analyzer

Crucial transistor parameters such as mobility, subthrehsold swing, and *on* voltage are extracted from the transfer characteristics. A Matlab code is used for calculating the mobilities as follows:

$$\mu = \frac{g_{m}(=\partial I_d / \partial V_g)}{(W / L)C_{ox}V_d}$$

(9)

Aging conditions used in this research are a) illumination stress testing under wavelengths within the visible range of the spectrum, b) thermal stressing at 20 °C, 50 °C, and 80 °C, and c) bias stress testing un der gate voltages of ± 20 V, and drain voltages of 0, 20 V. A combination of conditions a and c, and b and c are used to understand the effect of extreme stresses towards driving the transistors into extreme degradation or even failure.

#### Chapter 3

# DOPANT ACTIVATION AND DIFFUSION PROFILE OF ARSENIC IMPLANTED SILICON

#### 3.1. Introduction

To perform quick regrowth or dopant activation by post implantation processing, the semiconductor is intentionally adulterated with additional dopant or metal atoms [38] which act as localized heating spots when annealed, raising to higher temperatures quicker than the semiconductor atoms due to their specific heat properties and Fermi level effects. Regrowth rate becomes greater with temperature, and hence shorter times suffice for recrystallization. Over the years there has been success in the development of processes which achieve this high temperature in shorter hours, and some even in seconds (*e.g.*, RTA), but without adulterating the sample in order to do so. In this study we have used microwave annealing (by using a SiC susceptor/assistor) to achieve a high quality crystalline Si layer in much shorter times, and have compared it against the samples treated using RTA, to verify the reduced extent of end-of-range diffusion. This shallower dopant profile over RTA confirms the potential use of susceptor assisted microwave annealing for dopant activation and solid phase regrowth. The assistor, as the name suggests, is used to supply additional heat to the sample for it to reach the desired temperature range in a shorter time. This study discusses the mechanism of this heat supply, and the quality of the results produced, if they are better than the results obtained from methods mentioned before.

### 3.2. Experimental procedure

The base samples are p-type boron doped, 100  $\Omega$ -cm (100) orientated silicon wafers cleaned using the Radio Corporation of America procedure. Eaton Nova NV10-180 batch process ion implanter was used to implant the cleaned Si wafers. Ion implantation was performed while orienting the wafers at 7° with respect to the normal to the incident beam and with a 45° plane twist, so that ion channeling can be minimized. One set of wafers was implanted at room temperature (RT) using 30 keV As<sup>+</sup> ions and a dose of 5×10<sup>14</sup> As<sup>+</sup> cm<sup>-2</sup>. Another set of wafers was implanted using 30 keV As<sup>+</sup> ions and a dose of 1×10<sup>15</sup> As<sup>+</sup> cm<sup>-2</sup> dosage. The last set of samples was implanted with a dose of 180 keV 1×10<sup>15</sup> As<sup>+</sup> cm<sup>-2</sup> ions. Microwave annealing of different dosage arsenic implanted Si samples was done in a single-frequency (2.45 GHz), 2.8×10<sup>4</sup> cm<sup>3</sup> cavity applicator microwave system equipped with a 1300 Watt magnetron source. The anneal times ranged between 40-100 seconds for each sample type. A Raytek Compact MID series pyrometer with a spectral response of 8–14 µm was used to monitor the near surface temperature. The emissivity for the samples was adjusted by careful calibration of the temperature read by the pyrometer against the temperature monitored by a thermocouple. For the arsenic implanted samples, the surface temperatures ranged 620-680 °C

lon implantation with concentrations and energies such as of the samples in our study causes implant damage. Ion channeling experiments were conducted to compare the damage in unannealed samples as opposed to processed samples, and to ascertain if the microwave annealing could repair damage of this extent. Rutherford backscattering spectrometry (RBS) was used to quantify the implant damage, and a 2.0 MeV He<sup>+</sup> analyzing beam for ion channeling. Samples were analyzed in random and [001] channeled orientations. He<sup>+</sup> ions were collected using a solid state detector, positioned 13<sup>o</sup> from the incident beam. The software program RUMP was used to simulate layer thicknesses from RBS data.

To test for any electrical dopant activation, the samples were placed face up under an in-line 4 point probe reading out to a 100 mA Keithley 2700 digital multimeter. The sheet resistances ( $R_{sh}$ ) of the samples were carefully tabulated for every process time. In order to determine if there was any carrier inversion that occurred after microwave annealing, Hall measurement testing was performed over the samples before and after annealing using Van der Pauw method. To do so, the samples were mounted onto a printed circuit board by making aluminum deposits for contacts, and using copper wires and silver paste to establish contacts. Secondary ion mass spectroscopy (SIMS) was performed to capture the secondary As<sup>+</sup> ions from the sample across its depth. The results observed as a function of the yield with time were calibrated to give a measure of the density of As<sup>+</sup> across the depth of the sample. The plot of As<sup>+</sup> density as a function of Si depth gives a measure of the extent of diffusion of the dopant for the microwave annealed samples and for RTA annealed samples.

#### 3.3. Results

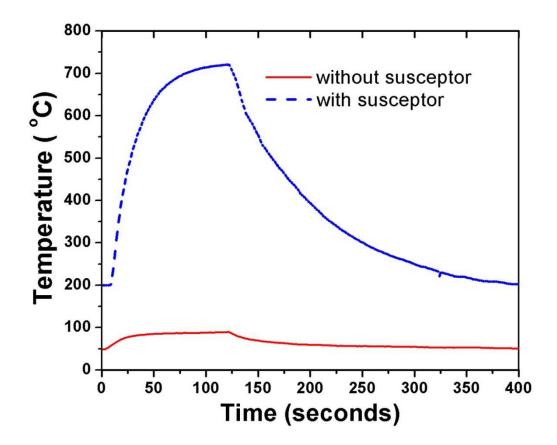

The anneal time in the study is defined as the duration between when the microwave is switched on and when the microwave is turned off. The temperature profile of the samples suggests that stand alone microwave heating is not sufficient for the samples to reach the required temperatures of around 600 °C as mentioned earlier, since *a*-Si cannot absorb microwave energy at low temperatures [16], and supports our incentive of using an additional heating material in the setup to enable the samples to absorb the microwave radiation. Inspection of Fig. 3.1 reveals how microwave radiation assisted by the alumina coated silicon carbide (SiC-alumina) susceptor [16,39], allows for rapid heating and confirms that microwave annealing without a susceptor does not help the sample obtain a high temperature.

34

Fig. 3.1 Temperature vs Time profile of As implanted Si with and without susceptor

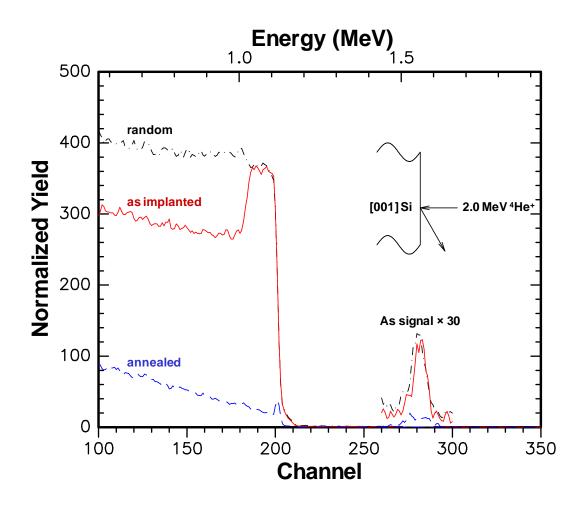

The spectra *random* and *as-implanted* in Fig. 3.2 present RBS results obtained from the as-implanted samples in a random orientation and a [001] channeling orientation, respectively. The energetic arsenic ions create a thin damaged Si layer and amorphize the crystalline Si. Both the plots show the lattice damage due to ion implantation, and also a magnified (× 30) As peak around channel number 280 [39], that confirms arsenic is located off the lattice sites instead of at the substitutional sites [20]. A comparison of the normalized yield of random

spectra gives the order of lattice damage. The factor is denoted by  $\chi_{min}$  [40]. Channeling spectrum *annealed* presents ion channeling results of the samples in a [001] channeling orientation after 40 sec microwave annealing. The  $\chi_{min}$  for annealed is 0.11 implying that the lattice damage was repaired to a great extent. The ion channeling yield of a 70 sec annealed sample (not shown), also has a  $\chi_{min}$  of around 0.11 confirming that the improvement in lattice damage repair is insignificant over a 40 sec microwave anneal. The results signify that the dopant atoms are now essentially located in substitutional sites instead of off-lattice sites, as in the as-implanted channeled spectrum in Fig. 3.2. This repair of lattice damage, and dopant relocation, are key factors that lead to dopant activation and reduced sheet resistance of the arsenic implanted Silicon samples. The spectra of 180 keV arsenic implanted samples, confirms deeper lattice damage, and thicker damaged surface layer. However great the damage, a 40 second anneal would still suffice to repair the lattice implant damage, and distribute the dopant atoms to substitutional sites in the lattice.

Fig. 3.2. Ion channeling results of As<sup>+</sup> implanted Si: Dotted *random* represents ion channeling of 180 keV 1x10<sup>15</sup> as-implanted As<sup>+</sup> sample in random orientation. Solid line *as implanted* represents ion channeling of as implanted As<sup>+</sup> in channeling orientation. Dotted *annealed* represents ion channeling of 180 keV 1x10<sup>15</sup> cm<sup>-2</sup> arsenic implanted Si annealed for 40s, in channeling orientation. The As signal represented in the analysis has been enhanced 30 times for *random*, *as implanted*, and *annealed* spectra, and follows the same legend.

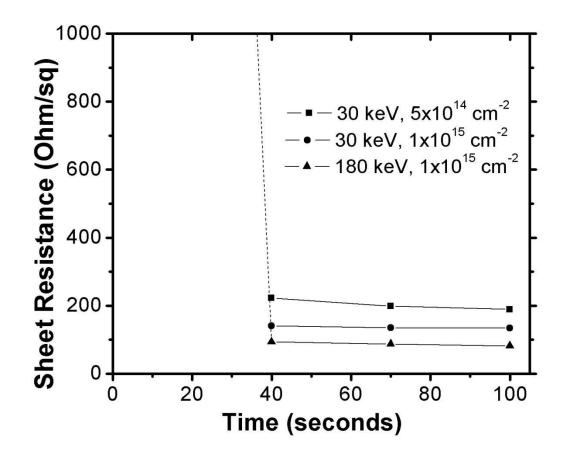

Analysis of sheet resistance values of annealed samples against readings from the unannealed samples shows that almost complete dopant activation was achieved within a processing time of 40 sec, beyond which there is no significant improvement, as seen in Table 1.

| Implant<br>energy<br>(keV) | Implant dose<br>(1 × 10 <sup>15</sup> cm <sup>-2</sup> ) | Sheet Resistance (Ohm/sq) for different microwave anneal times |            |            |             |  |

|----------------------------|----------------------------------------------------------|----------------------------------------------------------------|------------|------------|-------------|--|

|                            |                                                          | as-implanted                                                   | 40 seconds | 70 seconds | 100 seconds |  |

| 30                         | × 0.5                                                    | overflow                                                       | 221        | 198        | 188         |  |

| 30                         | × 1                                                      | overflow                                                       | 140        | 134        | 133         |  |

| 180                        | × 1                                                      | overflow                                                       | 93         | 86         | 81          |  |

# Table 1 Sheet Resistance measurements over different anneal times

This applies to all three samples of different dosages and energies that were included in the study. As seen in the table, before microwave anneal, the 4 point probe reads *overflow* which implies the samples are non-conductive or that their sheet resistance ( $R_{sh}$ ) is beyond the order of mega Ohm/sq. The Fig.3.3 below shows the pattern of sudden reduction is  $R_{sh}$ , which saturates for greater annealing times.

Fig. 3.3 Sheet Resistance measurements of the different dosage and implantation energy As implanted Si at different anneal times.

The Hall measurements show the inversion of carriers from p-type before annealing, which is from the heavily boron doped substrate, to being n-type from the arsenic that was implanted onto Si samples. Due to the heavy doping that causes degenerate sheet concentration values, ion scattering becomes dominant in the surface, reducing the mobilities after annealing, which were otherwise expected to be high. Table 2 summarizes the resistivities, sheet and bulk concentrations, and mobilities of 30 keV  $1 \times 10^{15}$  As<sup>+</sup> cm<sup>-2</sup> and 180 keV  $1 \times 10^{15}$  As<sup>+</sup> cm<sup>-2</sup> implanted Si samples. The values of the 30 keV  $1 \times 10^{14}$  As<sup>+</sup> cm<sup>-2</sup> fell between those of the sample variety *A* and *B*, but were not discussed in the table.

| Sample                                   | Resistivity<br>(Ω cm) | Carrier type | Sheet<br>concentration<br>(# cm <sup>-2</sup> ) | Bulk<br>Concentration<br>(# cm <sup>-3</sup> ) | Mobility<br>(cm <sup>2</sup> /V-<br>sec) |

|------------------------------------------|-----------------------|--------------|-------------------------------------------------|------------------------------------------------|------------------------------------------|

| A and B as-<br>implanted Backside        | 45                    | р            | 6.8×10 <sup>12</sup>                            | 1.7×10 <sup>14</sup>                           | 530                                      |

| Sample A as-implanted Front              | 1.3×10 <sup>-3</sup>  | р            | 1.7×10 <sup>14</sup>                            | 3.5×10 <sup>19</sup>                           | 235                                      |

| Sample A<br>40 second<br>annealed Front  | 2.8×10 <sup>-3</sup>  | n            | 8.3×10 <sup>14</sup>                            | 1×10 <sup>20</sup>                             | 53                                       |

| Sample A<br>100 second<br>annealed Front | 2.7×10 <sup>-3</sup>  | n            | 7.65×10 <sup>14</sup>                           | 1.53×10 <sup>20</sup>                          | 61                                       |

| Sample B<br>as-implanted Front           | 13×10 <sup>-3</sup>   | р            | 9.25×10 <sup>13</sup>                           | 3.7×10 <sup>18</sup>                           | 120                                      |

| Sample B<br>40 second<br>annealed Front  | 2.4×10 <sup>-3</sup>  | n            | 9.95×10 <sup>14</sup>                           | 4.0×10 <sup>19</sup>                           | 65                                       |

| Sample B<br>100 second<br>annealed Front | 2.1×10 <sup>-3</sup>  | n            | 8.2×10 <sup>14</sup>                            | 3.3×10 <sup>19</sup>                           | 89                                       |

Table 2Hall measurement values for **A**: 30 keV  $1 \times 10^{15}$  As<sup>+</sup> cm<sup>-2</sup> and **B**: 180 keV  $1 \times 10^{15}$  As<sup>+</sup> cm<sup>-2</sup> implanted Si

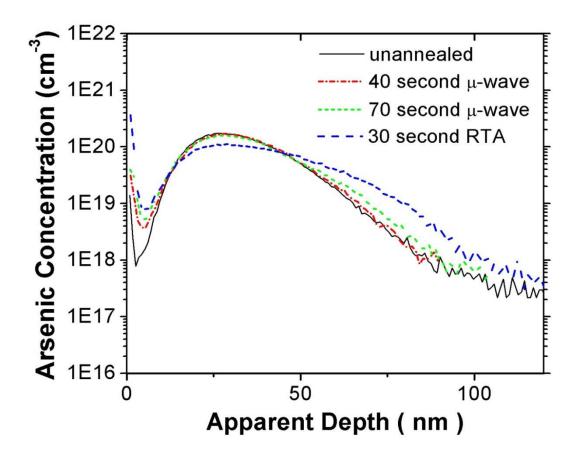

To assess the impact of susceptor-assisted microwave annealing on dopant diffusion, SIMS analysis was performed on a 900 °C RTA sample, annealed for 30 seconds, apart from the microwave annealed samples. As seen in Fig. 3.4, both 40 and 70 seconds microwave annealing on the samples shows minimal dopant diffusion across the depth. RTA on the sample shows greater

dopant diffusion possibly as a result of energizing the As<sup>+</sup> to diffuse into the sample.

Fig. 3.4 SIMS profile of 30 keV 5×10<sup>14</sup> As<sup>+</sup> impanted Si annealed under different conditions

#### 3.4. Discussion

The cumulative effect of a few phenomena is responsible for the effectiveness of susceptor-assisted microwave annealing. These can be categorized into the effect of microwaves, and the effect of the susceptor. Microwaves supply sufficient energy to surmount the high activation energy

needed for lattice damage repair and bring about dopant activation, without causing dopant diffusion, all in a short duration. For dopant activation of arsenic to be achieved, the As need to replace Si in the substitutional sites. Our ion channeling results also show that the dopant atoms now occupy substitutional lattice sites suggesting successful dopant activation.

The mechanism underlying the heating of the sample is microwave power loss. Microwave power converts into heat based on the property of the material defined as effective loss factor, which comprises conduction and polarization losses [41]. Depending on the dielectric constant of the sample, the power absorbed and the depth of absorption of the microwave radiation vary [42]. The power thus absorbed is converted into heat based on the specific heat capacity value of the sample. The sample in discussion is arsenic doped Si, As having a  $C_P$  of 326 J/Kg-K, and Si having a  $C_P$  of 710 J/Kg-K.

Apart from the dielectric constant, the dielectric loss factor of a material is another property that decides its absorption capability. Materials with high dielectric loss factor can absorb microwave radiation better. Thus, considering only the effect of microwave radiation, which provides volumetric heating, the power absorbed per unit volume is given by equation 1 as

$$P_{abs} = \sigma_{eff} |E|^{2}$$

=  $\omega \in_{0} \in_{eff}^{"} |E|^{2}$  (1)

=  $\omega \in_{0} \in_{r}^{"} \tan \delta |E|^{2}$

where *E* is the magnitude of the internal electric field,  $\in_{eff}$  is the relative effective dielectric factor,  $\in_0$  is the permittivity of free space,  $\omega$  gives the microwave frequency,  $\sigma_{eff}$  is the total effective conductivity,  $\in_r$  is the relative dielectric constant, and  $tan\delta$  is the energy loss required to store a given quantity of energy [43]. The above relation takes into effect the ionic conduction losses and dipole polarization losses which comprise the overall microwave loss mechanism responsible for absorption of the microwave energy. The ionic conduction losses, also called the ohmic losses arise from the movement of the free electrons available due to the presence of the arsenic dopant atoms, and the dipole polarization losses are as a result of the interaction between the vacancies and interstitials present in the sample. The conversion of the power thus absorbed, into heat based on the material properties follows the relation [44]

$$\mathsf{P} = m \, C_P \, \frac{\Delta T}{\Delta t} \tag{2}$$

where m is the mass. In terms of the dielectric properties of the material, the change in temperature of the sample with time would be [42]

$$\frac{\Delta T}{\Delta t} = \frac{\omega \in_0 \in_r^{"} \tan \delta |E|^2}{\rho_{mass} C_P}$$

(3)

For a given material, the factor that can vary at a fixed frequency is  $tan\delta$  [45] which is the ratio of the dielectric loss with respect to the dielectric constant. For both a-Si and c-Si this reduces with temperature, as dielectric constant rises with temperature. Hence, in the heating curves of all the samples in this study, we observe that the temperature rises fast initially, and the dielectric constant increases [46] with time, saturating the temperature, as  $tan\delta$  reduces.

Microwave radiation provides volumetric heating [43] to the sample, limiting the depth of penetration to  $D_P$  which is the depth into the sample, at which the effect of the microwave field reduces by a factor 1/e, or the power absorbed is half as much as it is at the surface of the sample.  $D_P$  is given by equation (4)

$$D_P = \frac{3\lambda_0}{8.686\pi \tan \delta \sqrt{\frac{\varepsilon_r}{\varepsilon_0}}}$$

(4)

With the extent of ion implantation damage caused by the energetic arsenic items during doping, the volumetric heating and the depth of penetration of the radiation into the sample is not sufficient to repair the damage by nucleation followed by growth. Furthermore, arsenic being a high Z material requires a higher temperature to absorb the microwaves.

The advantages of microwave radiation can be applied to our As implanted Si samples and other high Z implanted samples, by including an additional assisting system, that can help the sample obtain a temperature where it can absorb the microwave radiation and further convert the power to heat. The susceptor surely pronounces its effect in the arsenic implanted Si samples, by acting as a source of additional heat, but does not negate the underlying impact of microwave radiation, hence making it an assisted annealing method.

### 3.5. Conclusion

Through this study, we were able to elucidate in detail how microwave loss mechanisms, high activation energies, and the susceptor, all combine to achieve an electrically active arsenic doped Si thin film layer. Susceptor assisted microwave annealing also proved better than the widely used RTA method, since it led to very low dopant diffusion across the film. With some more improvements, this technique would be a promising replacement in the semiconductor industry.

#### Chapter 4

# RECRYSTALLIZATION OF ARSENIC AND as-IMPLANTED SILICON 4.1. Introduction

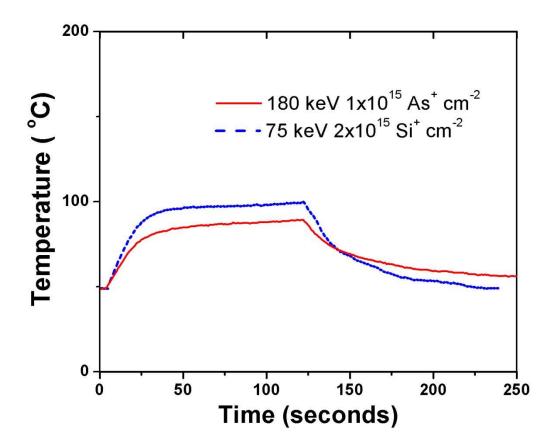

Inorder to compare the temperature profiles of a doped sample versus self implanted Si sample without the influence of a susceptor, an as-implanted Si with 75 keV implantation energy, and  $2 \times 10^{15}$  cm<sup>-2</sup> Si<sup>+</sup> dosage was also chosen. Figure 4.1 shows a typical plot of temperature as a function of anneal time for a) 180 keV,  $1 \times 10^{15}$  As<sup>+</sup> cm<sup>-2</sup> implanted Si sample and b) 75 keV,  $2 \times 10^{15}$  cm<sup>-2</sup> as implanted Si<sup>+</sup>, both samples annealed for 2 minutes without a susceptor. The anneal time in the study is defined as the duration between when the microwave is switched on and when the microwave is turned off. The temperature profile of these samples suggests that stand alone microwave heating is not sufficient for them to reach the required temperatures of around 600 °C as mentioned earlier since *a*-Si cannot absorb microwave energy at low temperatures [16], and necessitates the use of an additional heating material in the setup to enable the samples to absorb the microwave radiation.

Fig. 4.1 Temperature vs time profile of As implanted Si and as-implanted Si without a susceptor.

Fig. 4.2 Temperature vs time profile of As implanted Si and asimplanted Si witht a susceptor.

The samples in discussion are arsenic doped Si and as-implanted Si, As having a  $C_P$  of 326 J/Kg-K, and Si having a  $C_P$  of 710 J/Kg-K. But an atom of Si heats to a higher temperature than an atom of arsenic for the same power absorbed, since Si weighs lesser than arsenic, and the  $mC_P$  (Si) <  $mC_P$  (As). The effect of  $C_P$  on heating rate without the assistance of a susceptor can be noticed in Fig.4.1. In order to create the same extent of damage as 180 keV 1×10<sup>15</sup> cm<sup>-2</sup> arsenic implanted Si, the as-implanted Si was formed by implanting with 75 keV 2×10<sup>15</sup> cm<sup>-2</sup> Si<sup>+</sup>. The dosage [47] of Si<sup>+</sup> chosen produced the same depth of the

damage layer as did the As<sup>+</sup> implantation, and the energy required was in correspondence with the TRIM [48] simulated implant projection range ( $R_P$ ) to provide a similar depth of damage within the sample. Figure 4.1 compares the heating rate of both these samples without a susceptor, and confirms our theory that with the same damage and negating the impact of the susceptor, the as-implanted Si<sup>+</sup> heats faster than as-implanted As<sup>+</sup>. The results presented in the figure also support our argument that materials with higher *Z* require assisted heating. For the same samples, when a susceptor was included in the anneal setup , the heating rates overlapped, suggesting that the effect of higher *Z* and differences in the factor  $mC_P$  have been overridden by the heat provided by the susceptor, as seen in Fig.4.2. The dielectric properties of the susceptor are responsible for this enhanced supply of heat to the mounted samples.

# 4.2. Structural Characterization

The as-implanted As<sup>+</sup> and the microwave annealed samples were characterized using several methods to test for dopant activation and film recrystallization. A Raman line scan was performed to determine the structure of the As<sup>+</sup> implanted Si pre and post microwave annealing. An argon laser with an excitation wavelength of 532 nm is focused onto the samples mounted underneath the optical microscope, through an Olympus 100×0.8 NA objective. The spectra from the sample are reflected into a Sopra 2000 2m double spectrometer by a 50% beam-splitter. A 532 nm notch filter blocks any scattered

light from the laser. The spectrum is dispersed and collected into a Princeton CCD Camera with an energy dispersion of 60pixels/cm. The Raman spectra collected from the CCD is calibrated as a function of intensity that depends on the time of exposure, against the relative wavenumber [35].

Ion channeling experiments were carried on for as-implanted Si samples with and without susceptor annealed for different times to verify once again if anneal without susceptor is capable of damage repair, and to compare the lattice damage repair by anneal with susceptor.

To observe the microstructure of the sample before and after annealing, cross-section transmission electron microscopy (XTEM) was performed using a Philips CM200 FEG TEM operated at a voltage of 200 kV. Enhancement of defect contrast was provided by 220 bright-field and dark-field imaging. TEM samples were prepared using a FEI835 focused-ion beam tool with a gallium ionsource.

# 4.3. Results