# Evaluation and Characterization of Silicon MESFETs in Low Dropout Regulators

by

Bo Chen

A Thesis Presented in Partial Fulfillment of the Requirements for the Degree Master of Science

Approved April 2013 by the Graduate Supervisory Committee:

Trevor Thornton, Chair Bertan Bakkaloglu Michael Goryll

ARIZONA STATE UNIVERSITY

May 2013

### ABSTRACT

The partially-depleted (PD) silicon Metal Semiconductor Field Effect Transistor (MESFET) is becoming more and more attractive for analog and RF applications due to its high breakdown voltage. Compared to conventional CMOS high voltage transistors, the silicon MESFET can be fabricated in commercial standard Silicon-on-Insulator (SOI) CMOS foundries without any change to the process. The transition frequency of the device is demonstrated to be 45GHz, which makes the MESFET suitable for applications in high power RF power amplifier designs. Also, high breakdown voltage and low turn-on resistance make it the ideal choice for switches in the switching regulator designs.

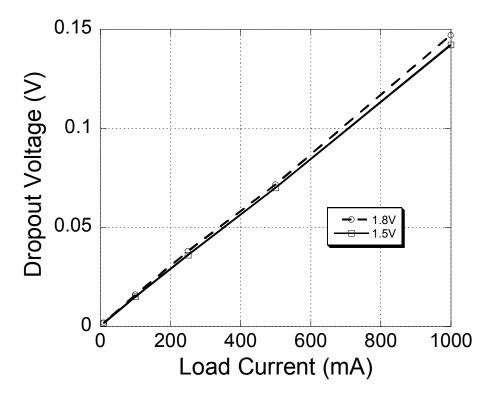

One of the anticipated applications of the MESFET is for the pass device for a low dropout linear regulator. Conventional NMOS and PMOS linear regulators suffer from high dropout voltage, low bandwidth and poor stability issues. In contrast, the N-MESFET pass transistor can provide an ultra-low dropout voltage and high bandwidth without the need for an external compensation capacitor to ensure stability. In this thesis, the design theory and problems of the conventional linear regulators are discussed. N-MESFET low dropout regulators are evaluated and characterized. The error amplifier used a folded cascode architecture with gain boosting. The source follower topology is utilized as the buffer to sink the gate leakage current from the MESFET. A shunt-feedback transistor is added to reduce the output impedance and provide the current adaptively. Measurement results show that the dropout voltage is less than 150 mV for a

1A load current at 1.8V output. Radiation measurements were done for discrete MESFET and fully integrated LDO regulators, which demonstrate their radiation tolerance ability for aerospace applications.

# TABLE OF CONTENTS

|                                                  | Page |

|--------------------------------------------------|------|

| ST OF FIGURES                                    | vi   |

| ST OF TABLES                                     | X    |

| HAPTER                                           |      |

| 1. INTRODUCTION                                  | 1    |

| 1.1 MESFET Device Structure and Fabrication      | 1    |

| 1.2 MESFET Operation and Characterization        | 6    |

| 1.2.1 Threshold Voltage                          | 8    |

| 1.2.2 Device Operation                           | 10   |

| 1.2.3 Leakage Current and Temperature Dependence | 11   |

| 1.2.4 RF Performance                             | 12   |

| 1.3 Brief Summary of the MESFET Applications     | 16   |

| 1.4 Conclusion                                   | 18   |

| 2. DESIGN THEORY OF LINEAR REGULATORS            | 19   |

| 2.1 Introduction to Linear Regulator             | 19   |

| 2.1.1 Linear Regulator                           | 19   |

| 2.1.2 Switching Regulator                        | 20   |

| 2.2 Linear Regulator Specifications              | 22   |

| 2.2.1 Load Regulation                            | 22   |

| CHAPTER     |                                      | Page |

|-------------|--------------------------------------|------|

|             | 2.2.2 Line Regulation                | 23   |

|             | 2.2.3 Dropout Voltage                | 24   |

|             | 2.2.4 Power Supply Rejection         | 25   |

|             | 2.2.5 Transient Response             | 26   |

| 2.3 I       | PMOS Linear Regulator                | 27   |

| 2.4 1       | NMOS Linear Regulator                | 32   |

| 2.5 (       | Conclusion                           | 34   |

| 3. DESIGN ( | OF N-MESFET LDO REGULATOR            | 36   |

| 3.1 1       | N-MESFET Regulator and Design Issues | 36   |

| 3.2 I       | Error Amplifier and Buffer Design    | 39   |

|             | 3.2.1. Error Amplifier (EA) Design   | 39   |

|             | 3.2.2 Buffer Design                  | 41   |

| 3.3 \$      | Stability Issues                     | 43   |

| 3.4 (       | Conclusion                           | 44   |

| 4. MEASUR   | EMENT OF THE N-MESFET LDO            | 45   |

| 4.1 (       | General Board Setup                  | 45   |

| 4.2 I       | DC Performance                       | 47   |

| 4.3 I       | Power Supply Rejection               | 51   |

| 4.4 I       | Radiation Measurement                | 53   |

| CHAPTER     |                             | Page |

|-------------|-----------------------------|------|

|             | 4.5 Load Transient Response | 57   |

|             | 4.5 Conclusion              | 66   |

| 5. CON      | CLUSIONS AND FUTURE WORK    | 67   |

|             | 5.1 Conclusions             | 67   |

|             | 5.2 Future Work             | 68   |

| REFERENCES. |                             | 71   |

# LIST OF FIGURES

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Cross sectional view of the n-type SOI MESFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2. Fabrication step for SOI MESFET [5].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3. 32nm SOI MESFET device Gummel plots after progressive exposure to high drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4. SOI MESFET Device Operation: (a) linear region ( $V_{GS}>V_{TH}$ , $V_{DS}\ll V_{DSAT}$ ), (b) the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| boundary between the saturation and the linear region ( $V_{DS}$ = $V_{DSAT}$ ), (c) saturation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| region ( $V_{DS} > V_{DSAT}$ ), (d)cut-off region ( $V_{GS} < V_{TH}$ ), (e) body effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5. Family of Curves (FOC) plot of a 45nm SOI MESFET with $L_{aD} = 2000$ nm,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6. Threshold voltage change due to the body effect of the device. The substrate voltage is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| change from -6V to 3V with $V_D\!\!=\!\!2V$ . The MESFET has an $L_{aD}$ = 1000nm, $L_{aS}$ =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1000nm, and $L_g = 200$ nm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7. The device operation change with temperature from -60° to 150°. The solid lines are the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| drain current while the dash ones are the gate current. The device is from 350nm SO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| process, $L_g = L_{aD} = L_{aS} = 0.6 \mu m [5]$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

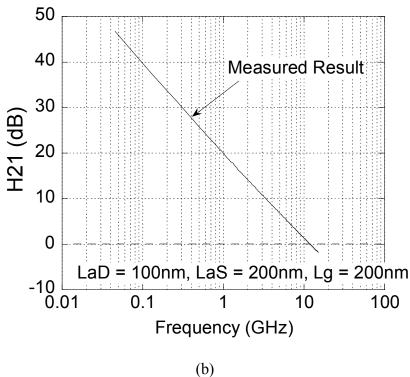

| 8. The measured $h_{21}$ parameters of the MESFETs from the IBM 45nm process: (a) $L_g$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 200nm, $L_{aS}$ = 200nm, $L_{aD}$ = 200nm, $V_{GS}$ = 0.45V, $V_{DS}$ = 2V; (b) $Lg$ = 200nm, $L_{aS}$ |

| 200nm, $L_{aD} = 1000$ nm, $V_{GS} = 0.25$ V, $V_{DS} = 4$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure                                                                                        |

|-----------------------------------------------------------------------------------------------|

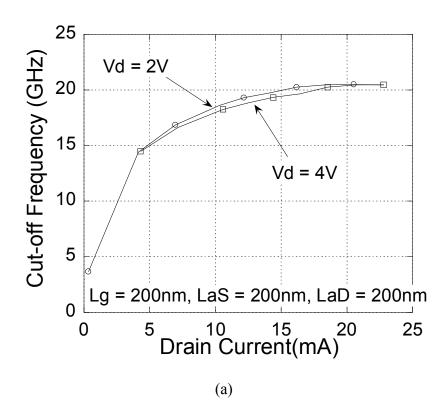

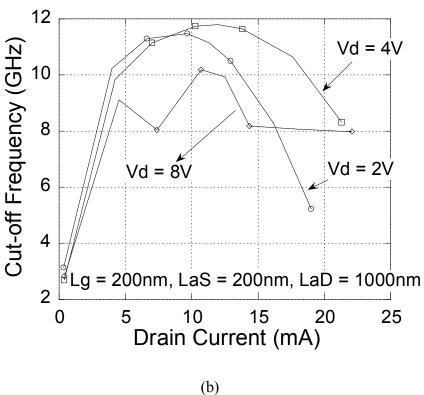

| 9. The cut-off frequency of the MESFET from the 45nm IBM process: (a) $L_g$ = 200nm, $L_{aS}$ |

| = 200nm, $L_{aD}$ = 200nm; (b) $Lg$ = 200nm, $L_{aS}$ = 200nm, $L_{aD}$ = 1000nm              |

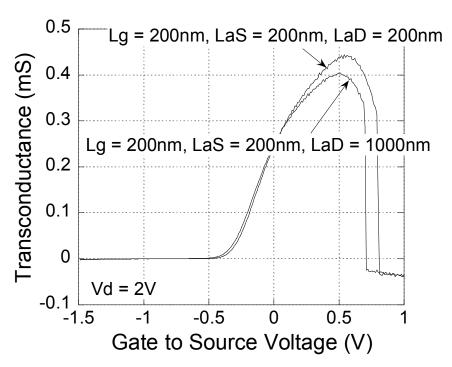

| 10. Transconductance of the MESFET from the 45nm IBM process, extracted from the              |

| Gummel plots, $V_D = 2V$ .                                                                    |

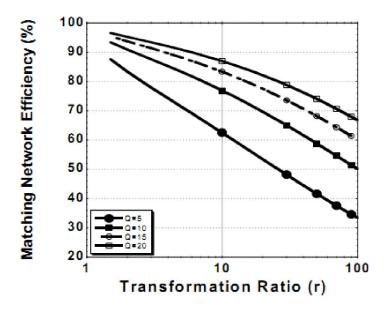

| 11. Matching network efficiency versus transformation ratio [26]                              |

| 12. Linear Regulator topology: (a) General topology. (b) One with a bandgap and feedback      |

| resistors included. 20                                                                        |

| 13. A typical architecture for a voltage mode buck DC-DC converter                            |

| 14. The typical input-output characteristic of a linear regulator                             |

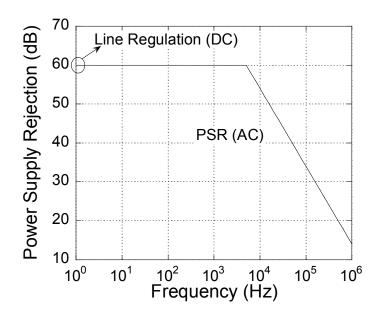

| 15. Typical PSR of the linear regulator versus frequency                                      |

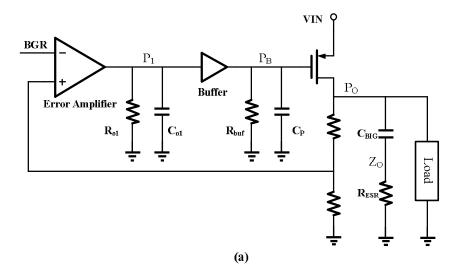

| 16. PMOS linear regulator topology: (a) External compensation using big capacitor and the     |

| Equivalent Series Resistor (ESR) (2) Internal compensation                                    |

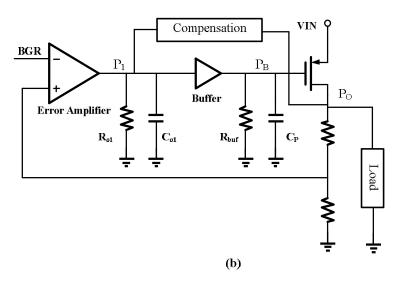

| 17. Bode plot of the closed-loop gain of the externally compensated linear regulator 30       |

| 18. Bode plot of the loop gain of the internal compensated PMOS linear regulator 31           |

| 19. NMOS linear regulator topology with internal compensation being used                      |

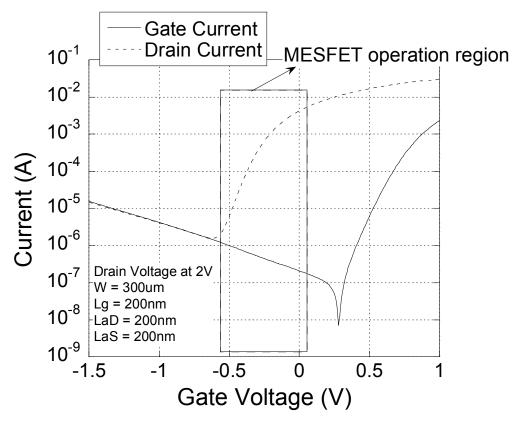

| 20. Scaled down pass device performance and the operating region                              |

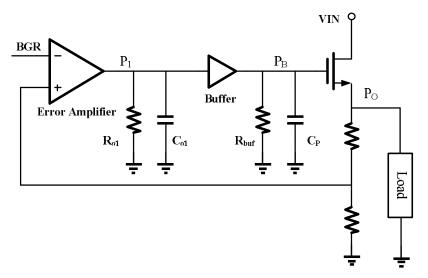

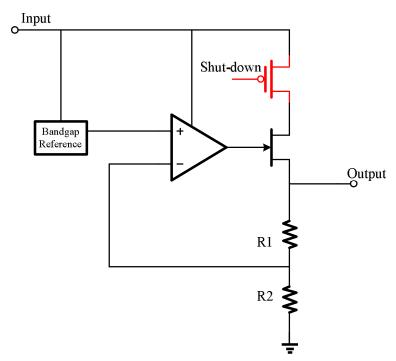

| 21. MESFET based LDO regulator with shut-down operation                                       |

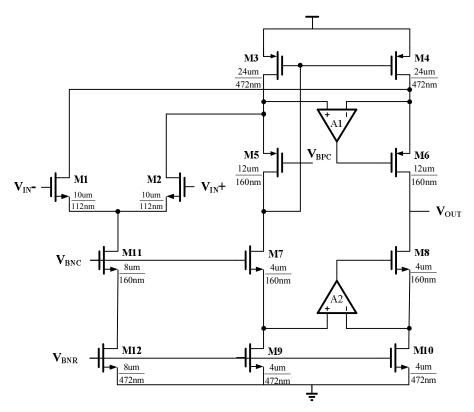

| 22. Folded cascode error amplifier with the device sizing                                     |

| Figure                                                                               | Page    |

|--------------------------------------------------------------------------------------|---------|

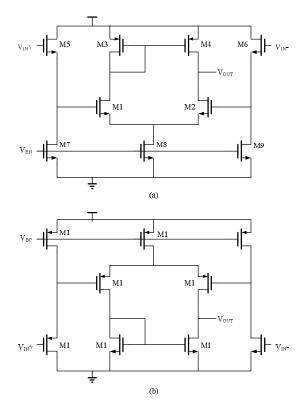

| 23. Auxiliary amplifiers used for gain boosting: (a) A1 have a NMOS input pair, (b)  | A2 has  |

| a PMOS input pair [20]                                                               | 41      |

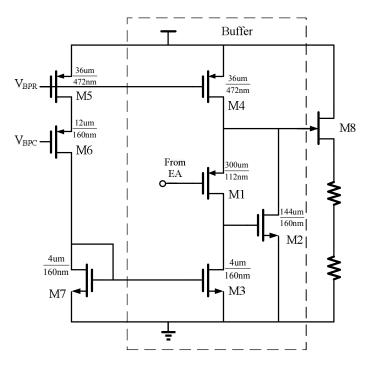

| 24. PMOS source follower and shunt feedback to improve the output impedance          | 42      |

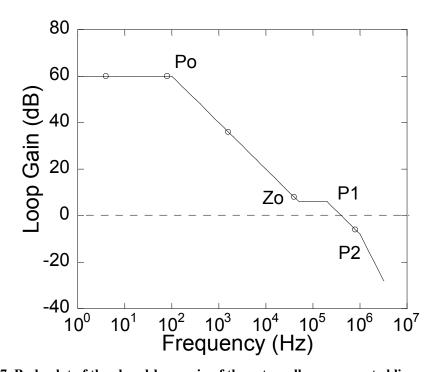

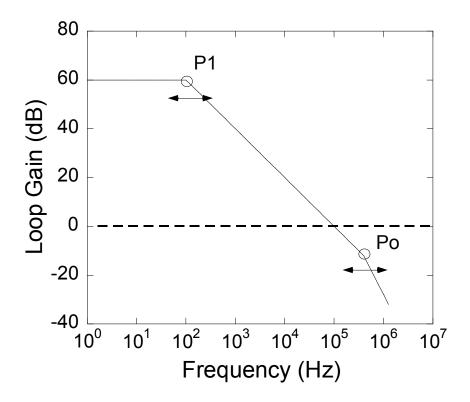

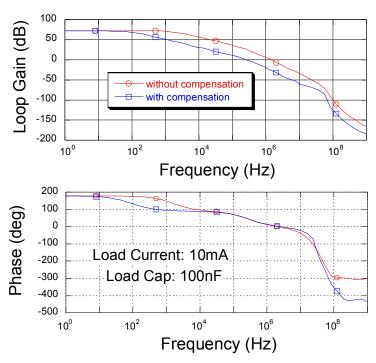

| 25. Simulation result of the bode plot of the MESFET LDO regulator with 100nF        | output  |

| capacitor and 10mA load current                                                      | 44      |

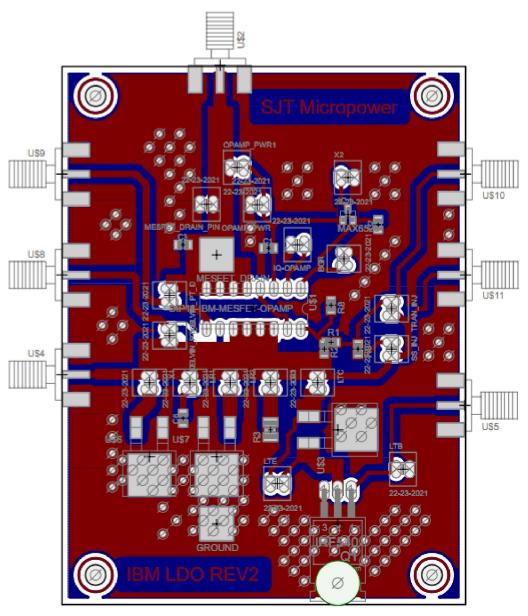

| 26. Board layout for the IBM N-MESFET linear regulator                               | 46      |

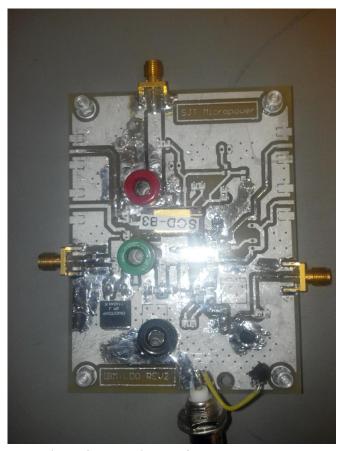

| 27. The pictures for the board setup.                                                | 47      |

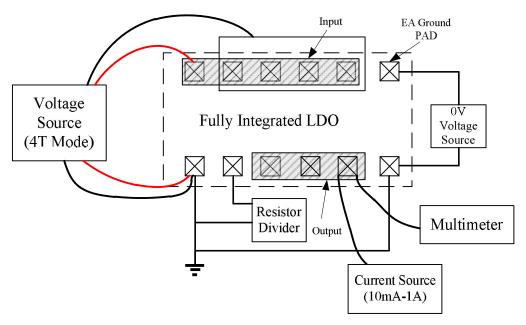

| 28. V <sub>IN</sub> -V <sub>OUT</sub> characteristic measurement setup.              | 48      |

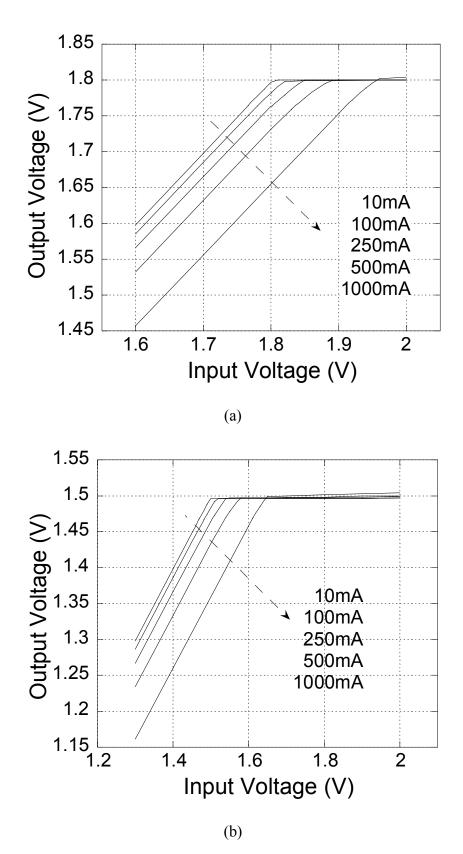

| 29. IBM LDO regulator input-output characteristic: (a) for 1.8V, (b) for 1.5V output | t49     |

| 30. Dropout voltage with load current for IBM N-MESFET LDO regulator                 | 50      |

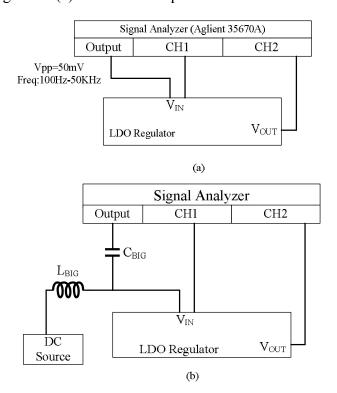

| 31. PSR Measurement setup: (a) typical setup, (b) using a large value choke and cap  | acitor. |

|                                                                                      | 51      |

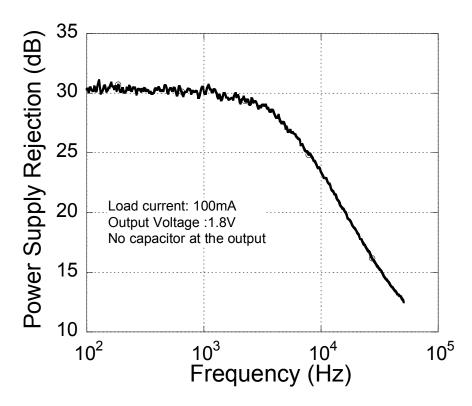

| 32. Power supply rejection as a function of frequency frequency for 1.8V outp        | ut and  |

| 100mA load current.                                                                  | 53      |

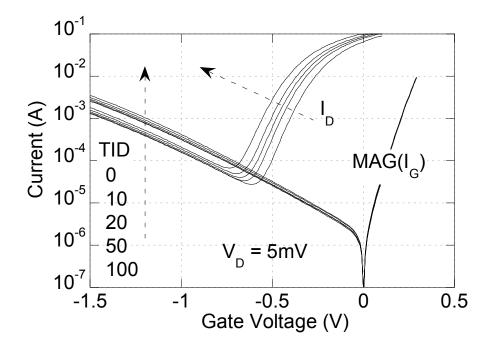

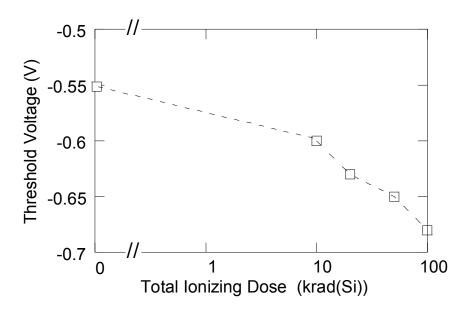

| 33. Drain and gate current versus gate voltage for different TID [25]                | 54      |

| 34. Threshold voltage of a discrete MESFET versus TID [25].                          | 54      |

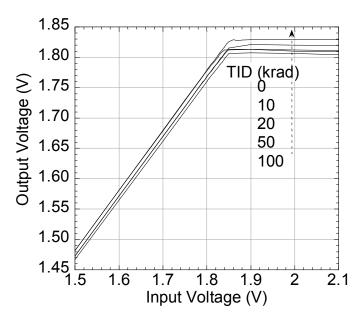

| 35. Line regulation for 100mA load current versus TID [25]                           | 56      |

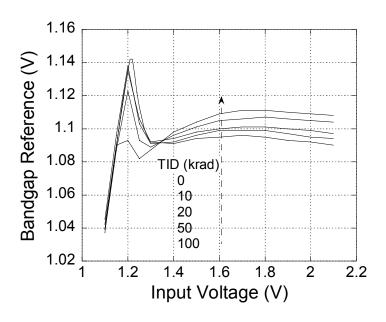

| 36. The bandgap reference voltage variation due to the radiation [25]                | 56      |

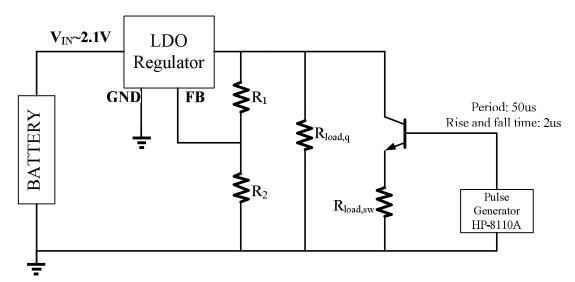

| 37. Measurement setup for the load transient response                                | 58      |

| Figure                                                                                 |

|----------------------------------------------------------------------------------------|

| 38. The connector that used to connect the output to the oscilloscope directly         |

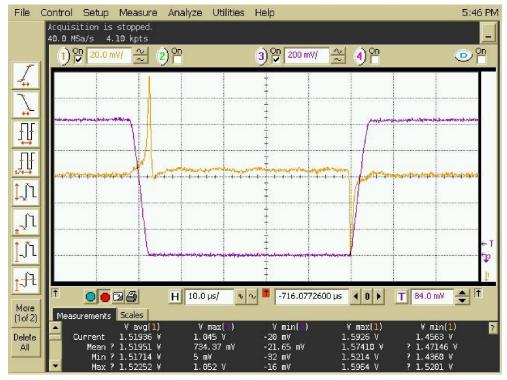

| 39. Load transient response with 0-100mA load current. The orange line shows the outp  |

| voltage and the purple line shows the voltage at the emitter of the BJT                |

| 40. Load transient response with 0-200mA load current. The orange line shows the outp  |

| voltage and the purple line shows the voltage at the emitter of the BJT                |

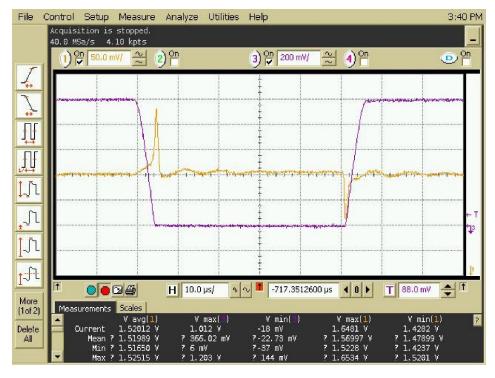

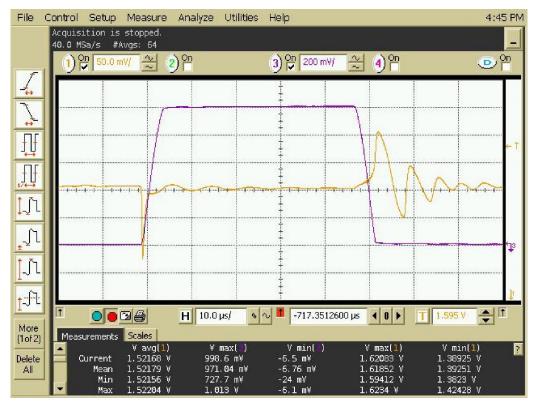

| 41. Load transient response with 0-500mA load current. The orange line shows the outp  |

| voltage and the purple line shows the voltage at the emitter of the BJT                |

| 42. Load transient response with 0-500mA load current. A 6.8 nF capacitor is connected |

| the output. The orange line shows the output voltage and the purple line shows the     |

| voltage at the emitter of the BJT                                                      |

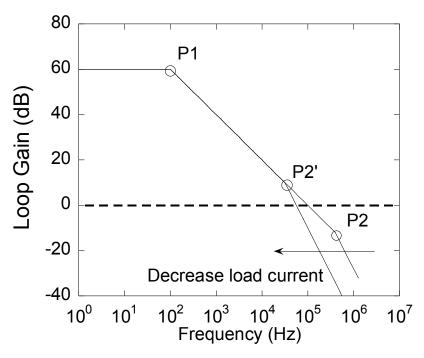

| 43. Closed loop frequency response with respect to the load current change             |

# LIST OF TABLES

| Table                                                    | Page |

|----------------------------------------------------------|------|

| Comparison between switching and linear regulators       | 22   |

| 2. Comparison between NMOS and PMOS linear regulators    | 35   |

| 3. Line and Load Regulation of the MESFET LDO Regulators | 51   |

#### CHAPTER 1

#### INTRODUCTION

Metal Semiconductor Field Effect Transistors (MESFETs) utilize a Schottky gate (metal-semiconductor) to control the device. It was first developed in 1966 [1]. Conventional MESFETs are fabricated using compound semiconductors such as GaAs and are usually used for RF and microwave applications. The research group at ASU has demonstrated that the MESFET can be fabricated on commercial partially depleted (PD) SOI CMOS processes without any changes to the process flow [2][3]. Devices on a SOI substrate have lower parasitic capacitance and leakage current compared to those on a bulk silicon substrate. It has been demonstrated that the Si-MESFETs from ASU have high breakdown voltage and over 35GHz cut-off frequency [4]. Although these Si-MESFETs cannot compete with their GaAs counterparts for high frequency performance, they can be integrated with CMOS, which will reduce the cost of certain analog circuits. In this chapter, an introduction of the PD-MESFETs will be given, including their structure, fabrication, operation and the applications.

## 1.1 MESFET DEVICE STRUCTURE AND FABRICATION

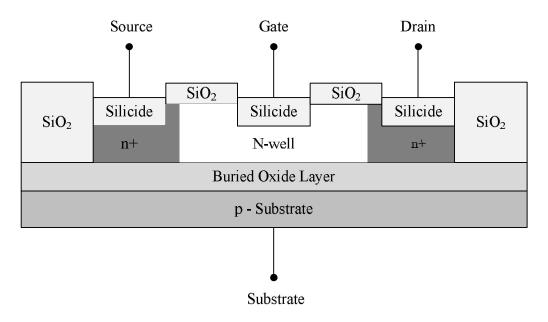

Figure 1 shows the cross-section view of the n-type PD-MESFET. Compared to a conventional GaAs three-terminal device, it has four terminals including the substrate. The n-MESFET is fabricated on an n-well since it is a majority carrier device. A Schottky gate is formed with the silicide and the lightly doped n-well. The source and drain area

are heavily doped and are also processed with silicide to reduce the contact resistance. Two spacers are inserted between the gate and source and gate and drain to prevent shorting between them. The access length is defined as the length of spacer on the source side ( $L_{aS}$ ) and drain side ( $L_{aD}$ ). The gate length ( $L_{g}$ ) is defined as the distance between the two spacers [6].

Figure 1. Cross sectional view of the n-type SOI MESFET.

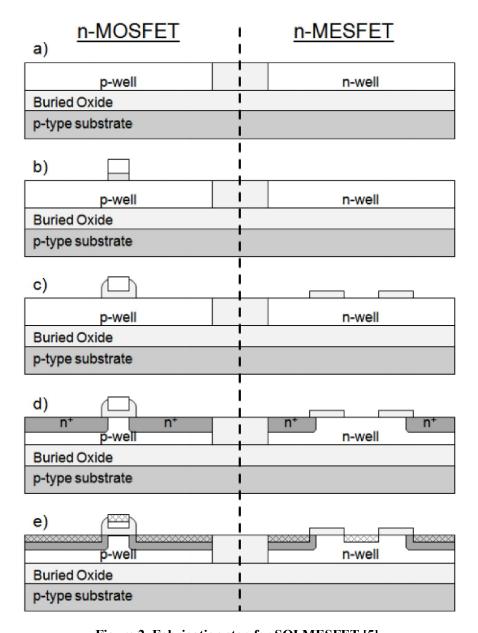

The MESFETs can be fabricated in a standard SOI process. The steps to fabricate a MESFET are the same as MOSFET until the LOCal Oxidation of Silicon (LOCOS) step, which is used to form the active region of the substrate. After the well is patterned, the gate for the MOSFET will be formed while nothing is done during this step for the MESFET except the wafer cleaning, which will make the channel slightly thinner. After that, the silicide block layer will result in silicon dioxide (SiO<sub>2</sub>) being patterned. This forms the Schottky gate and also the spacer regions between the gate and the source/drain.

The oxides that are not required for the sidewall spacer and the silicide block region will be removed. Ion implantation will be used to form the source and drain area for the MOSFET and the MESFET. During this step, a layer is necessary to cover the channel of the MESFET to make it lightly doped which is necessary in order to make a Schottky gate. As discussed later, modern CMOS technology has some additional process steps, specifically implants, which can affect the performance of the device. After the implant of the source/drain area, the exposed silicon will react with the cobalt, which will create a low-resistance contact after the annealing. The rest of the fabrication process steps are the same as for the CMOS.

Figure 2. Fabrication step for SOI MESFET [5].

In deep submicron processes, short channel and threshold voltage effects limit the performance of the devices [7]. Modern CMOS technologies use many additional implants and doping for the well and the substrate to overcome these effects [8]. However, this is typically unwanted for the MESFET fabrication. As discussed early in this chapter,

the nearly ideal Schottky gate is formed between the silicide and a lightly doped well. Any changes to the well-doping will affect the leakage of the device. What is typically done for these processes is colleagues in the research group will go through the design kit and the manual and will identify certain drawing layers, to the best of their ability, which block some of these unwanted implants. However, modern CMOS processes are very complex and many layers are derived from various Boolean expressions. Thus, it is very difficult to block all the necessary implants while only working with the design manual. Moreover, some of the layers are restricted for internal use at the foundry.

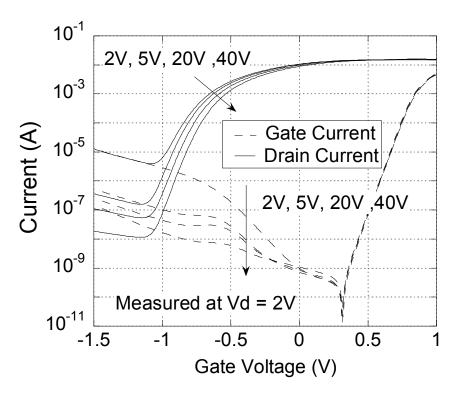

Figure 3 shows how the leakage current changes when the drain voltage increases for an SOI MESFET on a 32nm process. As it can be seen, the leakage current goes down about 10 times. The reason why this happened has not been pointed yet been identified. It may be the trapped charge in the channel that moves forward due to the high voltage of the drain side changing the MESFET threshold voltage but it is hard to see how this can reduce the reverse bias gate leakage current. More work is required to identify the mechanisms responsible for the shift in the gate and drain currents after a high voltage is applied to the drain.

Figure 3. 32nm SOI MESFET device Gummel plots after progressive exposure to high drain voltages.

# 1.2 MESFET OPERATION AND CHARACTERIZATION

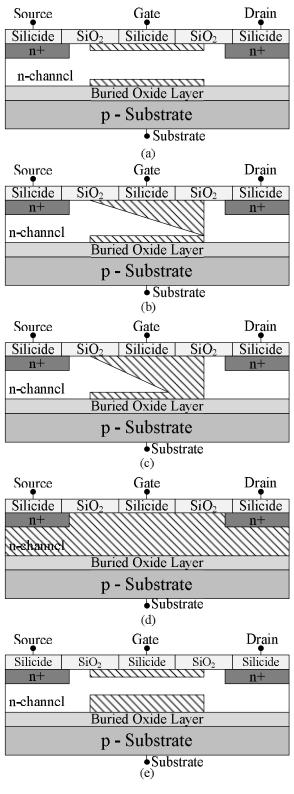

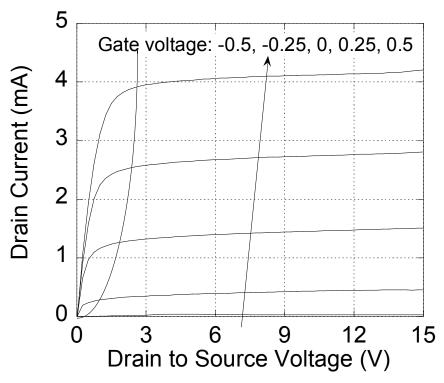

The MESFET is an n-channel depletion mode device which means its threshold voltage is negative. The current from the drain to the source is controlled by the width of the depletion region. Figure 4 shows the device operated in different bias regions. Figure 5 shows the Gummel plot and family of curves (FOC) results from a MESFET fabricated using the IBM 45nm SOI process. Several characteristics can be acquired from these figures, which will be discussed in the next sections.

Figure 4. SOI MESFET Device Operation: (a) linear region ( $V_{GS} > V_{TH}$ ,  $V_{DS} < V_{DSAT}$ ), (b) the boundary between the saturation and the linear region ( $V_{DS} = V_{DSAT}$ ), (c) saturation region ( $V_{DS} > V_{DSAT}$ ), (d)cut-off region ( $V_{GS} < V_{TH}$ ), (e) body effect.

# 1.2.1 THRESHOLD VOLTAGE

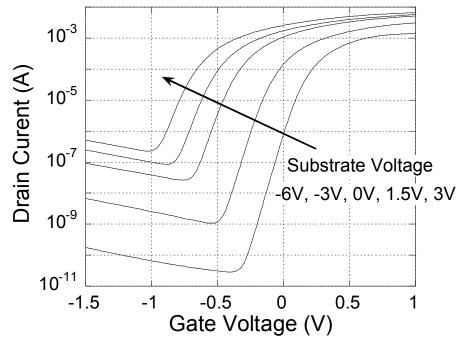

Since Si MESFETs are depletion mode devices, a channel is already present at a V<sub>GS</sub> of 0V. As V<sub>GS</sub> becomes more negative, the width of the depletion region under the gate will increase. When V<sub>GS</sub> reaches a certain value, the depletion region will fill all the silicon region under the gate and the device will be pinched-off. Typically the threshold voltage of a SOI-MESFET is -0.5V – 1V [5]. For the SOI MESFETs, different ways can be used to change the threshold voltage. The simplest way is to modulate the back-gate of the device. Decreasing V<sub>BS</sub> will increase the depletion width from the bottom of the device. This will make the threshold voltage more positive. Another way is to change the thickness of the silicide or the thickness of the channel. However, both of these may be difficult since it requires changing the process steps. One feasible method is to change the doping level of the region under the gate. Increasing the doping level of the well will make the threshold more negative since it is more difficult to pinch-off the device with the same V<sub>GS</sub>. This is possible on many modern CMOS processes since there are typically more than one threshold voltage options for MOSFET devices that can be used to change the doping of the n-well.

Figure 5. Family of Curves (FOC) plot of a 45nm SOI MESFET with  $L_{aD}$  = 2000nm,  $L_{g}$  = 200nm, and  $L_{aS}$  = 200nm.

Figure 6. Threshold voltage change due to the body effect of the device. The substrate voltage is change from -6V to 3V with  $V_D$ =2V. The MESFET has an  $L_{aD}$  = 1000nm,  $L_{aS}$  = 1000nm, and  $L_g$  = 200nm.

## 1.2.2 DEVICE OPERATION

When  $V_{GS}$  exceeds the threshold voltage, a channel forms in the n-well. If a voltage source is applied between the drain and the source, current will flow through the channel. At this condition, the device is working in the linear region and the current will increase proportional to the source drain voltage  $(V_{DS})$ . In this region, the device will work like a resistor, whose value is controlled by the gate to source voltage. By applying a larger  $V_{GS}$ , the resistance of the device will reduce.

As  $V_{DS}$  keeps increasing, the width of the depletion region at the drain side will further increase. With enough  $V_{DS}$  voltage, the depletion region from the top will contact with the bottom one. At this time, the channel will pinch-off and the device will go into the saturation region. Further increasing  $V_{DS}$  will not increase the drain current as much as in the linear region. As a result of channel length modulation the MESFET drain current will increase slightly with increasing  $V_{DS}$ . The equations for the drain current of the device operated in the linear (1) and saturation (2) regions are shown as follows.

$$I_D = \beta (V_{GS} - V_t)^2 \tanh(\alpha V_{DS}) \quad (1)$$

$$I_D = \beta (V_{GS} - V_t)^2 (1 - \lambda V_{DS})$$

(2)

where

$\beta$  is the transconductance gain,

$\alpha$  is the saturation factor,

$\lambda$  is the channel length modulation factor,

$V_t$  is the threshold voltage of the device. [5]

### 1.2.3 LEAKAGE CURRENT AND TEMPERATURE DEPENDENCE

One of the major differences between MOSFETs and MESFETs is that the latter have a leakage current due to the Schottky gate. The leakage current from the Schottky gate can be written as shown in (3) [5].

$$I_G \approx AA^*T^2 e^{\frac{-\phi_B}{U_T}} e^{\frac{V_{GS}}{nU_T}}$$

(3)

where

A is the conducting area,

A\* is the Richardson constant,

T is absolute temperature,

$\Phi_B$  is the Schottky barrier.

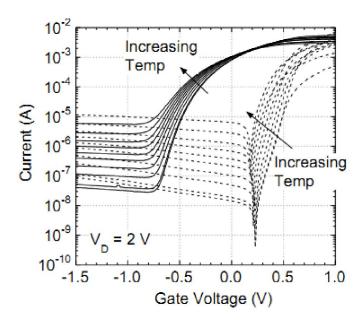

Since there is a temperature dependent parameter in the drain current and gate current, the performance of the device will change with temperature. The leakage current will increase with increasing temperature, which can be described by (3). The drain current change with temperature has a corner point of  $V_{GS}$  since there are two factors changing. When  $V_{GS}$  is low, the threshold changing with temperature will dominant and the current will increase with temperature since the threshold voltage is decreasing. As  $V_{GS}$  becomes higher, the effect of the mobility will be dominant since the over-drive voltage of the device is becoming larger. Thus the current will decrease with the increasing of the temperature. This behavior is illustrated in Figure 7.

Figure 7. The device operation change with temperature from -60° to 150°. The solid lines are the drain current while the dash ones are the gate current. The device is from 350nm SOI process,  $L_g$  =  $L_{aD} = L_{aS} = 0.6 \mu m$  [5].

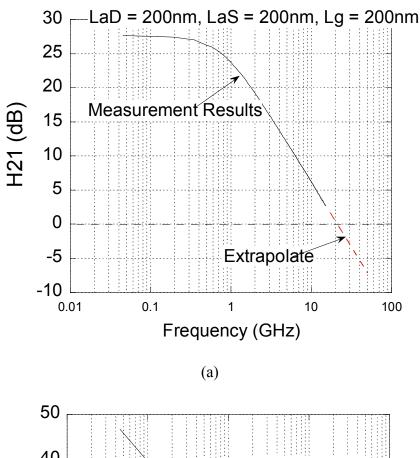

## 1.2.4 RF PERFORMANCE

The S-parameters of the MESFET under different biasing conditions have been measured using a vector network analyzer. In order to remove the effects of the parasitic capacitance and resistance of the pads used to probe the device, the s-parameters of the pads alone were measured first, and then removed (i.e. de-embedded) from the device results. The results are converted to h-parameters to extract the cut-off frequency. Figure 8 shows the h-parameters of the MESFET under the biasing condition that gives the peak cut-off frequency, f<sub>T</sub>. Figure 9 shows the cut-off frequency under different biasing conditions.

Figure 8. The measured  $h_{21}$  parameters of the MESFETs from the IBM 45nm process: (a)  $L_g$  = 200nm,  $L_{aS}$  = 200nm,  $L_{aD}$  = 200nm,  $V_{GS}$  = 0.45V,  $V_{DS}$  = 2V; (b) Lg = 200nm,  $L_{aS}$  = 200nm,  $L_{aD}$  = 1000nm,  $V_{GS}$  = 0.25V,  $V_{DS}$  = 4V.

Figure 9. The cut-off frequency of the MESFET from the 45nm IBM process: (a)  $L_g$  = 200nm,  $L_{aS}$  = 200nm,  $L_{aD}$  = 200nm,  $L_{aD}$  = 200nm,  $L_{aD}$  = 1000nm.

The cut-off frequency has a peak value with the increasing drain current. This is because of the change of the transconductance of the device with  $V_{GS}$ . The cut-off frequency of a device is given by (4)

$$f_T = \frac{g_m}{2\pi (C_{gs} + C_{gd})}$$

(4)

where

g<sub>m</sub> is the transconductance of the device,

C<sub>gs</sub> is the gate to source parasitic capacitance,

$C_{\text{gd}}$  is the gate to drain parasitic capacitance.

Usually,  $C_{gd}$  is much smaller than  $C_{gs}$  and can be neglected. As the change in the parasitic capacitance with respect to the biasing point is relatively small, the transconductance will dominate the change of cut-off frequency. The transconductance of the device can be extracted from the Gummel plot, as shown in Figure 10.

The cut-off frequency is also smaller for the device with larger  $L_{aD}$ , as shown in Figure 9. This is because large  $L_{aD}$  will result more parasitic capacitance (especially for Cgs). Also it will increase the parasitic resistance for the drain side and reduce the voltage that applied on it. The cut-off frequency of the device also decreases with increasing of  $L_{aS}$ . Large LaS will add more parasitic resistance to the source, which acts as the source degeneration to the device and reduce the transconductance [5].

Figure 10. Transconductance of the MESFET from the 45nm IBM process, extracted from the Gummel plots,  $V_D = 2V$ .

## 1.3 Brief Summary of the MESFET Applications

One of the most promising applications of the SOI MESFET is that it can be used for high power RF power amplifiers (PAs) [9]. The power output is dependent on the voltage or current level. Modern CMOS devices in deep submicron technology give a high cut-off frequency as the channel length becomes shorter. However, as the process is scaled, the voltage also scales. Modern CMOS processes usually have a voltage limitation not larger than 1V. Some processes provide thick oxide transistor, which can have the ability to handle 2V. Such a low voltage limitation will have problems for designing RF PAs. For example, in order to deliver 1W (+30dBm) power to a 50 Ohm antenna, the peak current in a Class A amplifier needs to be 2A. Thus, the output

impedance of the power amplifier is  $0.5\Omega$ . To match such a small resistance to the  $50\Omega$  antenna, an impedance matching network with a large transformation ratio needs to be added. As discussed in [26], a large impedance transformation network will decrease the efficiency of the PA – see Figure 11. Moreover, the voltage drop across the parasitic resistance and inductance of the bonding wires will affect the performance of the circuit. SOI MESFETs provide a solution for these applications. With the large access length  $L_{aD}$ , the device can have a high breakdown voltage. High voltage gives a small current, which will help the impedance matching and improve the overall performance of the PA. The cut-off frequency of the 45 nm SOI MESFET is about 20 GHz, which limits the working frequency to  $\sim$ 2 GHz. Although it is a little lower compared to GaAs MESFET, it can be integrated on chip with the high performance CMOS for a system-on-a-chip (SoC) applications, which reduces the cost of the product.

Figure 11. Matching network efficiency versus transformation ratio [26].

Another very important application for the MESFET is as the pass device of the linear regulator [10]. It enables the source follower configuration for the output stage, which gives good stability, low dropout voltage and the low noise output at the same time.

#### 1.4 CONCLUSION

Silicon MESFETs have been demonstrated to be a promising device for analog and RF applications. By using the silicide to form the Schottky gate, the MESFETs can be fabricated using standard SOI CMOS processes without any further changes to the process flow. N-channel SOI MESFETs are depletion mode devices and have a negative threshold. Besides these characteristics, they have almost the same operation as the MOSFETs. Due to their high breakdown voltage and good cut-off frequency, they have potential applications for high power RF power amplifiers.

Another important application is the MESFET based linear regulator. Since the MESFET based linear regulators have been designed by another colleague in the research group [5], and this thesis will focus on their evaluation and characterization. The thesis is organized as follows. Chapter 2 will give a basic review of the design of the linear regulator, including the general parameters for evaluating the regulator and the trade-offs between n-type and p-type pass devices. MESFET based linear regulator designs will be reviewed in Chapter 3. Chapter 4 will focus on the characterization of the MESFET based linear regulator. Measurement results will be shown and analyzed. Finally, conclusion and future work will be discussed in Chapter 5.

#### CHAPTER 2

#### DESIGN THEORY OF LINEAR REGULATORS

#### 2.1 Introduction to Linear Regulator

Power management integrated circuits (PMIC) are one of the most fundamental and important parts in modern electronics systems. Good power management systems lead to longer stand-by time for portable devices such as cell phones and laptops. In general, power management circuits can be classified into two categories: linear regulators and switching regulators. The most popular type of linear regulars is low-dropout (LDO) regulators since they can operate with input voltages much closer to the regulated output which allows them to be more efficient. This chapter will give an introduction to the design theory of linear regulators [11].

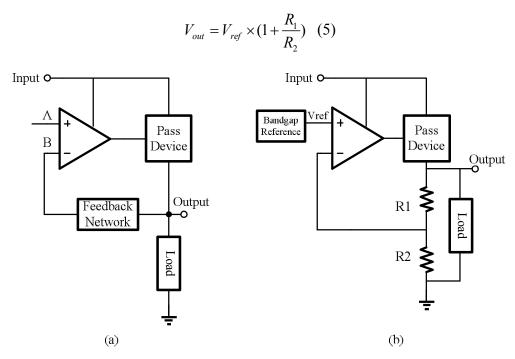

## 2.1.1 LINEAR REGULATOR

Figure 7 shows the basic topology of a linear regulator, which consists of three parts: a pass device which drives the load current, a feedback network which senses the output voltage and an error amplifier, which generates the control signal. The circuit includes negative feedback and the loop is designed with high enough gain so that  $V_A$  will equal to  $V_B$ . Thus the output voltage will be  $V_B$  divided by the feedback factor.  $V_A$  often comes from a bandgap reference and is typically about 1.2V. The feedback network often is realized using a resistor divider, as illustrated in Figure 12(b). Thus the output voltage can be written as,

Figure 12. Linear Regulator topology: (a) General topology. (b) One with a bandgap and feedback resistors included [11].

The efficiency of the LDO regulator is shown in Equation (6) and is limited by the difference between the input and output voltage.

$$\eta = \frac{P_o}{P_i} = \frac{V_{out} \times I_{load}}{V_{in} \times I_{in}} < \frac{V_{out}}{V_{in}} \quad (6)$$

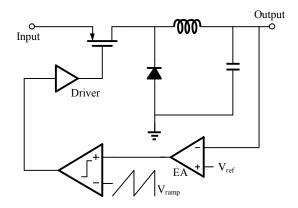

# 2.1.2 SWITCHING REGULATOR

Another kind of power management circuit is the switching regulator. Figure 13 shows the typical architecture for a voltage mode buck switching regulator [12]. Switches are turned on or off based on the pulsed width modulated signal generated from the controller to provide a constant output voltage. Compared to linear regulators, switching regulators can provide high efficiency. From (2), the efficiency of the linear regulators

cannot be higher than output over input voltage. On the other hand, most switching regulators offer a high efficiency. However, compared to switching regulators, linear regulators can provide a much cleaner output voltage. Due to the digital nature of the switching regulator, most of them will have a large ripple at the output voltage, while the noise of the linear regulator can be as low as the thermal noise floor of the circuit. This is why switching regulators are more suitable for digital circuits while linear regulators are more ideal for certain analog applications. [11]

Figure 13. A typical architecture for a voltage mode buck DC-DC converter.

Another advantage of the linear regulator is its high bandwidth. Compared to the bandwidth of the linear regulator, which is limited by the poles and zeroes in the loop, the speed of the switching regulator is much lower and always limited by the switching speed. Fast switching speed will give rise to higher bandwidth; however, the efficiency decreases due to switching losses.

Since switching regulators provide high efficiency while linear regulators provide a clean signal, these two are usually designed in series to provide a better power supply. The trade-offs between linear and switching regulator are summarized in Table 1 [11]

Table 1. Comparison between switching and linear regulators

|            | Switching Regulator     | Linear Regulator                                    |

|------------|-------------------------|-----------------------------------------------------|

| Speed      | Limited by the switches | High bandwidth                                      |

| Noise      | Large ripple at output  | Limited by thermal noise                            |

| Efficiency | High efficiency         | Poor, unless $V_{\rm IN}$ is close to $V_{\rm OUT}$ |

# 2.2 LINEAR REGULATOR SPECIFICATIONS

Before going to the detail design and trade-offs, it is better to review the definition of different parameters to evaluate linear regulators. These parameters include line regulation, load regulation, dropout voltage, efficiency, transient response and power supply rejection (PSR) [13].

# 2.2.1 LOAD REGULATION

Load regulation is the ability of the regulator to maintain the output voltage under different load currents. It is defined as,

$$LDR = \frac{\Delta V_{out}}{\Delta I_{out}} \quad (7)$$

The unit of the load regulation is usually mV/A. For an ideal regulator, the output voltage remains the same with different load currents. However, due to the finite gain of the op-amp, the regulated output voltage will change with the load current. Load regulation is approximately the output impedance of the regulator, which can be written as [11]

$$LDR = \frac{\Delta V_{out}}{\Delta I_{out}} = \frac{R_o}{1 + A_V \beta} \quad (8)$$

where

A<sub>V</sub> is the gain of the error amplifier,

β is the feedback factor determined by the resistor divider,

R<sub>O</sub> is the output resistance of the pass device.

## 2.2.2 LINE REGULATION

Line regulation (LNR) of the LDO is the ability of the circuit to maintain the output voltage for different input voltages. It is defined as follows [11]:

$$LDR = \frac{\Delta V_{out}}{\Delta V_{in}} \quad (9)$$

The unit for line regulation is mV/V, since the change at the output small relative to the change in the input. If a perfect reference voltage is used (i.e. it does not change with the supply voltage), the line regulation is proportional to the PSR of the regulator. Load regulation and line regulation can be improved by putting a high gain error amplifier in the loop.

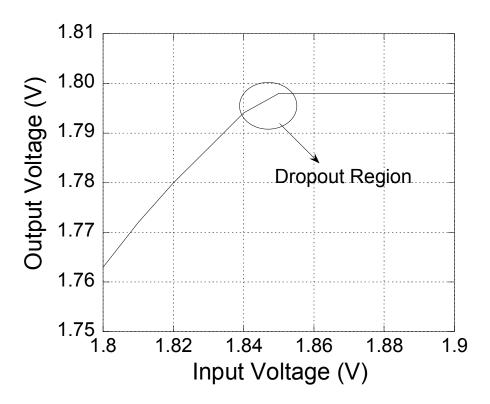

## 2.2.3 Dropout Voltage

Dropout voltage is defined as the difference between the input and output voltage at the point when the regulator loses regulation. Figure 14 shows a typical  $V_{IN}$ - $V_{OUT}$  characteristic for the linear regulator. As the input voltage decreases, the transistor needs more over-drive voltage to provide the load current. When the transistor cannot provide enough current, it will enter the triode region, which will decrease the loop gain and the output cannot maintain regulation. For a LDO regulator, the dropout voltage is usually approximately proportional to the on-resistance of the pass transistor when it is in the edge of the triode region

The dropout voltage defines the lowest input voltage to maintain the constant output voltage. For a specific circuit, the highest efficiency can be obtained with the input voltage slightly higher than the output voltage plus dropout voltage. Low dropout voltage will give rise to higher efficiency, which can be acquired by rewriting the efficiency equation [11].

$$\eta = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times I_{IN}} < \frac{(V_{IN} - V_{DROP}) \times (I_{IN} - I_Q)}{V_{IN} \times I_{IN}} < 1 - \frac{V_{DROP}}{V_{IN}}$$

(10)

Figure 14. The typical input-output characteristic of a linear regulator.

# 2.2.4 POWER SUPPLY REJECTION

Power supply rejection (PSR) is defined as the ability of a linear regulator to resist high frequency noise at the input. Figure 15 shows the typical PSR response. At low frequency, the linear regulator can reject the noise due to the high loop gain. As the frequency is increasing, the gain of the error amplifier and the pass device decrease, increasing the noise at the output. The corner frequency of the PSR is usually determined by the dominant pole of the loop. Decoupling capacitors with different values will be put at the input to filter out the high frequency noise [14].

Figure 15. Typical PSR of the linear regulator versus frequency.

## 2.2.5 Transient Response

Transient variation is used to evaluate how the regulators response with a sudden change in the load current or the line voltage. Load transient response usually reflects the loop gain, bandwidth and stability of the regulator. For the same bandwidth, a good phase margin results a fast recover time (typical 60° for fastest) while poor stability performance will lead to ringing. Line transient response usually reflects the PSR of the regulator.

As we can see from the previous analysis, the pass device plays an important role in the performance of a linear regulator, since it has influences loop gain, bandwidth, stability and dropout voltage. In standard CMOS technology, two kinds of transistors are usually used as the pass device: PMOS and NMOS. In the following section, the design and trade-off between these two type regulators will be analyzed in details.

#### 2.3 PMOS LINEAR REGULATOR

A typical PMOS linear regulator is shown in Figure 11. The main advantage of this topology is its low dropout voltage. For a PMOS transistor, the gate voltage is lower than the source for turning on the device. To ensure the pass device is in the saturation region to maintain regulation, the source to drain voltage of the device should be larger than the over-drive voltage. The dropout region happens at the edge of the saturation region, which is

$$V_{DROP} = R_{ON} \times I_{OUT} \quad (11)$$

where,  $R_{ON}$  is the on resistance of the pass device,  $I_{OUT}$  is the load current. This is why PMOS linear regulators are also called low dropout (LDO) regulators. In reality, the dropout voltage also includes the voltage dropped across the bonding wires and the metal lines on the chip and circuit board.

One disadvantage of this topology is the mobility of the p-type transistor, which is typically 2-3 times lower than n-type devices. In order to have a specific current driving ability, the p-type device also has to be 2-3 times larger than an n-type device. As a result, it will have much more parasitic capacitance and need more silicon area.

Another critical issue for the PMOS linear regulator is its inherent instability due to the common-source topology of the output stage. This is illustrated in Figure 16, where the error amplifier (EA) is assumed to be a single pole system. Due to the parasitic capacitance in the circuit, there are two dominant poles inside the loop, which are,

$$P_1 = \frac{1}{2\pi R_{o1} C_{o1}}$$

(8)

$$P_o = \frac{1}{2\pi R_{o(PMOS)} C_L}$$

(9)

where,  $R_{O1}$  and  $C_{O1}$  is the output resistance and capacitance of the EA respectively.  $R_{O(PMOS)}$  is the output resistance of the pass device and  $C_L$  is the load capacitor.

Figure 16. PMOS linear regulator topology: (a) External compensation using big capacitor and the Equivalent Series Resistor (ESR) (2) Internal compensation.

Due to the high output impedance of the common source configuration and the high load capacitor, the location for  $P_0$  and  $P_1$  may become very close to each other, which will result in low phase margin or even unstable operation. In order to solve the stability problem as discussed above, two types of compensation are generally used: external compensation and internal compensation [11].

External compensation is usually utilized for the conventional LDO regulator design, which means that the bandwidth is determined by the output of the regulator [11]. A big capacitor (about several micro fara) is added at the output to make  $P_o$  the dominant pole. On one hand, it can help splitting the two low frequency pole by pushing the output one further close to the origin. On the other, adding a capacitor can be used as a bypass filter to reduce the over-shoot and under-shoot due to the wire resistance and inductance when the load current changes. A buffer is usually added between the error amplifier and the pass device to further push  $P_1$  into high frequency. Due to the load current variation and the high output impedance of the EA, the stability is still difficult to ensure. The most popular way is to take advantage of the Equivalent Series Resistance (ESR) of the output capacitor to create a left hand plane zero (LHP) to compensate for the stability, which is

$$Z_O = \frac{1}{2\pi C_O R_{ERS}} \quad (10)$$

For a conventional LDO regulator, the output capacitor must be carefully chosen to ensure the stability. Most of the conventional LDO regulators provide the specifications for the output capacitor [15]. The typical bode plot of the loop gain is shown in Figure 17.

System on Chip (SoC) is becoming more popular due to its low cost and chip size. In order to integrate the conventional LDO regulator onto a SoC design, either a large capacitor is required on-chip, or an external pin is required. The first option is hard on a CMOS process since a large area is needed to achieve the required capacitance while the second option requires additional board space. Thus, a capacitor-free LDO regulator is ideal for this particular application.

Figure 17. Bode plot of the closed-loop gain of the externally compensated linear regulator.

Compared to a conventional regulator, internal compensation is usually used for a capacitor-free regulator, which means that the dominant pole is determined inside the loop. Usually,  $P_1$  will be designed as the dominant pole of the loop, while some techniques will be used for further splitting of  $P_1$  and the non-dominant pole such as  $P_0$  and  $P_2$ . Unlike the conventional LDO regulator, adding capacitors at the output will decrease the phase

margin; thus giving poor load transient response. However, for SoC applications, the load capacitor and the bypass capacitor are not as large as traditional designs. Since the output resistance of the PMOS device ( $R_0$  of the transistor) is very high, the bandwidth of the capacitor-free LDO regulator is usually around a few hundred kHz. Figure 18 shows a typical Bode plot for the internally compensated linear regulator.

The PSR of PMOS linear regulators are not very good. The noise at the power supply are presented directly at the source of the PMOS, which will modulate the over-drive voltage of the pass device and change the output.

Figure 18. Bode plot of the loop gain of the internal compensated PMOS linear regulator.

## 2.4 NMOS LINEAR REGULATOR

An n-channel MOSFET can also be used as the pass device of the linear regulator. A typical NMOS regulator is shown in Figure 14. Compared to p-type devices, the mobility of electron is usually faster, thus requiring smaller silicon area to provide for the same current driving ability. The main drawback of this topology is its high dropout voltage. In order to make the NMOS work properly, the gate voltage ( $V_G$ ) must be higher than the output plus the threshold voltage, which is typically about 600mV-1V due to the body effect. For a normal circuit,  $V_G$  cannot exceed the supply voltage. Thus

$$V_{DROP} = V_{IN} - V_{OUT} > V_G - V_{OUT} = R_{on} \times I + V_{TH}$$

(11)

where  $V_{TH}$  is the threshold voltage of the pass device. Equation (11) shows that the dropout voltage of the NMOS linear regulator includes the threshold voltage and will be higher than PMOS linear regulator. In order to remove  $V_{TH}$  from dropout voltage, a charge pump can be added to boost the gate voltage higher than the supply [16]. However, such a circuit will introduce switching noise to the circuit, losing the natural advantage of the linear regulator.

Figure 19. NMOS linear regulator topology with internal compensation being used [5].

An advantage of the NMOS linear regulator is its good PSRR performance. Since the supply voltage is added to the drain of the pass device, the NMOS device works as a cascode device to shield the output [17]. Another important advantage of the NMOS linear regulator is the better stability performance compared to PMOS regulators.

As illustrated in Figure 19, there are still three poles in the loop. However, the output impedance of the NMOS in common-drain configuration is  $1/g_m$  since the output is looking into the source compared to  $R_O$  of the PMOS linear regulator. Thus the output pole is at a relative high frequency. The equation for each pole is given below.

$$P_1 = \frac{1}{2\pi R_{o1} C_{o1}} \quad (12)$$

$$P_{1} = \frac{1}{2\pi R_{o1}C_{o1}} \quad (13)$$

$$P_O = \frac{gm_{NMOS}}{2\pi C_o} \quad (14)$$

Internal compensation is usually utilized for NMOS linear regulator. A simple way is adding a capacitor at the output of the error amplifier to push P<sub>1</sub> closer to the origin [5]. Other compensation techniques can also be utilized to further split the poles. Although internal compensation can still be used for a PMOS regulator, in order to have the same stability performance, the bandwidth is much smaller than that of a NMOS regulator. Higher bandwidth will provide a fast transient response.

#### 2.5 CONCLUSION

Linear regulators are one of the most popular power converters for power management circuits. Compared to switching regulators, linear regulators have higher bandwidth and lower noise. Line regulation, load regulation, dropout voltage, transient response, and power supply rejection are important parameters to evaluate the performance of the linear regulator. Generally, two types of transistors, PMOS and NMOS can be utilized as the pass device for the linear regulator. The PMOS regulator provides low dropout voltage, but it has inherent stability issues, lower bandwidth and needs a larger device. The NMOS regulator has better stability and is much faster, however, it requires additional circuits like a charge pump in order to provide low dropout operation. The comparison between these two types linear regulator are summarized in Table 2.

Table 2. Comparison between NMOS and PMOS linear regulators

|                 |         | U      |

|-----------------|---------|--------|

|                 | NMOS    | PMOS   |

| Dropout Voltage | Low     | High   |

| Bandwidth       | High    | Low    |

| Stability       | Good    | Poor   |