Energy and Quality-Aware Multimedia Signal Processing

By

Yunus Emre

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved August 2012 by the Graduate Supervisory Committee:

Chaitali Chakrabarti, Chair Bertan Bakkaloglu Yu Cao Antonia Papandreou-Suppappola

ARIZONA STATE UNIVERSITY

December 2012

### ABSTRACT

Today's mobile devices have to support computation-intensive multimedia applications with a limited energy budget. In this dissertation, we present architecture level and algorithm-level techniques that reduce energy consumption of these devices with minimal impact on system quality.

First, we present novel techniques to mitigate the effects of SRAM memory failures in JPEG2000 implementations operating in scaled voltages. We investigate error control coding schemes and propose an unequal error protection scheme tailored for JPEG2000 that reduces overhead without affecting the performance. Furthermore, we propose algorithm-specific techniques for error compensation that exploit the fact that in JPEG2000 the discrete wavelet transform outputs have larger values for low frequency subband coefficients and smaller values for high frequency subband coefficients.

Next, we present use of voltage overscaling to reduce the data-path power consumption of JPEG codecs. We propose an algorithm-specific technique which exploits the characteristics of the quantized coefficients after zig-zag scan to mitigate errors introduced by aggressive voltage scaling.

Third, we investigate the effect of reducing dynamic range for datapath energy reduction. We analyze the effect of truncation error and propose a scheme that estimates the mean value of the truncation error during the pre-computation stage and compensates for this error. Such a scheme is very effective for reducing the noise power in applications that are dominated by additions and multiplications such as FIR filter and transform computation. We also present a novel sum of absolute difference (SAD) scheme that is based on most significant bit truncation. The proposed scheme exploits the fact that most of the absolute difference (AD) calculations result in small values, and most of the large AD values do not contribute to the SAD values of the blocks that are selected. Such a scheme is highly effective in reducing the energy consumption of motion estimation and intra-prediction kernels in video codecs.

Finally, we present several hybrid energy-saving techniques based on combination of voltage scaling, computation reduction and dynamic range reduction that further reduce the energy consumption while keeping the performance degradation very low. For instance, a combination of computation reduction and dynamic range reduction for Discrete Cosine Transform shows on average, 33% to 46% reduction in energy consumption while incurring only 0.5dB to 1.5dB loss in PSNR.

.

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my advisor, Dr. Chaitali Chakrabarti for her guidance, support, and encouragement. Working with her has been my best learning experience so far. I believe that I am capable of working independently now and I have not felt better prepared than I feel now to undertake challenges that may lie ahead. I have been feeling amazingly fortunate that I could work with her in the past years.

I would like to extend my gratitude to Professors Antonia Papandreou-Suppappola, Bertan Bakkaloglu and Yu Cao for serving as members of my committee. I thank all my friends at Arizona State University, Osman Emir Erol, Berkay Kanberoglu, Ender Yilmaz, Ahmet Cemal Durgun who made my stay here pleasant and enjoyable, other friends, family and relatives who wished me success with my program and have been in touch with me for a very long time. I am profoundly indebt to my mentors at Intel Corporation, Umit Ogras, Mike Kishinevsky, and Jianping Xu, for teaching me the importance of critical thinking and hardworking. I also wish to thank my fellow members of Low Power Systems Lab, Chengen Yang, Ming Yang, and Rupa Mahadevan, for providing a fun environment in which to discuss, and learn more. I am also thankful to Science Foundation of Arizona (SFAz) and National Science Foundation (NSF) for supporting my work during my PhD study.

I am deeply grateful to my father, Cafer Emre, my mother, Saliha Emre, and my sister, Nilufer Emre. None of this would have been achieved without their support. Special thanks go to my wife, Refika Koseler Emre, who has always been my joy and my pillar. I would like to thank her for her company, understanding, and encouragement during the past years.

# TABLE OF CONTENTS

| Page                                                             |

|------------------------------------------------------------------|

| LIST OF TABLES                                                   |

| LIST OF FIGURES                                                  |

| CHAPTER                                                          |

| 1. INTRODUCTION                                                  |

| I. Overview of Existing Work2                                    |

| II. Problems Addressed                                           |

| A. Voltage Scaling and Error Compensation in Memories:           |

| B. Voltage Scaling and Error Compensation in Data-path:          |

| C. Dynamic Range Reduction in Datapath:6                         |

| D. Hybrid Schemes for Energy Reduction in Data-path8             |

| III. Organization                                                |

| 2. BACKGROUND                                                    |

| I. Sources of Power Consumption10                                |

| II. Power Reduction in Dynamic Component10                       |

| A. Power Reduction by Voltage Scaling11                          |

| B. Power Reduction by Voltage Scaling11                          |

| C. Power Reduction by Architecture Modification13                |

| D. Power Reduction by Algorithm Modification: Reducing Number of |

| Computations                                                     |

# CHAPTER

| III. Power Reduction of Static Component15                |

|-----------------------------------------------------------|

| IV. Overview of Image/ Video Coding Algorithms16          |

| A. JPEG [44]17                                            |

| B. JPEG200019                                             |

| C. Video Codec (H.264)                                    |

| 3. COMPENSATING FOR MEMORY ERRORS CAUSED BY VOLTAGE       |

| SCALING: CASE STUDY JPEG2000                              |

| I. Introduction                                           |

| II. Power Reduction in Memories                           |

| A. SRAM Failure Analysis27                                |

| B. Previous Work on Compensating for SRAM Errors          |

| III. Proposed Unequal Error Protection for JPEG2000       |

| IV. Proposed Algorithm-Specific Techniques for JPEG200040 |

| A. Method-141                                             |

| B. Method-241                                             |

| C. Method-3                                               |

| D. Method-4                                               |

| V. Simulation Results for the Proposed Techniques43       |

| A. System Performance Results                             |

| B. Overhead: Area, Delay, Power Consumption               |

| VI. Summary                                                        | 53 |

|--------------------------------------------------------------------|----|

| 4. COMPENSATING FOR DATAPATH ERRORS CAUSED BY VOLTAC               | ЗE |

| SCALING: CASE STUDY JPEG                                           | 54 |

| I. Introduction                                                    | 54 |

| II. Voltage Scaling Induced Errors in Datapath                     | 54 |

| A. Failure Analysis                                                | 54 |

| B. Previous Work on Compensating Datapath Errors                   | 56 |

| III. Proposed Algorithm-Specific Technique: Case Study DCT         | 58 |

| IV. Simulation Results                                             | 61 |

| A. Algorithm Performance                                           | 61 |

| B. Hardware Overhead                                               | 63 |

| V. Summary                                                         | 64 |

| 5. COMPENSATING FOR DATAPATH ERRORS CAUSED BY DYNAM                | IC |

| RANGE REDUCTION                                                    | 65 |

| I. Introduction                                                    | 65 |

| II. Effects of Dynamic Range Reduction                             | 65 |

| III. Reducing Dynamic Range by Low Order Bit Truncation            | 66 |

| IV. Reducing Dynamic Range by High Order Clipped Computation (HOC) | 76 |

| A. Proposed SAD Algorithm                                          | 80 |

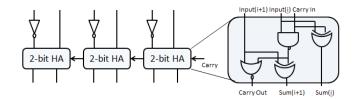

| B. Proposed SAD Architecture                                       | 82 |

# CHAPTER

|    | C. P    | Performance Analysis of Proposed HOC                        | 86    |

|----|---------|-------------------------------------------------------------|-------|

|    | Alg     | orithm Performance                                          | 86    |

|    | D. E    | Energy Quality Trade-off                                    | 89    |

|    | V. Su   | mmary                                                       | 92    |

| 6. | HY      | BRID ENERGY SAVING TECHNIQUES FOR DATAPATH                  | 95    |

|    | I.      | Combining Computation Reduction and Voltage Scaling         | 95    |

|    | II.     | Combining Voltage Scaling and Dynamic Range Reduction       | 96    |

|    | III.    | Combining Computation Reduction and Dynamic Range Reduction | . 102 |

|    | IV.     | Summary                                                     | . 109 |

| 7. | COI     | NCLUSION                                                    | . 110 |

| v  | Vorks ( | Cited                                                       | .114  |

Page

| L | IST | OF | ΤA | BL | LES |

|---|-----|----|----|----|-----|

|   |     |    |    |    |     |

| Table Page                                                                                 |

|--------------------------------------------------------------------------------------------|

| 3.1. PSNR values of different techniques at 0.75bpp compression rate for BER= $10 - 2$ ,   |

| using error models 1&249                                                                   |

| 3.2. Necessary modules for algorithm-specific methods                                      |

| 3.3. Area, latency and power consumption overhead of circuit components used in the        |

| algorithm-specific methods                                                                 |

| 3.4. Area, latency and power consumption overhead of ECC Schemes for (137,128),            |

| (72,64) and (39,32)                                                                        |

| 4.1. Number of bits necessary to represent each group of 2D DCT coefficients for natural   |

| images                                                                                     |

| 4.2. PSNR values of proposed technique at 0.75bpp compression rate when                    |

| BER(VOS)=10 - 4                                                                            |

| 4.3. Power Consumption and latency of the three units in the voltage overscaling           |

| compensation scheme                                                                        |

| 5.1. Quality, power and latency of DCT engine for different levels of truncation           |

| 5.2. Percentage of AD Values during Inter-prediction that can be represented by 4 to 8     |

| bits for Football Video sequence                                                           |

| 5.3. Percentage of AD values during Inter-prediction that can be represented by 4 to 8     |

| bits for Foreman Video Sequence                                                            |

| 5.4. Statistics of Selected and Unselected SAD Values for Foreman Video Sequence           |

| during Inter Prediction                                                                    |

| 5.5. Average increase in compressed data rate and reduction in PSNR <i>Thr</i> =16,32,6482 |

| 5.6 Average increase in compressed data rate and reduction in PSNR for Inter-prediction    |

|                                                                                            |

# Table

| 5.7 | Average | increase in | o compressed | data ra | te and | reduction | in | PSNR | for | Intra-prec | liction |

|-----|---------|-------------|--------------|---------|--------|-----------|----|------|-----|------------|---------|

|-----|---------|-------------|--------------|---------|--------|-----------|----|------|-----|------------|---------|

| 6.1. MSE Improvement for different Gaussian Filters                   |       |

|-----------------------------------------------------------------------|-------|

| 6.2. Reduction Order of 6 Sample Images                               |       |

| 6.3. Final Order for Scheme I, II and III                             | 106   |

| 6.4. Delay, Power and Area for Original and Reduced Computation 1D-DC | Г 107 |

# LIST OF FIGURES

| Figure     Page                                                                                   |

|---------------------------------------------------------------------------------------------------|

| 1.1 Goal: Reduce energy consumption with minimal quality degradation2                             |

| 2.1. Power delay profile of 14-bit RCA adder under voltage scaling                                |

| 2.2. Sub-sampling patterns for 1/2 and 1/4 schemes                                                |

| 2.3. Block Diagram of JPEG17                                                                      |

| 2.4. 2D DCT architecture using 1-D DCTs                                                           |

| 2.5. a) Luminance Quantization Matrix for $Q = 50$ ; b) Zigzag scan order                         |

| 2.6 Block diagram of JPEG2000                                                                     |

| 2.7 a) Sub-band representation of DWT output b) Bit plane representation of Sub-band c)           |

| Code block representation of bit planes                                                           |

| 2.8. Block Diagram of the Video Encoder                                                           |

| 2.9. a) Nine prediction modes of Intra_4x4 b) Diagonal Down Right25                               |

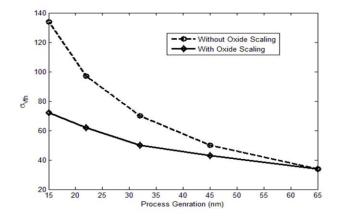

| 3.1. $\sigma VT$ scaling trend with and without oxide scaling [35] [53]27                         |

| 3.2. Schematic of a SRAM cell                                                                     |

| 3.3. Delay distribution of a single SRAM read operation                                           |

| 3.4. Read, write and total failure probability of SRAM in 32nm technology for different           |

| voltage levels when $\sigma VT$ =40mV                                                             |

| 3.5. $\Delta DE$ (normalized) due to error in different bit positions for different levels of DWT |

| a) Linear b) Logarithmic Scale                                                                    |

| 3.6. a) Overhead and b) Performance Degradation for different settings of line-1 and line-        |

| 2                                                                                                 |

| 3.7. Performance Degradation x Overhead for different settings of line1 and line2 39              |

| 3.8.Parity generation of (39, 32) code from (72, 64) code                                        |

|--------------------------------------------------------------------------------------------------|

| 3.9. Number of non-zero bits in different subbands in a) Bridge b) Lena images                   |

| 3.10. Lena Image a) Original b) HL1 c) HL2 subband                                               |

| 3.11. Bit planes used in error detection mechanism                                               |

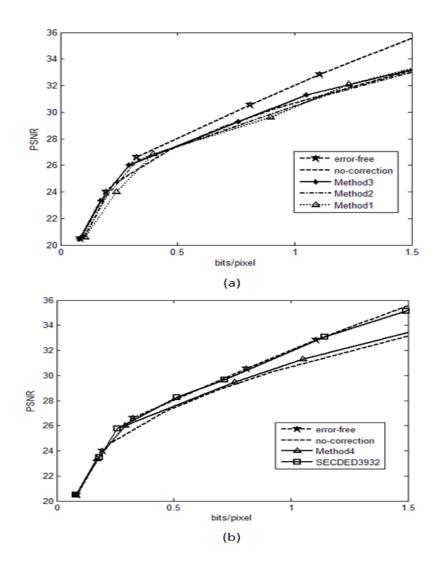

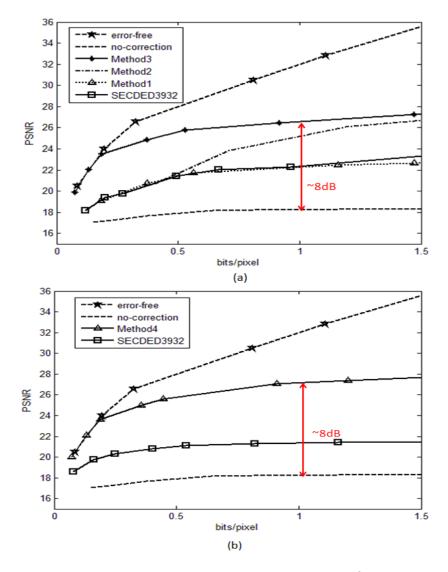

| 3.12. Quality vs. Compression rates when $BER=10 - 4$ for Lena a) for error model-1 b)           |

| for error model-2                                                                                |

| 3.13. Quality vs. Compression rates when BER= $10 - 3$ for Lena a) for error model-1 b)          |

| for error model-2                                                                                |

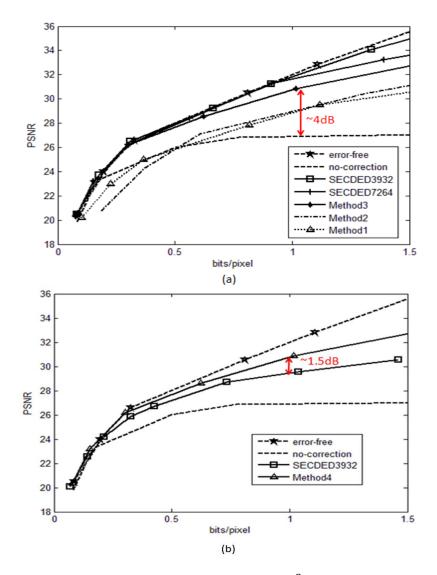

| 3.14. Quality vs. Compression rates for Lena when $BER=10 - 2$ using algorithmic                 |

| techniques a) for error model-1 b) for error model-2                                             |

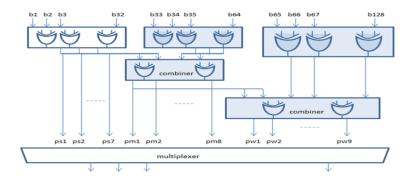

| 3.15. Block diagram of encoder for (137,128), (72, 64) and (39, 32) codes                        |

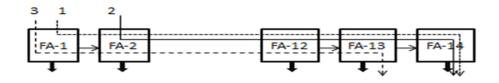

| 4.1. Block Diagram of 14-bit RCA55                                                               |

| 4.2. Probability of error distribution for 14-bit RCA for different voltage settings             |

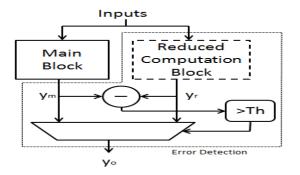

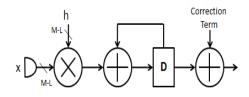

| 4.3. Block Diagram of Algorithm Noise Tolerant (ANT) Scheme                                      |

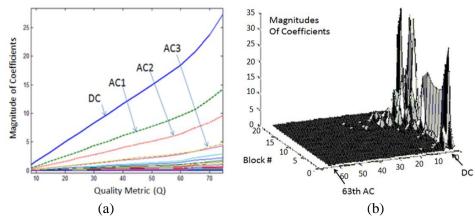

| 4.4. Magnitude of DC and AC coefficients a) averaged over all blocks; b) first 20 blocks         |

| of Bridge image                                                                                  |

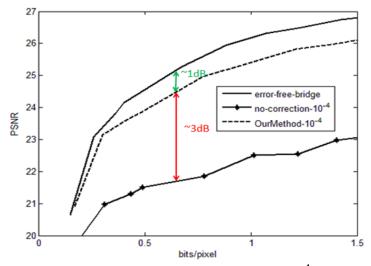

| 4.5. PSNR vs. Compression rate for Bridge when $BER=10 - 4$                                      |

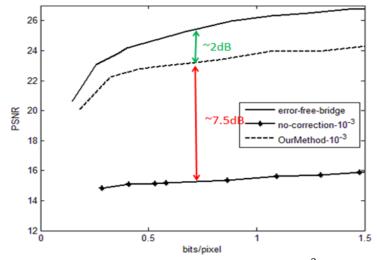

| 4.6. PSNR vs. Compression rate for Bridge when $BER=10 - 3$                                      |

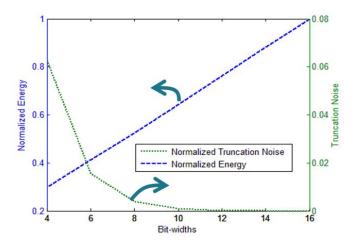

| 5.1. Energy and Noise distribution of 16-bit RCA wrt bit-width                                   |

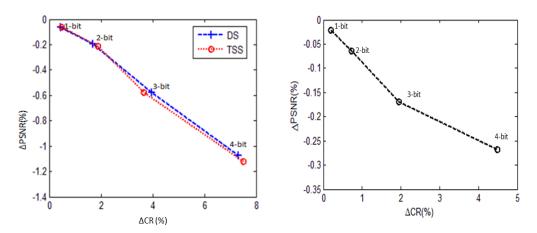

| 5.2. Average performance loss due to bit truncation a) using DS and TSS in motion                |

| estimation b) intra prediction of H.26467                                                        |

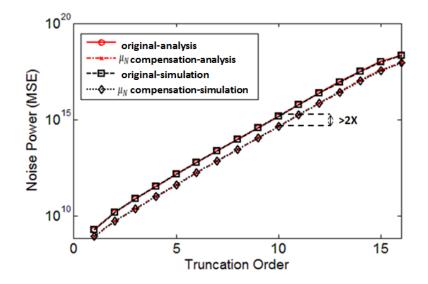

| 5.3: Noise power of <i>Qmul</i> for 16-bit multiplication with and without $\mu$ -compensation70 |

Page

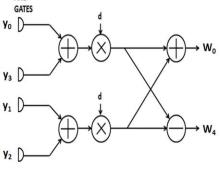

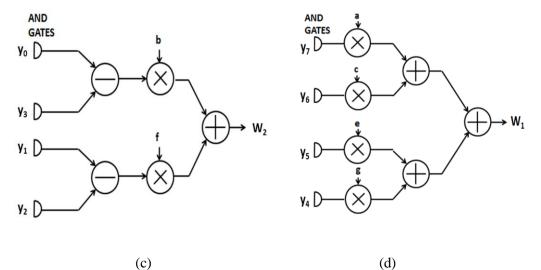

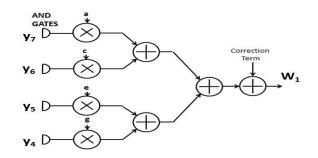

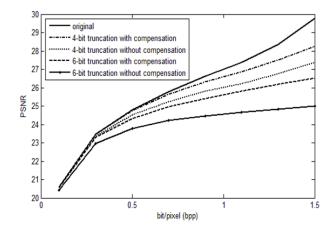

| 5.4. Architecture of 1-D DCT coefficients. a) First stage butterfly b) $w0$ and $w4$     |

|------------------------------------------------------------------------------------------|

| computation units, c) w2 unit, d) w1 unit72                                              |

| 5.5. Modified DCT computation of <i>W</i> 173                                            |

| 5.6. Performance comparison between uncompensated and compensated bit truncation         |

| for DCT computation of Baboon image74                                                    |

| 5.7. MAC implementation of a low pass filter76                                           |

| 5.8. Histogram plots of AD computations in motion estimation of a) Football and b)       |

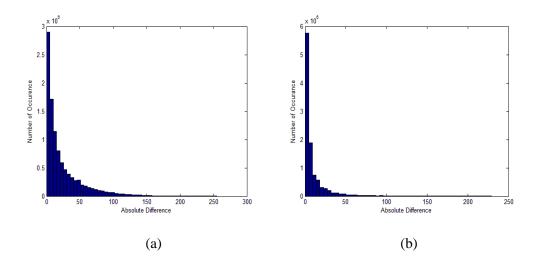

| Foreman video sequences                                                                  |

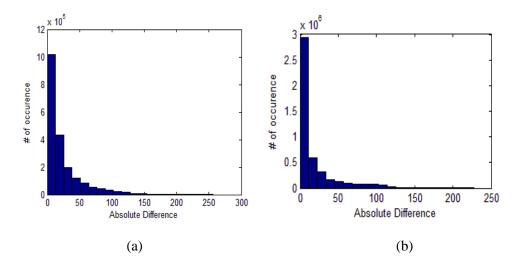

| 5.9. Histogram plots of AD computations in intra-prediction of a) Football and b)        |

| Foreman video sequences                                                                  |

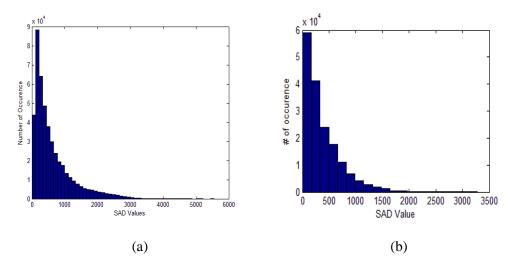

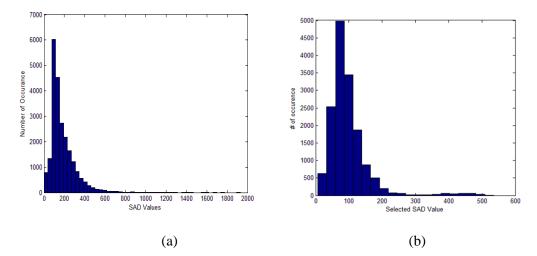

| 5.10. Histogram of SAD values of all blocks a) Inter Prediction b) Intra Prediction79    |

| 5.11. Histogram of SAD values of selected blocks a) Inter Prediction b) Intra Prediction |

|                                                                                          |

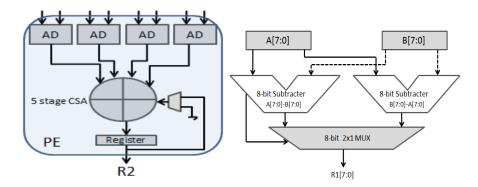

| 5.12. a) Baseline SAD calculation unit, b) 8-bit absolute difference calculator          |

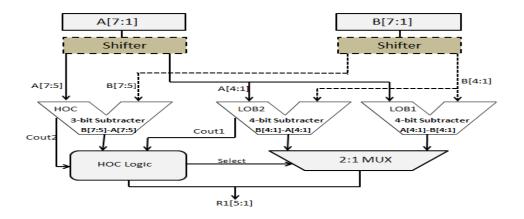

| 5.13. Proposed SAD calculation unit                                                      |

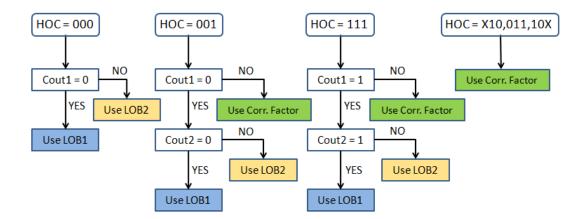

| 5.14. Flow Chart of the proposed SAD calculation scheme                                  |

| 5.15. 6-bit Half Adder Chain85                                                           |

| 5.16. Delay vs Energy Consumption of the baseline and proposed schemes                   |

| 5.17. PSNR vs Compressed Data Rate of a) Football, b) Claire sequences under different   |

| configurations for inter-prediction                                                      |

| 5.18. Cost of using proposed scheme in terms of percentage increase in compressed data   |

| size and PSNR reduction for inter-prediction                                             |

| 5.19. Algorithm performance for different SAD architectures                              |

| 5.20. Comparison of latency and energy consumption at nominal voltage of all candidate           |

|--------------------------------------------------------------------------------------------------|

| schemes                                                                                          |

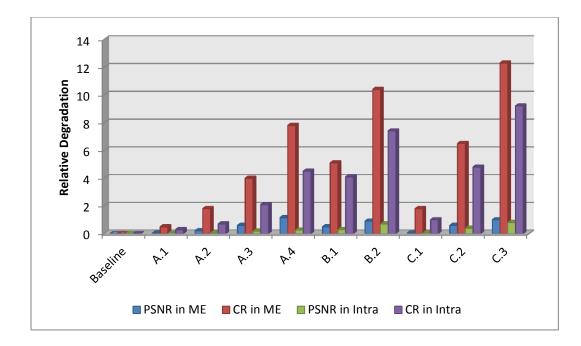

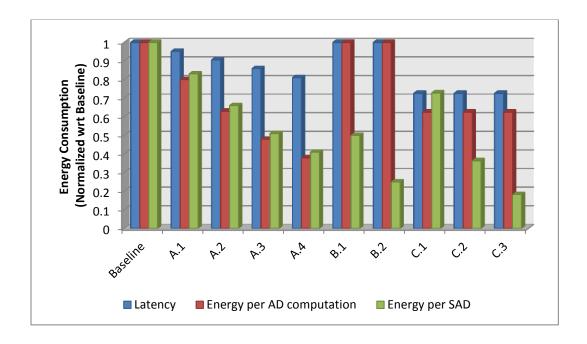

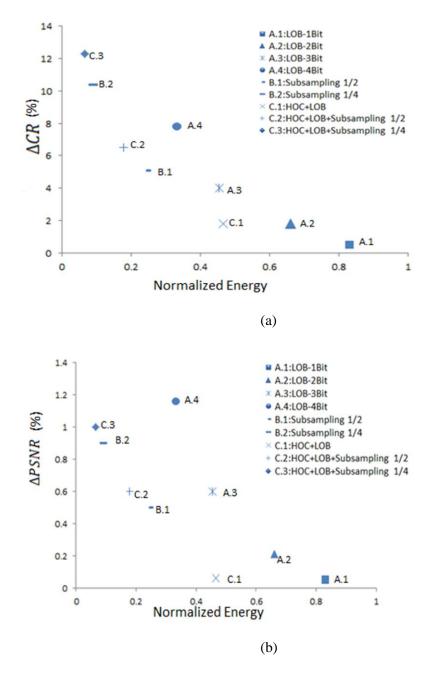

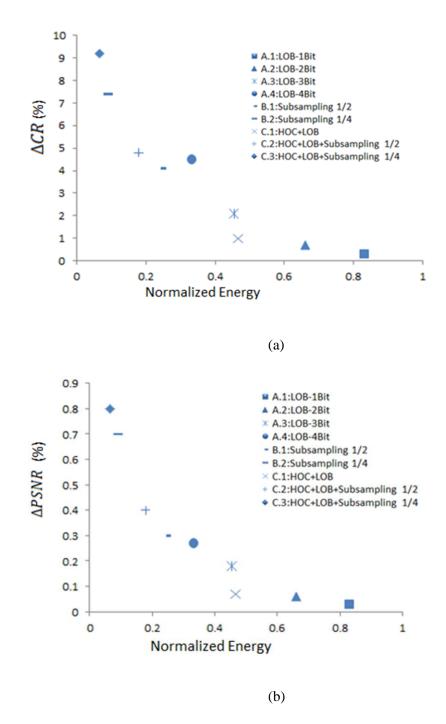

| 5.21. Inter-Prediction a) Compressed Data Rate Increase ( $\Delta CR$ ) vs Normalized Energy, b) |

| PSNR degradation ( $\Delta PSNR$ ) vs Normalized Energy                                          |

| 5.22. Intra-Prediction a) Compressed Data Rate Increase ( $\Delta CR$ ) vs Normalized Energy, b) |

| PSNR degradation ( $\Delta PSNR$ ) vs Normalized Energy                                          |

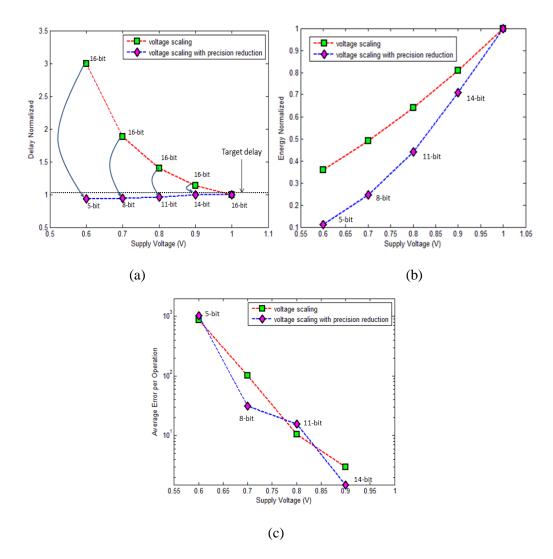

| 6.1. 16-bit RCA a) Delay, b) Energy, c) Average Error per Operation distribution with            |

| and without precision reduction under voltage scaling                                            |

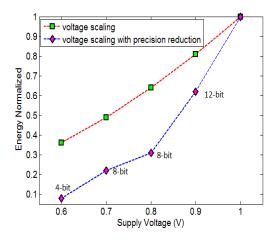

| 6.2. 16-bit CLA Energy distribution with and without precision reduction under voltage           |

| scaling for comparable average error per operation                                               |

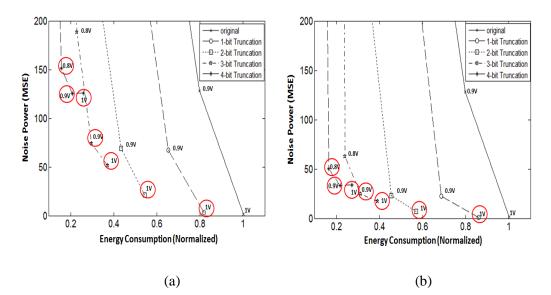

| 6.3. Noise Power vs Energy Consumption of 3x3 Gaussian filter on Lena image under                |

| voltage scaling with a) precision reduction, b) precision reduction with voltage scaling         |

|                                                                                                  |

| 6.4. Performance comparison of 3x3 Gaussian filter on Lena image; original and reduced           |

| precision filter with and without compensation101                                                |

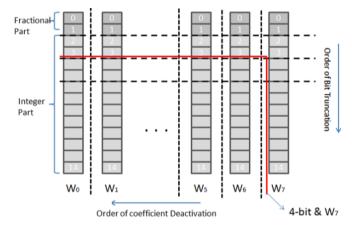

| 6.5. DCT coefficient deactivation and low order bit truncation for the 1D-DCT                    |

| coefficients                                                                                     |

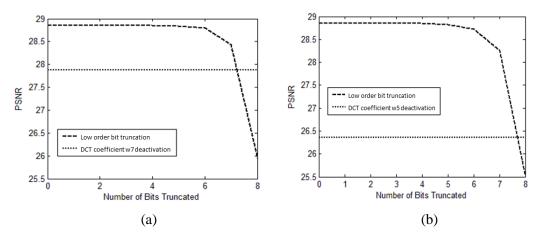

| 6.6. Comparison between bit truncation level and DCT coefficient deactivation for a) $W_{7,}$    |

| b) W <sub>5</sub> for Baboon image when Q=55104                                                  |

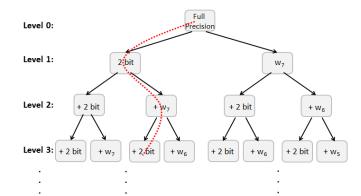

| 6.7. Binary decision tree to choose combination of coefficient deactivation and truncation       |

| level                                                                                            |

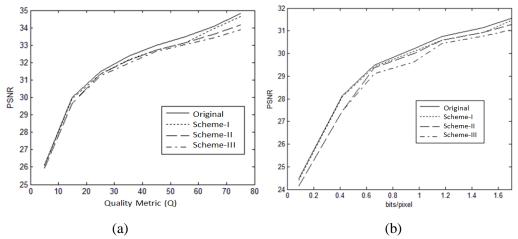

| 6.8. Performance of the resulting decision order generated using 6 training samples on           |

| test images a) Lake, and b) Elaine                                                               |

| 6.9. Energy saving at different quality levels for three candidate schemes                       |

#### CHAPTER 1

### **INTRODUCTION**

Portable multimedia devices have proliferated in the last two decades, and the number of applications supported by these devices has increased significantly. Each additional application results in higher energy consumption and since most of these devices are battery powered, it is important that every effort be made to reduce the energy cost. The challenge is to minimize this cost while executing increasingly complex functionalities with minimal degradation in algorithm performance quality. Fortunately, many of the multimedia applications do not need 100% correctness during computation and energy saving transformations are favored as long as the output quality is only mildly affected [1] [2].

There are many multimedia systems which achieve low energy consumption at the expense of low system quality. Our goal is to achieve low energy consumption with minimal degradation in quality. Fig. 1.1 shows the DCT energy consumption and final image quality for a JPEG coded sample image corresponding to three different algorithm configurations. On two ends of the spectrum are configurations with low energy and low quality (left sub-figure) and high energy and high quality (middle sub-figure). Our goal is to derive configurations with fairly low energy and reasonably high quality performance as shown in the right sub-figure. In this work, we propose several architecture and algorithm level techniques that help derive such configurations for image and video codecs.

Low Energy (9.2 nJ)High Energy (16.2 nJ)Low Energy (11.3 nJ)Low Quality (PSNR = 19dB)High Quality (PSNR = 31dB)High Quality (PSNR = 28 dB)Fig.1.1 Goal: Reduce energy consumption with minimal quality degradation

#### I. OVERVIEW OF EXISTING WORK

Three of the most effective techniques for reducing energy consumption are voltage scaling [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15], reduction in number of computations [2] [14] [16] [17] [18] [19] [20] and dynamic range adjustment [17] [20] [21] [22] [23] [24]. While voltage scaling results in significant reduction in energy consumption due to the quadratic dependence between supply voltage and energy consumption, voltage over-scaling (VOS) can lead to failures. Techniques have been developed to mitigate the errors due to critical path violation in the computation unit and memory due to VOS. While circuit-level techniques such as Razor [25] are quite effective, we propose low overhead algorithm-level techniques that use the inherent redundancy and characteristics of the data to detect and correct errors that occurred during the computation.

Unlike general purpose computing, most multimedia applications can provide decent quality even with reduced number of computations as long as the significant computations are retained. The basic idea is that all components of the computation are not equally significant and so for systems with limited resources, the more important computations are done first and the less important computations are performed later or even eliminated. Such a methodology has been successfully applied to many image and video processing algorithms [2] [19] [20].

Another popular energy-saving technique is dynamic range reduction in the datapath computation. Typically, low order bits are less important and so can be truncated to save energy. Such a methodology has been used in many multimedia kernels such as filtering [20], DCT [21] [23], FFT [5] etc. While truncation reduces energy consumption, it also introduces errors due to operation with a reduced dynamic range.

#### **II. PROBLEMS ADDRESSED**

We describe several energy-saving techniques that achieve minimum degradation in quality with low overhead for image and video codecs. While some of these techniques are general, others have been geared to exploit the algorithmic features and result in superior performance both in terms of energy consumption and algorithm performance quality.

## A. Voltage Scaling and Error Compensation in Memories:

Voltage scaling is an effective way of reducing memory power. However, aggressive voltage scaling exacerbates SRAM memory errors especially in scaled technologies. Several circuit, system and architecture level techniques have been proposed to mitigate and/or compensate for memory failures. At the circuit level, different SRAM structures such as 8T and 10T have been proposed [26] [27]. In [28], the error locations in the cache are detected using built in self test circuitry and an error address table is maintained to route accesses to an error-free locations. Many techniques make use of error control coding (ECC) such as orthogonal latin square codes in [12] and extended Hamming codes in [29]. More recently, algorithm-specific techniques have been developed for codecs such as JPEG2000 [13], MPEG-4 [10] to compensate for memory errors caused by voltage scaling. In [13], binarization and second derivative of the image are used to

detect error locations in different sub-bands in JPEG2000. These are then corrected in an iterative fashion by flipping one bit at a time starting from the most significant bit (MSB). The overall procedure has fairly high latency and power overhead. The method in [10] uses a combination of 6T and 8T SRAM cells based on read reliability, area and power consumption and applies it to a MPEG-4 implementation.

**Contribution** [9] [30]: We propose techniques that make use of voltage overscaling to reduce the energy consumption of memories with minimal effect on the system quality. We choose JPEG2000 as the demonstration platform since it is a widely used image coding standard that has applications in digital photography, high definition video transmission, medical imagery, etc [31]. This codec has large memory requirements since it processes one entire frame at a time, and consequently, large memory power consumption. For instance, it was shown in [9] [13] that in a JPEG2000 encoder, 25% to 35% power saving is possible when the memory operates at scaled voltages.

In our work, first, we characterize the different types of memory error under scaled voltage levels. Majority of the errors are exacerbated by process variations. These include variation of the transistor sizes (W/L) and variation in  $V_{th}$  due to random dopant fluctuation (RDF). Then, we propose several techniques to mitigate the effect of memory failures in JPEG2000 due to operating the memory at scaled voltages. The first scheme is an unequal error protection (UEP) scheme based on single error correction double error detection (SECDED) codes that is customized for JPEG2000. The UEP scheme assigns error control coding (ECCs) with different strengths to different subbands so that the overall memory overhead is reduced with minimal effect in performance. Next, we propose four algorithm-specific methods with different levels of complexity that do not require additional SRAM memory. These methods exploit the fact that the discrete

wavelet transform (DWT) outputs have larger values for low frequency subband coefficients and smaller values for high frequency subband coefficients and that the coefficients in a subband have similar magnitudes. Thus errors in most significant bits (MSBs) of high frequency components can easily be identified and removed.

The algorithm-specific methods allow us to operate at very high compression ratio for high memory bit error rate (BER) with small drop in performance. For instance, for compression ratio of 0.75bpp and BER= $10^{-3}$ , the proposed techniques can achieve less than 1dB drop in PSNR from the no-error case. Even for very high bit error rate of BER= $10^{-2}$ , there is only a 2.8dB degradation at 0.75bpp with no memory cost. ECCs, on the other hand, can provide decent performance when BER= $10^{-3}$  and the high memory overhead of these codes can be reduced by using our UEP scheme. However, at BER= $10^{-2}$ , the error correcting capability of fixed ECC or UEP scheme is significantly worse than the algorithm-specific methods. For compression ratio of 0.75bpp, the best ECC scheme is approximately 5dB less than the best algorithm-specific method. Furthermore, the overhead of algorithm-specific methods is very small, making it possible to easily compensate for errors introduced due to low voltage operation of SRAM in JPEG 2000 implementations.

### B. Voltage Scaling and Error Compensation in Data-path:

As in memory, an effective way of reducing the power consumption in the datapath is lowering the supply voltage. However, this could result in critical path violations leading to failures. In our work, we investigate use of voltage overscaling to reduce the energy consumption of datapath with minimal effect on the system quality. We focus on JPEG since this is part of many embedded devices for multimedia where power consumption is a very important metric. Several JPEG architectures have been proposed that trade-off power consumption and quality. The DCT architecture in [32] exploits correlation between DCT coefficients in conjunction with standard techniques such as voltage scaling, data parallelism and pipelining. Data bit-width adaptation is used in [21] to reduce the processing load of high frequency coefficient computations. A similar scheme is also investigated in [23] where truncation of up to 4 low order bits is shown to achieve 40% reduction in energy consumption of the memory and data-path.

**Contribution** [8] [33]: We first characterize the distribution of timing violations in datapath and model the errors due to aggressive voltage scaling. Most of these errors reside in high order bits that incur very excessive degradation in system quality. To compensate for these errors, we introduce an algorithm-specific technique tailored for Discrete Cosine Transform (DCT) engine in JPEG codecs. The technique exploits the fact that in  $8 \times 8$  DCT, two adjacent AC coefficients after zig-zag scan have similar values and two coefficients corresponding to higher frequencies generally have smaller values. These features are used to detect the datapath errors and then compensate for them. Operating the datapath at 0.83V (instead of the nominal 1V), results in BER= $10^{-4}$  due to voltage overscaling. For this error rate, the proposed technique achieves 3.4dB PSNR improvement compared to no correction case and approximately 1.2dB degradation compared to error-free performance for a 20% reduction in power consumption. Thus the proposed techniques allow JPEG codecs to have lower power consumption with only a mild degradation in image quality.

#### C. Dynamic Range Reduction in Datapath:

Reducing dynamic range is an effective technique to reduce energy consumption. However, they incur degradation in system quality. In [16], low order bit truncation is applied to motion estimation in video encoding; instead of using 8 bits, only 4 or 5 of the higher order bits are kept to reduce dynamic energy consumption by approximately 60%. The truncation based technique in [23] achieves up to 40% energy saving for DCT while causing approximately 0.2 reduction in mean structural similarity (MSSIM) (which corresponds to approximately 15dB loss in peak signal to noise ratio (PSNR)).

**Contribution** [17] [34]: We investigate use of bit truncation to reduce the power consumption of signal processing kernels such as FIR filter and DCT kernels. Low order bit truncation introduces errors which have to be compensated to minimize quality degradation. To handle the errors, we propose a compensation unit based on unbiased estimation of the truncation noise. For 4-bit truncation in DCT computation in JPEG, such a scheme achieves 23% power savings with only 0.6dB drop in PSNR. Thus, this technique is very effective in improving the PSNR performance with a small circuit overhead.

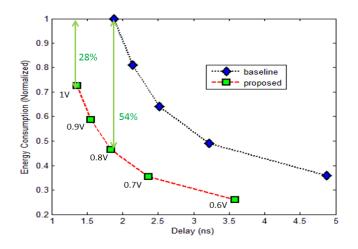

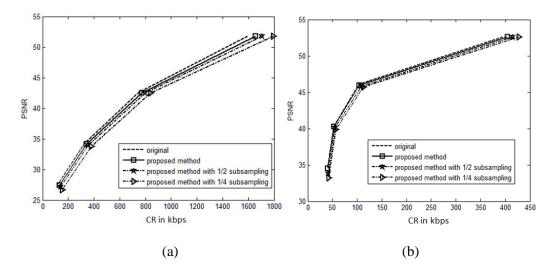

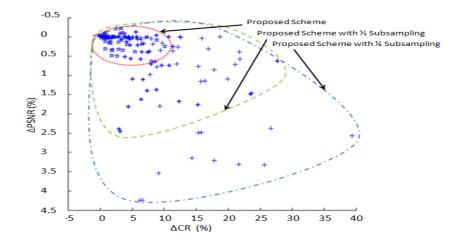

We also propose a MSB truncation scheme for sum of absolute difference (SAD) computation in motion estimation and inter-prediction. The proposed scheme uses the statistics of absolute difference (AD) and SAD computations to approximate the computations. Specifically, it exploits the fact that: i) most of the AD values are small, due to locality of current and reference blocks, and that ii) most of the large AD values are for blocks that are likely not to be selected, and thus these values can be approximated. In the proposed scheme, large AD values are detected using special logic and the corresponding SAD value updated with a correction factor. We also propose variants of this scheme based on sub-sampling which further reduce the energy consumption. The corresponding architecture has a lower critical path delay compared to the baseline SAD architecture and achieves 28% energy reduction at nominal voltage.

For iso-throughput, i.e., when the throughput is the same as the baseline architecture, it achieves 54% energy reduction while incurring less than 2% increase in compressed data rate and approximately 0.1% reduction in PSNR. If larger increase in compressed data rate is tolerable, the proposed scheme with ½ sub-sampling has approximately 90% reduction in energy consumption with ~7% increase in compressed data rate and less than 1% reduction in PSNR.

### D. Hybrid Schemes for Energy Reduction in Data-path

Voltage scaling, reducing number of computation and dynamic range reduction all achieve energy savings; however their combination achieves even higher energy savings. Selective deactivation of DCT coefficient based on the operating voltage has been proposed in [35]. It has been shown that 41% to 90% power saving is possible compared to baseline scheme with up to 10dB degradation in PSNR. A similar approach is applied in [36] for color interpolation where only less important computations are affected by voltage scaling and process variation. Such a scheme achieves 40% power savings with 5dB PSNR degradation.

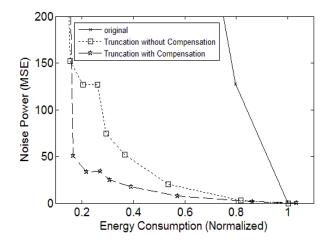

**Contribution** [34]: We study the combination of voltage scaling and dynamic range reduction for low pass FIR filter kernels. The errors due to increase in critical path delay during voltage scaling are reduced by truncating the lower order bits which causes a reduction in the critical path. The noise that is introduced due to truncation is compensated by using an unbiased estimator to calculate the average noise power due to truncation and compensating for it. For a MAC based FIR filter, such a scheme achieves 85% energy saving for fairly low noise level. We also study the combination of computation reduction and dynamic range reduction for low-pass FIR filter and DCT. We propose a scheme that chooses which DCT coefficients have to be deactivated and the

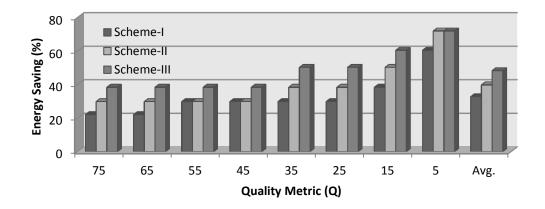

number of bits to be truncated based on the quality metric, Q. We derive combinations of deactivation and truncation for different acceptable PSNR degradations across the whole range of Q. Simulation results show on average, 33% to 46% reduction in energy consumption while incurring 0.5dB to 1.5dB degradation in PSNR performance of JPEG.

#### **III. ORGANIZATION**

The layout of this report is as follows. Chapter 2 briefly describes the schemes to reduce power consumption in CMOS circuits. It also include a brief review of the image and video codecs that were used in this work. In Chapter 3, failures due to voltage scaling in memories are investigated. Unequal error protection and algorithm specific techniques are proposed to mitigate errors in tile memory of JPEG2000 image codecs. Chapter 4 describes the voltage scaling and error compensation techniques in data-path for JPEG. An algorithm-specific technique is proposed that exploits inherent redundancy in the DCT transform of JPEG to minimize the voltage scaling induced performance degradation. Chapter 5 addresses the effects of reducing dynamic range in datapath computations. Techniques to compensate truncation noise due to low order bit truncation using unbiased estimator are presented along with a high order clipped computation scheme that is applicable for motion estimation and intra prediction schemes. Chapter 6 describes combination of different energy saving techniques such as voltage scaling, number of computation and dynamic range reduction for two case studies, FIR filtering and DCT transform in JPEG. Chapter 7 concludes the thesis.

#### **CHAPTER 2**

#### BACKGROUND

#### I. SOURCES OF POWER CONSUMPTION

There are three main sources of power consumption in CMOS circuits: dynamic (switching), short circuit current, static (leakage) as illustrated in equation (2.1) [3].

$$P = \underbrace{\alpha C_L V_{dd}^2 f_{clk}}_{dynamic} + \underbrace{I_{sc} V_{dd}}_{short \ ciruit} + \underbrace{I_{leak} V_{dd}}_{static}$$

(2.1)

The dynamic component is a function of  $\alpha$ , the probability of transition, i.e. average number of times a node makes a power consuming transition in one clock period,  $C_L$ , the load capacitance,  $V_{dd}$ , the supply voltage and  $f_{clk}$ , the clock frequency.  $I_{sc}$  is the short circuit current which arises when both the pmos and nmos are on during switching, thereby conducting a direct path current from supply to ground;  $I_{leak}$  is the leakage current due to subthreshold leakage, direct tunneling gate leakage, source-substrate and drain-substrate reverse biased pn junction leakage. Of the three components, the dynamic component is the largest. For instance, in 45nm technology for an SRAM memory, it is about 55% of the total power consumption, while static power consumption is about 40% [37]. Next we describe some well-known techniques to reduce power consumption in CMOS circuits.

#### II. POWER REDUCTION IN DYNAMIC COMPONENT

The dynamic power consumption is given by  $\alpha C_L V_{dd}^2 f_{CLK}$  and so any reduction in the switching activity or capacitance or supply voltage or clock frequency results in lower power.

#### A. Power Reduction by Voltage Scaling

The product of switching activity ( $\alpha$ ) and load capacitance ( $C_L$ ) is defined as effective capacitance ( $C_{eff}$ ). While  $C_L$  reduces with technology scaling,  $C_{eff}$  can be minimized through choice of logic function, logic style, and exploiting signal statistics [38].

### B. Power Reduction by Voltage Scaling

Voltage scaling is one of the most effective techniques to reduce dynamic power consumption due to its quadratic relation as shown in equation (2.1). It is effective for reducing the power consumption of datapath, memory and even interconnects. However, it increases the latency of the circuitry and promotes delay induced errors for a given clock period. The relation between  $V_{dd}$  and latency of a circuit can be expressed as follows:

$$T_d \propto \frac{C_L V_{dd}}{(V_{dd} - V_{th})^{\gamma}}$$

(2.2)

where  $\gamma$  is 2 for long channel devices and approaches to ~1.2, 1.3 for short channel devices [38]. Delay of the device increases dramatically as  $V_{dd}$  approaches to  $V_{th}$ , which makes voltage scaling harder for scaled technologies due to smaller  $\frac{V_{dd}}{V_{th}}$  ratio.

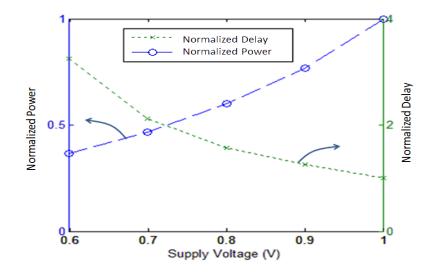

Fig. 2.1 illustrates the normalized power saving and delay increase of a 14-bit ripple carry adder (RCA) with respect to nominal voltage using 45nm PTM models [40]. When the voltage is scaled to 0.8V, there is approximately 40% reduction in power consumption of the adder and a 46% increase in the delay. Thus aggressive voltage scaling can lead to timing violations.

Fig. 2.1. Power and delay profiles of 14-bit RCA adder under voltage scaling

Even larger power savings can be obtained by operating the SRAM memory at scaled voltages. For instance, for a 32nm 6T SRAM memory structure whose nominal voltage is 0.9V, operating at 0.6V results in power saving of approximately 80% in write and read while leakage power also drops by more than 80%. However, such aggressive voltage scaling results in  $10^{-2}$  BER for the SRAM due to incorrect voltage sharing and timing violations.

To exploit voltage scaling with minimal effect on overall system performance, schemes based on fine-grained multiple supply voltage  $(V_{dd})$  levels have been introduced. For a given combinational logic, nominal voltage level  $(V_{dd}^H)$  is assigned for circuit components in the critical path while lower voltage level  $(V_{dd}^L)$  is used for components in the other non-critical paths. Level converters are placed between high and low voltage levels [41] which consume extra power and diminish the effect of multiple voltage levels. To reduce the overhead, only a few voltage levels are used and a large chunk of computing resources are operated at the same voltage [42].

#### C. Power Reduction by Architecture Modification

Circuit parallelization and pipelining are two popular techniques used to reduce power without throughput degradation. The throughput of a single processing unit at clocked at f Hz can be obtained by using M parallel units operating at f/M Hz. Now as operating frequency is reduced, each of the processing units has M times longer time to complete the processing. This allows the voltage to be scaled down to exploit the timing slack, and results in significant reduction in power. For instance, in 45nm technology, if two processing units are used, the voltage can be scaled to 0.7V instead of nominal voltage (1V) resulting in ~50% power saving. Adding pipeline latches in the critical path also allows for operating at lower voltages without affecting the throughput. While additional pipeline latches introduce extra capacitance, the overhead is quite small [39].

Other techniques include ordering of input signals to reduce the transition activity, which also reduces the power consumption. In [43], it has been shown that for a 9 tap FIR filter implemented on a DSP board, the power consumption can be reduced by 25 to 40% by reordering the filter coefficients. Such a reordering scheme is very effective for symmetric filters that are widely used in multimedia such as 2D-Gaussian filtering.

Resource sharing is another power reduction technique that utilizes multiplexed architectures in which multiple functional operations can be mapped to a less number of computational units. Even though this increases the switching activity, the circuit area is reduced which in turn reduces leakage power consumption.

## D. Power Reduction by Algorithm Modification: Reducing Number of Computations

The number of computations can be reduced by choosing a smarter algorithm with a lower complexity. Examples include Fast Fourier Transform implementation of the Discrete Fourier Transform, differential tree search based vector quantization [3], etc. However, most of the time reduction in the number of computations comes with a performance hit. For instance, in block matching that is used in motion estimation, heuristic algorithms such as three step search and diamond search have lower complexity but sub-optimal performance. These search algorithms are used when the performance requirements are not that stringent and the available energy is low [18]. Now for each search algorithm, sub-sampling can also be used to further reduce the number of computations [6] [16] [17]. If 1/s is the subsampling ratio, then these schemes reduce the number of absolute difference computations in motion estimation by 1/s and result in significant energy reductions. Two subsampling schemes for s=2 and s=4 tailored for 8x8 block based motion estimation are illustrated in Fig. 2.2 [17]. These schemes reduce the number of AD computations by 1/s, and for iso-throughput, they also allow us to scale the voltage of the system, resulting in significant energy reduction.

Another way of reducing the number of computations with minimal effect in image quality is by exploiting the fact that different portions of the computation have different levels of significance on the overall system quality. For instance, most of the image energy of the DCT resides in the low frequency coefficients and higher frequency coefficients can be sacrificed when good enough quality is achieved [2] [20]. Similarly, in FIR filtering, larger filter taps contribute more to system performance, and so sorting the impulse response filter taps in decreasing order of magnitude and computing on larger coefficients first helps achieve energy saving with reduced overall quality degradation [20]. The concept is related to progressive transmission where data or image transmission is halted when decent quality acquired as in [19].

| S |   | s |   | s |   | s |   |

|---|---|---|---|---|---|---|---|

|   | s |   | s |   | s |   | s |

| s |   | s |   | s |   | s |   |

|   | S |   | S |   | S |   | s |

| S |   | s |   | s |   | S |   |

|   | s |   | S |   | S |   | s |

| s |   | s |   | s |   | s |   |

|   | s |   | s |   | S |   | s |

| S | S | S    | S |  |

|---|---|------|---|--|

|   |   |      |   |  |

| S | S | S    | S |  |

|   |   |      |   |  |

| S | S | S    | S |  |

|   |   |      |   |  |

| S | S | S    | S |  |

|   |   |      |   |  |

|   |   | <br> |   |  |

Fig. 2.2. Sub-sampling patterns for 1/2 and 1/4 schemes

#### III. POWER REDUCTION OF STATIC COMPONENT

The static component of power consumption is due to subthreshold leakage, direct tunneling gate leakage, source-substrate and drain-substrate reverse biased pn junction leakage. The significance of static power consumption in todays' systems is rapidly increasing due to continually shrinking transistor geometry and larger die size.

The subthreshold current  $(I_{sub})$  is due to weak conduction between source and drain of the MOSFET when the gate voltage is below the threshold voltage  $(V_{th})$ . It occurs due to thermal emission of carriers over the potential barrier set by the threshold [38].  $I_{sub}$  can be expressed as

$$I_{sub} = I_0 e^{\frac{V_{gs} - V_{th} + \eta V_{ds} - k\gamma V_{sb}}{nv_T}} \left(1 - e^{-\frac{V_{ds}}{v_T}}\right)$$

(2.3)

where  $I_0$  is the current at  $V_{th}$  and is dependent on geometry and process. *n* is a process dependent term and is typically 1.3-1.7 for CMOS.  $V_{ds}$  is the drain to source voltage, and  $v_T$  is the thermal voltage. The drain induced barrier lowering (DIBL- $\eta V_{ds}$ ) effect reduces the threshold voltage of the transistor and increases the subthreshold current that results in higher static power consumption. The body biasing voltage ( $V_{sb}$ ) also modulates the threshold voltage and changes the leakage current. Techniques based on use of multiple threshold voltage levels have been used to manage leakage power. However, threshold voltage not only affects leakage power, but also affects dynamic power and latency. Thus, fine-grained multiple threshold voltage schemes use higher threshold voltage for the components that are off the critical path and nominal threshold voltage levels for those on the critical path. Body biasing is another widely used technique for leakage control. It is used to control the energy gap between the conduction bands of the gate (polysilicon) and body (SiO<sub>2</sub>), which in turn changes the threshold voltage. Use of stacked transistors also reduces the  $V_{ds}$  value per transistor which consequently reduces the leakage current.

Gate leakage is due to tunneling of carriers from the bulk silicon to gate which is inversely proportional to gate thickness and material conductivity. With technology approaching 1nm for gate thickness, high-k materials are used to maximize the insulation between gate and body, thereby reducing the gate leakage problem [38]. Reverse biased pn junction between source/drain and body causes leakage under high electric field (>  $10^6 V/cm$ ) in which electrons tunnel through the junction [41]. Changing the doping concentration of the body and/or applying reverse bias voltage are two common techniques to reduce pn junction current [38].

### IV. OVERVIEW OF IMAGE/ VIDEO CODING ALGORITHMS

In this section, we review general flow of image and video processing standards such as JPEG, JPEG2000 image coding standards and H.264 video coding and their important processing kernels.

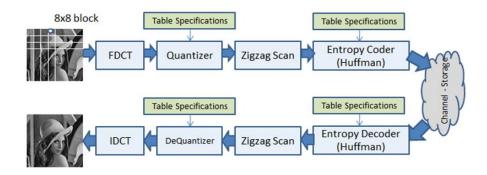

The general block diagram of a JPEG encoder/decoder is shown in Fig. 2.3. The original image in pixel domain is divided into  $8 \times 8$  blocks which are transformed into frequency domain using 2 dimensional (2-D) DCT. This is followed by quantization, where the coefficients are scaled by factors that depend on the desired image quality and/or compression rate. Next, zig-zag scanning is used to order the  $8 \times 8$  quantized coefficients into a one dimensional vector ( $1 \times 64$  format) where low frequency coefficients are placed before the high frequency coefficients. The entropy coder generates the compressed image using Huffman coding.

Fig. 2.3. Block Diagram of JPEG

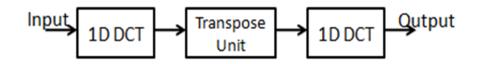

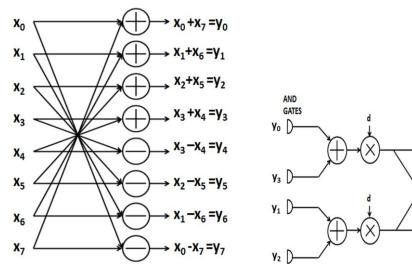

**Discrete Cosine Transform (DCT):** 2-D DCT is typically implemented using 1-D DCTs along rows (columns) followed by 1-D DCT along columns (rows) as illustrated in Fig. 2.4.

Fig. 2.4. 2D DCT architecture using 1-D DCTs

1-D DCT transform of size 8 that is used in JPEG can be expressed as follows:

$$W_i = \frac{c_i}{2} \sum_{k=0}^{7} x_k \cos \frac{(2k+1)k\pi}{16} \qquad c_i = \begin{cases} \frac{1}{\sqrt{2}} & i = 0\\ 1 & i = 1, \dots, 7 \end{cases}$$

(2.4)

where  $x_k$ 's are input pixels in row or column order and  $W_i$ 's are the corresponding outputs. Typically 8-point DCT is computed along rows and the coefficients stored in the transpose unit so that data for the 8-point DCT along columns can be obtained efficiently. The properties of the coefficient matrix are used to reduce the number of multiplications. We use the following method of implementing the odd and even coefficients.

$$\begin{bmatrix} W_0 \\ W_2 \\ W_4 \\ W_6 \end{bmatrix} = \begin{bmatrix} d & d & d & d \\ b & f & -f & -b \\ d & -d & -d & d \\ f & -b & b & -f \end{bmatrix} \begin{bmatrix} x_0 + x_7 \\ x_1 + x_6 \\ x_2 + x_5 \\ x_3 + x_4 \end{bmatrix}$$

(2.5)

$$\begin{bmatrix} W_1 \\ W_3 \\ W_5 \\ W_7 \end{bmatrix} = \begin{bmatrix} a & c & e & g \\ c & -g & -a & -e \\ e & -a & g & c \\ g & -e & c & -a \end{bmatrix} \begin{bmatrix} x_0 - x_7 \\ x_1 - x_6 \\ x_2 - x_5 \\ x_3 - x_4 \end{bmatrix}$$

(2.6)

$$a = \frac{1}{2}\cos\left(\frac{\pi}{16}\right), b = \frac{1}{2}\cos\left(\frac{2\pi}{16}\right), c = \frac{1}{2}\cos\left(\frac{3\pi}{16}\right), d = \frac{1}{2}\cos\left(\frac{4\pi}{16}\right), e = \frac{1}{2}\cos\left(\frac{5\pi}{16}\right), f = \frac{1}{2}\cos\left(\frac{6\pi}{16}\right), g = \frac{1}{2}\cos\left(\frac{7\pi}{16}\right).$$

The DCT engine is implemented by 12 bit integer operations in [21] [45].

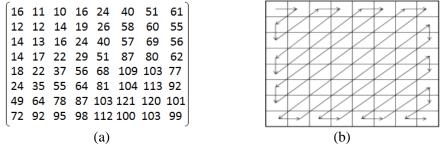

**Quantizer:** The rate and quality of the image is determined by the quantization level. In order to achieve different quality and compression rates, the quantization matrix is scaled by quality factor that is a function of the quality metric (Q), which ranges from 1 to 100 [46]. A lower Q results in lower image quality and compression rate. Fig. 2.5 illustrates JPEG luminance quantization table for Q=50. Note that high frequency components which are at the bottom right corner are quantized aggressively while low frequency components which are at the top left corner are mildly quantized. Fig. 2.5 also shows the

zig-zag scanning order. The very first element is the DC coefficient which is encoded in differential order by subtracting the DC coefficient of the previous block and encoding the difference using a Huffman table in baseline JPEG; the rest of the coefficients are AC coefficients, which are encoded using another Huffman table specified in the standard [44].

In Chapter 4, we use the fact that two adjacent AC coefficients after zig-zag scan have similar values, and that coefficients corresponding to higher frequencies generally have smaller values. These are used to derive schemes that correct errors in the datapath.

Fig. 2.5. a) Luminance Quantization Matrix for Q = 50; b) Zigzag scan order

**Entropy Coder:** Entropy coding of JPEG exploits the fact that most of the quantized coefficients at high frequencies consists are small numbers, if not zeros. Thus, instead of coding each zero pixel value separately, the entropy coder counts the number of zeros and uses it to specify the run-length of the zeros. Furthermore, the coder uses small codewords for small pixel values to effectively compress the non-zero pixels.

### B. JPEG2000

JPEG2000 is a widely used still image compression technique. It supports progressive image and region of interest coding and has better visual quality and compression performance compared to JPEG. In fact, it achieves more than 2 dB improvement in PSNR for the same compression rate compared to JPEG [31].

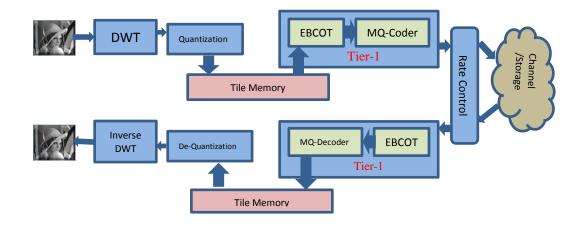

The general block diagram of the JPEG2000 encoder/decoder is illustrated in Fig. 2.6. The original image (in pixel domain) is transformed into frequency sub-bands using the discrete wavelet transform (DWT) engine followed by quantization and stored into tile memory. Compressed image is obtained after embedded block coding with optimized truncation (EBCOT) processing followed by rate control. While rate control can be achieved by adjusting quantization level or by EBCOT, EBCOT provides gradual improvement (unlike quantization) and is more favorable.

Fig. 2.6. Block diagram of JPEG2000

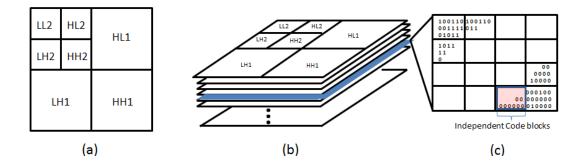

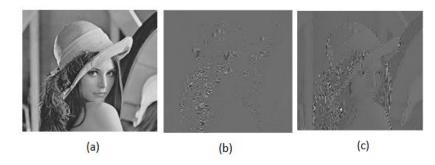

The 2 level sub-band representation of the DWT output is shown in Fig. 2.7-a. The input image of size NxN is processed by high-pass (H) and low-pass (L) filters along rows and columns followed by subsampling to generate the first level outputs of size N/2xN/2: HL1 (high-pass along row followed by low-pass along columns), HH1 (high-pass along rows followed by high-pass along columns), LH1 (low-pass along rows and high-pass along columns) and LL1 (low-pass along rows and columns). The LL1 outputs are further processed by high-pass and low-pass filters along the rows and columns to generate the second level outputs, HH2, HL2, LH2, and LL2, each of which is of size N/4xN/4. For a natural image, the low frequency sub-bands are likely to contain

coefficients with larger values while higher frequency sub-bands contain coefficients with small values. Therefore the most significant bits of high frequency sub-bands (such as HL1, LH1, HH1) typically consist of all zeros. We exploit this fact in developing the memory error compensation techniques in Chapter 3.

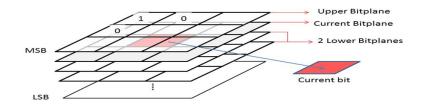

The DWT outputs are processed by Tier-1 coding which exploits the redundancy of these outputs in different bitplanes. Tier-1 coding in JPEG2000 takes  $32 \times 32$  or  $64 \times 64$  bits from each bitplane and encodes them independently. This stage has two main sections: EBCOT and MQ-Coder. EBCOT uses context based coding for each bit in a given bit plane, MQ-Coder then calculates its probability and determines the final compressed bit stream. For the all-zero bit plane, tier-1 coding skips processing that bit plane and only adds one bit information to the header of the file. Fig. 2.7-b and c illustrate the bit plane representation and independent code blocks ( $32 \times 32$  and  $64 \times 64$ ) of an image.

In most implementations, DWT coefficients are stored in a memory as shown in Fig. 2.7. In general, the tile memory is typically a SRAM because of its low latency. In scaled technologies, there may be errors in these memories as will be described in Chapter 3. As a result the DWT output that is stored in the tile memory is different from the data that is read out of the memory for EBCOT processing. In Chapter 3, we describe techniques to compensate for these errors.

Fig. 2.7 a) Sub-band representation of DWT output b) Bit plane representation of Subband c) Code block representation of bit planes

#### C. Video Codec (H.264)

In a video codec such as in H.264 [47], frames are partitioned into smaller nonoverlapping blocks typically of size 8x8 or 16x16 (macroblocks). Two types of encoding are employed for a given frame: intra (spatial) and inter (temporal). In the inter block coding, motion estimation (ME) is used to remove temporal redundancy across consecutive frames [16]. In intra block coding, pixels of the current macroblock (MB) are estimated using the adjacent pixels in the same frame.

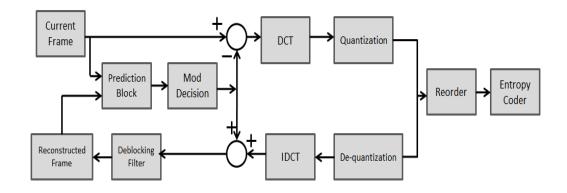

The general block diagram of the encoding flow is illustrated in Fig. 2.8. Prediction blocks using ME and intra-prediction are computed and the best match is subtracted from the current block to remove redundancy in the video frames. The residual is transformed using  $4 \times 4$  DCT followed by a quantizer with a predefined step size. Quantizer has 51 configuration each of which results in different bit rate and video quality. The remaining data is fed into an entropy coder (context adaptive variable length coding (CAVLC) or binary arithmetic coding (CABAC)) [48]. Residual frame is regenerated by back tracing the DCT and quantization steps that contracts the reference

frame. In the last stage, deblocking filter removes the blocking artifacts due to DCT and quantization processes [49].

Fig. 2.8. Block Diagram of the Video Encoder

**Inter Prediction (Motion Estimation):** ME in video codec is used to remove the temporal redundancy in the consecutive frames. Cost functions are based on Lagrangian multiplier, sum of absolute transform difference (SATD) and sum of absolute difference (SAD) to find the best match [16]. The mode that minimizes distortion and reduces the code rate is then chosen. Due to its simplicity, the sum of absolute difference (SAD) is widely used in real time implementation. Here the absolute difference (AD) of pixels corresponding to the same location in the reference and current blocks are computed and then summed over all the pixels in the block. SAD can be expressed as:

$$SAD(P_{cur}, P_{ref}) = \sum_{m=0}^{B-1} \sum_{n=0}^{B-1} |P_{cur}(m, n) - P_{ref}(m, n)|$$

(2.7)

where the current block is of size  $B \times B$ , and  $P_{cur}$  and  $P_{ref}$  refer to current and reference blocks, respectively. The block that achieves the lowest SAD value is the block that is selected for motion compensation. In Chapter 5, we use the fact that most of the AD values are small due to locality of current and reference blocks, and that most of the large AD values are for blocks that are likely not to be selected, and thus these values can be approximated. This helps in reducing the number of SAD computations.

There are several search strategies to find the candidate blocks in a search area. Full search, where all reference block positions are searched, is computationally intensive and thus rarely used. Instead, several heuristic algorithms with lower complexity but suboptimal performance are used. A comprehensive list of search strategies has been described in [50]. We use two popular strategies, namely, three step search (TSS) [51] and diamond search (DS) in our work [52]. The proposed techniques are essentially independent of the search algorithm and can be used in conjunction with other search methods.

H.264 supports sub-pixel motion estimation with half and quarter pixel accuracy. Following the integer ME, sub-pixels are estimated at four neighboring directions of the current pixel using interpolators. A 6-tap filter whose taps are {1,-5, 20, 20,-5, 1} is used in half-pixel and bilinear interpolation is used in quarter pixel ME of H.264.

**Intra Prediction:** In intra prediction mode of H.264, MBs are predicted using the adjacent MBs that are already encoded. There are two main types of prediction modes in luminance compression: Intra\_4x4 (I4MB) and Intra\_16x16 (I16MB) and one mode for chrominance component: Intra\_8x8.

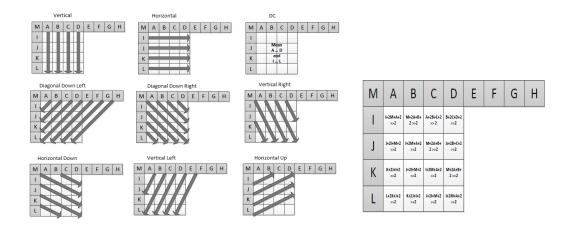

In Intra\_4x4 mode, each MB is partitioned into sixteen 4x4 coding blocks. There are 9 different prediction modes for each 4x4 block that are illustrated in Fig. 2.9. These modes are called vertical, horizontal, DC, diagonal down left, diagonal down right, vertical right, horizontal down, vertical left and horizontal up where they are suited to predict regions with specified direction of intensity change. Thirteen boundary pixels

from previously encoded blocks are used to generate prediction blocks (PB). Each PB has sixteen pixel values that are computed using some or all of the boundary pixels. The direction of the prediction is shown with arrows starting from boundary pixels whose weighted average generates the predicted value. For instance, predicted values for mode 4 (Diagonal down right) is illustrated in Fig. 2.9. On the other hand, predicted values for DC mode is the mean of boundary pixels L to K and A to D. Similarly, Intra\_16x16 and Intra\_8x8 have four combinations with different direction of prediction [47]. SAD given in equation (2.7) is widely used for mode decision in intra-prediction.

Fig. 2.9. a) Nine prediction modes of Intra\_4x4 b) Diagonal Down Right

#### **CHAPTER 3**

# COMPENSATING FOR MEMORY ERRORS CAUSED BY VOLTAGE SCALING: CASE STUDY JPEG2000

#### I. INTRODUCTION

Voltage scaling is an effective way of reducing memory power. Unfortunately aggressive voltage scaling results in memory failures. In this chapter, we describe several ECC and algorithm-specific techniques to mitigate the effect of memory failures caused by low voltage operation of SRAM memory in JPEG2000 codecs. First, we analyze the failures in SRAM memories in Section II. Then, we propose an unequal error protection (UEP) scheme that is customized for JPEG2000 in Section III. The UEP scheme assigns ECCs with different strengths to different subbands so that the overall memory overhead is reduced with minimal effect in performance. Next, we describe four algorithm-specific techniques with different levels of complexity that do not require additional SRAM memory in Section IV and V. These techniques exploit the characteristics of the discrete wavelet transform (DWT) coefficients and use these to identify and correct the errors. They allow the codec to operate at a high performance level even when the number of memory errors is quite high.

#### II. POWER REDUCTION IN MEMORIES

In this section, we investigate the effects of voltage scaling on SRAM memory performance. Specifically, we analyze its effect on bit error rate (BER) of the low voltage SRAM memories.

#### A. SRAM Failure Analysis

There are several factors that affect the failure in SRAMs: hard errors which are mainly due to manufacturing (random dopant fluctuations (RDF), channel length, and width modulations), temperature, aging, and soft errors which are primarily due to alpha particles which cause memory cells to lose their charge. As transistor sizes scale down, the number of soft errors increases since the probability of hitting multiple transistors by the same alpha particle gets larger [12] [53] [54]. The number of soft errors also increases exponentially as voltage is scaled down. However, the overall failure rate in memories is still dominated by RDF and channel length modulation [37] [55].

RDF is the result of random distribution of dopant atoms in the transistor channel. The effect of RDF on threshold voltage is typically modeled with an additive iid Gaussian distributed voltage variation. Standard deviation of this model is highly dependent on manufacturing and transistor sizing [55]. Variance of threshold voltage of a MOSFET is proportional to  $\sigma_{VT} \sim \frac{EOT}{\sqrt{L_t * W_t}}$ , where *EOT* is oxide thickness, and  $L_t$  and  $W_t$ are length and width of the transistor, respectively. Fig. 3.1 shows the trend in threshold

Fig. 3.1.  $\sigma_{VT}$  scaling trend with and without oxide scaling [37] [55]

voltage variation due to RDF in scaled technologies from [37] [55]. For 32nm,  $\sigma_{VT}$  is approximately between 40 to 60mV. With the help of high-K materials such as SiON, HfSiON, the thickness of oxide can be scaled down thereby reducing the variation in threshold voltage.

In addition to random variations, there are systematic variations in threshold voltage that can be modeled as correlated Gaussian random process [56]. Variance for systematic variations depends on the distance between two transistor positions in the chip. However, in this chapter, we focus on random variations since they are the major source of cell failures in SRAM. The effect of other parameters (such as temperature, aging, etc.) can be modeled as an increase in the threshold voltage variation.

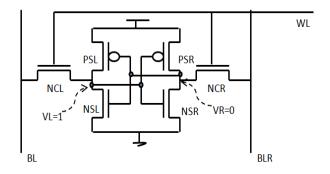

Next, we describe the causes of errors in a typical 6T SRAM cell illustrated in Fig. 3.2. NCR and NCL are control transistors which are activated in the case of a read and write operation. BL and BLR lines, which have very high capacitive values, are used to retrieve or store a bit into the cell. These lines are precharged to the same value at read and opposite values at write cycles. There are three main factors that contribute to overall hard error rate: read, write and access failure [28] [57].

Fig. 3.2. Schematic of a SRAM cell

During read operation after control signal (WL) is turned on, voltage division occurs between one of the control transistors and the NMOS in the same side. Read failure is the result of unbalanced voltage sharing at the read node (VR - Fig. 3.2) which causes flipping of the stored bit in the cell. Increase in  $V_{th}$  of NMOS transistors NSR, NSL and/or reduction in  $V_{th}$  of control transistors NCL, NCR increase the probability of read failure.

During write operation, bit lines are charged to opposite values depending on bit value that is stored. In order to have a successful write, the node between PMOS and control transistor (VL –Fig. 3.2) should be reduced below a voltage level. Increase in  $V_{th}$  of control transistors and/or drop in  $V_{th}$  of PMOS devices increases the probability of failure in the write operation.

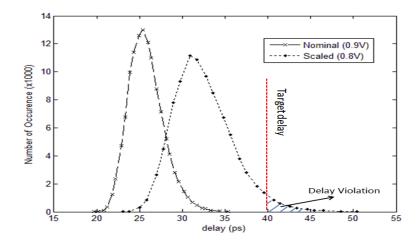

Increase in  $V_{th}$  of control transistors and NMOS devices can cause access time violations. However, for this application, the delay constraint is relaxed and access time violation is not an issue. So in the rest of the paper, we consider total error rate to be the union of read and write failure. For instance, Fig. 3.3 illustrates the delay variation distributions of an SRAM cell when the voltage is scaled from nominal (0.9V) to 0.8V while the target delay is 40ps.

SRAM failure analyses have been investigated by several researchers [57] [28] [58] [55] [27] [10]. In [57] and [28] statistical models of RDF are used to determine read, write failure and access time variations. One bit cell failure probability is considered and long channel transistor models are used to derive analytical current equations. In [58], read and write noise margin of 6T SRAM structure is used to calculate reliability of the memory. Importance sampling is applied in [27] to reduce the sample size and improve

the speed of simulations. In [55], statistical techniques are used to model the tail distribution of access time when the error rates are very low. In [10], read failure rate of 6T SRAM structure at nominal (typical) corner for 65nm technology is shown to differ from  $10^{-8}$  to  $10^{-3}$  when voltage is dropped from nominal value of 1V to 0.6V. Moreover, at scaled voltage levels, write failure rate is evaluated to be  $10^{-3}$  for the same technology.

Fig. 3.3. Delay distribution of a single SRAM read operation

We studied the two types of failure due to RDF and channel length variation for 32nm technology using Hspice with high performance predictive technology models (PTM) from [40]. A SRAM cell with bitline load value equal to that 256 cells with half of them storing '1' and the other half storing '0' is simulated using Monte Carlo simulations. The overall BER for different levels of RDF is calculated for 5% channel length variation at different supply voltages. Each transistor is sized using minimum length (L=32nm). To estimate failure rates, we follow a procedure similar to that given in [57].

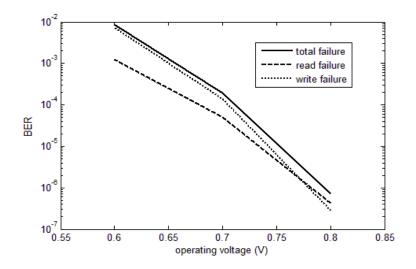

Fig. 3.4 illustrates the read, write and total failure rates for  $\sigma_{VT}$ =40mV from 0.8V to 0.6V. At the nominal voltage of 0.9V, the BER is estimated to be 10<sup>-10</sup>. At lower voltages, the BER are very high. For instance, at 0.7V, the BER is 10<sup>-4</sup> and at 0.6V, it climbs to 10<sup>-2</sup>. Such high error rates were also reported in [10] [57].

Fig. 3.4. Read, write and total failure probability of SRAM in 32nm technology for different voltage levels when  $\sigma_{VT}$ =40mV

Operating at low voltage levels saves both dynamic and static power. Our simulations show that the read (write) power of the SRAM cells (without read/write circuitry) can be reduced as much as 52% (71%) when the voltage is scaled to 0.7V and 72% (84%), when the voltage level is scaled to 0.6V. This is at the expense of a significant increase in the number of memory errors; techniques to compensate for these errors will be described in the following sections

#### B. Previous Work on Compensating for SRAM Errors

Several circuit, system and architecture level techniques have been proposed to mitigate and/or compensate for memory failures. At the circuit level, different SRAM structures such as 7T, 8T and 10T have been proposed [26] [27] [59] [60]. In 8T and 10T

structures, data path for read and write operation are separated to increase the robustness of the operations. However, additional circuitry increases leakage power and circuit area by approximately 20% to 30%. To reduce the impact of variations and improve stability, boosting and suppressing voltage levels for read and write operations have been described in [37]. However, the additional voltage converters and controlling circuitry increase the complexity of the system.

Architecture level techniques have been proposed to avoid faulty bits using defect maps in [28] [61] [62]. In [28], the error locations in the cache are detected using built in self test circuitry and an error address table is maintained to route accesses to error-free locations. Row and column redundancy have been effectively used for low error rates in [61]. For high error rates, the memory area overhead is significant and it is no longer a viable option. In [62], 25% to 50% of cache memory capacity is traded-off for reliable operation at very low voltage levels. The method involves identifying and disabling defective portions of the cache at word level and bit-level granularities.

Many techniques make use of error control coding (ECC) [12] [29] [63]. In [12], orthogonal latin square codes are used to trade-off cache size with correction capability. Extended Hamming codes which provide single error correction, double error detection (SECDED) have been used for several years to combat failures in memory systems [29]. Their simple structure makes them appealing for applications that require low latency and power consumption. To increase the error correction capability, a two dimensional coding (product code) is used in [37]. Although this scheme can handle errors that occur within a certain square shaped memory region (smaller than 32x32), correction capability degrades when errors are randomly distributed over the whole memory.

More recently, algorithm-specific techniques have been developed for JPEG2000 [13], MPEG-4 [10]. These techniques mitigate system degradation due to memory failures using additional features that are intrinsic to the algorithm. In [13], binarization and second derivative of the image are used to detect error locations in different sub-bands in JPEG2000. These are then corrected in an iterative fashion by flipping one bit at a time starting from the most significant bit (MSB). The overall procedure has fairly high latency and power overhead. The method in [10] uses a combination of 6T and 8T SRAM cells based on read reliability, area and power consumption and applies it to a MPEG-4 implementation. The method in [11] is a general technique where the memory banks that store MSBs operate at a different voltage level than the ones that store LSBs. This is shown to achieve 45% power reduction with slight degradation in image quality.

#### **III. PROPOSED UNEQUAL ERROR PROTECTION FOR JPEG2000**

In this section, we first study the use of ECC in combating errors in memories in JPEG2000 codecs. We study the use of 3 different SECDED codes: (137, 128), (72, 64), and (39, 32). Of these three codes, (39, 32) is the strongest with memory area increase of 21.9% followed by (72, 64) with an area increase of 12.5%, and (139, 128) with an area increase of 7%. The memory overhead of an (n, k) ECC code is defined as  $\frac{n-k}{k}$  where k represents the number of information bits for an ECC codeword length of n.

Since the memory area overhead of the stronger codes is very large, we propose to use unequal error protection (UEP) in the tile memory. By using a combination of strong and weak codes, the area overhead can be reduced without sacrificing performance. Note that UEP has been investigated earlier in the context of wireless transmission of images [64] [65]. The main idea of UEP is to provide superior protection for the more important bits. For instance, in JPEG2000 the higher subband DWT outputs are more important and so should be protected better with stronger codes.

In order to quantitatively measure the importance of a bit, we introduce  $\Delta DE$ which is quality degradation due to bit failures in memory. This is the same for all images and is solely a function of the subband level and location of the error bit position in the subband coefficient. Errors in high level subband coefficients cause a larger degradation in image quality, as expected. In a particular subband, an error in the  $k^{th}$  bit position of a coefficient affects the value by  $2^k$  and the  $\Delta DE$  due to an error in the  $k^{th}$  bit position is 2 times as large as that due to an error in  $(k - 1)^{th}$  bit position.

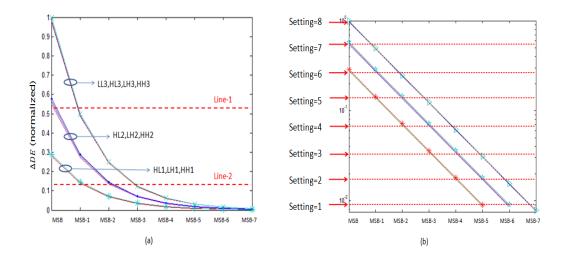

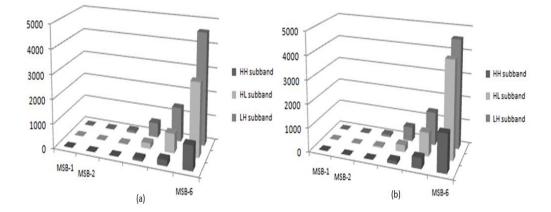

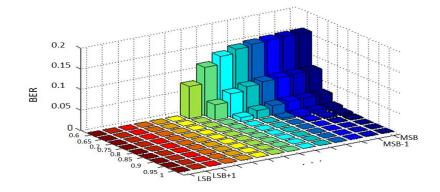

Fig. 3.5 plots the normalized  $\Delta DE$  for different subband outputs of a 3-level DWT as a function of a 1 bit error in different bit positions. The values are normalized with respect to maximum  $\Delta DE$  of the LL3 subband. Bits whose failures result in higher  $\Delta DE$  are clearly more important in terms of image quality. Thus, level-3 subband outputs are the most sensitive to bit errors and should be protected with stronger codes. Furthermore, as seen from the figure, errors in MSB-2 bit of level 3 outputs (LL3, HL3, LH3 and HH3) generate approximately same degradation in image quality as errors in MSB-1 bit of level 2 outputs (HL2, LH2 and HH2) and errors in MSB bit of level 1 outputs (HL1, LH1 and HH1). We use the same strength code for the bits that generate similar  $\Delta DE$ .

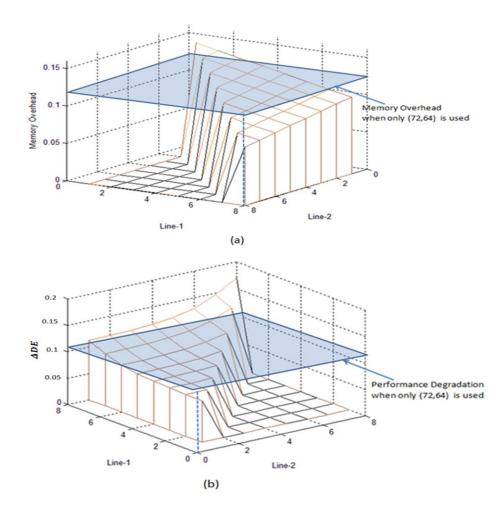

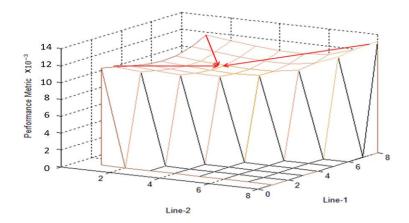

In a system that uses 3 codes, we break Fig. 3.5-a into 3 regions bounded by line-1 and line-2. We use the strongest code, which is (39, 32), for the points above line-1, (72, 64) code for the points between line-1 and line-2 and the weakest code (137, 128) for the rest of the points. Fig. 3.5-b illustrates the same figure in logarithmic scale with