Compilation of Stream Programs onto Embedded Multicore Architectures

by

Weijia Che

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved July 2012 by the Graduate Supervisory Committee:

Karamvir Chatha, Chair Sarma Vrudhula Chaitali Chakrabarti Aviral Shrivastava

ARIZONA STATE UNIVERSITY

August 2012

#### ABSTRACT

In recent years, we have observed the prevalence of stream applications in many embedded domains. Stream programs distinguish themselves from traditional sequential programming languages through well defined independent actors, explicit data communication, and stable code/data access patterns. In order to achieve high performance and low power, scratch pad memory (SPM) has been introduced in today's embedded multicore processors. Current design frameworks for developing stream applications on SPM enhanced embedded architectures typically do not include a compiler that can perform automatic partitioning, mapping and scheduling under limited on-chip SPM capacities and memory access delays. Consequently, many designs are implemented manually, which leads to lengthy tasks and inferior designs. In this work, optimization techniques that automatically compile stream programs onto embedded multi-core architectures are proposed. As an initial case study, we implemented an automatic target recognition (ATR) algorithm on the IBM Cell Broadband Engine (BE) [17]. Then integer linear programming (ILP) [19] and heuristic [18] approaches were proposed to schedule stream programs on a single core embedded processor that has an SPM with code overlay. Later, ILP and heuristic approaches for Compiling Stream programs on SPM enhanced Multicore Processors (CSMP) [20] were studied. The proposed CSMP ILP and heuristic approaches do not optimize for cycles in stream applications. Further, the number of software pipeline stages in the implementation is dependent on actor to processing engine (PE) mapping and is uncontrollable. We next presented a Retiming technique for Throughput optimization on Embedded Multi-core processors (RTEM) [14]. RTEM approach inherently handles cycles and can accept an upper bound on the number of software pipeline stages to be generated. We further enhanced RTEM by incorporating unrolling (URSTEM) [16] that preserves all the beneficial properties of RTEM heuristic and also scales with the number of PEs through unrolling.

#### ACKNOWLEDGEMENTS

First I would like to give my special thanks to my graduate advisor Dr. Karam Chatha for directing me throughout my Ph.D study. It is his guidance that brought me into the exciting and challenging world of embedded systems. The vision he shared with me has always been the beacon that leads me through darkness and confusion. His kind help contributes to almost all the research that I have done and all the papers that I have published. I can never forget the efforts that Dr. Chatha devoted to push my first paper through. It is his selfless dedication that motivates and encourages me to conquer whatever challenges come in front of me. All the days and nights we worked together are going to be precious memories that I will cherish forever. I am honored to have the opportunity to work with Dr. Chatha during the five years of my Ph.D study. His wisdom will continue to guide me and help me success in my career after graduation.

I also would like to thank my committee members for agreeing to join my committee. I sincerely appreciate their time and professional guidance. Without their kind support I will not be able to achieve what I have achieved today. I would like to thank Dr. Vrudhula for his dedication to Embedded Systems Consortium that benefits all the members including me. I would like to thank Dr. Shrivastava for his active enthusiasm and contributions for the collaborations of the compiler micro-architecture lab and the computing systems research lab. I would like to thank Dr. Chakrabarti for her professional knowledge and guidance. I consider myself very lucky to have such a kind and helpful committee for my Ph.D study.

All the lab members who have spent time with me, discussed research problems with me, conducted projects with me, and wrote papers with me, I would like to take this opportunity to thank them too. It is their support and accompaniment that took me through the toughest times. I would like to thank Sushu Zhang for introducing me to the computing systems research lab and getting me started when I was a fresh Ph.D student. She is a great mentor and provided me endless of support during my entire Ph.D study. I would like to thank Micheal Baker for all the exciting discussions we had and the projects we worked together. I would like to thank Glenn Leary for always being a great help whenever a challenge is encountered. I also like to thank Amrit Panda for his professional knowledge in architectures that has enlightened me in so many different ways, HaeSeung Lee for the paper we worked together, and Jyothi Swaroop for the support and discussions we shared. There are many other group members who have been of great help. Pravin Dalale, Nikhil Ghadge, Derek Woodman, and many others. They all helped me in one way or another and I would like to thank them for their time and support.

I am luckily to have both technical and financial supports from outside of Arizona State University and I would like to show my appreciation here. In particular, the collaboration with Raytheon company provided me with the experience of programming on the IBM Cell Broadband Engine and led me to success of the compiler work that follows. The Semiconductor Research Corporation has been a great help in both leading me technically and supporting my study financially. The task of system-level design of streaming applications on domain specific multi-sore processors has gradually evolved as part of my dissertation. The internship that was offered by The MathWorks provided me the first opportunity to step into industry and trained me from an entirely different perspective from academia. The collaborations with the industry partners not only helped me successful in my academic study but also lays the foundation for a bright future for me after my graduation.

Last but not least, I would like to thank the people who have known me for the longest time and have been there for me throughout my life, my parents and my brother. I cannot put it into words to show my appreciation and love. Except that they are always in my heart even when I am thousands of miles away from home.

## TABLE OF CONTENTS

|    |      |           |                                      | Page   |

|----|------|-----------|--------------------------------------|--------|

| LI | ST O | F TABLES  | 5                                    | . xvi  |

| LI | ST O | F FIGURI  | $\mathbf{S}$                         | . xvii |

| 1  | INT  | RODUCTI   | ON                                   | . 1    |

|    | 1.1  | StreamIt  | Language                             | . 3    |

|    | 1.2  | IBM Cell  | BE                                   | . 6    |

|    | 1.3  | Contribut | ions                                 | . 8    |

| CF | ІАРТ | ER        |                                      |        |

| 2  | DES  | IGN OF .  | AN ATR ALGORITHM ON IBM CELL BROAD-  |        |

|    | BAN  | ND ENGIN  | Έ                                    | . 11   |

|    | 2.1  | Automati  | c Target Recognition                 | . 12   |

|    | 2.2  | Previous  | Work                                 | . 13   |

|    | 2.3  | Reference | Implementation on Pentium4 PC        | . 15   |

|    | 2.4  | Design of | ATR on the IBM Cell BE               | . 16   |

|    |      | 2.4.1 Pc  | orting ATR to PPE                    | . 17   |

|    |      | 2.4.2 Pa  | arallelized implementation of ATR    | . 18   |

|    |      | 2.4.3 Al  | oplication parallelization on 6 SPEs | . 18   |

|    |      | 2.4.4 Do  | ouble buffering                      | . 19   |

|    |      | 2.4.5 2-1 | D FFT                                | . 20   |

|    |      | 2.4.6 M   | atrix transpose                      | . 20   |

|   |     | 2.4.7  | Small function relocation                | 21 |

|---|-----|--------|------------------------------------------|----|

|   |     | 2.4.8  | SIMD & loop unrolling                    | 22 |

|   |     | 2.4.9  | Pretouch memory                          | 22 |

|   |     | 2.4.10 | Mailbox communication                    | 23 |

|   | 2.5 | Experi | imental Results                          | 24 |

|   | 2.6 | Summ   | ary                                      | 25 |

| 3 | SCH | IEDULI | ING OF STREAM PROGRAMS ON ONE EMBEDDED   |    |

|   | COI | RE WIT | TH CODE OVERLAY                          | 33 |

|   | 3.1 | Prelim | inaries                                  | 34 |

|   |     | 3.1.1  | Code overlay                             | 35 |

|   |     | 3.1.2  | Basic pre-fetching and deep pre-fetching | 36 |

|   |     | 3.1.3  | Data overlay                             | 39 |

|   | 3.2 | Design | n Trade-offs                             | 40 |

|   |     | 3.2.1  | PASS generation                          | 40 |

|   |     | 3.2.2  | Actor to region assignments              | 43 |

|   |     | 3.2.3  | Segmentation                             | 44 |

|   |     | 3.2.4  | Data overlay                             | 45 |

|   | 3.3 | Proble | em Formulation                           | 46 |

|   | 3.4 | Relate | d Work                                   | 47 |

| 3.5 | 3-stag | e ILP Wi | thout Pre-fetching                          | 49 |

|-----|--------|----------|---------------------------------------------|----|

|     | 3.5.1  | Stage 1  | ILP: Scheduling                             | 50 |

|     |        | 3.5.1.1  | Decision variables                          | 50 |

|     |        | 3.5.1.2  | Derived variables                           | 50 |

|     |        | 3.5.1.3  | Constraints                                 | 51 |

|     |        | 3.5.1.4  | Objective function                          | 53 |

|     | 3.5.2  | Stage 2  | ILP: Region Assignment                      | 54 |

|     |        | 3.5.2.1  | Variables derived from Stage 1              | 54 |

|     |        | 3.5.2.2  | Decision variables                          | 54 |

|     |        | 3.5.2.3  | Derived variables                           | 54 |

|     |        | 3.5.2.4  | Constraints                                 | 55 |

|     |        | 3.5.2.5  | Objective function                          | 56 |

|     | 3.5.3  | Stage 3  | ILP: Segmentation                           | 56 |

|     |        | 3.5.3.1  | Results derived from Stage 1 and Stage 2 $$ | 56 |

|     |        | 3.5.3.2  | Decision variables                          | 56 |

|     |        | 3.5.3.3  | Derived variables                           | 57 |

|     |        | 3.5.3.4  | Constraints                                 | 59 |

|     |        | 3.5.3.5  | Objective function                          | 59 |

| 3.6 | 3-stag | e ILP Wi | th Pre-fetching                             | 60 |

|     | 3.6.1 | Stage 1   | ILP: Scheduling                             | 60 |

|-----|-------|-----------|---------------------------------------------|----|

|     |       | 3.6.1.1   | Additional derived variables                | 60 |

|     |       | 3.6.1.2   | Modified constraints                        | 61 |

|     |       | 3.6.1.3   | Updated objective function                  | 61 |

|     | 3.6.2 | Stage 2   | ILP: Region Assignment                      | 61 |

|     |       | 3.6.2.1   | Additional variables derived from Stage $1$ | 62 |

|     |       | 3.6.2.2   | Additional derived variables                | 62 |

|     |       | 3.6.2.3   | Updated constraints                         | 62 |

|     |       | 3.6.2.4   | Updated objective function                  | 63 |

|     | 3.6.3 | Stage 3   | ILP: Segmentation                           | 63 |

|     |       | 3.6.3.1   | Additional derived variables                | 63 |

|     |       | 3.6.3.2   | Updated derived variables                   | 63 |

|     |       | 3.6.3.3   | Updated constraint                          | 64 |

| 3.7 | SDF S | cheduling | g Heuristic                                 | 64 |

|     | 3.7.1 | Code ov   | erlay overhead calculation                  | 64 |

|     | 3.7.2 | Overall o | description                                 | 66 |

|     | 3.7.3 | Region a  | assignments                                 | 68 |

|     | 3.7.4 | Segment   | ation                                       | 69 |

|     | 3.7.5 | Overall a | algorithm complexity                        | 70 |

| Page |

|------|

|------|

|   | 3.8  | Exten  | sions to SDF Scheduling Heuristic                    | 71 |

|---|------|--------|------------------------------------------------------|----|

|   |      | 3.8.1  | Basic pre-fetching optimization                      | 71 |

|   |      | 3.8.2  | Deep pre-fetching optimization                       | 73 |

|   |      | 3.8.3  | Data overlay optimization                            | 75 |

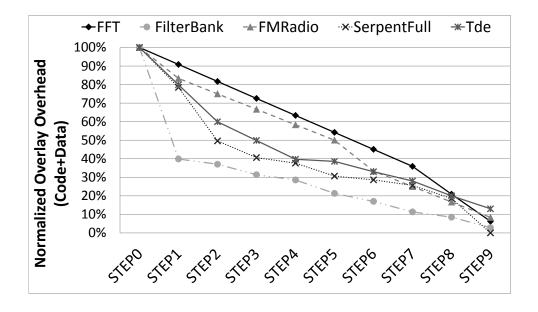

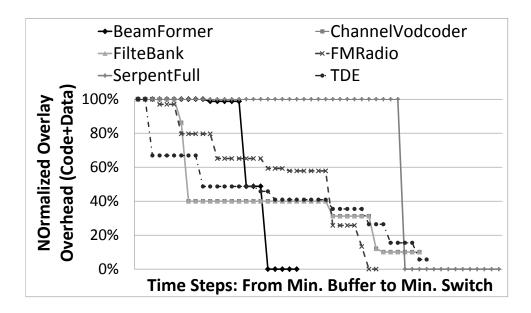

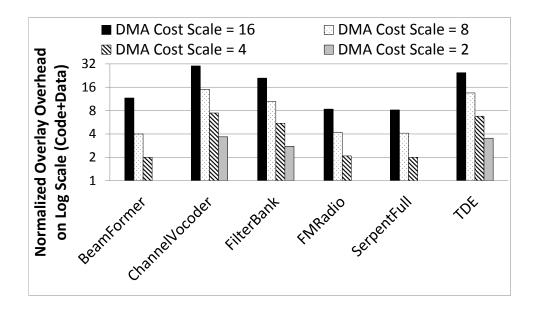

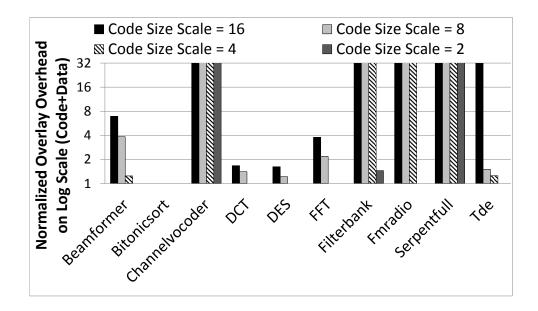

|   | 3.9  | Exper  | imental Results                                      | 81 |

|   |      | 3.9.1  | Experimental setup                                   | 81 |

|   |      | 3.9.2  | Comparison of 3-stage ILP and heuristic with minimum |    |

|   |      |        | buffer scheduling                                    | 82 |

|   |      | 3.9.3  | Impact of each optimization                          | 84 |

|   |      | 3.9.4  | Impact of SPM size                                   | 87 |

|   |      | 3.9.5  | Code overlay evolution                               | 88 |

|   |      | 3.9.6  | Impact of scaling DMA cost                           | 89 |

|   |      | 3.9.7  | Impact of scaling code size and run time $\ldots$    | 91 |

|   | 3.10 | Summ   | nary                                                 | 92 |

| 4 | SCH  | EDUL   | ING OF STREAM PROGRAMS ON SPM BASED MUL-             |    |

|   | TIC  | ORE P  | ROCESSORS THROUGH FUSION AND FISSION                 | 94 |

|   | 4.1  | Motiv  | $\operatorname{ation}$                               | 94 |

|   | 4.2  | Previo | ous Work                                             | 96 |

|   |      | 4.2.1  | Problem description                                  | 97 |

| 4.3 | Intege | er Linear Programming Approach                                                                           | 0 |

|-----|--------|----------------------------------------------------------------------------------------------------------|---|

|     | 4.3.1  | Constraints                                                                                              | 0 |

|     | 4.3.2  | Objective function                                                                                       | 4 |

|     |        | 4.3.2.1 Computation cost $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 10$             | 4 |

|     |        | 4.3.2.2 Communication cost $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 10$           | 5 |

|     |        | 4.3.2.3 Execution cost $\ldots \ldots 10$ | 5 |

|     |        | 4.3.2.4 Effective execution cost                                                                         | 5 |

|     |        | 4.3.2.5 Overall cost function $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 10$        | 5 |

| 4.4 | Heuris | stic Approach                                                                                            | 6 |

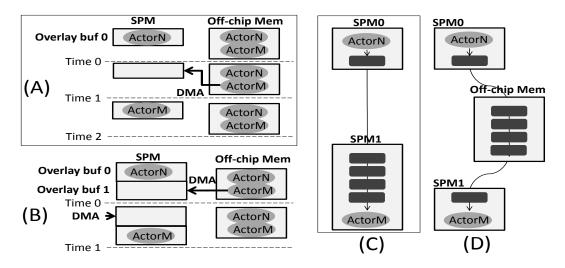

|     | 4.4.1  | Overlay Scheme                                                                                           | 8 |

|     | 4.4.2  | Cost functions                                                                                           | 8 |

|     |        | 4.4.2.1 Buffer usage                                                                                     | 9 |

|     |        | $4.4.2.2  \text{Computation cost}  \dots  \dots  \dots  \dots  \dots  10$                                | 9 |

|     |        | 4.4.2.3 Communication cost                                                                               | 9 |

|     |        | 4.4.2.4 Overall cost of solution                                                                         | 0 |

| 4.5 | Exper  | rimental Results                                                                                         | 1 |

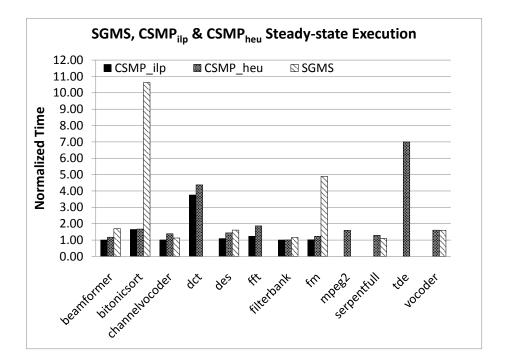

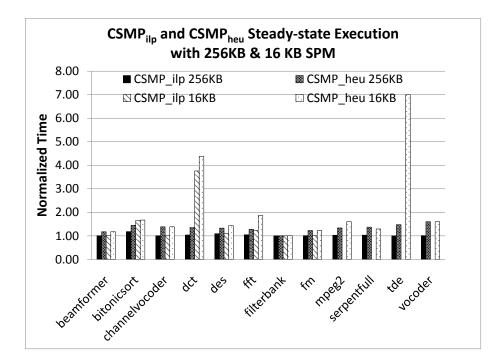

|     | 4.5.1  | Comparisons with 256KB SPE memory                                                                        | 2 |

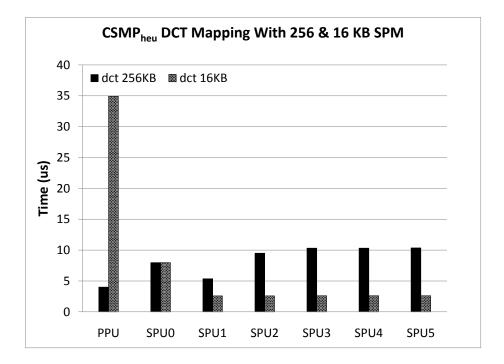

|     | 4.5.2  | Comparisons with 16KB SPE memory 11                                                                      | 5 |

| 4.6 | Summ   | nary                                                                                                     | 7 |

| 5 | SCH | IEDULI | ING OF STREAM PROGRAMS ON SPM BASED MUL- |     |

|---|-----|--------|------------------------------------------|-----|

|   | TIC | ORE P  | ROCESSORS THROUGH RETIMING               | 119 |

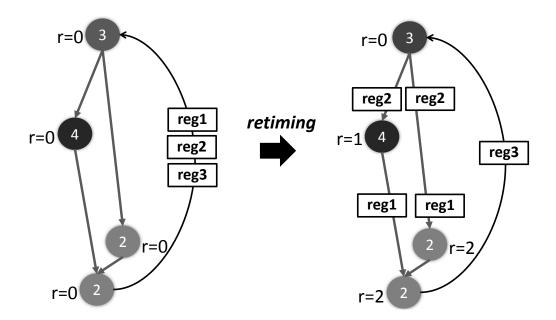

|   | 5.1 | Retim  | ing                                      | 120 |

|   | 5.2 | Motiva | $\operatorname{ation}$                   | 121 |

|   | 5.3 | Proble | em Description                           | 124 |

|   | 5.4 | Relate | ed Work                                  | 125 |

|   | 5.5 | Resolv | ring Cycles                              | 127 |

|   | 5.6 | Pre-pr | rocessing                                | 131 |

|   | 5.7 | Intege | r Linear Programming Approach            | 132 |

|   |     | 5.7.1  | Decision variables                       | 134 |

|   |     | 5.7.2  | Derived variables                        | 134 |

|   |     | 5.7.3  | Constraints                              | 136 |

|   |     | 5.7.4  | Cost functions                           | 139 |

|   |     | 5.7.5  | Objective function                       | 140 |

|   | 5.8 | RTEM   | 1 Heuristic Approach                     | 140 |

|   |     | 5.8.1  | AlgorithmII                              | 141 |

|   |     |        | 5.8.1.1 Calculation of $\tau_c(v)$       | 142 |

|   |     |        | 5.8.1.2 Calculation of $\tau_o(v)$       | 143 |

|   |     | 5.8.2  | AlgorithmFEAS                            | 144 |

|   |      | 5.8.3  | AlgorithmRTEM                                           | 145  |

|---|------|--------|---------------------------------------------------------|------|

|   |      | 0.0.0  |                                                         | 110  |

|   |      |        | 5.8.3.1 Implementation of smart double buffering scheme | e146 |

|   |      | 5.8.4  | Complexity                                              | 148  |

|   | 5.9  | Exper  | imental Results                                         | 148  |

|   |      | 5.9.1  | Experimental setup                                      | 148  |

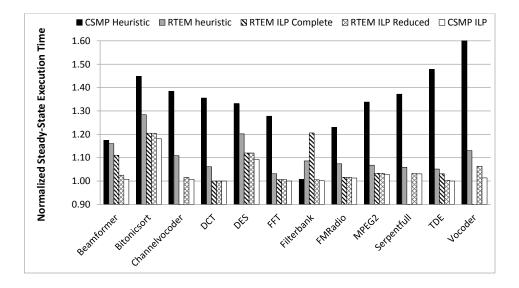

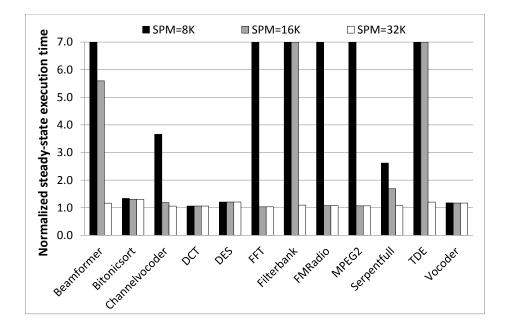

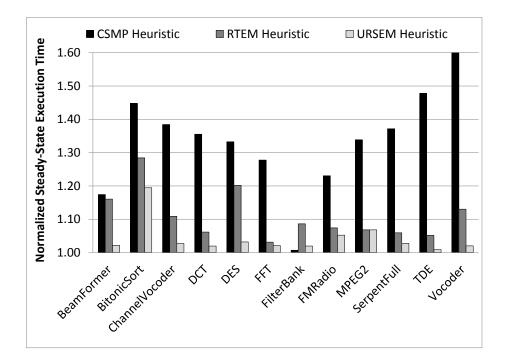

|   |      | 5.9.2  | Overall performance comparison                          | 148  |

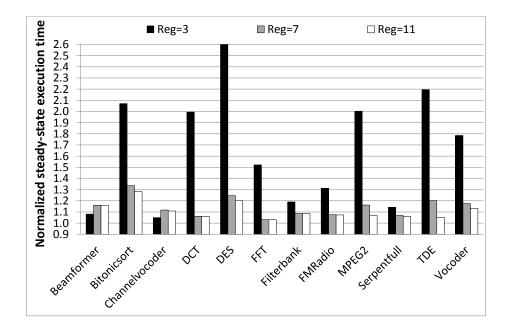

|   |      | 5.9.3  | Comparison with different SPM sizes                     | 151  |

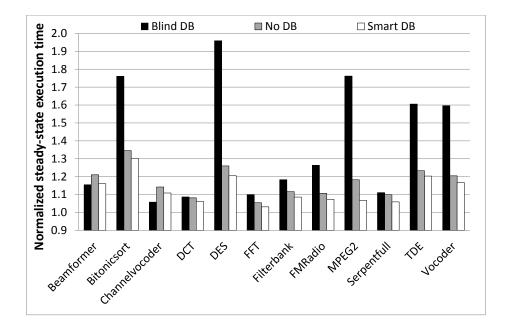

|   |      | 5.9.4  | Comparison with different double buffering schemes      | 153  |

|   |      | 5.9.5  | Comparison with different number of pipeline stages and |      |

|   |      |        | PEs                                                     | 154  |

|   | 5.10 | Summ   | ary                                                     | 156  |

| 6 | UNF  | ROLLIN | NG AND RETIMING OF STREAM PROGRAMS ON                   |      |

|   | SPM  | I BASE | D MULTICORE PROCESSORS                                  | 158  |

|   | 6.1  | Proble | em Description                                          | 161  |

|   | 6.2  | Relate | d Work                                                  | 163  |

|   | 6.3  | URSE   | M Heuristic Approach                                    | 165  |

|   |      | 6.3.1  | Pre-processing                                          | 165  |

|   |      | 6.3.2  | URSEM heuristic algorithm                               | 165  |

|   |      |        |                                                         |      |

Page

|    |      | 6.3.4  | Algorith  | mDeltaCD                                          | 168 |

|----|------|--------|-----------|---------------------------------------------------|-----|

|    |      |        | 6.3.4.1   | Construction of RG to PE mapping                  | 169 |

|    |      |        | 6.3.4.2   | Calculation of code, data memory usage $\ldots$ . | 170 |

|    |      |        | 6.3.4.3   | Calculation of processor workload                 | 171 |

|    |      |        | 6.3.4.4   | Calculation of $\tau_c(v)$                        | 171 |

|    |      |        | 6.3.4.5   | Calculation of $\tau_o(v)$                        | 173 |

|    |      | 6.3.5  | Algorith  | m Complexity                                      | 173 |

|    | 6.4  | Exper  | imental R | esults                                            | 174 |

|    |      |        | 6.4.0.1   | Overall performance comparison                    | 174 |

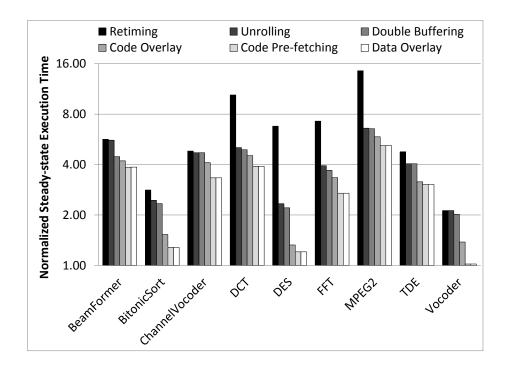

|    |      |        | 6.4.0.2   | Impact of optimizations                           | 175 |

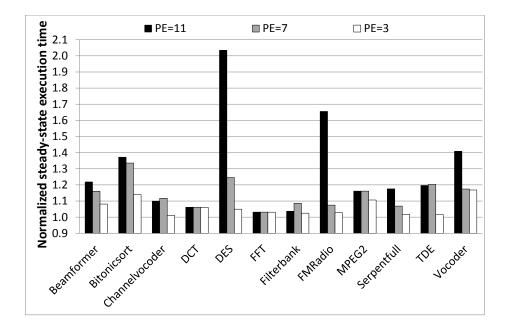

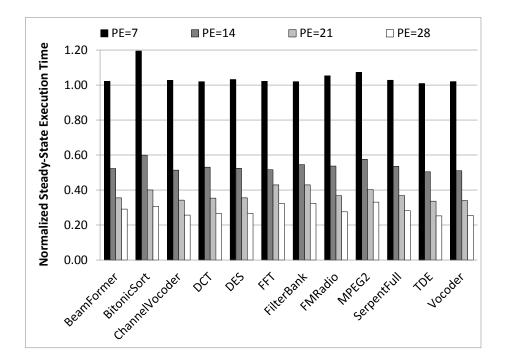

|    |      |        | 6.4.0.3   | Performance scaling with PEs                      | 176 |

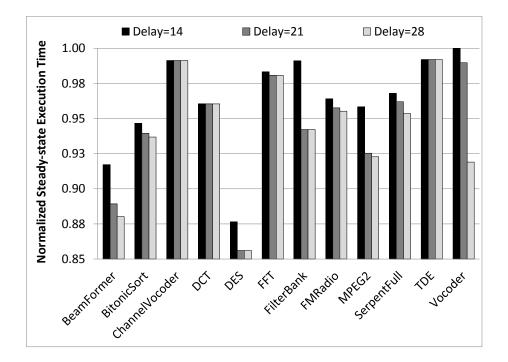

|    |      | 6.4.1  | Perform   | ance scaling with Delays                          | 178 |

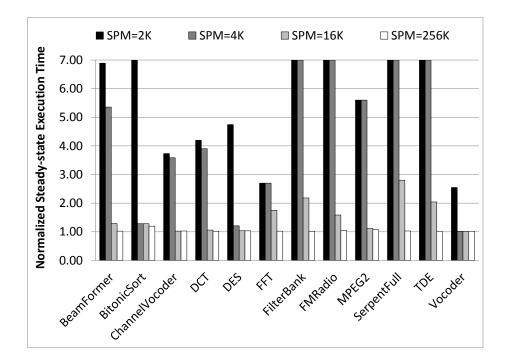

|    |      |        | 6.4.1.1   | Performance scaling with SPMs                     | 178 |

|    | 6.5  | Summ   | ary       |                                                   | 179 |

| 7  | COI  | NCLUS  | ION ANE   | FUTURE WORK                                       | 181 |

|    | 7.1  | Future | e Work on | 0 OpenCL                                          | 183 |

|    | 7.2  | Future | e Work on | TI Multicore                                      | 184 |

| RI | EFER | ENCES  | S         |                                                   | 186 |

# CHAPTER

# Page

| APPENDIX   | <br>• | • | • | • | • | • | • | • | • | • | • | • | <br>• | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 196 |

|------------|-------|---|---|---|---|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| APPENDIX A |       | • |   |   | • |   | • | • | • | • | • | • |       | • | • | • | • | • | • | • | • | • | • | • | • | • |   | 196 |

| APPENDIX B |       |   |   |   | • |   |   |   |   |   |   |   |       |   |   |   |   |   |   |   |   |   |   |   |   |   | • | 205 |

| Tab | le Page                                                                                |

|-----|----------------------------------------------------------------------------------------|

| 1.1 | Benchmark Specifications                                                               |

| 2.1 | Stages in the ATR allgorithm                                                           |

| 2.2 | Profile Analysis of ATR on host PC and PPE                                             |

| 2.3 | Profile Analysis of ATR on PPE and SPEs                                                |

| 2.4 | Computation/Communication Latency Comparison                                           |

| 2.5 | Problem State Area Mapped Mailbox Performance                                          |

| 3.1 | Design trade-offs with PASS generation. Buffer Usage and Avail-                        |

|     | able Code Memory in the table are represented in bytes 42                              |

| 3.2 | Design trade-offs with actor to region assignments. Available Code                     |

|     | Memory and Region Sizes in the table are represented in bytes. $.$ 44                  |

| 3.3 | Architecture and SDF Description                                                       |

| 3.4 | Benchmark Specifications 81                                                            |

| 4.1 | Architecture and SDF Description                                                       |

| 4.2 | Base and Derived Variables                                                             |

| 4.3 | Maximum SPE Buffer usage of SGMS, $\text{CSPM}_{ilp} \& \text{CSPM}_{heu}$ (BYTES).    |

|     | 112                                                                                    |

| 4.4 | Run time of SGMS, $CSPM_{ilp}$ & $CSPM_{heu}$ (SECONDS) 113                            |

| 4.5 | Maximum communication buffer usage of SGMS, $\text{CSMP}_{ilp} \& \text{CSMP}_{heu}$ . |

|     | 118                                                                                    |

| 5.1 | SDF and architecture specification                                                     |

| LIST | OF | FIGURES |

|------|----|---------|

|      |    |         |

| Figure   Pag |                                                                  | Page |

|--------------|------------------------------------------------------------------|------|

| 1.1          | StreamIt program example                                         | 4    |

| 1.2          | IBM Cell BE architecture overview.                               | 6    |

| 1.3          | DMA performance with 6 SPEs                                      | 7    |

| 2.1          | ATR algorithm overview.                                          | 13   |

| 2.2          | 2-Dimensional real FFT                                           | 26   |

| 2.3          | Data partition for the morphological filter                      | 27   |

| 2.4          | fft_1d_r2 profile on one SPE                                     | 28   |

| 2.5          | Unoptimized and Optimized FDF                                    | 29   |

| 2.6          | Data partition in matrix transpose module                        | 29   |

| 2.7          | Task schedule. The modules annotated with SPE execute in par-    |      |

|              | allel on 6 SPEs.                                                 | 30   |

| 2.8          | Frequency Domain Filtering.                                      | 30   |

| 2.9          | Latency comparison for integrating each optimization. $\ldots$ . | 31   |

| 2.10         | Computation Comparison for Each Process in ATR                   | 32   |

| 3.1          | Segment-region code overlay overview.                            | 35   |

| 3.2          | Code pre-fetching and deep pre-fetching.                         | 37   |

| 3.3          | DMA engine status with basic pre-fetching                        | 37   |

| 3.4          | DMA engine status with deep pre-fetching                         | 39   |

| 3.5          | Data overlay overview.                                           | 40   |

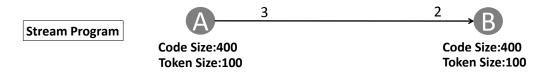

| 3.6          | Stream program with one producer and one consumer. The code,     |      |

|              | token sizes are in bytes                                         | 41   |

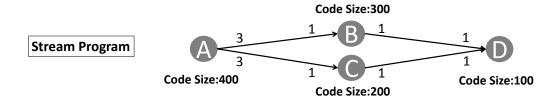

| 3.7          | Stream program with four actors. The code sizes are in bytes     | 43   |

| 3.8          | Design trade-offs with data overlay.                             | 46   |

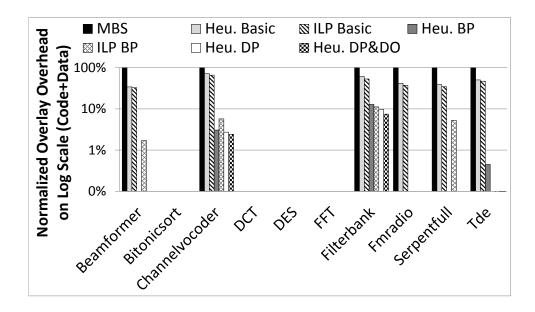

| 3.9  | Our 3-stage ILP and heuristic approaches compared with minimum                             |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | buffer scheduling.                                                                         | 83  |

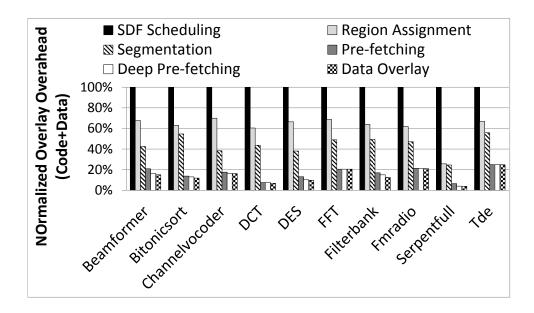

| 3.10 | Impact of each optimization in our heuristic approach                                      | 84  |

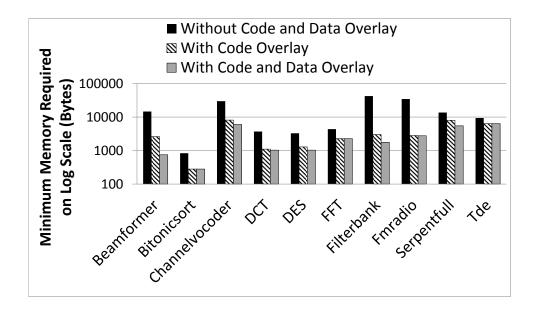

| 3.11 | Memory usage comparison.                                                                   | 85  |

| 3.12 | SPM size variation $(1^{st} \text{ set})$                                                  | 88  |

| 3.13 | SPM size variation $(2^{nd} \text{ set})$                                                  | 89  |

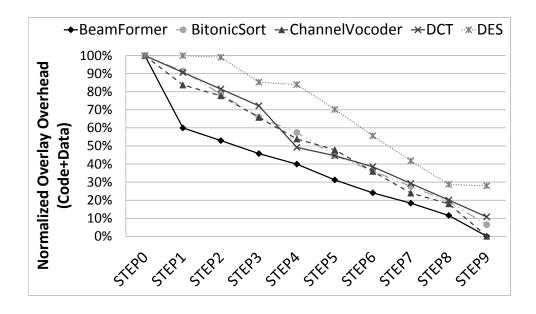

| 3.14 | Overlay cost evolution with SDF scheduling.                                                | 90  |

| 3.15 | Impacts of scaling DMA overhead.                                                           | 91  |

| 3.16 | Impacts of scaling code size and run time                                                  | 92  |

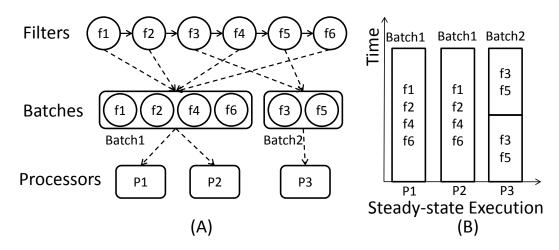

| 4.1  | (A) filter-batch, and batch-processor mapping; (B) steady-state $\ .$                      | 101 |

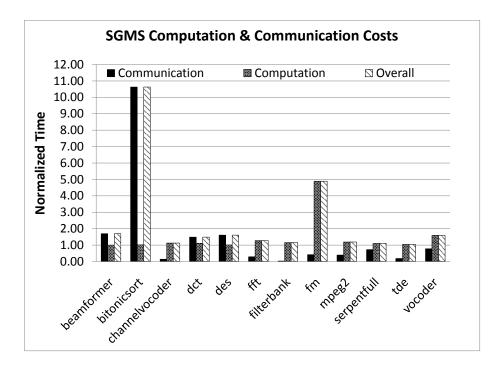

| 4.2  | Computation and communication costs for SGMS $\ . \ . \ . \ .$ .                           | 110 |

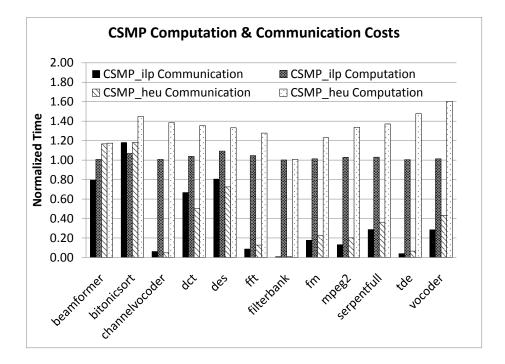

| 4.3  | Computation and communication costs for $\mathrm{CSMP}_{ilp}$ and $\mathrm{CSMP}_{heu}$    | 111 |

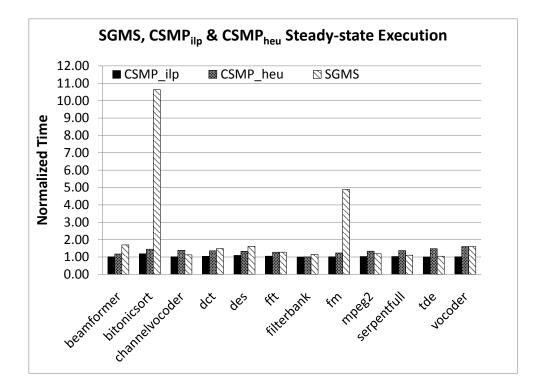

| 4.4  | SGMS, $\text{CSMP}_{ilp}$ and $\text{CSMP}_{heu}$ with 256KB SPM                           | 114 |

| 4.5  | SGMS, $\text{CSMP}_{ilp}$ and $\text{CSMP}_{heu}$ with 16KB SPM                            | 115 |

| 4.6  | <code>Performance of CSMP_{ilp}</code> and <code>CSMP_{heu}</code> with 256KB and 16KB SPM | 116 |

| 4.7  | DCT with 256KB and 16KB SPM                                                                | 117 |

| 5.1  | Retiming example.                                                                          | 120 |

| 5.2  | Single appearance SDF construction from a multiple appearance                              |     |

|      | stream program without cycles.                                                             | 128 |

| 5.3  | Single appearance SDF construction from a multiple appearance                              |     |

|      | stream program with a tight cycle dependence. $\ldots$ $\ldots$ $\ldots$ $\ldots$          | 130 |

| 5.4  | Single appearance SDF construction from a multiple appearance                              |     |

|      | stream program with a loose cycle dependence.                                              | 131 |

| 5.5  | A simple example of retiming a stream program with 3 PEs and 4    |     |

|------|-------------------------------------------------------------------|-----|

|      | software pipeline stages                                          | 134 |

| 5.6  | RTEM ILP and heuristic against CSMP ILP and heuristic ap-         |     |

|      | proaches.                                                         | 149 |

| 5.7  | Performance comparison with different size of SPMs. $\ldots$      | 152 |

| 5.8  | Smart double buffering against blind double buffering and no dou- |     |

|      | ble buffering.                                                    | 153 |

| 5.9  | Performance comparison with different pipeline stages. $\ldots$ . | 155 |

| 5.10 | Performance comparison with different number of PEs               | 156 |

| 6.1  | Code overlay and data overlay                                     | 161 |

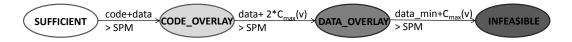

| 6.2  | Processor memory state transitions.                               | 173 |

| 6.3  | Overall performance comparison                                    | 175 |

| 6.4  | Impact of optimizations.                                          | 176 |

| 6.5  | Performance scaling with PEs                                      | 177 |

| 6.6  | Performance scaling with Delays                                   | 179 |

| 6.7  | Performance scaling with SPMs.                                    | 180 |

#### Chapter 1

## INTRODUCTION

Recent years have witnessed the recognition of stream computing as an important model of computation in many embedded system domains, such as signal processing, multimedia, and network processing. Stream applications share common characteristics such as well defined independent actors, explicit exposed data communication, and stable code/data access patterns. Due to these characteristics, several languages have been developed in the past few years to model stream applications (formally referenced as stream languages). Example stream languages include StreamIt [71], CAL [29], CUDA [60], Brook [13]. Many of these languages model the compute intensive units of a program as actors and expose the data communication among distinct actors as FIFOs. Many stream languages in fact implement the synchronous data flow (SDF) model of computation.

Processor designers have responded to the high performance requirements of stream applications by developing domain specific multi-core processors. Examples of commercial processors that are aimed at streaming applications include IBM Cell Broadband Engine (BE) [22] [64], Tilera64 [72], Intel Larrabee [68], Nvidia GeForce series [43], Ageia's PhysX [76], TI TMS320C6472 [73] and many DSPs. In many of these embedded architectures, SPM has replaced traditional caches for faster access time, smaller chip area, and lower power/energy consumption. In an SPM enhanced design, the workload of dynamic management of the limited on-chip SPM is shifted from the hardware side to a programmer or compiler. Data and code transfers among various memory elements are realized through direct memory access (DMA) engines and are completely software managed.

Current design frameworks for developing stream applications on SPM enhanced embedded architectures typically do not include a compiler that can automatically address the limited on-chip SPM and memory access delays and efficiently perform partitioning, mapping and scheduling under various design trade-offs. Consequently, many designs are implemented manually. In a manual design, the programmer has to manage the code and data transfers among various memory elements during the entire program life time. Due to the limited on-chip SPM capacity, code overlay and data overlay schemes have to be implemented for sharing the same physical memory with different code/data segments. To amortize memory access delays, double buffering (DB) for overlapping data communication with computation has to be evaluated. The introduction of double buffering scheme requires storing an extra copy of data, which could result in additional code and data overlay overhead. Given the challenges and various design trade-offs discussed above, manual development of stream programs on SPM enhanced architectures often leads to lengthy design time and inferior quality designs.

In this dissertation, we propose optimization techniques that automatically compile stream programs onto embedded multicore architectures. As an initial case study, we implement an automatic target recognition (ATR) algorithm on the IBM Cell BE [17]. Then integer linear programming (ILP) and heuristic approaches are proposed to schedule stream programs on a single core embedded processor that has an SPM with code overlay [19] [18]. Later, ILP and heuristic approaches for Compiling Stream programs on SPM equipped Multicore Processors are studied (named as CSMP ILP and CSMP heuristic respectively) [20]. The CSMP ILP and heuristic approaches cannot optimize feedback cycles in stream programs and also could result in very deep software pipeline stages. We next present a Retiming algorithm for Throughput optimization on Embedded Multicore processors (named as RTEM) [14]. RTEM heuristic inherently optimizes feedback cycles and allows a user to specify the number of software pipeline stages to be generated. RTEM heuristic relies on the existing parallelism in an application therefore may not scale with the number of PEs of an embedded multicore processor. Finally, we provide Unrolling and Retiming of Stream programs on Embedded Multicore processors (URSEM) that preserves all the beneficial properties of RTEM and also scales with the number of PEs.

Since StreamIt language and IBM Cell BE are used throughout our experiments as the software and hardware specifications, we begin with a discussion that introduces both of them.

#### 1.1 StreamIt Language

We adopted StreamIt language from MIT [71] as the input specification to our experiments. StreamIt programs implement the synchronous data flow (SDF) model of computation [49]. Four basic structures, namely filter, pipeline, splitjoin, and feedback-loop are provided by StreamIt to construct a stream program. The actors/filters<sup>1</sup> in an SDF represent small compute intensive units in a stream application. The edges in an SDF stand for data communica-

<sup>&</sup>lt;sup>1</sup>Filter is the formal name for an actor in a StreamIt program. We use actor and filter interchangeably in this chapter.

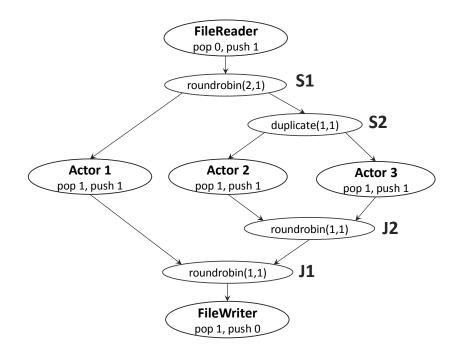

Figure 1.1: StreamIt program example.

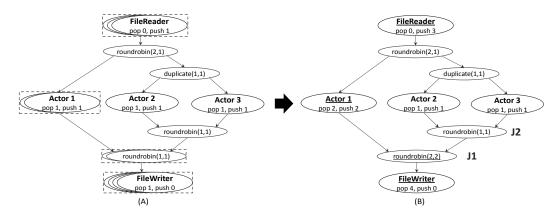

tion/FIFOs among actors. At each iteration, an actor consumes a constant amount of data from its incoming edges and produces a constant amount of data to its outgoing edges. We require the SDF to be consistent [49] in our technique. In fact, all legal StreamIt programs are consistent by default. In other words, there exists a steady-state execution state for a valid stream program. In Figure 1.1 we provide an example of a simple stream program. In the figure, FileReader and FileWriter handle the I/O operations of the program. FileReader pushes one token (denoted by push 1) to its outgoing edge in each execution and thus serves as a token source. FileWriter consumes one token from its incoming edge in each execution and serves as a token sink. There are two split-join structures in the program, one consists of two roundrobin filters (S1 and J1) and the other is constructed with a pair of duplicate and roundrobin (S2 and J2). roundrobin and duplicate filters are built in data flow

| Benchmark Names | Number of Actors | Number of Edges |

|-----------------|------------------|-----------------|

| Beamformer      | 56               | 58              |

| Bitonicsort     | 40               | 46              |

| Channelvocoder  | 55               | 70              |

| DCT             | 40               | 69              |

| DES             | 53               | 60              |

| FFT             | 17               | 16              |

| Filterbank      | 85               | 99              |

| Fmradio         | 43               | 53              |

| MPEG2-Subset    | 23               | 26              |

| Serpentfull     | 120              | 128             |

| TDE             | 29               | 28              |

| Vocoder         | 116              | 150             |

| Average         | 56               | 67              |

Table 1.1: Benchmark Specifications

\*The size of Bitonicsort is 8 points. The size of DCT is 8 by 8, and the size of FFT is 256 single precision complex points.

filters in the StreamIt language. The weight array attached to each roundrobin or duplicate denotes the data tokens it pops (J1, J2) from its incoming edges or pushes (S1, S2) to its outgoing edges in each execution. The difference between a roundrobin filter and a duplicate filter is that a roundrobin only collects or splits data tokens according to its weight array while a duplicate first replicates each token according to its weight array and then splits them to its outgoing edges.

Twelve benchmarks that are delivered with StreamIt compiler version 2.1.1 will be used extensively to in our experiments. Table 1.1 details the characteristics of each benchmark. The first column provide us with the benchmark names. The second and third columns provides us with the number of actors and edges in each benchmark. The last row calculates the average for each column.

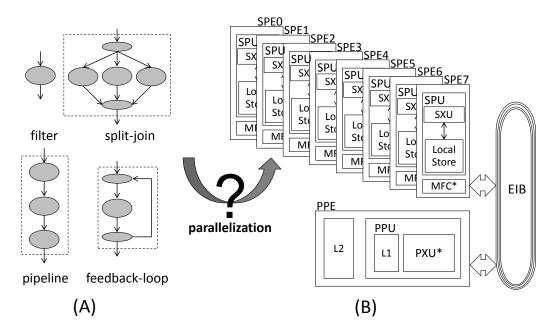

Figure 1.2: IBM Cell BE architecture overview.

### 1.2 IBM Cell BE

IBM Cell BE was used as the target architecture to evaluate the efficiency of our techniques. IBM Cell BE is a heterogeneous multicore processor collaboratively developed by IBM, Sony and Toshiba [64]. Figure 1.2 provides an architecture overview of this architecture. There are nine processing elements with one PowerPC Engine (PPE) and eight Synergistic Processing Engines (SPEs) [33]. PPE in the Cell BE is a 64-bit dual issue, dual threaded, inorder processor. It works as a control plane that launches tasks on SPEs. Eight SPEs run as high performance data processing planes. Each SPE has a 128×128 bit register file and supports single instruction multiple data (SIMD) operations. Each SPE also hosts an SPM of 256 KB that is formally referred as the SPE local store. A four-ring structured element interconnect bus (EIB) [44] connects the PPE, eight SPEs, and the memory controllers, providing a cumulative bandwidth of over 204.8 GBps. Direct memory access or DMA

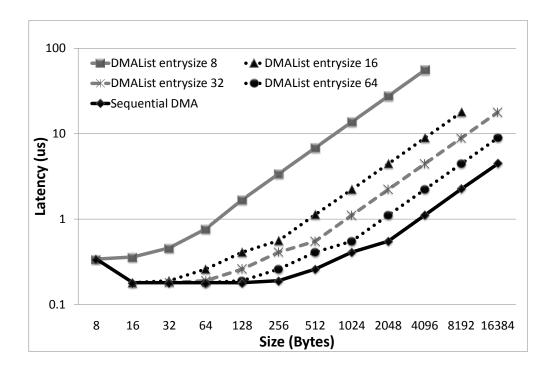

Figure 1.3: DMA performance with 6 SPEs.

(which can be launched by either the PPE or an SPE) is the primary mechanism for communicating between the local store of two SPEs or between an SPE local store and the off-chip PPE main memory<sup>2</sup>. The non-blocking nature of a DMA engine permits the amortization of communication overhead by concurrent computation. In the IBM Cell BE architecture, up to sixteen independent DMAs can be launched simultaneously by each initiating core.

As the software controlled memory management is one of the key features of Cell BE, we characterize the performance of the DMA engine in Figure

<sup>&</sup>lt;sup>2</sup>The CELL BE also supports signals and mail boxes for inter-SPE and PPE-SPE communication. However, these are primarily useful for synchronization for very small data items. As we are more concerned about large data items we focus on DMA.

1.3. The plot consists of two types of curves. The DMA list curves (4 in number) and the sequential DMA curve. DMA list as the name suggests denotes that a list of DMA requests was transferred with one command to the DMA engine. The DMA list curve of 8 bytes denotes that each DMA in the list was for 8 bytes. Similarly, the DMA list curve of 16, 32 and 64 denotes the size of each entry in the DMA list. The x-axis represents the total size of the DMA list request. The number of entries in a DMA list curve can be determined by dividing the x-axis index by the DMA list size of the curve. Finally, the sequential DMA curve denotes that a single DMA was initiated. Notice that both the x-axis and y-axis are on logarithmic scale with bases of 2 and 10, respectively.

### 1.3 Contributions

The contributions of this dissertation are summarized below:

• We design and implement an ATR algorithm [17] on the IBM Cell BE (Chapter 2). Eight optimizations that exploit both the specific algorithm constructs of the ATR algorithm and the architectural features of the Cell processor were implemented. The latency of the final Cell BE implementation is more than 25 times faster than the fully optimized PPE implementation and almost 20 times faster than our best efforts on a Pentium4 CPU. This initial manual design validates the computing power of the Cell BE. It also reveals the overheads and bottle-necks that are involved in developing stream applications for embedded architectures with SPMs.

- We propose ILP [19] and heuristic [18] approaches that schedule stream programs on a single core embedded processor that has an SPM with code overlay (Chapter 3). The three-stage ILP approach extensively explores the design alternatives with different schedules, code/data partitions, and actor to region/segment assignments. Experimental results demonstrate that our ILP approach is able to efficiently explore various design trade-offs and generate high quality solutions. Although the ILP approach generates high quality solutions, it could take a very long time to run due to the problem size. A fast heuristic algorithm that efficiently balances between a minimum buffer schedule and a minimum actor switching schedule, and solves the same problem with comparable results in a matter of seconds is also discussed.

- We present ILP and heuristic approaches for automatic compilation of stream programs onto embedded multicore processors that incorporate SPMs [20] (Chapter 4). In the ILP approach (CSMP ILP), fusion and fission operators are implemented by assigning actors to batches and then batches to PEs. The ILP formulation models both the code overlay and communication overheads under the constraint of limited on-chip SPM capacities and memory access delays. Experimental results show that CSMP ILP approach is able to effectively balance the computation and communication overheads when mapping stream programs onto multicore architectures. To overcome the long algorithm run time of CSMP ILP approach, we also provide a fast heuristic approach (CSMP heuristic) that solves the same problem with comparable results in a matter of seconds.

- CSMP ILP and heuristic approaches assume absence of feedback cycles in the program. The number of software pipelines stages being generated in the final schedule is uncontrollable. In Chapter 5, we propose a fast heuristic (RTEM) that schedules stream programs onto SPM based multicore processors through retiming [14]. Trade-offs between double buffering and code overlay are explored intensively in this approach. More importantly, the retiming approach inherently handles feedback cycles and it can accept a user specified upper bound on the number of software pipeline stages.

- When the number of PEs is very large and the existing parallelism in a stream program is comparably limited, RTEM heuristic fails to generate high quality solutions. In Chapter 6, we present unrolling and retiming of stream formats onto embedded multicore processors (URSEM) as our last optimization. URSEM preserves all the beneficial properties of RTEM heuristic and scales with the number of PEs. Apart from code overlays for addressing limited on-chip SPM capacities, code pre-fetching and data overlays are also introduced to address the increased code and data requirement caused due to unrolling.

#### Chapter 2

# DESIGN OF AN ATR ALGORITHM ON IBM CELL BROADBAND ENGINE

This chapter presents the design and optimization of an ATR algorithm on the IBM Cell BE. The ATR algorithm and the Cell BE are good representatives of stream applications and domain specific multicore processors. ATR belongs to the important class of signal processing algorithms that are widely utilized in Radar and electronic surveillance systems. The Cell BE is aimed at streaming applications that exhibit limited run time or dynamic variation during execution. Stream applications permit aggressive static or design time optimizations for maximizing their performance. The Cell BE designers recognized this fact and incorporated a 256KB local store or scratch pad for each SPE instead of caches. The local store is shared for both code and data, that are fetched under software control through DMAs. Thus the well know problems of functional partitioning, load balancing, communication versus computation trade-offs that are encountered during parallelization of an application must now be addressed in the context of a software controlled memory hierarchy. It is this additional complexity that makes designing applications on the Cell BE a daunting task. This chapter presents eight optimizations that are also applicable to other applications and processors that demonstrate similar characteristics. The contributions of the chapter include:

- Design of an ATR algorithm on the Cell BE.

- A detailed discussion of four basic categories of optimizations and their effects.

- An optimized scheme for Frequency Domain Filtering (FDF) with symmetric kernels.

- A generic design flow for porting streaming applications onto domain specific multicore architectures.

We begin with an introduction to the ATR algorithm in 2.1. We discuss previous work on optimizing applications on the Cell BE in Section 2.2. In Section 2.3 we discuss the design and optimization of a reference implementation of the ATR algorithm on an Intel Pentium4 based PC platform along with detailed profile analysis. The design flow of porting the ATR algorithm to the Cell BE along with various optimizations are presented in Section 2.4. We analyze the experimental results in Section 2.5 and summarizes in Section 2.6.

#### 2.1 Automatic Target Recognition

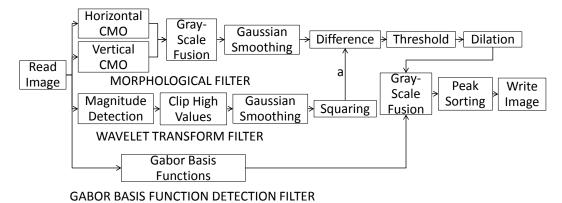

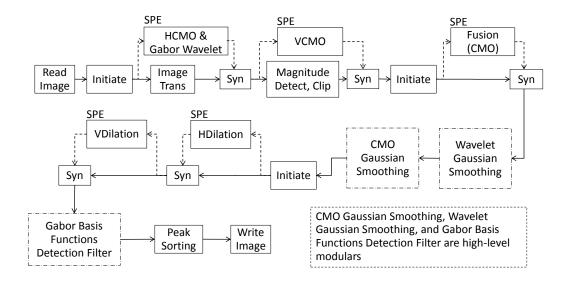

Automatic target recognition (ATR) algorithms belong to the class of high performance computation intensive image processing algorithms that are widely used in applications such as target detection, radar processing, and pattern recognition. In this chapter, we present an optimized implementation of the detection algorithm proposed by David Casasent and Anqi Ye [17]. Their ATR algorithm is a fusion of several detection algorithms. A high-level flow of the algorithm is given in Figure 2.1 and the short descriptions for each stage are provided in Table 2.1. In Figure 2.1, the morphological filter detects both the objects and the edges from an input image. The wavelet transform filter that can execute in parallel with the morphological filter extracts the edges. A weighted subtraction therefore gives us only the detected objects. The

Figure 2.1: ATR algorithm overview.

following threshold operator removes the background noises and the dilation operator recovers the shape of the objects. A third branch in the algorithm, namely the Gabor basis functions based detection filter utilizes a pre-trained kernel to do a frequency domain filtering (FDF) and outputs the detected objects. A grayscale fusion of the two branches reduces the false alarm rate  $P_{FM}$ while trying to maintain the object detection rate  $P_D$ . In the final stage, the peak sorting operator further erases potential false detections.

### 2.2 Previous Work

ATR [9][10] are high performance signal processing applications that perform automatic target acquisition, identification, and tracking. Due to their high performance requirements, ATR algorithms have been traditionally implemented on reconfigurable logic based systems [67][23]. Researchers have also explored specialized support vector machine implementations for ATR [78]. The recent advent of commercially available specialized multi-core processor architectures offer exciting new platforms for implementation of ATR. However

| Dilation              | $D_i = MAX_{i-K \le j \le i+K}A_j$                          |

|-----------------------|-------------------------------------------------------------|

| Erosion               | $E_i = MIN_{i-K \le j \le i+K}A_j$                          |

| Closing               | Dilation - Erosion                                          |

| Opening               | Erosion - Dilation                                          |

| НСМО                  | Horizontal Closing - Opening                                |

| VCMO                  | Vertical Closing - Opening                                  |

| Gray Scale Fusion     | $G_i = MIN(A_i, B_i)$                                       |

|                       | GS(A) = IFFT(B)                                             |

| Gaussian Smoothing    | B = FFT(A) * FFT(K)                                         |

|                       | K is a Gaussian Kernel                                      |

| Difference            | $D_i = A_i - B_i$                                           |

| Threshold             | $T_i = 0,  if \ A_i < T$                                    |

|                       | $A_i, if A_i > T$ $G_i = \sum_{j=-S}^{S} A_{i+j} * K_{i+j}$ |

| Gabor Wavelet         | $G_i = \sum_{j=-S}^{S} A_{i+j} * K_{i+j}$                   |

| Gabor Wavelet         | K is a Gabor Kernel                                         |

| Magnitude             | $M_i = A_i,  if \  A_i  > T$                                |

|                       | $0, \ otherwise$                                            |

| Clip High Values      | $C_i = 0,  if \ A_i > T$                                    |

|                       | $A_i, if A_i < T$                                           |

| Squaring              | $S_i = A_i^2$                                               |

| 2-D Dilation          | Horizontal dilation followed by vertical dilation           |

|                       | GB(A) = IFFT(B)                                             |

| Gabor Basis Functions | $B = FFT(A) * X_K$                                          |

|                       | $X_K = \sum \alpha_i * FFT(K_i)$                            |

|                       | $K_i$ is a Gabor Basis Kernel (GBK)                         |

|                       | $\alpha_i$ is weight of GBK                                 |

|                       | Iteratively do:                                             |

| Peak Sorting          | 1 detect object                                             |

|                       | 2 delete object                                             |

|                       | 3 delete its neighborhood                                   |

Table 2.1: Stages in the ATR allgorithm.

to the best of our knowledge, we are not aware of any existing implementation of ATR on such processor architectures.

In recent past, researchers have designed several optimized implementations of stream applications on the Cell BE. In the following we discuss a few representative implementations. Kato et al. [42] implemented a real time digital media application on the Cell BE. Petrini et al. [63] ported the Sweep3D application on the Cell BE. More recently, Baker et al. [4] designed a scalable implementation of the H.264 decoder on the Cell BE. The design experience and optimizations utilized by existing research are relevant for developing any application on the Cell BE. This chapter proposes optimizations that are particularly aimed at exploiting the unique algorithmic characteristics of the ATR application.

Researchers have begun to recognize the daunting challenge of developing applications on the specialized multi-core processor architectures such as the Cell BE. Eichenberger et al. [27] [28] proposed compiler techniques such as memory alignment, branch prediction, SIMDization, thread level parallelism, and data management for alleviating the task of programming the Cell BE. Maeda et al. [53] proposed a multi-layered programming model and a real time resource scheduler. Fatahalian et al. [30] presented a programming language, Sequoia, to facilitate the management of memory hierarchy when developing program with multi-level parallelism. Despite all the efforts that are involved, automated techniques for obtaining optimized parallel implementations on the Cell BE are still in their infancy and not close to commercial deployment.

#### 2.3 Reference Implementation on Pentium4 PC

We first implemented the ATR algorithm on our host PC with a 3.2GHz Intel Pentium4 CPU. The original implementation demonstrated a latency of 3.26s for a  $512 \times 512$  pixel image with 6 distinct objects (varying from  $2 \times 4$  to  $10 \times 4$  pixel size) that were detected. Column 2 of Table 2.2 gives a break down of the run time for various stages of the algorithm. As we can see from the table, the three frequency domain filtering (FDF) modules namely CMO Gaussian, Wavelet Gaussian and Gabor Basis Functions dominate the run time as each of them takes approximately 900 ms to complete. FDF modules contain one 2-dimensional Fast Fourier Transform (FFT), one pointwise matrix multiplication, one 2-dimensional inverse FFT (IFFT), and some miscellaneous functions for type casting and image normalization. Hence, we optimized the code for FFT and IFFT first. In particular, we applied two optimizations. The original FFT implementation accepted complex inputs. However, the image data only has real coefficients with imaginary parts as zero. Further, the FFT calculation has a symmetric kernel for real and imaginary parts of the data. Thus, we can pack two data points into one complex data, and reduce the number of calculations by a factor of 2. Additional data reorganization are required to recover the correct result. The improvements due to this optimization are depicted in Column 3 with gray shaded cells. We applied similar optimizations for IFFT. As our second optimization, we pre-computed the FFT and IFFT twiddle factors and accessed them by table look-up. The improvement due to this optimization over the previous step is depicted in Column 4 with gray cells. Figure 2.2 depicts the overall approach. After the application of these two optimizations the run time of the ATR algorithm reduced to 1.33 s.

### 2.4 Design of ATR on the IBM Cell BE

We utilized the Sony Playstation3 (PS3) with Fedora 7 as the target platform. The Cell BE has 8 SPEs. However, in PS3 only 6 of them are available to the programmer. In this section we discuss the various optimizations that

|                | Run Time (ms) |         |         |          |         |         |         |

|----------------|---------------|---------|---------|----------|---------|---------|---------|

| Functions      |               | PC      |         | PPE      |         |         |         |

|                | Original      | FDF     | FDF     | Original | VMX     | FDF     | FDF     |

|                |               | Real    | Coeff.  |          |         | Real    | Coeff.  |

| Read Image     | 1.38          | 1.38    | 1.38    | 1.06     | 0.86    | 0.86    | 0.86    |

| HCMO           | 207.52        | 207.52  | 207.52  | 106.71   | 106.71  | 106.71  | 106.71  |

| VCMO           | 144.27        | 144.27  | 144.27  | 132.65   | 132.65  | 132.65  | 132.65  |

| CMO Fusion     | 3.97          | 3.97    | 3.97    | 3.82     | 1.90    | 1.90    | 1.90    |

| CMO Gau.       | 907.9         | 517.24  | 267.9   | 3964.30  | 1992.68 | 1072.45 | 412.54  |

| Gabor Wavelet  | 105.05        | 105.5   | 105.5   | 185.66   | 161.51  | 161.51  | 161.51  |

| Detect& Clip   | 1.13          | 1.13    | 1.13    | 1.80     | 1.80    | 1.80    | 1.80    |

| Wavelet Gau.   | 904.47        | 514.16  | 264.47  | 3962.79  | 2000.84 | 1070.81 | 410.67  |

| Squaring       | 2.58          | 2.58    | 2.58    | 10.56    | 5.78    | 5.78    | 5.78    |

| Difference     | 16.8          | 16.8    | 16.8    | 16.59    | 6.45    | 6.45    | 6.45    |

| Threshold      | 1.04          | 1.04    | 1.04    | 3.91     | 3.91    | 3.91    | 3.91    |

| Dilation       | 41.37         | 41.37   | 41.37   | 27.69    | 27.69   | 27.69   | 27.69   |

| GBF            | 906.80        | 506.65  | 256.87  | 4052.68  | 1997.55 | 1087.74 | 407.23  |

| Fusion         | 2.17          | 2.17    | 2.17    | 1.90     | 1.90    | 1.90    | 1.90    |

| Peak Sorting   | 13.01         | 13.01   | 13.01   | 6.25     | 6.25    | 6.25    | 6.25    |

| Write Image    | 0.55          | 0.55    | 0.55    | 3.68     | 2.41    | 2.41    | 2.41    |

| Total Run Time | 3260.01       | 2079.70 | 1330.01 | 12482.05 | 6450.89 | 3690.82 | 1690.26 |

Table 2.2: Profile Analysis of ATR on host PC and PPE.

\*The cell with gray background indicates that the function run time is reduced by the current optimization.

were applied to achieve a high performance implementation of the ATR on the Cell BE. There are a total of eight optimizations that are categorized into 4 basic classes: data parallelism (application mapping), computation acceleration (FFT, SIMD), communication acceleration (matrix transpose, pre-touch memory, mailbox), and communication overhead amortization (double buffering, small function relocation). The various optimizations exploit both the algorithmic characteristics of the ATR application and specific architectural features of the Cell BE. As a first step toward porting ATR onto the Cell BE, we obtained an implementation solely on the PPE (denoted by PPE-Ori).

2.4.1 Porting ATR to PPE

Column 5 of Table 2.2 gives the performance of the original implementation on the PPE which was 12.48 s. This latency is much higher than the original PC implementation as the PPE has a relatively simpler architecture that does not support out of order execution. We next compiled the program such that the Vector Multimedia Extensions (VMX) on the PPE were utilized (Column 6 of Table 2.2). Finally, FDF specific optimizations were applied (Columns 7 and 8 of Table 2.2). The final run time of the implementation was 1.69 s.

#### 2.4.2 Parallelized implementation of ATR

In the following subsections we discuss the 8 optimizations that were applied for obtaining a parallelized implementation of ATR on the Cell BE. In the following the various optimizations are discussed in the order in which they were applied in the case study. Table 2.3 depicts the performance improvements that were obtained by application of each optimization.

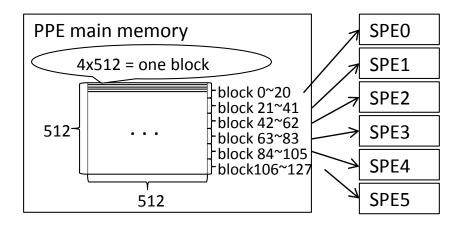

## 2.4.3 Application parallelization on 6 SPEs

We exploited the inherent data parallelism in the ATR algorithm for mapping it to 6 SPEs. The  $512 \times 512$  input image was divided into 128 block each of size  $4 \times 512$  for the morphological operations. Figure 2.3 illustrates this data partition scheme. Similarly for the FDF, the input image was divided into 512 blocks with the size of  $1 \times 512$  for each block. Note that in both the partition schemes, either  $4 \times 512$  (type of unsigned char) or  $1 \times 512$  (type of float), the size of each data piece is 2KB. This data size was selected in favor of the DMA/DMAList performance as discussed in Section 1.2. The latency of the first parallel implementation was 0.797 s (Column 2 of Table 2.3). Column 2 of Table 2.4 gives break-up of the communication and computation overheads for a few critical functions.

#### 2.4.4 Double buffering

Double buffering as the name suggests doubles the amount of memory utilized for communication between PPE and SPE. Essentially, while the SPE may be operating upon data in buffer 0, a DMA operation may be loading new data in buffer 1 from PPE. Similarly while the SPE may be writing to buffer 0, a DMA may be transferring data from buffer 1 to PPE. Double buffering enables amortization of communication overheads by overlapping it with computation. Double buffering is a well known mechanism for data memory management in software controlled memory systems. Double buffering can also be considered as pipelining of data reading, computation and data writing stages. Similar to pipelining, it also has a "warm up" and "drain out" time which should be ideally as small as possible. However, we also need to take the DMA/DMAList performance into account (Section 1.2). Consequently, a granularity of 2KB was selected to implement our double buffering scheme.

Column 3 in Table 2.3 gives the improvement achieved due to double buffering. As the results indicate double buffering only gave us incremental improvement to 0.769 s. Column 3 of Table 2.4 shows the same trend. This poor improvement was later diagnosed to high translation look aside buffer (TLB) and page table entry (PTE) misses overhead. Once these misses were eliminated the overall performance showed a significant improvement. Further details that addresses pre-touching of memory are discussed in Section 2.4.9.

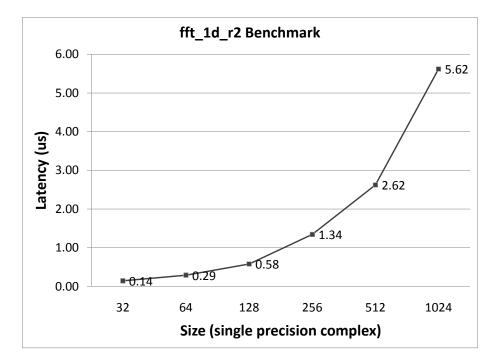

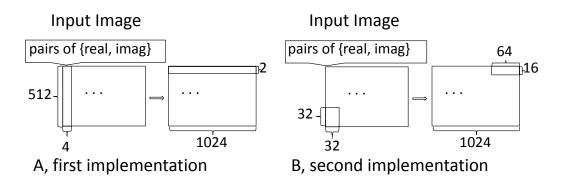

# 2.4.5 2-D FFT

We utilized the 1-D FFT kernel fft 1d r2 from the IBM SDK 3.0 to compute the 2-D FFT on the SPE. Figure 2.4 plots the performance of the fft 1d r2 kernel. As it is written in assembly, it demonstrates a performance of 5.62 $\mu s$  for a 1024 point FFT. However, it also posed several difficulties when it was utilized to implement a 2-D FFT. First, To compute 2-D FFT on the whole image, two sequential executions of the fft\_1d\_r2 kernel and 2 matrix transposes are required. Figure 2.5, Algorithm 1 line  $1 \sim \text{line } 4$  illustrates this basic scheme. Second, fft 1d r2 only takes complex input with each element represented by a pair of  $\langle real, imag \rangle$ , indicating that additional data reformulation is required. In our implementation, we utilized the spu shuffle intrinsic to efficiently re-format the data. We also managed to remove two matrix transposes from the FDF by modifying the flow as illustrated in Figure 2.5, Algorithm 2. The optimizations reduced the run time of each FDF module by almost half. The profile analysis is shown in Column 4 of Table 2.3. Column 3 of Table 2.4 gives the corresponding computation time and communication time. Since the FDF modules only work on half the data compared to the previous step, the data communication time also showed a large reduction. Consequently, we achieved an overall 34% performance improvement at this step.

#### 2.4.6 Matrix transpose

There are two matrix-transpose operations in each FDF module. We first utilized DMAList to fetch 128 bit data for each column, that is 512x4 floats, and then transpose them back as 2 rows. Figure 2.6 (A) gives an overview

of this scheme. The shape change is due to the representation of a complex data point. However, this simple scheme has a very big problem: for each single DMA inside the DMAList, the data size is only 128 bit, and 7 out of 8 of them are not 128 Bytes aligned. Both these aspects greatly impacted the performance [45]. The resulting matrix-transposes were so expensive that they took more than 40% of the total run time. Observing that the bottleneck comes from the DMAList operations, our second implementation gathers 32x32 floats from the PPE main memory, transposes them, and puts them back as 16x64 floats, as illustrated in Figure 2.6 (B). In the new approach, the data communication for the FDF module dropped down by more than half as shown in Column 5 of Table 2.4. The overall performance was improved by 35% as reported on Column 5 of Table 2.3.

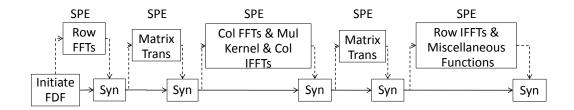

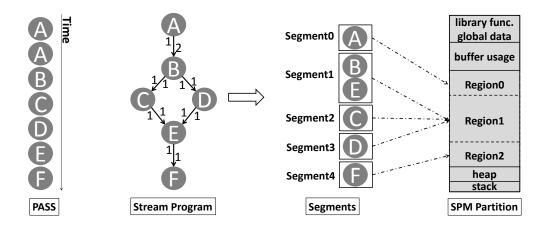

#### 2.4.7 Small function relocation

In this step we analyzed the computation granularity of non-performance intensive functions. Specifically, functions whose execution on the PPE could be hidden by other functions executing in parallel on SPE were assigned to PPE. Further, if the data transfer time for some functions executing on SPE was greater than their run time on the PPE, they were also assigned to the PPE. Figure 2.7 shows the final parallel schedule for execution of the application on the Cell BE. A module that is labeled as SPE in the figure executes in parallel across the 6 SPEs. A module that is not labeled executes on the PPE. Further, the "syn" module denotes barrier synchronization. Figure 2.8 gives the schedule for execution of high level modules (namely CMO Gaussian smoothing, Wavelet Gaussian smoothing, Gabor basis function detection). Column 6 of Table 2.3 illustrates the impact of this optimization. The cells marked with '-' denote that after small function relocation, these functions were either hidden by the execution of other functions, or they were combined to the end of the FDF modules.

# 2.4.8 SIMD & loop unrolling

There are two approaches that can be applied for code vectorization on the Cell BE, namely, manual vectorization or the IBM xlc compiler. The xlc compiler reduces the effort required for vectorization. However, in our experience the compiler was not found to be very effective as manual optimizations out performed the compiler generated code. Consequently, functions that were computationally intensive were vertorized/unrolled manually. On the other hand, less computationally intensive functions were optimized by the xlc compiler in our implementation. Column 7 of Table 2.3 and Column 6 of Table 2.4 detail the effects of this optimization.

# 2.4.9 Pretouch memory

There are two basic categories of memory hierarchy misses occurring in our code, namely TLB (Translation Lookaside Buffer) misses, and the PTE (Page Table Entry) misses. The TLB misses always take place when the SPEs first get started. We reference this delay by TLB warm-up time. As soon as the TLB table gets filled up, this delay disappears. The TLB warm-up time is predictable, and more or less stable. This delay in our implementation is hidden by the computation of "HCMO" and "Gabor Wavelet" through double buffering.

Besides TLB warm-up time, normal TLB misses also occur in the program. Normal TLB misses are unpredictable and thus hard to eliminate. Pretouching the memory can substantially reduce the overhead. Pre-touching implies that the memory is accessed but not operated upon. Pre-touching by the PPE ensures that the required page is in the main memory. Pre-touching by SPE ensure that the TLB entry is upto date. Pre-touching is scheduled to occur earlier than the execution of the DMA/DMAList transfers that actually access the page.

PTE misses are handed over to the operating system as an interrupt. Therefore, the processing time for PTE misses are much higher than TLB misses. This overhead could be thousands of micro-seconds compared to several micro-seconds for TLB misses. We discovered that PTE misses happen when a certain memory location is referenced by the SPEs for the first time before any PPE functions touch the same memory. Therefore, we managed to eliminate PTE misses by pre-touching the memory with PPE. Those operations were able to bring the run time down to 0.087 seconds. Examining the computation and communication time of each function in Table 2.4, we obverse that after this step, the communication time became smaller than the computation time for most of the functions mapped to the SPEs. The full impact of double buffering was realized after this optimization.

## 2.4.10 Mailbox communication

Mailbox communication is utilized to implement all synchronizations in our design. Experiments on the Cell processor showed that the classic mailbox implementation could take thousands of micro-seconds in the worst case. This unpredictable behavior resulted in degraded performance of our code. We examined several alternative implementation strategies including signaling, problem state area mapped mailbox, and DMA. The problem state area mapped mailbox implementation turned out to be the best solution with more than  $5 \times 10^5$  rounds of synchronization per second between the PPE and 6 SPEs. A detailed profile of problem state area mapped mailbox performance is shown in Table 2.5. After the application of this final optimization, the run time of our program dropped down to less than 70 milliseconds as detailed in Column 9 of Table 2.3.

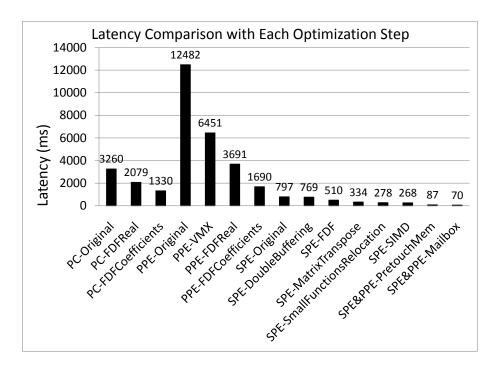

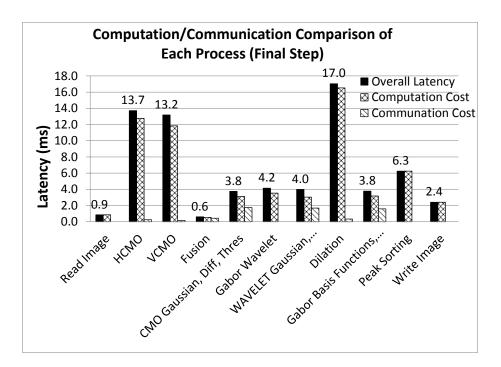

# 2.5 Experimental Results

In our final implementation, the code and data adds up to 131.625 KB for each SPE, which indicates that we have more than 120 KB of local store memory left for the stack and heap. Figure 2.9 summarizes the performance impacts of various optimizations on Pentium4 based PC, on PPE only, and on Cell processor across one PPE and 6 SPEs. The final run time coupled with the computation/communication time for each process is shown in Figure 2.10. As we can see from the figure, HCMO, VCMO and 2-D Dilation take up to 40% of the total run time in the final implementation. There are two reasons. First, the Dilation and Erosion operators that serve as the basic modules for the CMO and 2-D Dilation processes are sequential operations. Consequently, SIMDization has limited impact. Second, the Dilation and Erosion consist of conditional branches, which cannot be handled efficiently on SPEs that are primarily aimed at stream applications.

## 2.6 Summary

We presented a detailed case study of designing an ATR algorithm on the Cell BE in this chapter. Various optimizations that exploited both the unique features of the application as well as the target architecture were presented. The optimizations are applicable to other algorithms and architectures that have similar features as ATR and the Cell BE. The final implementation shows a latency of 0.07 s on a PS3 platform with 6 SPEs. The optimized performance was almost 20 times faster than our best efforts on a Pentium4 CPU. The achieved performance validates both the impact of our optimizations and the processing capabilities of the Cell BE.

Algorithm: 2 Dimensional Real FFT

Row FFT

$/*ROW_{ij}$  denotes the  $i_{th}$  row,  $j_{th}$  element in the image, R and I are one dimensional arrays that store the real and imag inputs of IDFFT\*/ 1 for i from 0 to 256 $\mathbf{2}$ for j from 0 to 511  $R_j = ROW_{2i,j}, I_j = ROW_{2i+1,j}$ 3 4 endfor /\*R and I are input arrays of 1DFFT, tempR and tempI are output arrays\*/ 1DFFT(R, I, 512, tmpR, tmpI)5 $R_{512} = R_0, I_{512} = I_0$ 6  $/^{*}R'$  and I', 2 dimensional arrays that store the results of 1DFFTs\*/ for j from 0 to 511 7 $\begin{array}{l} R'_{2i,j} = tmpR_j + tmpR_{512-j}, \ R'_{2i+1,j} = tmpI_j + tmpI_{512-j} \\ I'_{2i,j} = tmpI_j - tmpI_{512-j}, \ I'_{2i+1,j} = tmpR_{512-j} - tmpR_j \end{array}$ 8 9 10 endfor 11 endfor 12 Matrix Transpose Col FFT 13 for i from 0 to 256for j from 0 to 511 14 $R_j = R'_{i,j}, I_j = I'_{i,j}$ 1516endfor 171DFFT(R, I, 512, tempR, tempI)18 for j from 0 to 511  $R'_{i,j} = tempR_j, I'_{i,j} = -tempI_j$ if  $i \neq 0$  and  $i \neq 256$  /\*recover the other half of the image\*/ 1920 $R'_{512-i,512-(j+1)} = tempR_j$ 21 $I'_{512-i,512-(j+1)} = -tempI_j$ 2223endif 24endfor 25 endfor

Figure 2.2: 2-Dimensional real FFT.

Figure 2.3: Data partition for the morphological filter

|               |        |           |        | Run Ti | ime (ms) |        |          |         |

|---------------|--------|-----------|--------|--------|----------|--------|----------|---------|

| <b>D</b>      | SPE    | SPE       | SPE    | SPE    | SPE      | SPE    | S/PPE    | S/PPE   |

| Functions     | Orig.  | Double    | Real & | Matrix | Small    | Simd   | PreTouch | Mailbox |

|               | Ū      | Buffering | Coef.  | Trans. | Func.    |        | Memory   |         |

| Read Image    | 0.86   | 0.86      | 0.86   | 0.86   | 0.86     | 0.86   | 0.86     | 0.86    |

| HCMO          | 44.72  | 36.65     | 36.65  | 36.65  | 32.26    | 32.26  | 17.75    | 13.72   |

| VCMO          | 29.49  | 22.37     | 22.37  | 22.37  | 21.52    | 21.52  | 14.18    | 13.20   |

| CMO Fusion    | 1.90   | 1.90      | 1.90   | 1.90   | 1.90     | 1.90   | 0.61     | 0.61    |

| CMO Gau.      | 219.65 | 214.23    | 133.25 | 68.35  | 65.72    | 62.87  | 7.28     | 4.23    |

| Gabor Wavelet | 8.29   | 8.29      | 8.29   | 8.29   | 4.15     | 4.15   | 4.15     | 3.75    |

| Detect & Clip | 1.80   | 1.80      | 1.80   | 1.80   | -        | -      | -        | -       |

| Wavelet Gau.  | 227.21 | 221.10    | 124.73 | 63.21  | 57.38    | 57.24  | 7.26     | 3.99    |

| Squaring      | 5.78   | 5.78      | 5.78   | 5.78   | -        | -      | -        | -       |

| Difference    | 6.45   | 6.45      | 6.45   | 6.45   | -        | -      | -        | -       |

| Threshold     | 3.91   | 3.91      | 3.91   | 3.91   | -        | -      | -        | -       |

| Dilation      | 45.32  | 31.43     | 31.43  | 31.43  | 31.43    | 31.43  | 18.49    | 17.03   |

| GBF           | 190.82 | 204.22    | 121.65 | 72.16  | 49.84    | 46.99  | 7.91     | 3.78    |

| Fusion        | 1.90   | 1.90      | 1.90   | 1.90   | -        | -      | -        | -       |

| Peak Sorting  | 6.25   | 6.25      | 6.25   | 6.25   | 6.25     | 6.25   | 6.25     | 6.25    |

| Write Image   | 2.41   | 2.41      | 2.41   | 2.41   | 2.41     | 2.41   | 2.41     | 2.41    |

| Total Time    | 796.76 | 768.55    | 509.63 | 333.72 | 279.80   | 267.88 | 87.15    | 69.83   |

Table 2.3: Profile Analysis of ATR on PPE and SPEs.

\*The cells colored with gray indicate that the function is affected by the current optimization. The cells marked with '-' indicates the function execution is hidden by the execution of other functions, or padded to the end of the FDF modules.

|              | Computation/Communication Time (ms) |              |             |             |             |            |

|--------------|-------------------------------------|--------------|-------------|-------------|-------------|------------|

| Functions    | SPE                                 | SPE          | SPE         | SPE         | SPE         | S/PPE      |

| Functions    | Original                            | Double       | Real &      | Matrix      | SIMD        | Pretouch   |

|              | -                                   | Buffering    | Coef.       | Small Func  |             | Mailbox    |

| HCMO         | 12.77/20.14                         | 12.77/17.23  | 12.77/17.23 | 12.77/17.23 | 12.77/17.23 | 12.77/0.24 |

| VCMO         | 11.84/8.90                          | 11.84/6.60   | 11.84/6.60  | 11.84/6.60  | 11.84/6.60  | 11.84/0.16 |

| CMO Gau.     | 18.31/165.05                        | 18.31/161.05 | 5.12/117.50 | 5.74/54.72  | 3.12/54.72  | 3.12/1.75  |

| Wavelet Gau. | 18.20/161.75                        | 18.20/176.3  | 4.46/101.3  | 4.79/49.57  | 3.04/49.57  | 3.04/1.69  |

| Dilation     | 16.52/18.30                         | 16.52/12.13  | 16.52/12.13 | 16.52/12.13 | 16.52/12.13 | 16.52/0.33 |

| GBF          | 18.46/149.54                        | 18.46/154.49 | 5.25/97.70  | 5.41/36.54  | 3.18/36.54  | 3.18/1.62  |

Table 2.4: Computation/Communication Latency Comparison.

\*The cells colored with gray indicates that either the run time or the communication time of the function were effected by the current optimization.

Figure 2.4: fft\_1d\_r2 profile on one SPE.

| FDF Algorithm 1   | FDF Algorithm 2              |

|-------------------|------------------------------|

| 1 Row 1DFFTs      | 1 Row 1DFFTs                 |

| 2 Image Transpose | 2 Image Transpose            |

| 3 Column 1DFFTs   | 3 Column 1DFFTs              |

| 4 Image Transpose | 4 Multiply Transposed Kernel |

| 5 Multiply Kernel | 5 Column 1DIFFTs             |

| 6 Row 1DIFFTs     | 6 Image Transpose            |

| 7 Image Transpose | 7  Row 1D IFFTs              |

| 8 Column 1DIFFTs  |                              |

| 9 Image Transpose |                              |

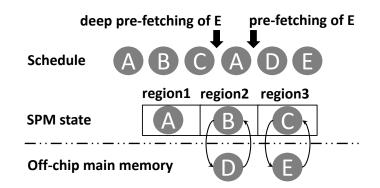

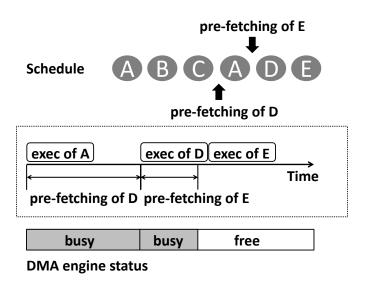

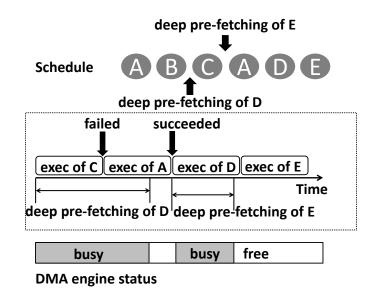

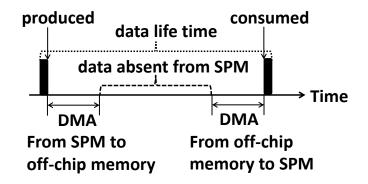

Figure 2.5: Unoptimized and Optimized FDF.