Digitally Controlled DC-DC Buck Converters with

Lossless Current Sensing

by

Tao Liu

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved October 2011 by the Graduate Supervisory Committee:

Bertan Bakkaloglu, Chair Sule Ozev Bert Vermeire Yu Cao

ARIZONA STATE UNIVERSITY

December 2011

### ABSTRACT

Current sensing ability is one of the most desirable features of contemporary current or voltage mode controlled DC-DC converters. Current sensing can be used for over load protection, multi-stage converter load balancing, current-mode control, multi-phase converter current-sharing, load independent control, power efficiency improvement etc. There are handful existing approaches for current sensing such as external resistor sensing, triode mode current mirroring, observer sensing, Hall-Effect sensors, transformers, DC Resistance (DCR) sensing, Gm-C filter sensing etc. However, each method has one or more issues that prevent them from being successfully applied in DC-DC converter, e.g. low accuracy, discontinuous sensing nature, high sensitivity to switching noise, high cost, requirement of known external power filter components, bulky size, etc.

In this dissertation, an offset-independent inductor Built-In Self Test (BIST) architecture is proposed which is able to measure the inductor inductance and DCR. The measured DCR enables the proposed continuous, lossless, average current sensing scheme.

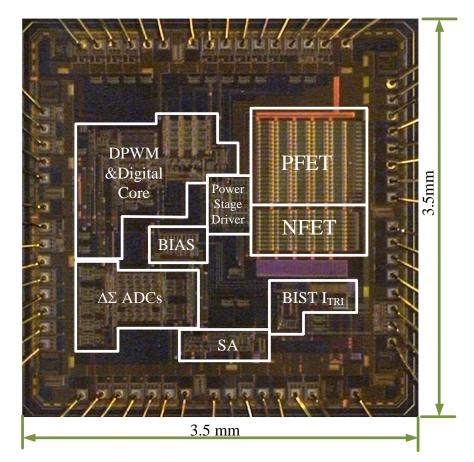

A digital Voltage Mode Control (VMC) DC-DC buck converter with the inductor BIST and current sensing architecture is designed, fabricated, and experimentally tested. The average measurement errors for inductance, DCR and current sensing are 2.1%, 3.6%, and 1.5% respectively. For the 3.5mm by 3.5mm die area, inductor BIST and current sensing circuits including related pins only consume 5.2% of the die area. BIST mode draws 40mA current for a maximum time period of 200us upon start-up and the continuous current sensing consumes

about 400uA quiescent current. This buck converter utilizes an adaptive compensator. It could update compensator internally so that the overall system has a proper loop response for large range inductance and load current.

Next, a digital Average Current Mode Control (ACMC) DC-DC buck converter with the proposed average current sensing circuits is designed and tested. To reduce chip area and power consumption, a 9 bits hybrid Digital Pulse Width Modulator (DPWM) which uses a Mixed-mode DLL (MDLL) is also proposed. The DC-DC converter has a maximum of 12V input, 1-11 V output range, and a maximum of 3W output power. The maximum error of one least significant bit (LSB) delay of the proposed DPWM is less than 1%. To My Parents Jiliang Liu and Luying Wu

#### ACKNOWLEDGMENTS

I would like to express my heartfelt gratitude to my advisor and committee chair, Professor Bertan Bakkaloglu, without whom my research and this dissertation would not have been possible. I am very grateful for his advising, encouragement, inspiration, and enduring patience. Dr. Bakkaloglu has watched every step that I have walked in the past several years. His help has become my life-long heritage.

I would also like to give special appreciation to Dr. Yu (Kevin) Cao, Dr. Sule Ozev, and Dr. Bert Vermeire for serving as my committee members. I benefit a lot from the insightful discussion with Dr. Vermeire on chip ESD design. Dr. Ozev has also given me very valuable suggestions on inductor tests.

I want to thank all the members in analog & RF integrated circuit design lab who helped me throughout my stressful PhD period: Dr. Hyunsoo Yeom, Dr. Hang Song, Dr. Hani Ahmad, Dr. Junghan Lee, Dr. Hyuntae Kim, Dr. Seungkee Min, Mr. Ahmad Dashtestani, Mr. Sridhar Shashidharan, Mr. Chao Fu and. Ms. Jing Bai. I owe special thanks to Dr. Hyunsoo Yeom for his patience and great help on the layout design of my every chip tape-out. I also want to express special thanks to Chao Fu for his critical support on average current mode controller design.

Last but not least, I would like to show my great appreciation to Space Micro, Inc. and NASA Jet Propulsion Laboratory for funding this project. Thank Dr. Philippe Adell from NASA and Dr. Bert Vermeire from Space Micro for their inspiration, comments, and recommendations during design reviews.

# TABLE OF CONTENTS

| Page                                             |        |  |  |  |  |

|--------------------------------------------------|--------|--|--|--|--|

| LIST OF TABLES                                   |        |  |  |  |  |

| LIST OF FIGURES xi                               |        |  |  |  |  |

| HAPTER                                           | CHAPTE |  |  |  |  |

| 1 INTRODUCTION                                   | 1      |  |  |  |  |

| 1.1 Research Background1                         |        |  |  |  |  |

| 1.1.1 DC-DC Application                          |        |  |  |  |  |

| 1.1.2 Digital Control of DC-DC Converter         |        |  |  |  |  |

| 1.1.3 Research Motivation                        |        |  |  |  |  |

| 1.2 Dissertation Outline                         |        |  |  |  |  |

| 2 STATE-OF-THE-ART CURRENT SENSING TECHNIQUES 10 | 2      |  |  |  |  |

| 2.1 Instantaneous Inductor Current Sensing11     |        |  |  |  |  |

| 2.1.1 External $R_{SENSE}$                       |        |  |  |  |  |

| 2.1.2 Power FET $R_{DS}$ Sensing                 |        |  |  |  |  |

| 2.1.3 Triode Mode Current Mirroring 14           |        |  |  |  |  |

| 2.1.4 Hall-effect Sensor                         |        |  |  |  |  |

| 2.1.5 Transformer 15                             |        |  |  |  |  |

| 2.1.6 Observer                                   |        |  |  |  |  |

| 2.1.7 Inductor DCR Sensing                       |        |  |  |  |  |

| 2.1.8 Gm-C Filter 19                             |        |  |  |  |  |

| 2.2 Average Inductor Current Sensing             |        |  |  |  |  |

| 2.2.1 Average Current Sensing                    |        |  |  |  |  |

|   | 2.2.2 Averaging Filter                                       |

|---|--------------------------------------------------------------|

|   | 2.2.3 Geometric Relation Based Predication                   |

|   | 2.3 Summary of Current Sensing Techniques                    |

| 3 | DIGITAL VMC BUCK CONVERTER CORE                              |

|   | 3.1 Digital VMC Buck Converter Core Architecture Overview 27 |

|   | 3.2 Digital VMC Buck Converter Core Implementation           |

|   | 3.2.1 DPWM                                                   |

|   | 3.2.1.1 DLL Overall Architecture                             |

|   | 3.2.1.2 Charge Pump                                          |

|   | 3.2.1.3 Delay Stage                                          |

|   | 3.2.2 ΔΣ ADC                                                 |

|   | 3.2.2.1 ΔΣ Modulator                                         |

|   | 3.2.2.2 CIC Decimator                                        |

|   | 3.2.2.3 ADC Resolution                                       |

|   | 3.2.3 PID Compensator                                        |

|   | 3.2.3.1 Uncompensated Loop 46                                |

|   | 3.2.3.2 PD Compensator                                       |

|   | 3.2.3.3 PI Compensator                                       |

|   | 3.2.3.4 Combined PID Compensator 50                          |

|   | 3.2.4 Level Shifter 56                                       |

|   | 3.2.5 Power Stage Driver                                     |

| 4 | INDUCTOR BIST AND CURRENT SENSING ARCHITECTURE 60            |

5

| 4.1 Inductor BIST Architecture            |

|-------------------------------------------|

| 4.1.1 Inductance and DCR measurement      |

| 4.1.2 Triangular Current Generator        |

| 4.1.2.1 Charge Pump                       |

| 4.1.2.2 Hysteric Comparator               |

| 4.1.3 ADC Gain Calibration                |

| 4.1.4 Power Stage Driver Modification     |

| 4.1.4.1 Short Path Issue                  |

| 4.1.4.2 Modified Power Stage Driver       |

| 4.2 Current Sensing Architecture          |

| 4.2.1.1 Current Sensing Theory            |

| 4.2.1.2 SA Output Averaging               |

| DIGITAL VMC BUCK CONVERTER MEASUREMENT 80 |

| 5.1 PCB Design and Test Setup             |

| 5.2 Measurement Results                   |

| 5.2.1 DPWM Linearity                      |

| 5.2.2 ΔΣADC                               |

| 5.2.3 Load Regulation Measurement         |

| 5.2.4 Efficiency Measurement              |

| 5.2.5 BIST Mode Measurement               |

| 5.2.5.1 BIST Mode Analog Signal           |

| 5.2.5.2 Inductance Measurement            |

| TE | R I                                                  | Page |

|----|------------------------------------------------------|------|

|    | 5.2.5.3 DCR Measurement                              | 89   |

|    | 5.2.6 Current Sensing Performance                    | 89   |

|    | 5.2.7 Load current based PID Adaptation              | 90   |

|    | 5.3 Chip Performance Summary                         | 94   |

| 6  | DIGITAL ACMC BUCK CONVERTER                          | 96   |

|    | 6.1 Digital ACMC Buck Converter Overall Architecture | 97   |

|    | 6.2 Digital ACMC Buck Converter Implementation       | 99   |

|    | 6.2.1 DPWM                                           | 99   |

|    | 6.2.1.1 Up/Dn Counter                                | 100  |

|    | 6.2.1.2 I-DAC and ICDL                               | 101  |

|    | 6.2.2 Level Shifter                                  | 103  |

|    | 6.2.3 Average Current Mode Controller                | 104  |

|    | 6.2.3.1 Current Loop Compensator Design              | 104  |

|    | 6.2.3.2 Voltage Loop Compensator Design              | .112 |

|    | 6.2.3.3 Compensator Implementation                   | .116 |

| 7  | DIGITAL ACMC BUCK CONVERTER MEASUREMENT              | .119 |

|    | 7.1 PCB Design and Test Setup                        | 120  |

|    | 7.2 Measurement Results                              | 121  |

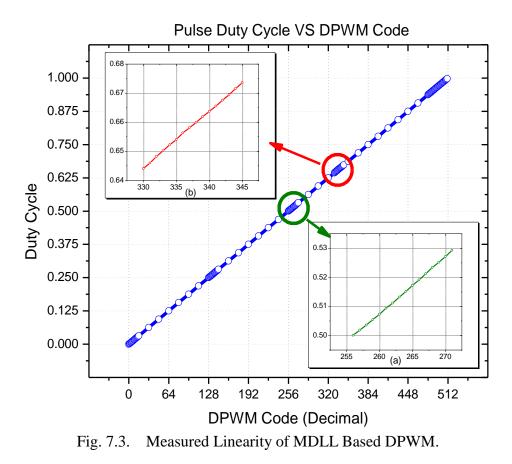

|    | 7.2.1 DPWM Linearity Measurement                     | 121  |

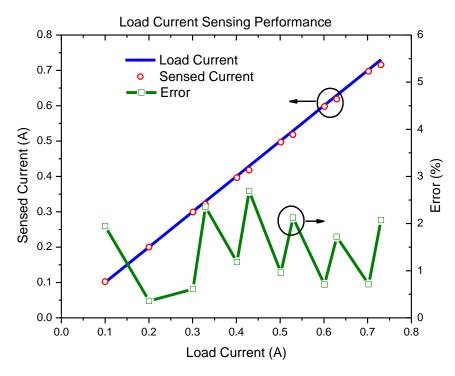

|    | 7.2.2 Average Current Sensing Performance            | 123  |

|    | 7.2.3 Load Regulation Measurement                    | 124  |

|    | 7.2.4 Efficiency Measurement                         | 125  |

| CHAPTER    | Page                         |

|------------|------------------------------|

| 7.3        | Chip Performance Summary 126 |

| 8 CONC     | CLUSION 128                  |

| 8.1        | Summary 128                  |

| 8.2        | Future Work                  |

| REFERENCES |                              |

# LIST OF TABLES

| Page |                                                        | Table |

|------|--------------------------------------------------------|-------|

| 2    | Typical Number of PMICs in Portable Devices            | 1.1.  |

| 5    | Comparison Between Digital and Analog Control in DC-DC | 1.2.  |

|      | Slopes of the Inductor Current Waveform.               | 2.1.  |

|      | Summary of Conventional Current Sensing Techniques     | 2.2.  |

| 56   | Summary of Parameters Used in PID Compensator Design   | 3.1.  |

|      | Summary of Digital VMC DC-DC Performance               | 5.1.  |

| 107  | Choice of Compensator Type                             | 6.1.  |

| 126  | Summary of Digital ACMC DC-DC Performance              | 7.1.  |

| L | JS | Т | OF | FI | GU | RES |

|---|----|---|----|----|----|-----|

|   |    |   |    |    |    |     |

| Figure | Page                                                             |

|--------|------------------------------------------------------------------|

| 1.1.   | Generic Digitally Controlled Voltage Mode DC-DC Buck Converter 7 |

| 2.1.   | External <i>R</i> <sub>SENSE</sub> Current Sensing11             |

| 2.2.   | Power MOSFET <i>R</i> <sub>DS</sub> Current Sensing              |

| 2.3.   | Triode Mode Current Mirroring Current Sensing14                  |

| 2.4.   | Transformer Current Sensing16                                    |

| 2.5.   | Observer Current Sensing                                         |

| 2.6.   | DCR Current Sensing                                              |

| 2.7.   | Gm-C Filter Based Current Sensing 19                             |

| 2.8.   | Average Current Sensing                                          |

| 2.9.   | Geometric Relation Based Predication                             |

| 3.1.   | Digitally Controlled Buck Converter Architecture                 |

| 3.2.   | DPWM Architecture and Operation Waveform                         |

| 3.3.   | DLL Architecture                                                 |

| 3.4.   | Charge Pump in DLL                                               |

| 3.5.   | Waveforms of DLL at Normal Lock Status (Delay=T)                 |

| 3.6.   | Waveforms of DLL at Multiple-Period-Lock Status (Delay=2T)35     |

| 3.7.   | Waveforms of DLL at Half Period Delay Status (Delay=T/2)         |

# Figure

| 3.8.  | DLL VCDL Delay vs Vctrl                             |

|-------|-----------------------------------------------------|

| 3.9.  | $\Delta\Sigma$ ADC Architecture                     |

| 3.10. | VCO in $\Delta\Sigma$ Modulator                     |

| 3.11. | Two-Stage CIC Decimator                             |

| 3.12. | Bode Plot of the Combined PID Compensator           |

| 3.13. | Digital Implementation of PID Compensator           |

| 3.14. | Small Signal Model of Buck Converter                |

| 3.15. | Bode Plot of the Uncompensated Loop 54              |

| 3.16. | Bode Plot of the PID Compensator55                  |

| 3.17. | Bode Plot of the Compensated Complete System 55     |

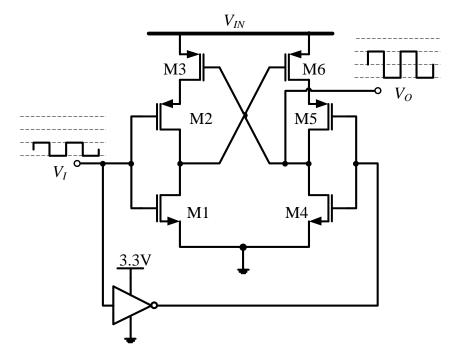

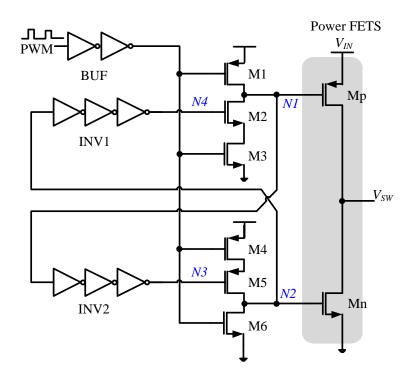

| 3.18. | Level Shifter                                       |

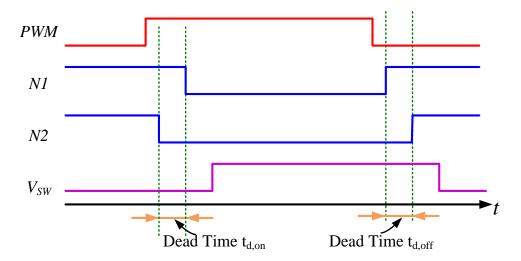

| 3.19. | Power Stage Driver with Built-In Dead Time          |

| 3.20. | Illustration of the Dead Time in Power Stage Driver |

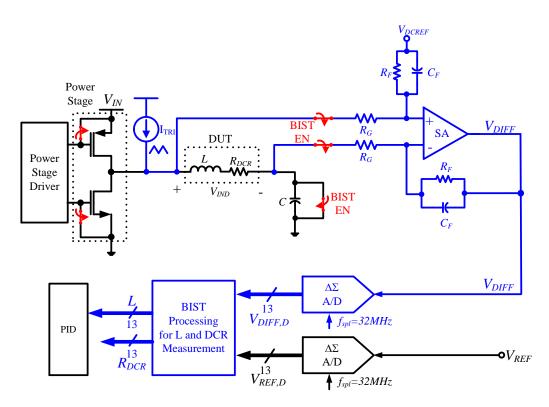

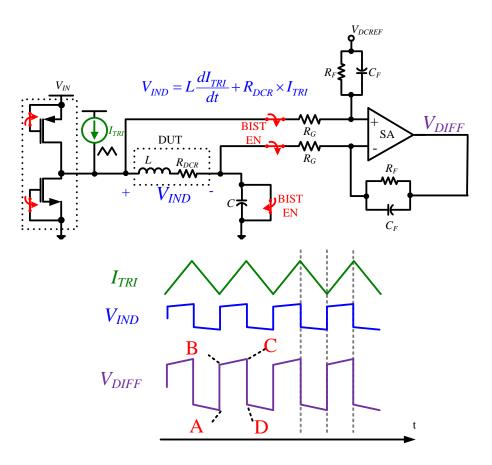

| 4.1.  | Overall Inductor BIST Architecture                  |

| 4.2.  | Illustration of Inductance and DCR measurement      |

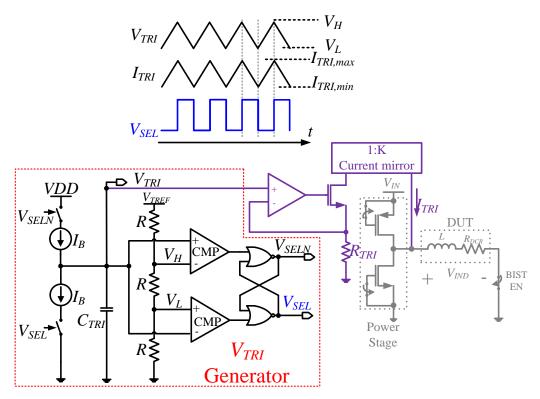

| 4.3.  | Triangular Current Generator                        |

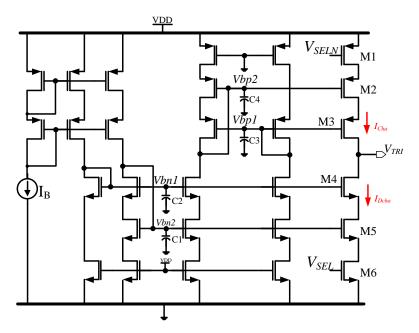

| 4.4.  | Charge Pump in Triangular Current Generator         |

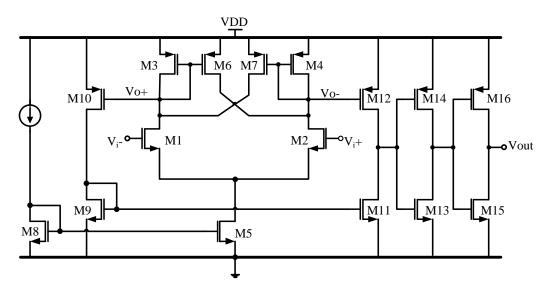

| 4.5.  | Hysteric Comparator in Triangular Current Generator |

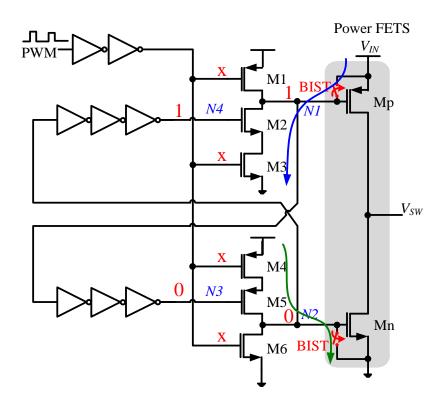

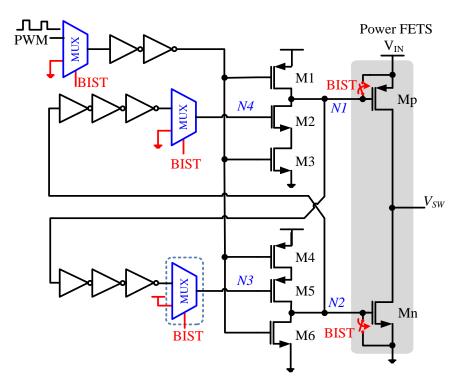

| 4.6.  | Illustration of Short Paths in Conventional Power Stage Driver         |

|-------|------------------------------------------------------------------------|

| 4.7.  | Modified Power Stage Driver with Built-In Dead Time71                  |

| 4.8.  | MUX in Modified Power Stage Driver72                                   |

| 4.9.  | Proposed Current Sensing Architecture73                                |

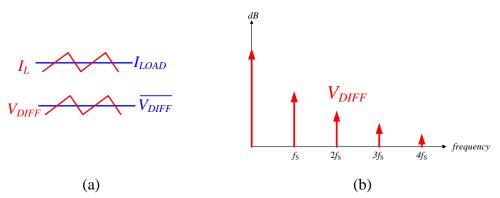

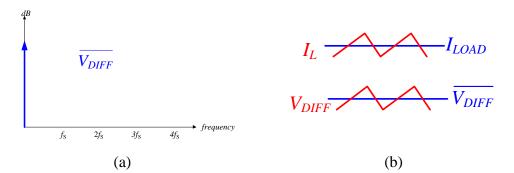

| 4.10. | SA Output V <sub>DIFF</sub> (a) Time-Domain (b) Spectrum               |

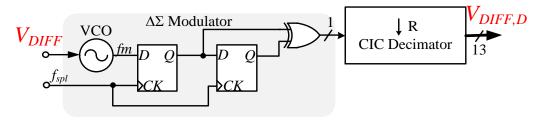

| 4.11. | <i>V<sub>DIFF</sub></i> Digitization77                                 |

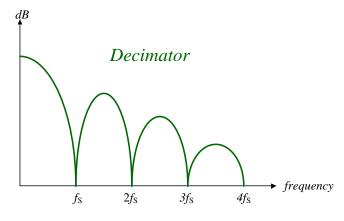

| 4.12. | Spectrum of CIC Decimator                                              |

| 4.13. | Digitized $V_{DIFF}$ (a) Spectrum (b) Equivalent Time Domain Signal 78 |

| 5.1.  | Digital VMC Buck Converter Die Micrograph                              |

| 5.2.  | Digital VMC Buck Converter Test Board                                  |

| 5.3.  | Digital VMC Buck Converter Test Lab Setup                              |

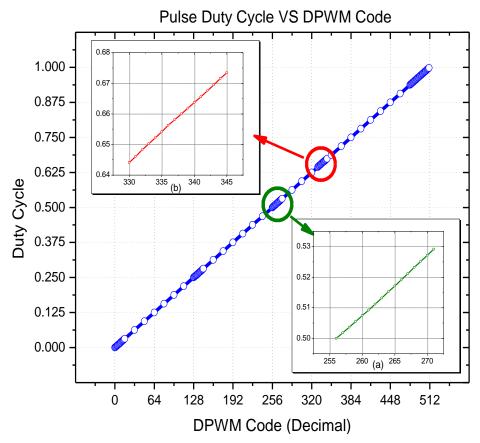

| 5.4.  | Measured Digital VMC Buck Converter DPWM Linearity                     |

| 5.5.  | Measured Frequency $\Delta\Sigma$ ADC Performance                      |

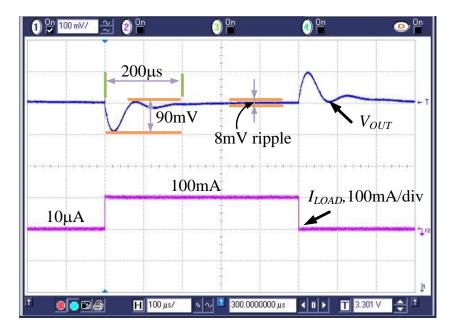

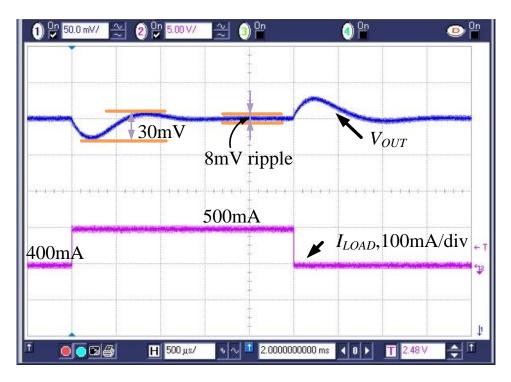

| 5.6.  | Typical Digital VMC Buck Converter Transient Response                  |

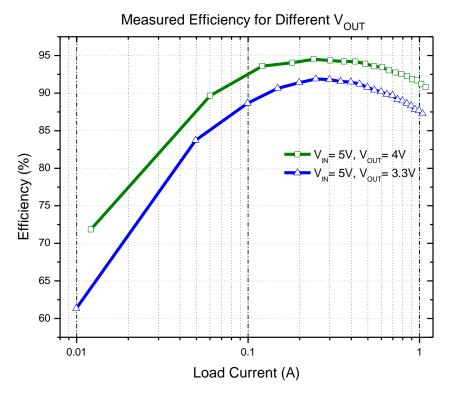

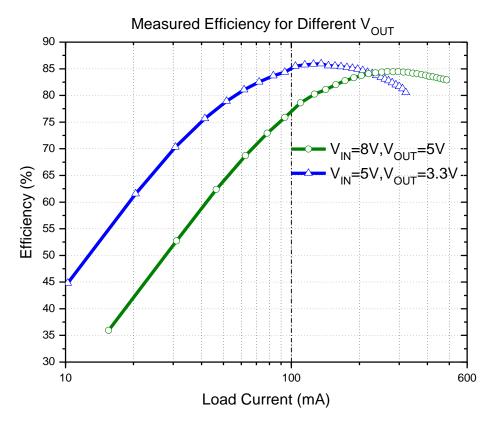

| 5.7.  | Measured Digital VMC Buck Converter Efficiency                         |

| 5.8.  | Typical BIST Mode Waveforms                                            |

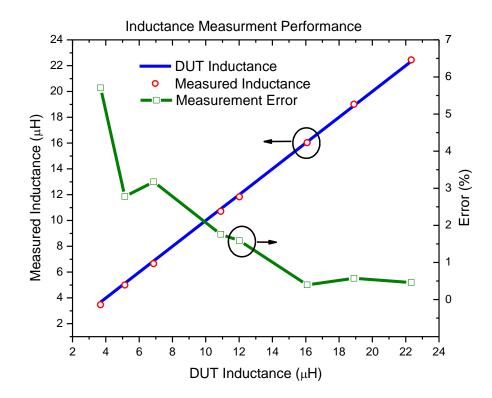

| 5.9.  | Inductor Inductance Measurement Performance                            |

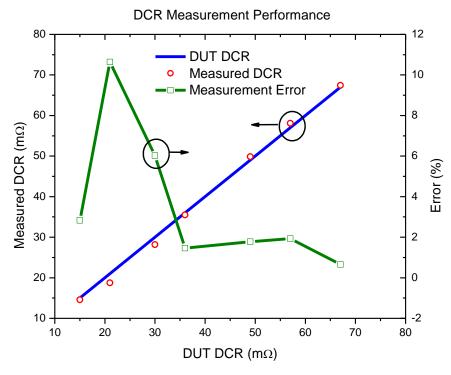

| 5.10. | Inductor DCR Measurement Performance                                   |

| Figure | Page                                              |

|--------|---------------------------------------------------|

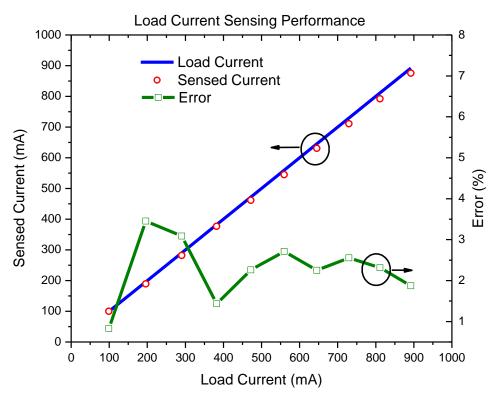

| 5.11.  | Load Current Sensing Performance                  |

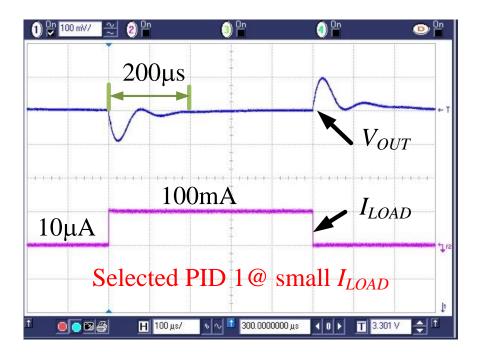

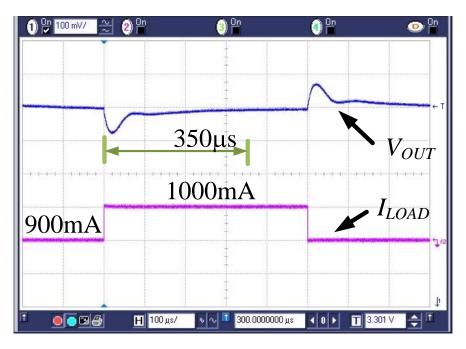

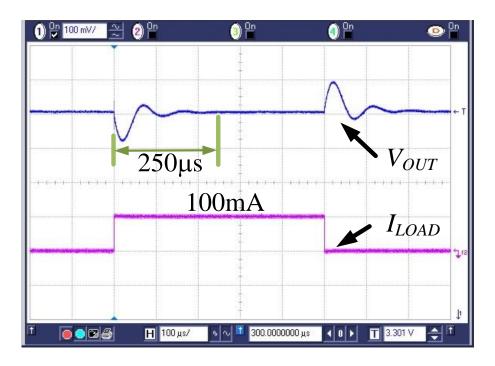

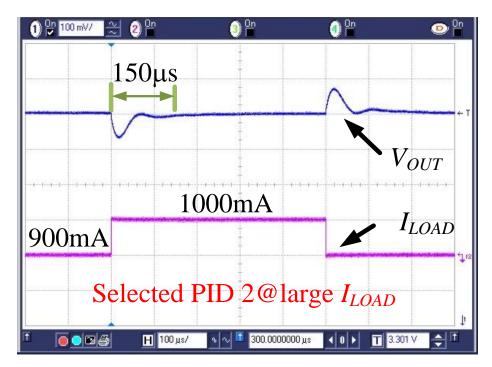

| 5.12.  | Transient Response for PID 1                      |

| 5.13.  | Transient Response for PID 2                      |

| 6.1.   | Digital ACMC DC-DC Buck Converter Architecture    |

| 6.2.   | Hybrid DPWM Architecture Using Mixed-Mode DLL     |

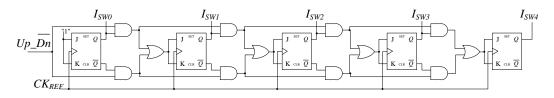

| 6.3.   | Up/Dn Counter in MDLL 100                         |

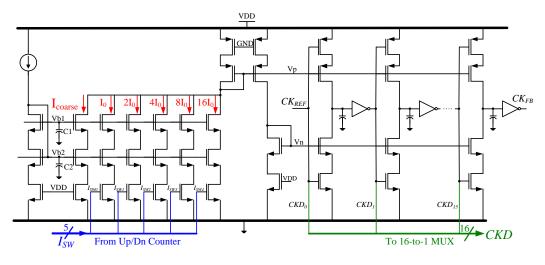

| 6.4.   | Current-Steering DAC Followed by ICDL in MDLL 102 |

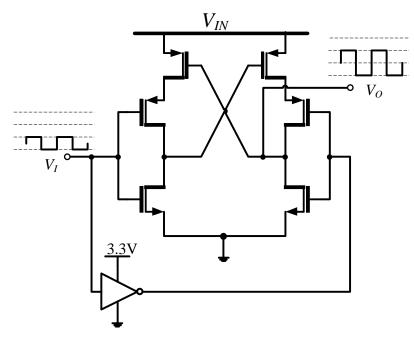

| 6.5.   | Level Shifter                                     |

| 6.6.   | Small Signal Model of Buck Converter 105          |

| 6.7.   | Bode Plot of the Uncompensated Current Loop111    |

| 6.8.   | Bode Plot of the Current Loop Compensator111      |

| 6.9.   | Bode Plot of the Compensated Current Loop112      |

| 6.10.  | Simplified Signal Flow of ACMC Buck Converter     |

| 6.11.  | Bode Plot of the Uncompensated Voltage Loop       |

| 6.12.  | Bode Plot of the Voltage Loop Compensator115      |

| 6.13.  | Bode Plot of the Compensated Voltage Loop         |

| 6.14.  | Digital Implementation of Type-I Compensator      |

| 6.15.  | Digital Implementation of Type-II Compensator     |

# Figure

| 6.16. | Digital Implementation of Type-III Compensator.         | .118 |

|-------|---------------------------------------------------------|------|

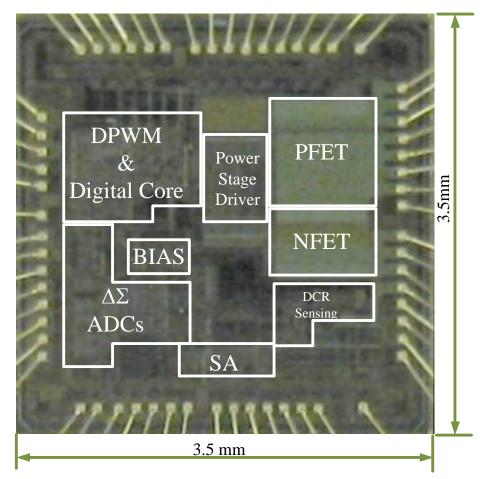

| 7.1.  | Digital ACMC Buck Converter Die Micrograph              | .119 |

| 7.2.  | Digital ACMC Buck Converter Test Board.                 | 120  |

| 7.3.  | Measured Linearity of MDLL Based DPWM.                  | 122  |

| 7.4.  | Average Inductor Current Sensing Performance.           | 123  |

| 7.5.  | Typical Digital ACMC Buck Converter Transient Response. | 124  |

| 7.6.  | Measured Digital ACMC Buck Converter Efficiency.        | 125  |

Page

# CHAPTER 1

# INTRODUCTION

# 1.1 Research Background

## 1.1.1 DC-DC Application

Power supply and Power Management Integrated Circuits (PMICs) have been widely used in Computer, Communication and Consumer (3C) electronics. In recent several years, the market of portable devices such as smartphones and tablets has been increasing rapidly. The annual unit growth rate for portable devices is estimated at more than 12%, from about 2 billion in 2008 to over 3.4 billion devices in 2013 [3]. 3C electronics especially portable devices require a large number of PMICs. This is because each subsystem often requires a specific power supply voltage level, while only one voltage level is available at the battery output. A portable device generally needs 7 to 20 PMICs as shown in Table 1.1. In last several years, the market of PMIC has undergone a strong growth. The market for power supply and power management ICs was US \$2.8 billion back in 1998 and jumped to over \$5.1 billion by the end of 2000 with a compound annual growth rate of 35% [1]. The revenue of PMICs in portable devices alone accounted for more than US \$14 billion in revenues and more than 26 billion units in 2008. This represents nearly 40% of total analog IC revenues and 1/3 of total analog IC units [3]. By 2013, the revenue of PMICs in portable devices alone is estimated to further increase to nearly 1/2 of total analog IC revenues and units (about US\$21 billion and 47 billion units, respectively) [3]. From 2010 to 2015, sales of PMICs will grow at a forecast average rate of 8 percent annually [2][4], reaching \$30.6 billion in total revenue by 2015 [4].

| Portable Device Type               | Typical Number of PMICs |  |

|------------------------------------|-------------------------|--|

| Notebook                           | 20                      |  |

| High multimedia / Smartphone       | 18                      |  |

| MID (Mobile Internet Device)       | 18                      |  |

| Digital still camera               | 18                      |  |

| Global Positioning System (GPS)    | 16                      |  |

| / Portable Navigation Device (PND) |                         |  |

| Digital picture frame              | 15                      |  |

| Portable ultrasound                | 15                      |  |

| Entry / regular phone              | 13                      |  |

| Netbook                            | 13                      |  |

| Portable medical device (Meters)   | 11                      |  |

| Digital media player               | 7                       |  |

| Bluetooth headset                  | 7                       |  |

Table 1.1.

Typical Number of PMICs in Portable Devices [3]

Among various PMICs, voltage regulator is one major product type. There are two major categories of voltage regulators: switching mode DC-DC regulator

and Low Dropout Voltage (LDO) regulator. LDO can provide a relatively low-noise output voltage, and is very suitable for powering noise-sensitive analog and radio frequency circuits such as low-jitter Phase Locked Loops (PLL), Delay Locked Loops (DLL) etc. But LDO can only provide lower voltage output from the input and has relatively low efficiency. The efficiency of LDO is approximately the ratio of the LDO output voltage  $V_{OUT}$  and the input voltage  $V_{IN}$ ,  $V_{OUT}/V_{IN}$ . LDO is therefore very inefficient when the dropout voltage ( $V_{IN}$ - $V_{OUT}$ ) is big. DC-DC regulator, on the other hand, can convert input voltage to either higher or lower voltage, and has better efficiency. The typical efficiency of modern DC-DC is larger than 80% and can be up to 98%. Although DC-DC has higher complexity, and generally higher cost, large ripple than LDO due to the switching nature, it still gains the popularity in battery based portable devices. The scope of this dissertation is only limited to switching mode DC-DC regulators.

#### 1.1.2 Digital Control of DC-DC Converter

DC-DC converter usually requires a loop compensator (also called controller) due to the insufficient DC gain and phase margin of the uncompensated DC-DC system. There are two types of DC-DC control methods: analog control and digital control. In recent years, digital control method in DC-DC converters has been studied by many researchers [5]-[12]. Compared to the traditional analog implementation, digital control method provides several advantages:

- Less susceptibility to PVT, component variations and ambient noise. Analog controller consists of poles and zeros set by resistors and capacitors. It suffers from Process, Voltage and Temperature (PVT) variations as well as component tolerance variation and drift due to ambient noise. A digital controller is able to precisely position poles and zeros and requires fewer components. Thus, the digital control system is more robust and has high tolerance on all kinds of variations.

- 2. Possibility of implementing advanced control schemes. It is much easier to implement advanced control techniques into digital control system. Some of these advanced control scheme, such as high order compensator, are considered impractical or too challenging for analog realization. Moreover, digital control enables programmable compensator. Advanced control schemes and programmability can be used to improve system performances such as dynamic performance, efficiency, stability, etc. Some examples of these advanced control schemes are accomplished in prior work [7]-[10].

- 3. Easiness of integrating with other digital systems. This is particularly attractive for applications where load is in digital implementation as well. In

these scenarios, both PMIC and other functionality chipset can be integrated on the same die or SOC platform. Therefore, it is able to provide a compact and low cost overall solution.

| Characteristics               | Analog Control | Digital Control |

|-------------------------------|----------------|-----------------|

| PVT Variation Tolerance       | No             | Yes             |

| Component Variation Tolerance | No             | Yes             |

| Programmability               | No             | Yes             |

| Advanced Control Algorithms   | No             | Yes             |

| Telemetry                     | No             | Yes             |

| Technology Exploitation       | No             | Yes             |

| System Integration            | No             | Yes             |

| Accuracy                      | High           | Lower           |

| Speed                         | Fast           | Slower          |

| Complexity                    | Low            | Higher          |

Table 1.2. Comparison Between Digital and Analog Control in DC-DC.

A comparison of analog and digital control methods is provided by Table 1.2. Analog control method generally has the advantage of high accuracy, fast speed and lower complexity. The accuracy of digital controlled DC-DC depends on the resolution of the Digital Pulse Width Modulator (DPWM). High resolution DPWM module is required to generate high accuracy DC-DC output voltage. This increases the DC-DC hardware complexity. Also A/D converters are extra demands in digital control method. Thus the hardware cost for digital control is normally higher than that of analog method. In spite of these drawbacks, digital control method is still appealing due to its advantages in robustness, programmability, and easiness of integration.

### 1.1.3 Research Motivation

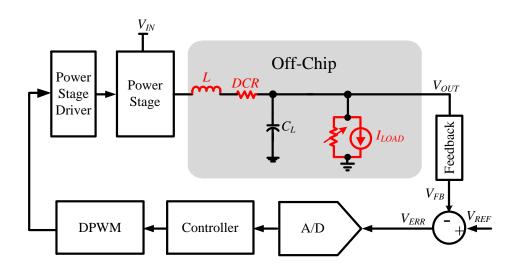

Regardless of the success in commercial applications and intensive research work in academy, switching mode DC-DC still has some issues that are not well addressed. One of the biggest issues is the dynamic performance and stability degradation due to the incognizance of off-chip components and load condition. For a generic DC-DC converter system, such as the digital voltage mode controlled DC-DC buck converter shown in Fig. 1.1, the inductor inductance *L*, DC Resistance (DCR) and load current  $I_{LOAD}$  are in the close loop of DC-DC and their values affect the loop response and stability. However, the inductor is usually off-chip due to the large size (normally  $\mu$ H range) and the load current is application dependent. As the exact information of inductor and load current is not known as a prior knowledge. DC-DC is generally designed around a desired nominal inductor value and specific load current. Unfortunately, inductor usually has large variation which can hurt the system's stability and transient response. In recent years, there is also an increasing interest of using single inductor to drive multiple outputs [13]-[17]. In these Single Inductor Multiple Outputs (SIMO) systems, the impact of inductor variation and potential damage is even more critical. Meanwhile, since the regulator is designed for a specific load current, it's difficult to compensate for a wide load range. Therefore, by monitoring the inductor and load current, we can improve the loop response and enable load independent control [18].

Fig. 1.1. Generic Digitally Controlled Voltage Mode DC-DC Buck Converter.

Load current sensing ability is also one of the most desirable features of contemporary current or voltage mode controlled DC-DC converters. Current sensing can be used for short circuit detection, over current protection, multi-stage converter load balancing, multi-phase converter current sharing, power efficiency improvement, current-mode control etc.

The motivation of this dissertation is to design DC-DC converters with two major features: 1) load inductor inductance and DCR Built-In Self-Test (BIST) functionality using the existing system resource; 2) lossless, continuous and integrated load current sensing ability. Since efficiency is a key requirement in power management systems, all these features are expected to be implemented with low power consumption and small hardware overhead.

# 1.2 Dissertation Outline

The organization of this dissertation is as follows:

Chapter 1 provides a brief introduction of DC-DC converters, explains the existing issues of contemporary DC-DC design methodology. Chapter 2 reviews prior current sensing approaches in DC-DC converters. The essentials of the most commonly used current sensing methods together with their advantages and shortages are discussed. Chapter 3 presents a digital Voltage Mode Controlled (VMC) buck converter core. The overall architecture and details of individual modules are described. In Chapter 4, the proposed inductor BIST and lossless current sensing architecture is presented. The VMC buck converter core together with the BIST and current sensing architectures are designed, fabricated and

experimentally tested. Chapter 5 demonstrates the measurement results of the VMC buck converter. As Average Current Mode Control (ACMC) has gained attention due to its advantages over voltage mode control, a digital ACMC buck converter is proposed in Chapter 6. A hybrid DPWM based on a mixed-mode DLL (MDLL) is proposed. Chapter 7 gives the experimental test results of the digital ACMC buck converter. The last Chapter, Chapter 8, offers a brief summary and a discussion of possible future work.

# CHAPTER 2

#### STATE-OF-THE-ART CURRENT SENSING TECHNIQUES

In DC-DC converters, current sensing has various applications such as over load protection, multi-stage converter load balancing, current-mode control, multi-phase converter current-sharing, mode hop etc. Depending on the application, the current to be measured could be the inductor current  $(I_L)$ , load current  $(I_{LOAD})$ , occasionally even the output capacitor current  $(I_C$ , equals to inductor ripple current). There are handful existing approaches in the field of current sensing. According to the current to be sensed, we can divide these methods into two major categories: instantaneous inductor current sensing and average inductor current sensing ( $I_{LOAD}$  in buck converter). This chapter first reviews state-of-the-art instantaneous inductor current sensing schemes then discusses the existing average inductor current sensing techniques. A summary of these techniques is provided at the end of this chapter. Although there are many existing current sensing schemes, an integratable, continuous, lossless, hardware and power efficient current sensing is still unavailable. The review in this chapter establishes the demand for our current sensing technique which has all the aforementioned features. This technique will be introduced in later chapters.

## 2.1 Instantaneous Inductor Current Sensing

# 2.1.1 External *R*<sub>SENSE</sub>

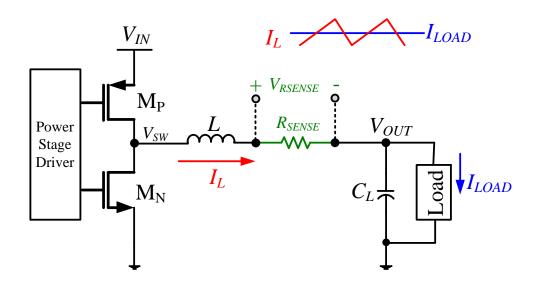

Fig. 2.1. External *R*<sub>SENSE</sub> Current Sensing.

The widely used conventional current sensing method is adding a known sensing resistor  $R_{SENSE}$  in the current path. One can monitor the current by measuring the voltage cross the  $R_{SENSE}$  as shown in Fig. 2.1. Depending on the place to insert  $R_{SENSE}$ , current to be sensed can be the power switch current, the inductor current or the load current. As the  $R_{SENSE}$  value must be precise to obtain accurate current sensing, external sensing resistor is usually used. The accuracy of this method relies on the type of resistor utilized. In the most common implementation, a discrete metallic resistor with zero temperature coefficient is used, either manganin or constantan. The accuracy is just determined by the initial tolerance of the part.

This approach generally has high accuracy but is not lossless. The power loss on  $R_{SENSE}$  results the power efficiency degradation of the DC-DC converter. The situation becomes worse especially in high load current application. A trade off must be done between the power loss and the sensing accuracy. The power loss can be reduced by using smaller  $R_{SENSE}$ . However, when  $R_{SENSE}$  is too small, the voltage across  $R_{SENSE}$  would be in the order of noise level or the sense amplifier offset thereby reducing the sensing accuracy. Meanwhile, an expensive high performance instrument amplifier may be required, which increases overall system cost.

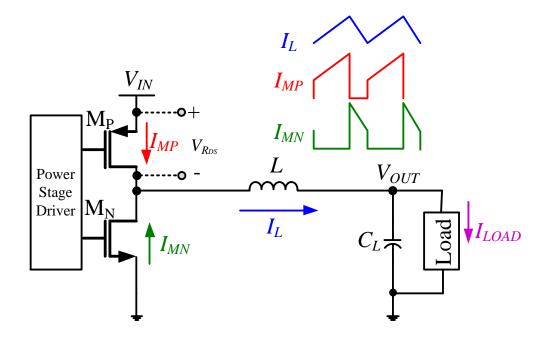

### 2.1.2 Power FET *R*<sub>DS</sub> Sensing

Power MOSFET turned on resistor  $R_{DS}$  can be used as a sensing resistor as shown in Fig. 2.2. When a MOSFET is in triode mode, the  $R_{DS}$  can be approximately expressed as:

$$R_{DS} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}$$

(2-1)

Here  $\mu$  is the mobility,  $C_{OX}$  is the unit area oxide capacitance, L and W are the MOSFET length and width, and  $V_{TH}$  is the transistor threshold voltage. Thus, the

current goes through one power MOSFET can be sensed by monitoring the voltage drop on the power FET.

Fig. 2.2. Power MOSFET *R*<sub>DS</sub> Current Sensing.

This approach is lossless and does not require external components. However, since the  $R_{DS}$  is inherently nonlinear and has significant variations over process, voltage and temperature, it inevitably has low accuracy. Another issue of this approach is that, since only one side MOSFET current is observed, i.e.  $I_{MP}$  or  $I_{MN}$  as shown in Fig. 2.2, it is not able to sense the inductor current through the entire switching period continuously.

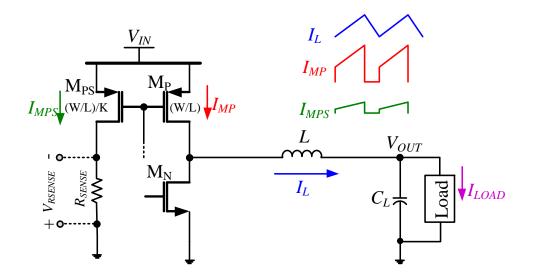

#### 2.1.3 Triode Mode Current Mirroring

Fig. 2.3. Triode Mode Current Mirroring Current Sensing.

The idea of triode mode current mirroring is adding a sense MOSFET in parallel with the power MOSFET through layout matching [19]-[24]. Fig. 2.3 illustrates the triode mode current mirroring current sensing method. By sensing the current goes through the parallel MOSFET, the power MOSFET current can be predicated.

To assure that the current goes to the parallel sensing MOSFET is very small thus the power consumed for current sensing is ignorable, a large 1:K current mirror ratio is normally utilized. The accuracy of the current-sensing circuit decreases since the matching accuracy between the main MOSFET and the sense-FET degrades. The accuracy of the sense-FET technique is about  $\pm 20\%$  in practice. Moreover, the sense-FET technique is sensitive to switching noise during power FETS switching. In addition, for converters with high load currents where the switches are off-chip, the implementation of the technique may not be feasible because of unavailability of discrete sense-FET switches.

# 2.1.4 Hall-effect Sensor

Hall-effect current sensor is one of the most popular magnetic field sensors. This sensor is based on the Hall-effect, which was discovered by Edwin Hall in 1879. There are some CMOS Hall-effect sensors reported in [27]-[31]. The most serious limitation of Hall-effect sensor is the degaussing cycle required after an over current incident [41]. Hall-effect sensor provides a current sensing with low loss and good accuracy, but in general at a very high price.

## 2.1.5 Transformer

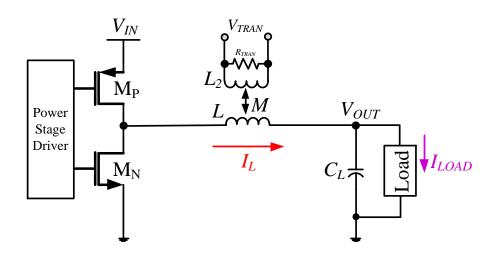

Transformer can be used to sense the current by using the mutual inductor properties [32]. The idea of transformer current sensing is shown in Fig. 2.4. Transformer is typically bulky and not able to be integrated. Also, transformers are normally expensive. Besides, since DC current is not able to transferred, this approach cannot be used for over current protection.

Fig. 2.4. Transformer Current Sensing.

Fig. 2.5. Observer Current Sensing.

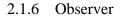

Observer current sensing approach was proposed in [33], the voltage over the power filter inductor is integrated over time to obtain the inductor current as shown in Fig. 2.5. Since the voltage over the inductor  $V_{IND}=L\times di/dt$ , the inductor

current can be obtained by measuring the integrator output. To obtain inductor current, L should be known as a prior knowledge. However, to avoid saturation in the integrator because of the voltage over inductor DCR, the integrator is reset periodically [33], and therefore only AC ripple current is estimated.

### 2.1.7 Inductor DCR Sensing

Inductor DCR current sensing was proposed in [34], an upgraded DCR current sensing approached was also given to deal with the voltage regulators with coupled inductors [35]. The extensive analysis of DCR current sensing can be found in [36][37].

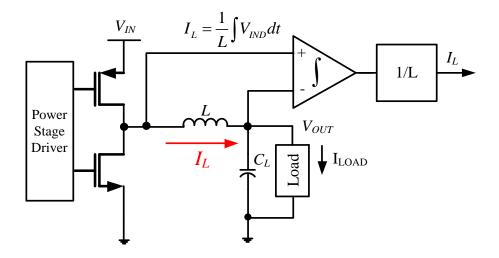

Fig. 2.6. DCR Current Sensing.

The idea of inductor DCR current sensing is illustrated in Fig. 2.6. An RC filter consisting of *Rs* and *Cs* is added between the power stage switching node

$V_{SW}$  and the DC-DC output node  $V_{OUT}$ . The voltage across the inductor (also is the voltage over the two terminals of RC filter) is:

$$V_{IND} = (sL + R_{DCR})I_L \tag{2-2}$$

We can obtain the voltage over the capacitor Cs by

$$V_{Cs} = V_{IND} \times \frac{\frac{1}{sC_s}}{R_s + \frac{1}{sC_s}}$$

=  $(sL + R_{DCR}) \times \frac{1}{1 + sR_sC_s} \times I_L$  (2-3)

=  $\left(\frac{1 + s\frac{L}{R_{DCR}}}{1 + sR_sC_s}\right) \times R_{DCR} \times I_L$

From equation (2-3) we can notice that, if Rs and Cs are selected such that the pole formed Rs and Cs cancels the zero formed by L and  $R_{DCR}$ , i.e.

$$R_S C_S = \frac{L}{R_{DCR}} \tag{2-4}$$

then we have:

$$V_{Cs} = R_{DCR} \times I_L \tag{2-5}$$

Thus we can sense the inductor current from the voltage over capacitor  $C_s$ . Apparently *L* and  $R_{DCR}$  need to be known first, and *Rs* and *Cs* are then chosen accordingly. In industry practice, a thermistor is often used in this current sensing method to compensate for the temperature drift of the inductor DCR.

# 2.1.8 Gm-C Filter

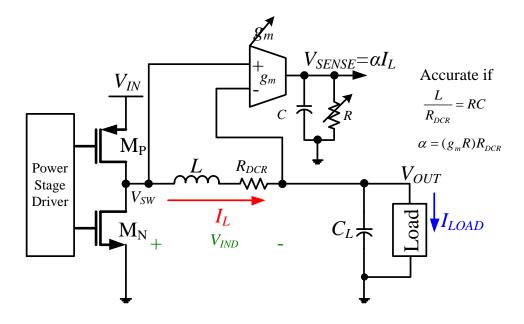

Fig. 2.7. Gm-C Filter Based Current Sensing.

One of the latest and representative current sensing approaches is the Gm-C filter based technique proposed in [40]. The idea of this technique is illustrated in Fig. 2.7. A transconductor Gm block is added to convert the voltage over the inductor into current, which goes through a shunt RC network. As the voltage over the inductor is:

$$V_{IND} = (sL + R_{DCR})I_L \tag{2-6}$$

We could therefore acquire the sensed voltage at the output of Gm block by

$$V_{SENSE} = g_m \times V_{IND} \times \left( R \parallel \frac{1}{sC} \right)$$

=  $g_m \times (sL + R_{DCR}) \times I_L \times \left( \frac{R}{1 + sRC} \right)$

=  $g_m \times R \times \left( \frac{1 + s \frac{L}{R_{DCR}}}{1 + sRC} \right) \times R_{DCR} \times I_L$  (2-7)

If we could tune *R* so that

$$RC = \frac{L}{R_{DCR}}$$

(2-8)

then sensing voltage  $V_{SENSE}$  becomes

$$V_{SENSE} = g_m \times R \times R_{DCR} \times I_L$$

(2-9)

Especially, if  $g_m$  can be tuned such that

$$g_m \times R \times R_{DCR} = \alpha \tag{2-10}$$

where  $\alpha$  is a known constant, then  $V_{SENSE}$  becomes

$$V_{\text{SENSE}} = \alpha \times I_L \tag{2-11}$$

Gm-C filter approach requires both inductance L and DCR information, such that the resistor R can be tuned. In [40], an inductor measurement circuit performs the test of L and DCR upon start-up.

Gm-C filter current sensing is an accurate analog technique, but the transconductor and RC filter R require tuning and calibration. Also, the Gm block's offset is cancelled in analog domain, it demands two identical units. The

offset is cancelled by configuring the two units in ping-pong style. The analog calibration and offset cancellation make Gm-C filter current sensing very complex and hardware costly.

## 2.2 Average Inductor Current Sensing

Average inductor current needs to be sensed in some applications. To obtain the average inductor current, one can use a designated sensing technique to sense the average current directly, or sense the instantaneous inductor current first and then do averaging or prediction based on the instantaneous inductor current. All these methods are reviewed in this section.

## 2.2.1 Average Current Sensing

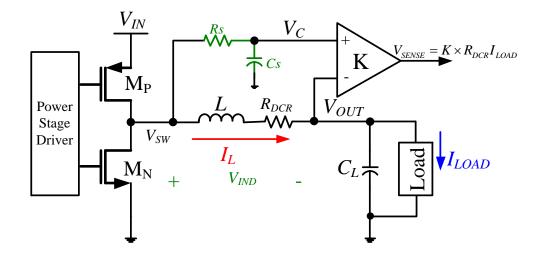

Average current sensing was proposed in [55]. This method is similar to the inductor DCR sensing technique introduced in section 2.1.7. In inductor DCR sensing technique, the RC filter consisting of Rs and Cs is added between the two nodes of inductor. Here in average current sensing technique, the RC low pass filter is added to the DC-DC switching node  $V_{SW}$  and ground. The architecture of the average current sensing method is shown in Fig. 2.8.

When applying an ideal LC filter to the switching node  $V_{SW}$ , the DC signal of the output of the filter (here is the output voltage  $V_{OUT}$ ) is the average of  $V_{SW}$ . Similarly, when applying an RC filter, the DC signal of the output of the filter (here is the capacitor voltage  $V_C$ ) is the average of  $V_{SW}$  as well. The difference of the  $V_{OUT}$  and  $V_C$  is due to the existence of inductor DCR. Thus we have:

$$\bar{V}_C - \bar{V}_{OUT} = R_{DCR} \times I_{LOAD}$$

(2-12)

Hence, we could sense the average inductor current by monitoring the voltage different of  $V_{OUT}$  and  $V_C$ .

Fig. 2.8. Average Current Sensing.

Since  $V_{SW}$  is being switched between  $V_{IN}$  and ground at the switching frequency, ( $V_C$ - $V_{OUT}$ ) has a large AC signal component riding on top of the desired  $R_{DCR} \times I_{LOAD}$  information. This AC signal must be filtered out to obtain the current signal. There is going to be a tradeoff between accuracy and RC filter bandwidth. If the bandwidth is too low, the signal will not be useful either for loop control or for current limiting.

## 2.2.2 Averaging Filter

An intuitive method to obtain average current is to capture multiple instantaneous current samples within one period and then take the average operation. As this method needs to store the sampled current value at multiple time instances, it is more suitable for digital implementation. The average operation realization is adding an averaging filter:

$$F_{AVG}(z) = \frac{1}{N} \sum_{i=0}^{i=N-1} z^{-i}$$

(2-13)

Averaging filter provides very high attenuation for the first several harmonics of the switching frequency and significantly removes the effects of the switching noise from the computed average value. For better DSP implementation, an approximation of this averaging filter by using Bessel filter is proposed in [11] where this filter approximates the averaging filter response very well up to one-half of the switching frequency.

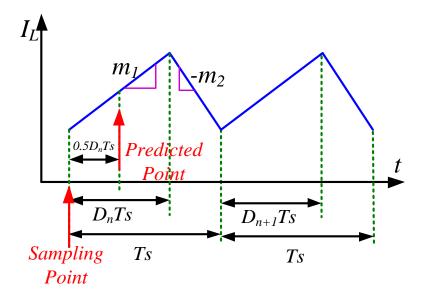

## 2.2.3 Geometric Relation Based Predication

Geometric relation based predication method is another method to obtain the average inductor current. It was first proposed in [12]. Compared to the averaging filter method, this approach just needs to sample once at the peak or valley inductor current instance. The idea of this approach is shown in Fig. 2.9.

Fig. 2.9. Geometric Relation Based Predication.

The inductor current is DC-DC has a triangular waveform shape. The slopes of the rising and falling parts are determined by the DC-DC input voltage  $V_{IN}$ , output voltage  $V_{OUT}$ , and the inductor *L*. The slopes of the inductor current waveforms for basic converters are provided in Table 2.1.

Table 2.1.

Slopes of the Inductor Current Waveform.

| Buck Converter       | $m_1 = \frac{V_{IN} - V_{OUT}}{L}$ | $-m_2 = -\frac{V_{OUT}}{L}$          |

|----------------------|------------------------------------|--------------------------------------|

| Boost converter      | $m_1 = \frac{V_{IN}}{L}$           | $-m_2 = -\frac{V_{IN} - V_{OUT}}{L}$ |

| Buck-boost Converter | $m_1 = \frac{V_{IN}}{L}$           | $-m_2 = \frac{V_{OUT}}{L}$           |

If we could detect  $V_{IN}$ ,  $V_{OUT}$ , and L, we would be able to obtain the inductor current waveform slopes. As the duty cycle D is normally known by the DC-DC, the average inductor can be predicated based on the current slope and the valley or peak inductor current as shown in Fig. 2.9. This predication method needs to monitor both input voltage and output voltage, the inductor must be known as a prior knowledge too.

## 2.3 Summary of Current Sensing Techniques

Table 2.2 summaries all the aforementioned current sensing techniques. For more information of current sensing, one could refer to comprehensive current sensing technique reviews given by [36][38][39][41]. As modern high performance DC-DC converter may exploit the current information for all kinds of applications, an integrated, lossless, accurate, hardware and power efficient current-sensing technique is required for state-of-the-art switching regulators. Although we have many available current sensing techniques as shown in Table 2.2, each one has one or more issues that prevent them from being successfully applied in DC-DC converter, e.g. low accuracy, discontinuous sensing nature, high sensitivity to switching noise, high cost, requirement of known external power filter components, bulky size, etc. The current sensing solution proposed in this dissertation has all required features for high performance DC-DC regulators.

The detailed implementation is discussed in the following chapters.

-

\_

|                                        | Techniques                              | Pros                  | Cons                                                                  |

|----------------------------------------|-----------------------------------------|-----------------------|-----------------------------------------------------------------------|

| Current Sensing                        | External R <sub>SENSE</sub>             | Accurate              | Low Efficiency                                                        |

|                                        | Power FET <i>R</i> <sub>DS</sub>        | Lossless              | Low Accuracy<br>Discontinuous<br>Noisy                                |

|                                        | Triode Mode<br>Current Mirroring        | Lossless              | Matching Issue<br>Only for On-Chip Switches<br>Discontinuous<br>Noisy |

| luctor                                 | Hall-effect Sensor                      | Lossless              | High Cost                                                             |

| Instantaneous Inductor Current Sensing | Transformer                             | Lossless              | High Cost<br>Bulky, not Integratable<br>No DC Current Information     |

|                                        | Observer                                | Lossless              | Known <i>L</i><br>Need Discrete Components                            |

|                                        | Inductor DCR Sensing                    | Lossless              | Known <i>L</i> and <i>DCR</i>                                         |

|                                        | Gm-C Filter                             | Lossless              | Known <i>L</i> and <i>DCR</i><br>Hardware Costly                      |

| Average Inductor<br>Current Sensing    | Average Current<br>Sensing              | Lossless              | Known DCR                                                             |

|                                        | Averaging Filter                        | Low<br>complexity     | Needs Multiple<br>Current Samples                                     |

|                                        | Geometric Relation<br>Based Predication | Needs only one sample | Known V <sub>IN</sub> , V <sub>OUT</sub> , L                          |

Table 2.2.

Summary of Conventional Current Sensing Techniques

## CHAPTER 3

# DIGITAL VMC BUCK CONVERTER CORE

The goal of this dissertation is to design DC-DC converters with inductor BIST and load current sensing abilities. Before implementing these two major features, a DC-DC converter needs to be designed at first to work as a platform. In this chapter, a digital Voltage Mode Controlled (VMC) DC-DC buck converter core is proposed with the detailed module implementation elaborated.

3.1 Digital VMC Buck Converter Core Architecture Overview

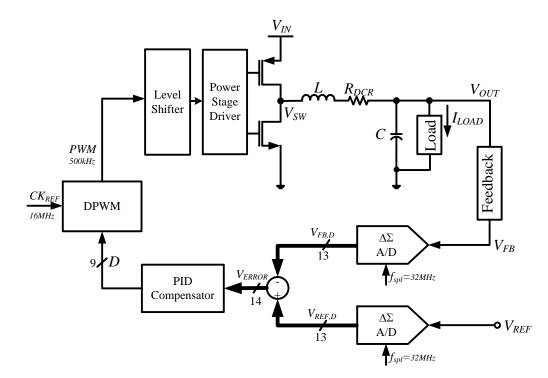

Fig. 3.1. Digitally Controlled Buck Converter Architecture.

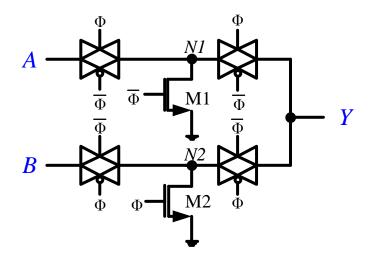

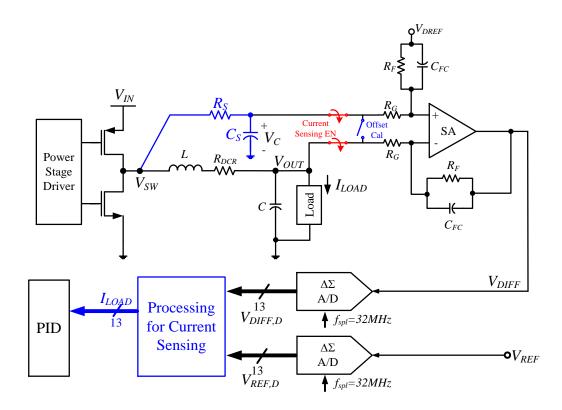

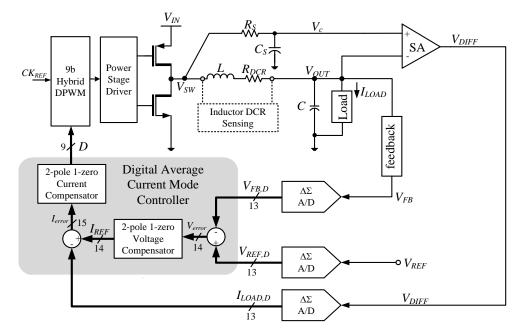

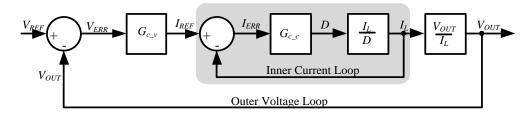

The proposed overall digital VMC buck converter core architecture is shown in Fig. 3.1. The operation of this buck converter regulation is as follows: two  $\Delta\Sigma$  A/D converters are used to digitize the DC-DC feedback voltage  $V_{FB}$  and the reference voltage  $V_{REF}$ . The error signal of the digitized feedback voltage  $V_{FB,D}$  and the digitized reference voltage  $V_{REF,D}$  is applied to the Proportional Integral Derivative (PID) compensator. The PID compensator calculates the required duty cycle D. The Digital Pulse Width Modulator (DPWM) converts this duty cycle requirement into a Pulse Width Modulation (PWM) signal and sends it to the level shifter. The level shifter's output then drives the power MOSFTES via a built in dead-time controlled gate driver. When feedback voltage and reference voltage are equal, error  $V_{ERROR}$  will be equal to zero. This DC-DC is designed with a close loop system crossover frequency 50kHz while PWM switching frequency is 500kHz.

## 3.2 Digital VMC Buck Converter Core Implementation

The digital DC-DC buck converter core architecture contains several critical blocks such as A/D converter, DPWM, power stage driver, PID compensator. This section explains all the major blocks used in the proposed digital VMC buck converter core architecture in details.

## 3.2.1 DPWM

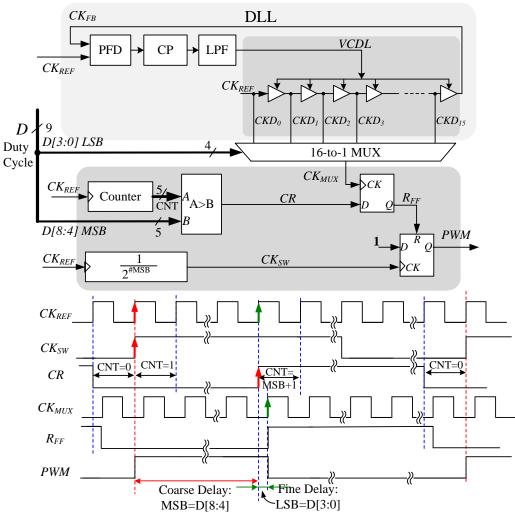

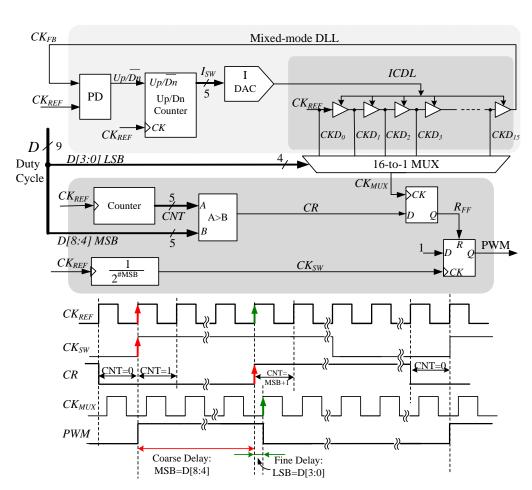

A 9bits hybrid DPWM is utilized to generate the pulse signal, where a 5bits digital counter controls the 5bits Most Significant Bits (MSBs) coarse part, and a

Type-I 4bits Delay Lock Loop (DLL) controls the Least Significant Bits (LSBs) fine delay part. The overall architecture of DPWM and its corresponding operation waveform is shown in Fig. 3.2. The detailed operation of the DPWM is as follows:

A  $1/2^{\#MSB}$  (#MSB is the number of MSBs bits) ratio frequency divider takes the reference clock 16MHz  $CK_{REF}$  and generates switching clock signal  $CK_{SW}$ .  $CK_{SW}$  runs at DC-DC switching frequency 500kHz. The rising edge of  $CK_{SW}$ works as the rising edge of the PWM signal.

Meanwhile, a 5bits counter running at  $CK_{REF}$  followed by a 5bit comparator generates the coarse part ready signal *CR*. After releasing from the reset, counter starts to count the number of  $CK_{REF}$  cycles. Once it reaches the PID MSBs code, the comparator set the *CR* to logic high. The delay from the rising edge of  $CK_{SW}$ to rising edge of *CR* is the coarse delay part of PWM.

In parallel with frequency divider and digital counter, a locked DLL generates 16-tap delay outputs of  $CK_{REF}$ . A multiplexer selects one of the DLL output  $CK_{MUX}$  based on the 4b LSBs of PID Code. The delay between  $CK_{MUX}$  and  $CK_{REF}$ is the fine delay part.  $CK_{MUX}$  is used to sample the coarse part ready signal CR, once CR=1, the delay between  $CK_{MUX}$  and CR is the fine delay part as well. The PWM high width is then determined by combining the coarse part and fine part,

i.e. from rising edge of  $CK_{SW}$  to the rising edge of  $CK_{MUX}$  right after CR=1.

Fig. 3.2. DPWM Architecture and Operation Waveform.

There are two types of conventional DPWM implementation methods: digital counter based DPWM or analog circuits (such as DLL) based DPWM. Digital counter based DPWM needs to run at  $f_{clk}=2^n \times f_s$ . Here *n* is DPWM resolution and  $f_s$  is the switching frequency.  $f_s$  needs to be balanced between the requirement of smaller off-chip inductor (the bigger  $f_s$  the better) and the requirement of lower switching power loss (the smaller  $f_s$  the better). Typical  $f_s$  is from ~100kHz order to ~10MHz order. DPWM resolution *n* is determined by the DC-DC output voltage control resolution, e.g. to achieve 0.1% DC voltage error, a 10bits DPWM is needed such that  $1/2^{10} < 0.1\%$ . According to these conditions, the DPWM clock  $f_{clk}$  can be up to ~GHz or higher frequency which incurs significant digital circuits switching power loss.

All analog implementation solution such as DLL based DPWM requires 2<sup>n</sup> DLL delay stages, which is both power and hardware costly.

In this work, by using hybrid structure, i.e., digital counter for the coarse delay part and DLL for the fine delay part, we could reduce digital clock frequency from  $f_{clk}=2^n \times f_s$  to  $f_{clk}=2^{MSBs} \times f_s$  and decrease the DLL delay stages from  $2^n$  to  $2^{\#LSB}$ . Therefore, both digital circuits and DLL can have low power consumption and small chip area.

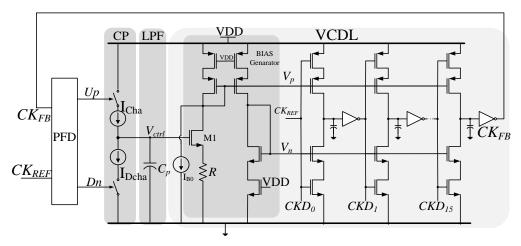

## 3.2.1.1 DLL Overall Architecture

The core circuit of DPWM is the DLL shown in Fig. 3.3. It consists of a Phase Frequency Detector (PFD), a Charge-Pump (CP), a Low Pass Filter (LPF) and a Voltage Controlled Delay Line (VCDL). The PFD compares the feedback clock signal  $CK_{FB}$  and the reference clock  $CK_{REF}$ , then generates up and down

signals. Up and down signals are used to control the LPF capacitor charge and discharge time. VCDL generates 16-tap delay output. The delay of each tap is controlled by the voltage over the capacitor (*Vctrl*). When the  $CK_{FB}$  and  $CK_{REF}$  are aligned, PFD produces identical up and down signal, thereby the capacitor voltage *Vctrl* maintains the same and DLL is locked.

Fig. 3.3. DLL Architecture.

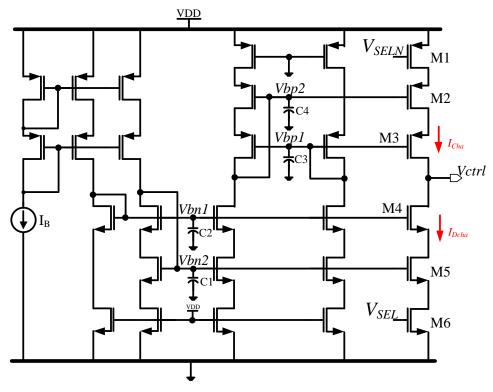

## 3.2.1.2 Charge Pump

A low jitter DLL is a critical requirement for a high precision DPWM. The jitter of DLL is caused by many reasons such as power supply and ground noise, mismatch in charge pump etc. Low jitter DLL therefore demands a charge pump with high supply and ground immunity and high precision matching between the charge and discharge current biases.

The charge pump of DLL in this work is shown in Fig. 3.4. It was originally proposed in [42]. To obtain better matching of the charge current  $I_{Cha}$  and the

discharge current *I*<sub>Dcha</sub>, wide-swing current mirrors are adopted in both PMOS and NMOS sides. The charge and discharge control switch M1 and M6 are placed to the source side of the current mirror transistors. Thus the switching noise of M1 and M6 can be isolated by two cascaded bias transistors (M2, M3 or M4, M5 in Fig. 3.4). Moreover, four bypass capacitors C1, C2, C3 and C4 are also connected to bias voltage nodes to stabilize the current biases and absorb switching noise.

Fig. 3.4. Charge Pump in DLL.

The power supply and ground noise are isolated by cascaded transistors M1 to M6, and further suppressed by the bypass capacitors as well. By using all these techniques, this charge pump is not susceptible to switching and power supply

noise, and has highly matched charge and discharged current biases, eventually makes low jitter DLL practical.

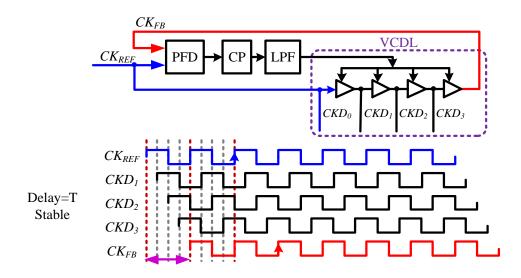

### 3.2.1.3 Delay Stage

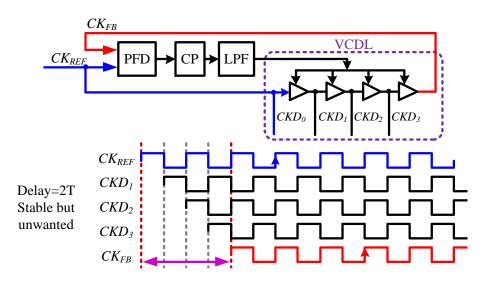

DLL has a well-known issue of being locked at multiple reference clock periods, which comes with its nature. DLL is designed to be locked when the delay from the reference clock  $CK_{REF}$  to the feedback clock  $CK_{FB}$  is just one period of  $CK_{REF}$ . However, DLL can also be locked when the delay from  $CK_{REF}$  to  $CK_{FB}$  is multiple periods of  $CK_{REF}$ .

Fig. 3.5. Waveforms of DLL at Normal Lock Status (Delay=T).

Fig. 3.5 shows the waveforms of a 4-tap DLL when it is locked at the desired delay, i.e. delay=T (T is the period of  $CK_{REF}$ ). In this scenario, each delay stage has a delay of T/4. The rising edges of  $CK_{REF}$  and  $CK_{FB}$  are aligned. DLL is locked as desired. However, when the delay=nT (n>1 is an integer), DLL is

locked as well. Shown in Fig. 3.6 is a case of delay=2T. Each delay stage has a delay of T/2 rather than the desired T/4. The rising edges of  $CK_{REF}$  and  $CK_{FB}$  are still aligned. PFD produces identical up and down signal, the cap voltage *Vctrl* maintains the same and DLL is locked falsely.

Fig. 3.6. Waveforms of DLL at Multiple-Period-Lock Status (Delay=2T).

Fig. 3.7. Waveforms of DLL at Half Period Delay Status (Delay=T/2).

DLL does not have issue when delay=T/n. A delay=T/2 example is shown in Fig. 3.7. As  $CK_{REF}$  and  $CK_{FB}$  do not arrive at the same time, PFD detects the difference and adjusts the LPF cap through CP, DLL is not locked in this case.

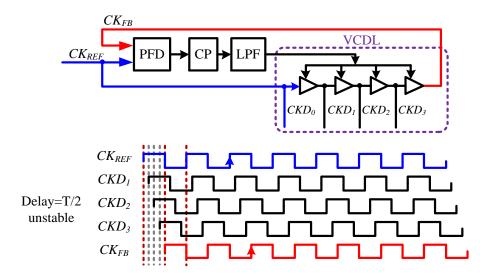

To avoid multiple-period-lock status, the tuning rage of the delay cell must be properly designed. As long as the delay of VCDL does not reach 2T or higher value for all VCDL control voltage *Vctrl* range, the multiple period lock issue will not exist. In our design, DLL has 4bits resolution, i.e. 16 stages VCDL. The reference clock  $CK_{REF}$  is 16MHz. When DLL is locked, the delay of each stage is:

$$Delay_{1stage} = \frac{1}{f_{CK_{RFF}}} \times \frac{1}{2^{\#LSB}} = \frac{1}{16M} \times \frac{1}{16} \approx 3.91n$$

(3-1)

As shown in Fig. 3.3, when the VCDL input voltage *Vctrl* rises from 0 to M1 threshold voltage  $V_{TH}$ , M1 is not turned on. Bias generator is only proved by bias  $I_{B0}$ . After  $V_{TH}$ , as *Vctrl* rises, the current goes to M1 increases, the delay of VCDL stages increase accordingly. When *Vctrl* reaches the power supply  $V_{DD}$ , the current replicas have the largest current and DLL has the minimum delay. The typical DLL delay line delay versus *Vctrl* curve is something like Fig. 3.8.

To avoid multiple-period-lock issue, the maximum delay of each stage for the entire *Vctrl* range is set to be 7.2ns at typical process and room temperature, which is less than 2 times of 3.91ns. 7.2ns is selected in a way that the maximum delay of the VCDL is less than 2 times of 3.91ns for all other process and temperature corners as well.

Fig. 3.8. DLL VCDL Delay vs Vctrl.

The *Vctrl* voltage at DLL lock status (typical 1.4V) is picked in a way that delay line has the same tuning range around the lock point, e.g, 3.3ns above or below the desired 3.91ns in this work as shown in Fig. 3.8.

## 3.2.2 ΔΣ ADC

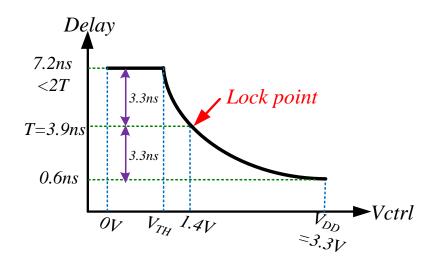

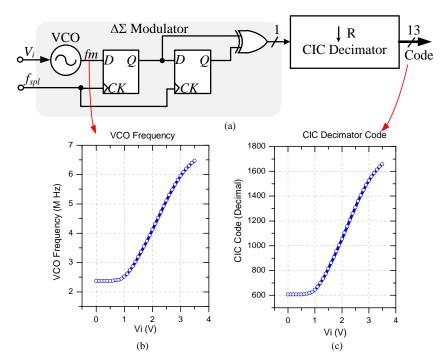

A/D Converters (ADCs) are required in digitally controlled DC-DC converters to digitize the DC-DC feedback voltage, reference voltages etc. Frequency domain  $\Delta\Sigma$ ADCs are utilized in our DC-DC converter feedback path. The ADC is composed of a non-feedback  $\Delta\Sigma$  modulator and a Cascaded Integrator-Comb (CIC) decimator as shown in Fig. 3.9.

Fig. 3.9.  $\Delta\Sigma$  ADC Architecture.

## 3.2.2.1 $\Delta\Sigma$ Modulator

The first-order  $\Delta\Sigma$  modulator is a Voltage Controlled Oscillator (VCO) followed by a  $\Delta\Sigma$  frequency discriminator ( $\Delta\Sigma$ FD).  $\Delta\Sigma$ FD consists of two D flip-flops and an XOR gate. The frequency domain  $\Delta\Sigma$  modulator was proposed in [43][44][45] and firstly used in DC-DC buck converter in [5].

The input of the  $\Delta\Sigma$  modulator is the voltage signal  $V_i$ .  $V_i$  is converted to a Frequency Modulation (FM) modulated signal  $f_m(t)$  after voltage-to-frequency conversion by VCO. An FM modulated signal can be described as:

$$fm(t) = \sin\left[\theta(t)\right] \tag{3-2}$$

where the total angle is given by

$$\theta(t) = 2\pi \int_{-\infty}^{t} [f_c + k \cdot x(\tau)] d\tau \qquad (3-3)$$

Here  $f_c$  is the FM carrier frequency, k is the frequency sensitivity of the modulator and  $x(\tau)$  is the modulating signal. The instantaneous frequency is equal to the derivative of the phase and is defined as:

$$f_{ins}(t) = \frac{1}{2\pi} \frac{d\theta(t)}{dt} = f_c + k \cdot x(\tau)$$

(3-4)

$\Delta\Sigma$ FD digitizes the deviation of  $f_{ins}(t)$  from its carrier frequency  $f_c$  with high pass quantization noise shaping similar to the traditional  $\Delta\Sigma$  modulator. The output of this  $\Delta\Sigma$  modulator is a stream of ones and zeros.

This non-feedback  $\Delta\Sigma$  modulator is equivalent to the traditional  $\Delta\Sigma$  modulator because it performs the same three main functions on a signal similar to the traditional modulator: integration, quantization and differentiation. The integration is achieved by the VCO, i.e. FM modulator; the quantization is accomplished via the detection of the FM phase zero-crossings position utilizing D flip flops, and the differentiation is done by the digital differentiator gate (XOR).

In terms of pattern noise, the first-order frequency  $\Delta\Sigma$  modulator is equivalent to a traditional  $\Delta\Sigma$  modulator as well. Simulation in [45] has found exact match between the pattern noise model introduced by Candy and Benjamin [46] and the pattern noise behavior of the frequency  $\Delta\Sigma$  modulator for constant inputs signals. In [45][47], it is pointed out that the first-order frequency  $\Delta\Sigma$  modulator shows 20dB/decade noise shaping ability as that of the conventional first-order  $\Delta\Sigma$  modulator.

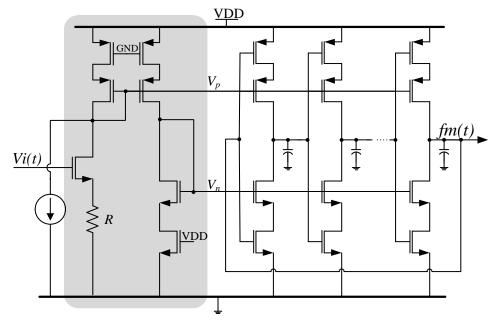

Fig. 3.10. VCO in  $\Delta\Sigma$  Modulator.

The most challenging module in frequency  $\Delta\Sigma$  Modulator is the FM modulator, i.e. the VCO. The VCO in  $\Delta\Sigma$  modulator in this work uses a similar structure as that in DLL for easiness of implementation. The architecture of VCO is shown in Fig. 3.10. One big difference is that: each delay stage in DLL produces the delay of the input clock while each ring oscillator stage in VCO produces the inverted phase of the input clock.

## 3.2.2.2 CIC Decimator

The noise shaped  $\Delta\Sigma$  modulator output signal is decimated by using CIC filter. Decimation is an important component of  $\Delta\Sigma$ ADC. It transforms the

digitally modulated signal from short words occurring at high sampling rate to longer words at a rate close to Nyquist rate. This reduction in the bit rate makes the data more suitable for processing.

An efficient way of performing decimation and interpolation was introduced in [48]. It is a flexible, multiplier-free filter which is suitable for hardware implementation. It also can handle arbitrary and large rate changes. This filter is known as Cascaded Integrator Comb (CIC) filter. An overview of CIC filter can also be found in [49] and an extension of CIC filters is available in [50].

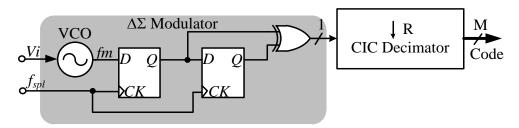

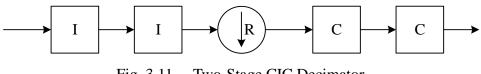

An N-stage CIC decimator has N cascaded integrator stages clocked at sampling frequency  $f_{spl}$ , followed by a rate change of factor *R*, and then followed by N cascaded comb stages running at  $f_{spl}/R$ . A two-stage CIC decimator example is provided in Fig. 3.11.

Fig. 3.11. Two-Stage CIC Decimator.

In CIC decimator, an integrator stage is simply a single-pole IIR filter with a unit feedback coefficient: y[n]=y[n-1]+x[n]. The corresponding transfer function of this integrator (accumulator) can be described as

$$H_I(z) = \frac{1}{1 - z^{-1}} \tag{3-5}$$

A comb filter is an odd-symmetric FIR filter described by: y[n]=x[n]+x[n-RM]. *M* is the *differential delay* and can be any integer but usually limited to1 or 2. *R* is the rate reduction factor. The corresponding transfer unction of a comb filter stage can be described as

$$H_C(z) = 1 - z^{-RM}$$

(3-6)

Thus, the system function for the CIC filter referenced to the high sampling rate  $f_{spl}$  is:

$$H(z) = H_{I}^{N}(z)H_{C}^{N}(z) = \frac{\left(1 - z^{-RM}\right)^{N}}{\left(1 - z^{-1}\right)^{N}} = \left(\sum_{k=0}^{RM-1} z^{-k}\right)^{N}$$

(3-7)

CIC filters have a low-pass frequency characteristic. The frequency response is given by (3-7) evaluated at

$$z = e^{j(2\pi\hat{f}/R)} \tag{3-8}$$

where  $\hat{f}$  is the frequency relative to the low sampling rate  $f_{spl}/R$ . By using mathematical approximations, we could obtain the magnitude response at the output of the CIC decimator:

$$\left|H(\hat{f})\right| \approx \left|RM\frac{\sin(\pi M\hat{f})}{\pi M\hat{f}}\right|^{N} \text{ for } 0 \le \hat{f} \le \frac{1}{M}$$

(3-9)

From (3-9), we notice that CIC filter has transmission zeros at  $\hat{f}/M$ . Thus, the differential delay *M* can be used as a design parameter to control the placement of

nulls. The DC gain of the CIC filter is  $(RM)^N$ . The bigger the decimator is, the larger the number of CIC filter stages, the bigger CIC filter DC gain is.

In our design, a two-stage CIC filter is used as a decimator. The differential delay M is picked as 1. The sampling frequency of CIC filter  $f_{spl}$  is 32MHz. CIC decimator output, PID compensator and DPWM share the same date rate, i.e. DC-DC switching frequency. This can be expressed as:

$$f_s = \frac{f_{spl}}{R} \tag{3-10}$$

Since the DC-DC switching frequency  $f_s$  is 500kHz, the decimation ratio R is therefore selected to be 32MHz/500kHz=64.

As the CIC filter's gain is  $(RM)^N$ , we can then calculate the number of bits required for the last comb stage due to bit growth. If  $B_{in}$  is the number of input bits, then the number of output bits,  $B_{out}$ , is

$$B_{out} = \left[ N \log_2(RM) + B_{in} \right]$$

(3-11)

Here operation [] denotes taking the upper rounded integer value of the argument. (3-11) is a guide to implement CIC decimator. A practical implementation normally uses  $B_{out}$  bits for each integrator and comb stage. The input is often sign extended to  $B_{out}$  bits and LSBs are either be truncated or rounded at later stages.

## 3.2.2.3 ADC Resolution

To satisfy specifications for the output voltage regulation, resolution of the ADC converter has to enable error that is lower than the allowed variation of the output voltage ( $\Delta V_{OUT}$ ) [52]. The required resolution is described as:

$$n_{ADC} = \operatorname{int}\left[\log_2\left(\frac{V_{\max,ADC}}{V_{REF}} \cdot \frac{V_{OUT}}{\Delta V_{OUT}}\right)\right]$$

(3-12)

where  $n_{ADC}$  represents the ADC resolution, i.e. the number of output bits of the ADC converter,  $V_{REF}$  is the reference voltage and  $V_{max,ADC}$  is the full range voltage of the ADC assuming unipolar conversion in the range from 0 to  $V_{max,AD}$ . Operation int[] denotes taking the upper rounded integer value of the argument. Equation (3-12) gives the minimum number of bits for the A/D converter to meet the design specifications in terms of the output voltage regulation. In our design, 8-bit ADC is used in design to enable less than 0.5% output voltage variation control.

The theoretical resolution of the single D flip-flop  $\Delta\Sigma$  Modulator is:

$$SQNR = 20\log_{10}\left(\frac{3}{2\pi}\right) + 20\log_{10}\left(\frac{\Delta f}{f_{bw}^{1.5}}\right) + 10\log_{10}\left(f_{spl}\right)$$

(3-13)

where  $\Delta f$  is the maximum deviation of the FM-signal,  $f_{bw}$  is the bandwidth of the modulating signal while  $f_{spl}$  is the sampling clock frequency. In our system,  $f_{bw}$  is equal to the loop bandwidth which is limited to crossover frequency of 50kHz.

Equation (3-13) makes it easy to adjust the SQNR by simply changing the sampling clock frequency and the sensitivity of the FM modulator taking into account the effect of  $\Delta f$  on the linearity of the FM modulator.

In digitally controlled PWM converters, there is a potential issue called limit cycling. When limit cycling happens, the DC-DC output shows steady state oscillations. To avoid limit cycling, several conditions must be met as analyzed in [45]. One of them is that the DPWM must have higher resolutions than ADC. In our design, since the ADC has 8 bits resolution, we use a 9bits DPWM as discussed in section 3.2.1 to avoid limit cycling.

## 3.2.3 PID Compensator

The PID compensator is used to compensate the loop such that the system is stable with sufficient phase margin under the specified range of input voltage and load condition. At the system level, there are two main approaches in designing the digital control loop: digital redesign and direct digital design. In the digital redesign approach, the designer uses the well-understood method of feedback analysis and well-established results in analog domain and then uses a standard method of translation between analog and digital domains (such as bilinear transformation). In the direct digital design, the system is converted to a sampled discrete system because of the switching action. Every block is treated as a digital block including the power stage. This method may generate more accurate results than the digital redesign but it is more complex due to lack of resemblance to analog design techniques. In this work, the digital redesign approach is used.

A well-established analog PID compensator design method is provided in [56]. Our design procedure is based on this method. The PID compensator is observed to be a product of Proportional Derivative (PD) and Proportional Integral (PI) compensators. That is, the PID compensator is a PD compensator in series with a PI compensator. So, the approach to the design of the PID compensator in this work is to design the PD and PI parts sequentially.

#### 3.2.3.1 Uncompensated Loop

The open-loop control-to-output transfer function for DC-DC buck converter is given by

$$G_{vd}(s) = \frac{V_{OUT}}{D} \frac{1}{1 + s\frac{L}{R_L} + s^2 LC}$$

(3-14)

where  $R_L$  is the equivalent load resistance, L and C are power LC filter inductor and capacitor. Here the DCR of inductor and Equivalent Series Resistance (ESR) of capacitor are not considered. The open loop transfer function has two poles and therefore can also be expressed as

$$G_{vd}(s) = G_{d0} \frac{1}{1 + \frac{s}{Q_0 \omega_0} + \left(\frac{s}{\omega_0}\right)^2}$$

(3-15)

where

$$G_{d0} = \frac{V_{OUT}}{D}$$

$$\omega_0 = \frac{1}{\sqrt{LC}}$$

$$Q_0 = R_L \sqrt{\frac{C}{L}}$$

(3-16)

The feedback scalar, which is usually a resistor voltage divider, can be modeled as

$$H = \frac{V_{REF}}{V_{OUT}} \tag{3-17}$$

The quiescent duty cycle is given by the steady state solution of the converter:

$$D = \frac{V_{OUT}}{V_{IN}}$$

(3-18)

The open-loop line-to-output transfer function is

$$G_{vg}(s) = D \frac{1}{1 + s \frac{L}{R_L} + s^2 LC}$$

=  $G_{g0} \frac{1}{1 + \frac{s}{Q_0 \omega_0} + \left(\frac{s}{\omega_0}\right)^2}$  (3-19)

with Gg0=D. The uncompensated complete system transfer function is

$$T_u(s) = G_{ADC} \frac{V_{OUT}}{D} G_{vd}(s) H$$

(3-20)

Here  $G_{ADC}$  is the ADC gain. Substitution of equations (3-15) into (3-20) leads to

$$T_{u}(s) = G_{ADC} H \frac{V_{OUT}}{D} \frac{1}{1 + \frac{s}{Q_{0}\omega_{0}} + \left(\frac{s}{\omega_{0}}\right)^{2}}$$

$$= T_{u0} \frac{1}{1 + \frac{s}{Q_{0}\omega_{0}} + \left(\frac{s}{\omega_{0}}\right)^{2}}$$

(3-21)

where  $T_{u0}$  is the DC gain of the complete system transfer function. (3-21) is the uncompensated complete system transfer function.

#### 3.2.3.2 PD Compensator

The PD compensator (also called lead compensator) is used to improve the phase margin. PD compensator acts like a high pass filter. The transfer function of PD compensator is

$$G_{C_{-}PD}(s) = G_{C_{-}PD0} \frac{\left(1 + \frac{s}{\omega_z}\right)}{\left(1 + \frac{s}{\omega_p}\right)}$$

(3-22)

Here, a zero is added to the loop gain at a frequency  $\omega_z$  far below the overall system crossover frequency  $\omega_c$  such that the phase margin is increased by the desired amount.  $\omega_c=2\pi f_c$  and  $f_c$  is the crossover frequency in terms of Hz and is selected to be 50kHz in our design. A high frequency  $\omega_p$  is also added to attenuate high-frequency noise. The fundamental goal of DC-DC is to regulate DC output. If the compensator gain at the switching frequency is too big, then the switching harmonics are amplified by the compensator, eventually disrupting the operation of DPWM. By considering these constrains,  $\omega_p$  is selected to be less than the switching frequency  $\omega_s$  ( $\omega_s = 2\pi f_s$ ). Particularly, to optimally obtain a compensator phase lead of  $\theta$  at crossover frequency  $f_c$ , the pole and zero frequencies ( $\omega_z$  and  $\omega_p$ ) are chosen as follows:

$$\omega_{z} = \omega_{c} \sqrt{\frac{1 - \sin(\theta)}{1 + \sin(\theta)}}$$

$$\omega_{p} = \omega_{c} \sqrt{\frac{1 + \sin(\theta)}{1 - \sin(\theta)}}$$

(3-23)

To avoid changing the crossover frequency, the magnitude of the compensator gain is chosen to be unity at crossover frequency  $f_c$ . Thus  $G_{C_PD0}$  in equation (3-22) is chosen as

$$G_{C_{-}PD0} = \sqrt{\frac{\omega_z}{\omega_p}}$$

(3-24)

## 3.2.3.3 PI Compensator

The PI compensator (also called lag compensator) is used to improve the DC and low-frequency loop gain. PI compensator acts as a low pass filter. The transfer function of PI compensator is

$$G_{C_PI}(s) = G_{C_PI\infty}\left(1 + \frac{\omega_L}{s}\right)$$

(3-25)

Here, a zero is added to the loop gain at a frequency  $\omega_L$ . If  $\omega_L$  is sufficiently lower than the crossover frequency  $\omega_c$ , the phase margin is unchanged. The pole at the origin 1/s is added to make the DC loop gain arbitrarily large. Therefore the DC component of the error signal between  $V_{FB}$  and  $V_{REF}$  is almost zero. The steady state output voltage is perfectly regulated accordingly.

To obtain a desired crossover frequency  $\omega_c$ , the PI compensator gain at very high frequency needs to be chosen as

$$G_{C_PI\infty} = \frac{\omega_c}{T_{u0}\omega_0}$$

(3-26)

where  $\omega_0$  is defined in(3-16) and  $T_{u0}$  is from (3-21).

#### 3.2.3.4 Combined PID Compensator

The product of the PD and PI compensator discussed can be expressed as

$$G_{c_{-}PID}(s) = G_{cm} \frac{\left(1 + \frac{\omega_L}{s}\right) \left(1 + \frac{s}{\omega_z}\right)}{\left(1 + \frac{s}{\omega_p}\right)}$$

(3-27)

This is a 2-pole 2-zero system. In practice, an extra pole is added at high frequency to increase the gain margin. It helps to prevent the switching ripple from disrupting the DC-DC regulation. A typical combined PID compensator is therefore a 3-pole 2-zero system. This type of compensator is also called Type-III compensator. The corresponding transfer function of this compensator is

$$G_{c}(s) = G_{cm} \frac{\left(1 + \frac{\omega_{L}}{s}\right) \left(1 + \frac{s}{\omega_{z}}\right)}{\left(1 + \frac{s}{\omega_{p1}}\right) \left(1 + \frac{s}{\omega_{p2}}\right)}$$

(3-28)

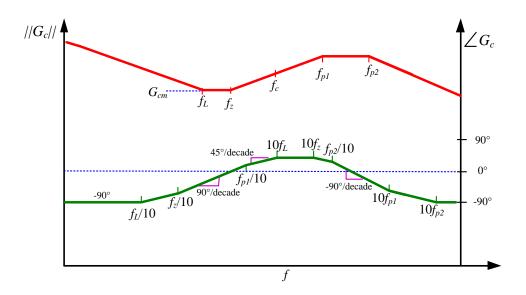

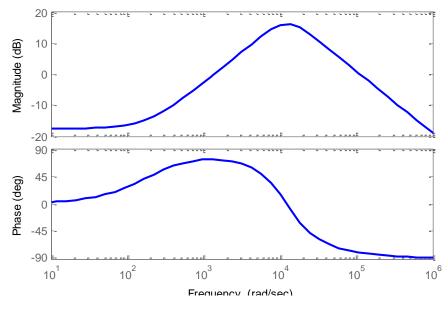

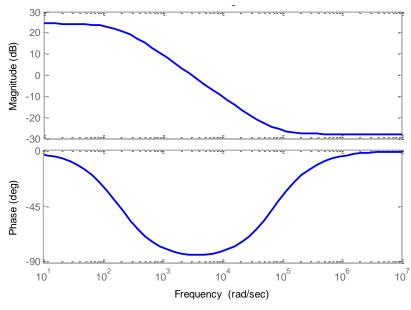

The bode plot of the PID compensator in (3-28) is shown in Fig. 3.12.

Fig. 3.12. Bode Plot of the Combined PID Compensator.

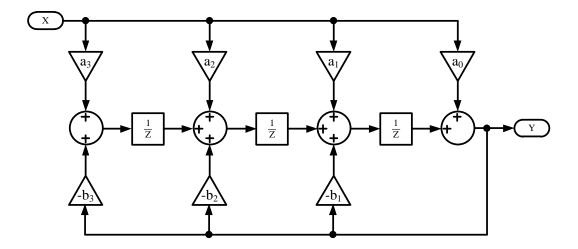

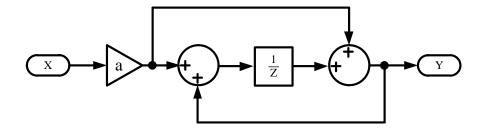

Equation (3-28) and Fig. 3.12 illustrate the poles and zeros in PID compensators. The inverted zero at  $\omega_z$  is added to extend the bandwidth of the feedback loop while maintaining an acceptable phase margin. The zero at  $\omega_L$  is used to increase the phase margin. The pole at the origin is inserted to boost the feedback loop DC gain to infinite large, thereby forcing the regulation error to be near zero. Two poles  $\omega_{p1}$  and  $\omega_{p2}$  are placed at high frequency to increase gain margin and to suppress the switching noise. Once the PID compensator is designed in s-domain, we could convert the continuous-time s-domain transfer function to the corresponding discrete-time z-domain transfer function via bilinear (Tustin) approximation method. For a Type-III PID compensator, the converted z-domain transfer function generally has the form of

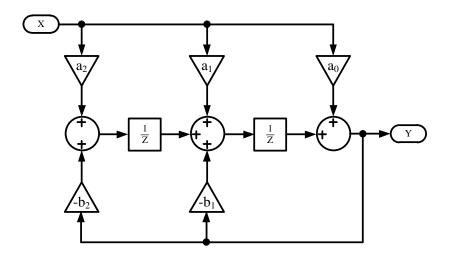

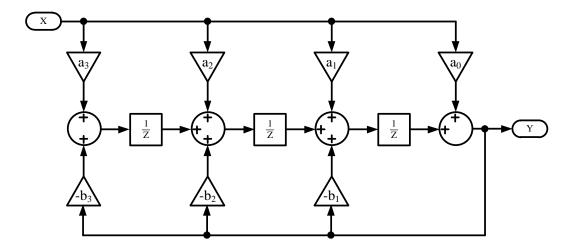

$$H(z) = \frac{a_0 z^3 + a_1 z^2 + a_2 z + a_3}{z^3 + b_1 z^2 + b_2 z + b_3}$$

(3-29)

The system in (3-29) can be implemented by using the architecture illustrated in Fig. 3.13.

Fig. 3.13. Digital Implementation of PID Compensator.

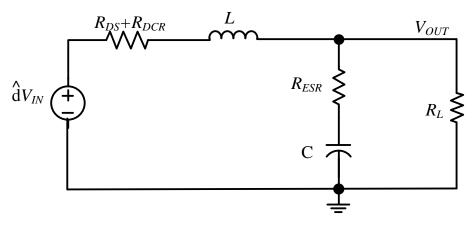

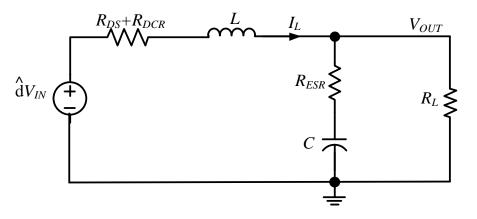

Please notice that the power inductor DCR  $R_{DCR}$ , power capacitor ESR  $R_{ESR}$ , and the turn-on resistance  $R_{DS}$  of the power switches were not considered in previous discussion. The small signal model of the buck converter taking these components into account is shown in Fig. 3.14.

Fig. 3.14. Small Signal Model of Buck Converter.

After considering  $R_{DCR}$ ,  $R_{ESR}$  and  $R_{DS}$ , the control-to-output transfer function from

(3-14) becomes

$$G_{vd}(s) = \frac{V_{IN}}{R_L + R_D} \frac{1 + sR_{ESR}C}{1 + s\left(R_{ESR}C + \frac{R_LR_D}{R_L + R_D}C + \frac{L}{R_L + R_D}\right) + s^2LC\frac{R_L + R_{ESR}}{R_L + R_D}}$$

(3-30)

where  $R_D$  is the sum of power inductor DCR  $R_{DCR}$  and the power switch turn-on resistance  $R_{DS}$ :

$$R_D = R_{DS} + R_{DCR} \tag{3-31}$$

The required duty cycle from (3-18) becomes

$$D = \frac{V_{OUT} + (R_{DCR} + R_{DS_N})I_{LOAD}}{V_{IN} - (R_{DS_P} - R_{DS_N})I_{LOAD}}$$

(3-32)

Here  $R_{DS_N}$  and  $R_{DS_P}$  are the  $R_{DS}$  of NMOS and PMOS power switches respectively.  $I_{LOAD}$  is the load current:

$$I_{LOAD} = \frac{V_{OUT}}{R_L}$$

(3-33)

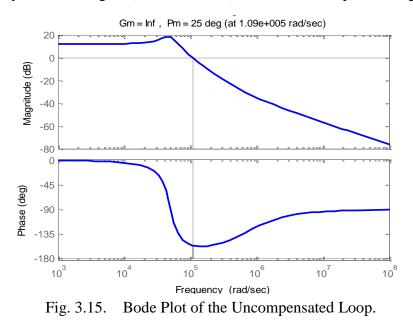

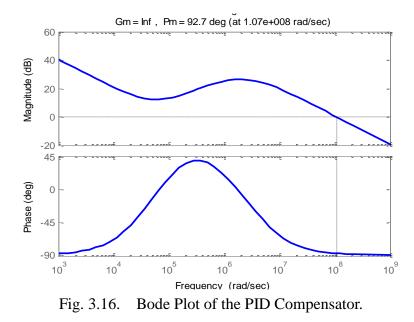

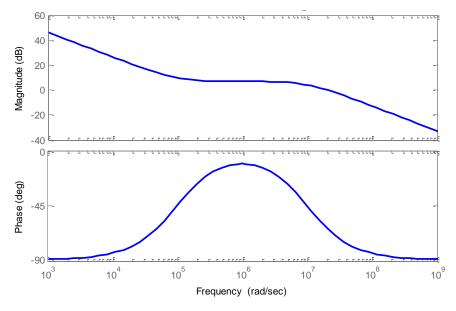

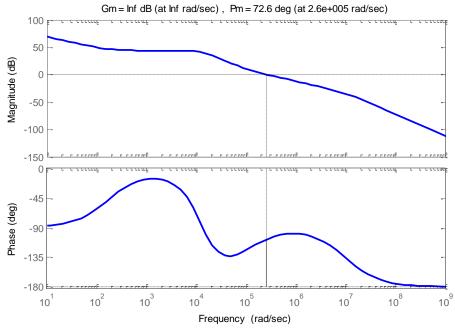

The PID compensator designed in this work is demonstrated in the following figures. Fig. 3.15 shows the uncompensated complete system  $T_u(S)$ . It apparently shows very limited DC gain (less than 20dB) and insufficient phase margin (25°).

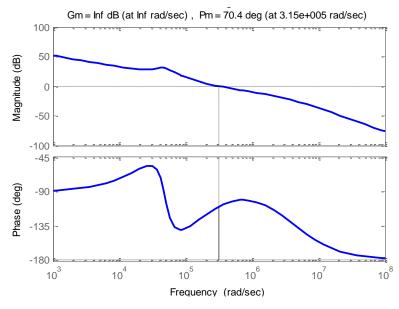

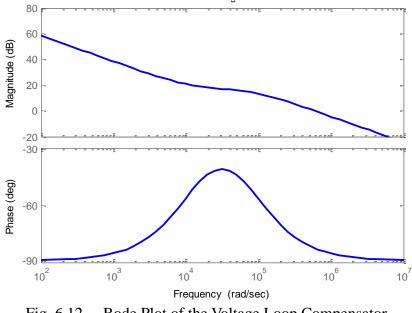

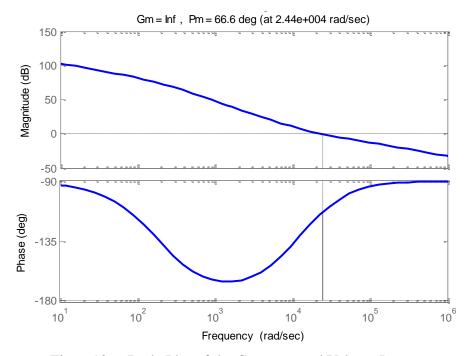

The constructed Type-III PID compensator is shown in Fig. 3.16. Fig. 3.17 is the compensated overall system. The crossover frequency  $f_c$  is selected to be 50kHz, i.e. 1/10 of the DC-DC switching frequency 500kHz. The phase margin is designed around 70 degree. This is to ensure the system's stability over certain range of input voltage, load current etc.

Fig. 3.17. Bode Plot of the Compensated Complete System.

The values of all components and other parameters used in the PID design are summarized in Table 3.1.

| Inductor    | $L = 18 \mu H$                               | $R_{DCR} = 60 \mathrm{m}\Omega$ |

|-------------|----------------------------------------------|---------------------------------|

| Capacitor   | $C = 22\mu F$                                | $R_{ESR} = 70 \mathrm{m}\Omega$ |

| I/O Voltage | $V_{IN} = 5 \mathrm{V}$                      | $V_{OUT} = 3.3 \mathrm{V}$      |

| Feedback    | H = 0.6                                      | $V_{REF} = 1.98 \mathrm{V}$     |