# Programmable Metallization Cell Devices for Flexible Electronics

by

## Sunil Baliga

## A Dissertation Presented in Partial Fulfillment of the Requirement for the Degree Doctor of Philosophy

Approved August 2011 by the Graduate Supervisory Committee:

Michael Kozicki, Chair Dieter Schroder Junseok Chae Terry Alford

## ARIZONA STATE UNIVERSITY

December 2011

#### ABSTRACT

Programmable metallization cell (PMC) technology is based on an electrochemical phenomenon in which a metallic electrodeposit can be grown or dissolved between two electrodes depending on the voltage applied between them. Devices based on this phenomenon exhibit a unique, self-healing property, as a broken metallic structure can be healed by applying an appropriate voltage between the two broken ends. This work explores methods of fabricating interconnects and switches based on PMC technology on flexible substrates. The objective was the evaluation of the feasibility of using this technology in flexible electronics applications in which reliability is a primary concern.

The re-healable property of the interconnect is characterized for the silver doped germanium selenide (Ag-Ge-Se) solid electrolyte system. This property was evaluated by measuring the resistances of the healed interconnect structures and comparing these to the resistances of the unbroken structures. The reliability of the interconnects in both unbroken and healed states is studied by investigating the resistances of the structures to DC voltages, AC voltages and different temperatures as a function of time. This work also explores replacing silver with copper for these interconnects to enhance their reliability. A model for PMCbased switches on flexible substrates is proposed and compared to the observed device behavior with the objective of developing a formal design methodology for these devices. The switches were subjected to voltage sweeps and their resistance was investigated as a function of sweep voltage. The resistance of the switches as a function of voltage pulse magnitude when placed in series with a resistance was also investigated. A model was then developed to explain the behavior of these devices. All observations were based on statistical measurements to account for random errors.

The results of this work demonstrate that solid electrolyte based interconnects display self-healing capability, which depends on the applied healing voltage and the current limit. However, they fail at lower current densities than metal interconnects due to an ion-drift induced failure mechanism. The results on the PMC based switches demonstrate that a model comprising a Schottky diode in parallel with a variable resistor predicts the behavior of the device. This dissertation is dedicated to my parents Dr. M. R. Baliga and Mrs. Bina Baliga, and my younger brother Sankarshan.

#### ACKNOWLEDGMENTS

I would like to begin by thanking my advisor Prof. Michael Kozicki, whose support and invaluable guidance has made my research possible. I would also like to thank my supervisory committee for their advice and taking the time to discuss various aspects of my research. I would especially like to thank Prof. Dieter Schroder for nurturing my interest in semiconductor devices and Prof. Terry Alford for the assistance on the material characterization of my samples and the discussions on electromigration and material composition of my samples. I would further like to thank the staff at CSSER and the Electrical Engineering department for the invaluable assistance and expert advice they have provided during the course of my research and for always being available to work with me when I needed the assistance.

I would also like to thank my parents Dr. M. R. Baliga and Mrs. Bina Baliga for encouraging me to pursue my Ph.D. and believing in me, even during the times when my self-confidence was on shaky ground. I would further like to acknowledge my younger brother, Sankarshan Baliga, for helping me discover what I wanted to do with my life. I would like to thank my extended family for their support and understanding, especially during the times when I was incommunicado.

I would like to thank my friends at ASU for their support and making my stay in Tempe very interesting. I would like to thank Sarath Puthen Thermadam for training me, Deepak Kamalanathan for his many intellectual discussions on various topics, William Lepkowski, Nicholas Summers, John Schoacki, Mohammad Reza Ghajar and Eric Tuffyas for introducing me to the various interesting aspects of Phoenix. I would also like to thank Newton Alex, Sujit Sanjeev, Chetan Satish, Balaji Padmabhan, Nadeem Mohammad, Raghunathan Srinivasan and Anand Sudhakaran, who have been my roommates at various times, for supporting me and for their understanding of my unconventional work schedule. I would also like to acknowledge the support of my friends Vindhya Kunduru, Karthik Sivaramakrishnan, Mandhar Gadhre and Katharina Brinkert, who have introduced me to various interesting activities in Tempe during the course of my stay here. I would like to thank Kathy Tousek and her yoga group for working with me to improve my yoga practice and their friendship. Lastly, I would like to thank my friend Laurie Herman for her invaluable and much appreciated support and friendship and for introducing me to athletic activities like rollerblading, skiing and scuba diving, which I never expected to do during my life. Her influence has added a new dimension to my personality, which I appreciate very much.

# TABLE OF CONTENTS

| LIST OF TABLES                                                   |

|------------------------------------------------------------------|

| LIST OF FIGURES xi                                               |

| INTRODUCTION                                                     |

| BACKGROUND AND REVIEW                                            |

| A. The Evolution of Interconnect Technology                      |

| 1. Structural Solutions for Stretchable and Flexible             |

| Electronics7                                                     |

| 2. Material Solutions for Stretchable and Flexible Electronics11 |

| B. Processing Techniques for Flexible and Stretchable            |

| Electronics14                                                    |

| 1. Solution Deposition of Organic Thin Films15                   |

| 2. Vapor-Phase Deposition of Materials16                         |

| 3. Thermal Transfer of Materials17                               |

| 4. Direct Patterning of Electronic Devices                       |

| C. Review of Properties of Flexible Substrates                   |

| 1. Stainless Steel Foil21                                        |

| 2. Glass                                                         |

| 3. Polymers                                                      |

| D. Review of Solid Electrolyte Material Systems and their    |    |

|--------------------------------------------------------------|----|

| Compatibility with Flexible Substrates                       | 24 |

| 1. The Silver-Germanium Selenide Electrolyte                 | 25 |

| 2. The Silver-Germanium Sulfide Electrolyte                  | 27 |

| 3. The Copper-Germanium Sulfide Electrolyte                  | 28 |

| 4. The Copper-Silicon Dioxide Electrolyte                    | 28 |

| 5. The Copper-Transition Metal Oxide Electrolyte             | 29 |

| E. Mechanical Properties of Germanium Selenide (Ge-Se) Glass | 30 |

| F. The Memristance Property                                  | 31 |

| SILVER BASED SOLID ELECTROLYTE INTERCONNECTS                 |    |

| A. Fabrication                                               | 34 |

| B. Characterization                                          | 37 |

| 1. Failure Resistance and Self-Healing Response of the Solid |    |

| Electrolyte Interconnect                                     | 37 |

| 2. Analysis of the Self-Healing Process                      |    |

| C. Reliability Testing of the Interconnects                  | 44 |

| D. D.C. Failure Model for the Interconnects                  | 48 |

| 1. Behavior of the Time-to-Failure as a Function of Applied  |    |

| Voltage                                                      | 49 |

| 2. Behavior of the Time-to-Failure as a Function of        |    |

|------------------------------------------------------------|----|

| Temperature                                                | 54 |

| 3. Behavior of the Saddle Point as a Function of Applied   |    |

| Voltage and Temperature                                    | 55 |

| COPPER BASED SOLID ELECTROLYTE INTERCONNECTS               | 58 |

| A. Fabrication                                             | 58 |

| B. Characterization                                        | 59 |

| 1. The Self-Healing Property                               | 61 |

| 2. D.C. Voltage Stressing                                  | 62 |

| C. Reliability Testing of the Interconnects                | 63 |

| SILVER DOPED GERMANIUM SELENIDE BASED SWITCHES             |    |

| FOR FLEXIBLE SUBSTRATES                                    | 67 |

| A. Fabrication                                             | 67 |

| B. Programming Model                                       | 70 |

| 1. Constant Voltage Case: $V(t) = V_A$                     | 72 |

| 2. Voltage Sweep: $V(t) = k_v t$ where $k_v$ is a constant | 73 |

| 3. Programming using a Voltage Pulse $V = V_A$ and a       |    |

| Current-Limiting Series Resistor R <sub>s</sub>            | 74 |

| C. Device Characterization                                 | 75 |

| 1. Voltage Sweep Behavior                                  | 77 |

# Page

| 2. Pulse Programming Behavior       | 83  |

|-------------------------------------|-----|

| SIMULATION OF P.M.C. BASED SWITCHES |     |

| A. Voltage Sweep Model              | 89  |

| B. Pulse Programming Model          | 94  |

| CONCLUSION                          | 100 |

| REFERENCES                          | 103 |

# LIST OF TABLES

| Table                                                           | Page |

|-----------------------------------------------------------------|------|

| 1. Density, Elastic Modulus, Indentation Hardness and Toughness |      |

| of Ge-Se glasses                                                | 30   |

| LIST | OF | FIG | URES |

|------|----|-----|------|

|      |    |     |      |

| Figure   Page                                                        |

|----------------------------------------------------------------------|

| 1. Shape optimized interconnect for improved mechanical              |

| performance                                                          |

| 2. Method for fabrication 3D vertical stacks of interconnects. The   |

| figure also shows the testing of these interconnects when            |

| mechanical stress is applied to it7                                  |

| 3. Interconnect fabrication after pre-stressing in order to ensure   |

| connectivity at maximum tolerances                                   |

| 4. SWNT trade-off between resistance and transparency 10             |

| 5. Illustration of semiconductor and metal nanomembranes 11          |

| 6. Schematic of Organic vapor deposition 14                          |

| 7. Schematic of the thermal transfer principle                       |

| 8. Schematic of cold welding                                         |

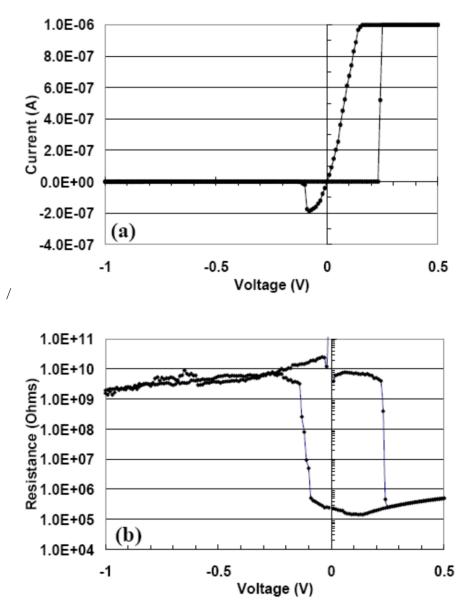

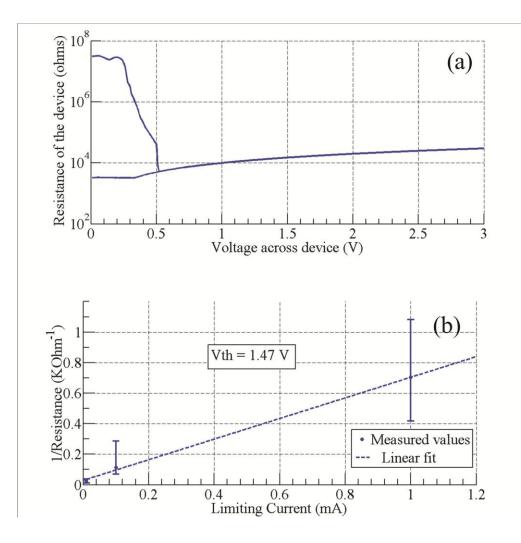

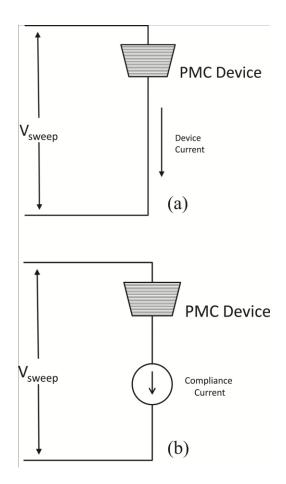

| 9. Sweep behavior of the PMC device                                  |

| 10. Schematic of the self-healing interconnect structure on          |

| polyimide                                                            |

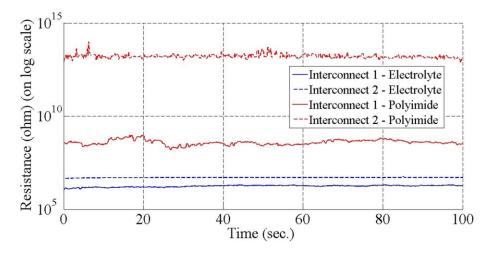

| 11. Resistance of two failed Ag lines on Ag-Ge-Se solid electrolyte  |

| and Ag directly on polyimide                                         |

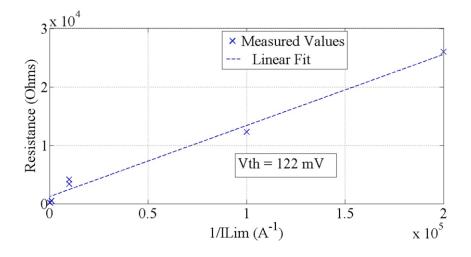

| 12. Healed interconnect resistance plotted against the reciprocal of |

| the current limit (2V DC healing bias)                               |

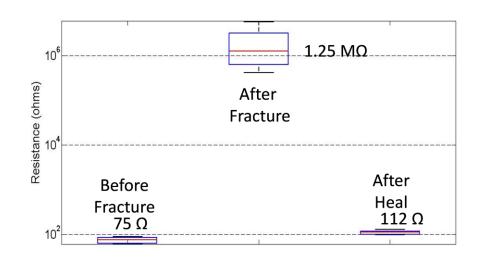

| 13. Interconnect resistance distributions before fracture, after     |

| fracture and after healing                                           |

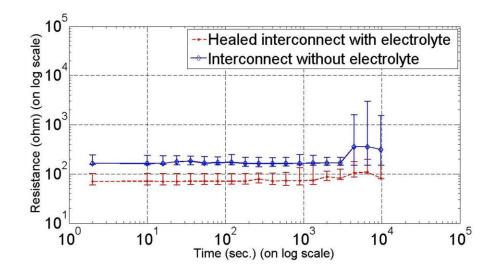

| 14. Analysis of measured resistance values of interconnects with        |

|-------------------------------------------------------------------------|

| and without an underlying solid electrolyte layer                       |

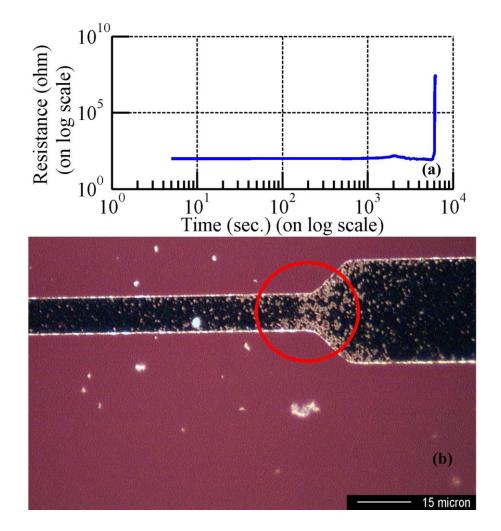

| 15. Constant voltage stressing of fabricated interconnect with a DC     |

| stressing voltage of 500 mV 45                                          |

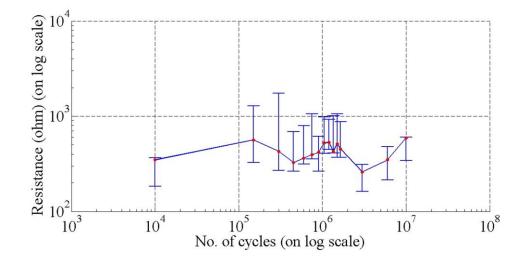

| 16. Statistical analysis of the resistances of 5 interconnect devices   |

| after healing when subjected to AC voltage stressing                    |

| 17. AC testing of fabricated and healed interconnects                   |

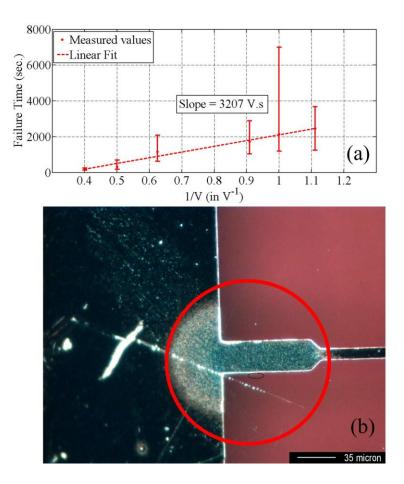

| 18. Plot of resistance as a function of time for a stressing voltage of |

| 1 V showing the saddle point and final failure                          |

| 19. Time-to-failure as a function 1/V for Ag-Ge-Se interconnects        |

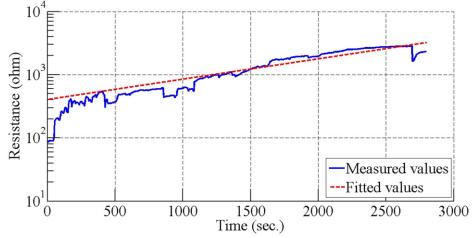

| 20. Plot of resistance as a function of time comparing fitted and       |

| observed response for Ag-Ge-Se interconnects                            |

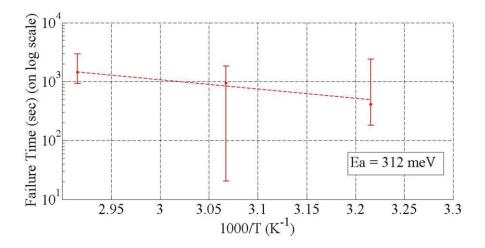

| 21. Failure time as a function of 1000/T for Ag-Ge-Se                   |

| interconnects                                                           |

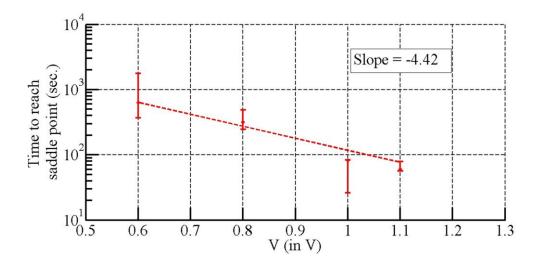

| 22. Plot of time to reach saddle point as a function of stressing       |

| voltage for Ag-Ge-Se interconnects                                      |

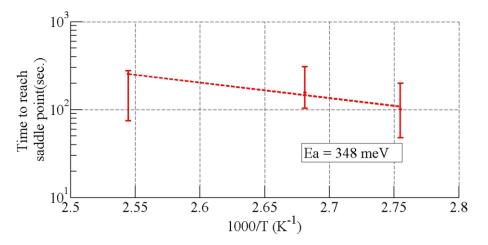

| 23. Arrhenius plot of time to reach saddle point as a function of       |

| temperature for Ag-Ge-Se interconnects                                  |

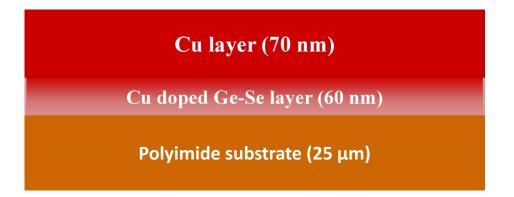

| 24. Cross-section of the copper based germanium selenide solid          |

| electrolyte interconnect                                                |

| 25. Sweep voltage behavior of Cu-Ge-Se interconnect                     |

| 26. Retention testing of Cu-Ge-Se interconnects                         |

| Figure Page                                                         |

|---------------------------------------------------------------------|

| 27. DC failure behavior of Cu-Ge-Se interconnects                   |

| 28. Schematic of the PMC switch                                     |

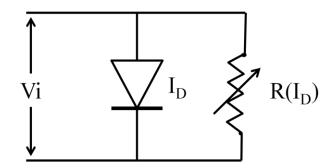

| 29. Proposed programming model for the device                       |

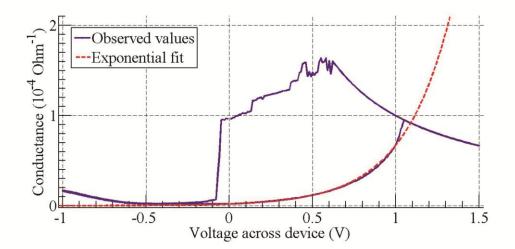

| 30. Exponential fit for the programming model of the                |

| electrodeposit                                                      |

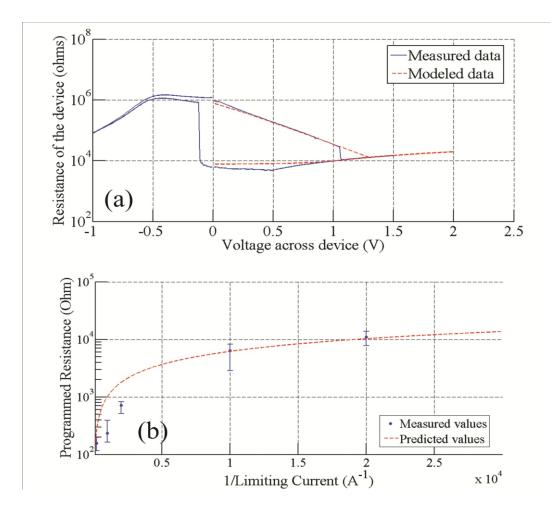

| 31. Comparison of predicted and actual values for the PMC switch    |

| during the voltage sweep                                            |

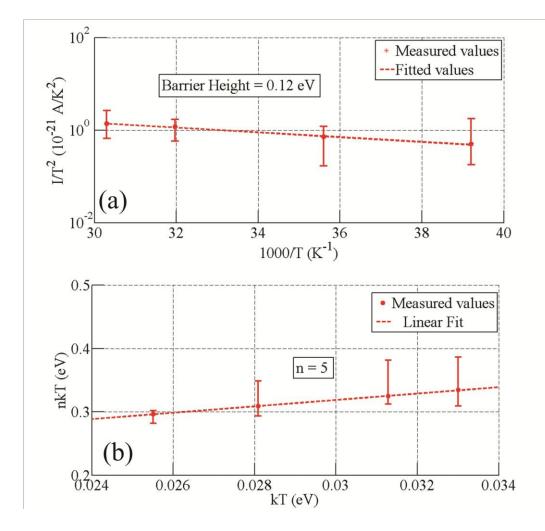

| 32. Characterization of the Schottky barrier height and ideality    |

| factor for the PMC switch                                           |

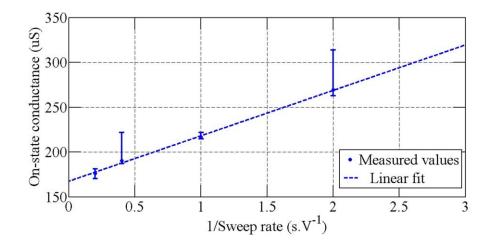

| 33. Plot of on-state conductance as a function of the reciprocal of |

| sweep rate                                                          |

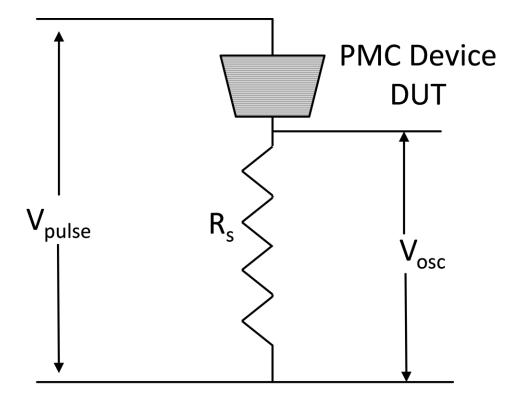

| 34. Pulse programming using a waveform generator and an             |

| oscilloscope                                                        |

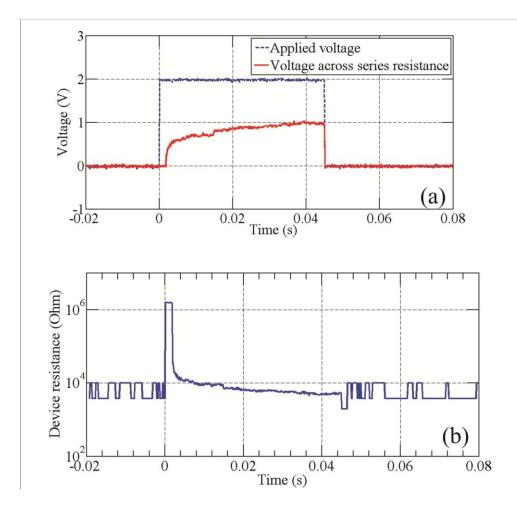

| 35. Resistance evolution of the PMC switch in response to a         |

| voltage pulse                                                       |

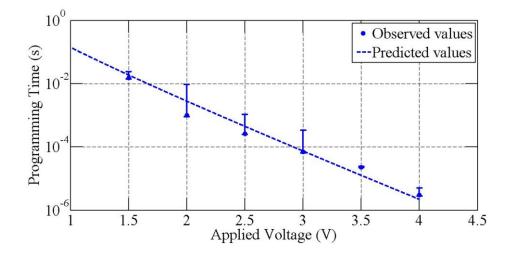

| 36. Programming time as a function of magnitude of the applied      |

| voltage pulse                                                       |

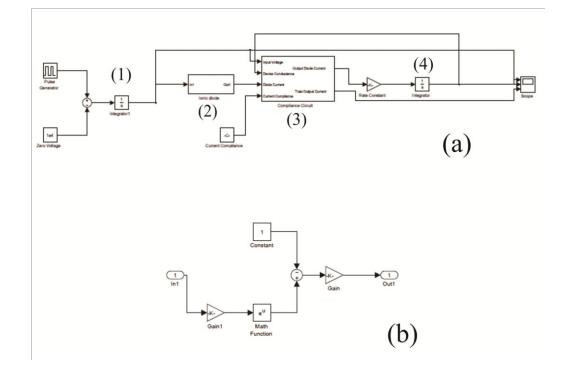

| 37. Voltage sweep models for the PMC switch                         |

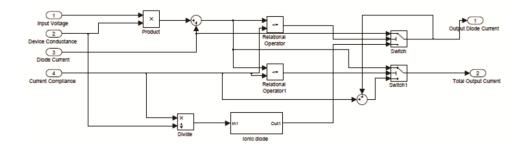

| 38. Mathematical model for the simulation components of the         |

| PMC switch                                                          |

| 39. Compliance current decision model                               |

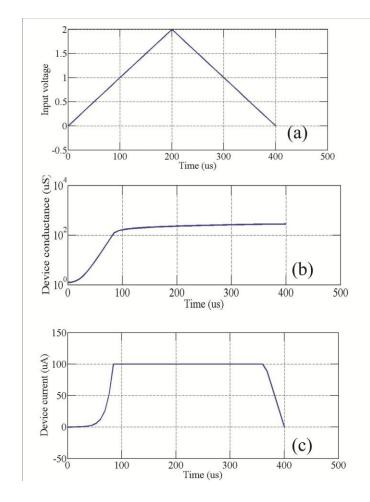

| 40. Outputs of the mathematical model                               |

# Figure

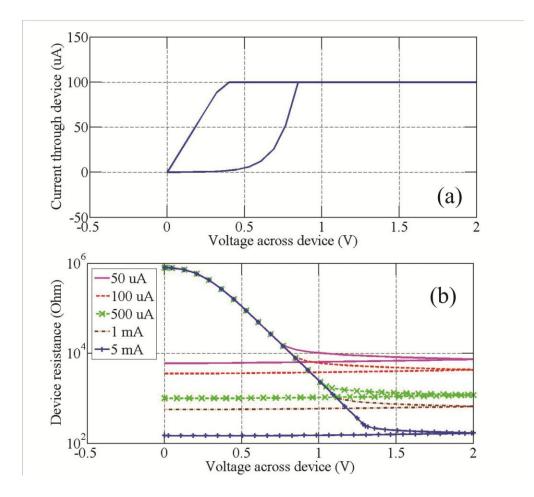

| 41. | (a) Simulated current-voltage sweep for a compliance current       |    |

|-----|--------------------------------------------------------------------|----|

|     | of 100 $\mu$ A. (b) Simulated resistance-voltage sweeps for        |    |

|     | different compliance currents.                                     | 94 |

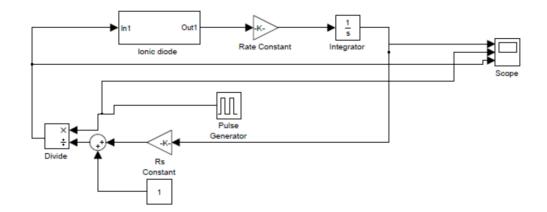

| 42. | Voltage pulse programming model                                    | 95 |

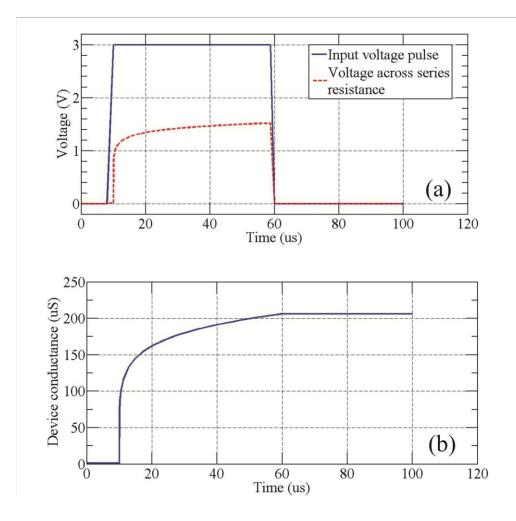

| 43. | (a) Voltage behavior as a function of time. (b) Conductivity       |    |

|     | variation as a function of time.                                   | 96 |

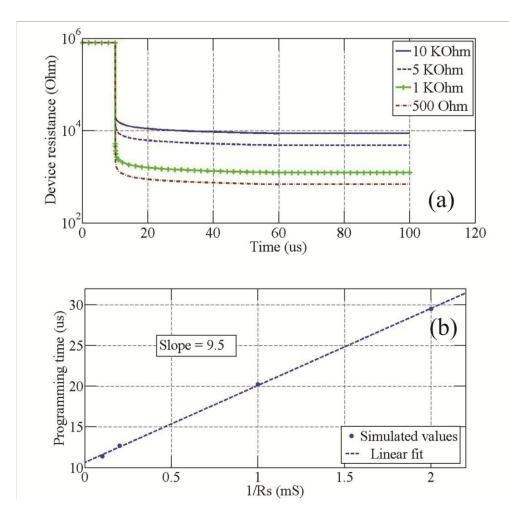

| 44. | (a) Resistance as a function of time for different series limiting |    |

|     | resistances. (b) Programming time as a function of 1/Rs            |    |

|     | showing a linear relationship.                                     | 98 |

Page

#### INTRODUCTION

Programmable Metallization Cell (PMC) technology is based on an electrochemical phenomenon in which the application of a voltage between two electrodes fabricated on a solid electrolyte results in either the growth or dissolution of a metal filament between the two electrodes [1]. This technology has been used to fabricate memories [1-5], capacitive elements [6], and memory elements on flexible substrates [7]. The myriad applications that this versatile technology has been applied to, prove its robustness. Another potential area of research for PMC technology is its use in mechanically demanding applications. Such applications arise when the associated electronic circuits are subjected to extreme physical conditions like bending and torsion during routine operation in wearable electronics and flexible displays, or in cameras, laptops and other portable equipment where the bending of these circuits occurs during manufacture in order to improve packing density. The fabrication of PMC circuit elements that are capable of withstanding these conditions is feasible because the thin films that comprise the device, namely, the solid electrolyte films which are generally chalcogenide glasses and the metal films, are very flexible [8].

Interconnects are metal lines that are used to connect different circuit elements or sub-modules of the integrated circuit (IC) together. These lines carry currents from one point of the circuit to the other. As applications for ICs get more diverse and demanding, the specifications for the interconnects become more challenging to meet. The earliest issues encountered were directly related to the scaling of IC process technology. As semiconductor device technology was

scaled, interconnects needed to carry correspondingly greater current densities. The most direct consequence of scaling was, therefore, power dissipation in the interconnect due to joule heating and subsequent failure of the interconnect due to accelerated electromigration [9-11]. Electromigration is a phenomenon in which the electrons comprising the current would transfer their momentum to the atoms comprising the interconnect, resulting in their movement and causing the interconnect to eventually fail. Both of these problems were resolved primarily by replacing the material that was used to fabricate the interconnect [12]. The current area of focus in the electronics industry is the development of ubiquitous computing devices and networks. These applications include wearable computers [13, 14] and devices [15], body area networks, flexible devices [16, 17] and portable devices [18, 19]. The ability of such electronics to withstand mechanical stress, while being able to reconfigure itself for optimum performance simultaneously, is an implicit specification. This work focuses on demonstrating that PMC technology is capable of fabricating robust interconnects that can withstand a very high degree of mechanical stress, and switches that perform well in flexible electronics applications. Furthermore, in the case of fracture of such an interconnect, this work demonstrates that the interconnect can be healed by simply applying an appropriate voltage for a small amount of time, thus restoring the circuit to normal operating conditions. This work also proposes a circuit model for a PMC based switch on a flexible substrate and demonstrates that it predicts actual device behavior accurately.

#### BACKGROUND AND REVIEW

This section provides a developmental perspective of interconnect technology. Some novel interconnect fabrication principles, specifically designed for flexible substrates, are discussed. A review of properties for materials that would make them good substrates for flexible electronics applications is also presented. The evolution of PMC technology is also discussed, along with the electrochemical and fabrication principles which form the basis of this technology. The mechanical properties of some of the solid electrolyte systems are presented to justify their use in flexible electronics applications. A discussion on the property of memristance is presented to develop a background for the analysis of the PMC switch as a memristive system.

#### A. The evolution of interconnect technology

Interconnects are metal lines which are used to connect different devices and sub-modules on an IC in a pre-determined path in order to ensure that the circuit performs a specific function. From a manufacturing perspective, the IC interconnect is fabricated by first lithographically patterning the required interconnect layout and then selectively depositing thin films of the chosen metal. In the early days of IC manufacturing, this was arguably one of the simplest processes in IC manufacture, as metal deposition and lithography were far in advance of transistor design and processing. However, with advances in transistor technology in order to keep up with IC scaling, interconnect performance in beginning to define the performance of the IC. The issues which interconnects face include compatibility with the new materials that are going into IC

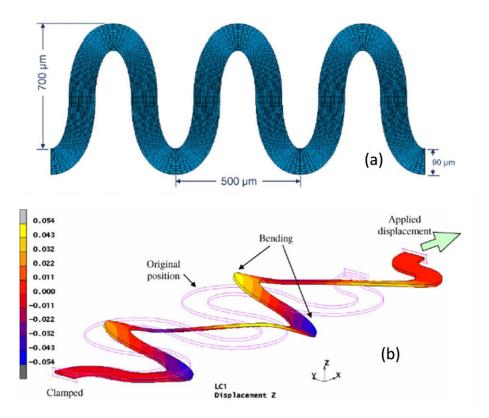

Fig. 1. (a) One of the possible optimized horseshoe-shaped interconnects that can withstand longitudinal strain on the substrate. (b) Mechanical behavior of the Cubased horseshoe shaped interconnect when subjected 20 % out-of-plane longitudinal strain [39]

manufacture and reliability of the interconnects when subjected to increasingly high current densities during scaling. The higher current densities result in increased heat dissipation within the IC and also a higher probability of the onset of electromigration [20, 21]. These reliability issues were ameliorated by changing the interconnect material in the sub-100 nm nodes from aluminum (Al) [20-22] to copper (Cu) [23, 24]. The change in interconnect material improved the interconnect reliability and performance drastically. However, Cu is incompatible with silicon dioxide (SiO<sub>2</sub>) and silicon (Si), since its diffusivity in both materials is high [25, 26]. The presence of copper in silicon devices increases leakage current [25] and reduces the quality of dielectric films [26], reducing the lifetime of the circuit. In order to ensure that the entire IC is reliable, a material needed to be found which would act as a diffusion barrier between the Cu interconnect and the underlying Si or  $SiO_2$  layer. Additionally, this layer needed to have excellent adhesion to the underlying layer and also capable of being deposited in the form of thin films. Many materials may be used for this purpose like titanium nitride (TiN) [27], tungsten nitride [28] and and tantalum nitride (TaN) [29]. The resulting process is known as the dual-damascene process [30]. Another reliability issue with interconnects has been delay through the line. A combination of the interconnect metal line and the inter-layer dielectric (ILD) produces a transmission line with distributed resistances and capacitances, which results in a delay through the line. With scaling, the values of the resistances and the capacitances have increased, resulting in the delay of the interconnect line now being comparable to the delay through the transistor itself. This results in the speed of the IC being limited more by the interconnect delays than by the delays associated with the transistors [31, 32]. In order to reduce delay, Cu interconnects with a low-k dielectric for the ILD have been used. However, the dual-damascene process is not compatible with the proposed ILDs and numerous integration challenges are presented when moving to the new ILD which include the mechanical and electrical instability of the material [33]. At present, no single, standard process exists for integrating the dual-damascene process with the low-k dielectric [32, 33]. Scaling trends continue to place demands on the material used

for the interconnect. Research has trended toward using Ag as a material for fabricating interconnects [34], as it has the highest electrical conductivity at room temperature, can be electroplated and produces films with low residual stress [34]. However, significant challenges remain with integrating Ag as an interconnect material. The most important factors are its very high rate of corrosion [34, 35] and its poor adhesion to most materials used in IC manufacturing processes [35].

The recent trend of the electronics industry to manufacture portable devices has produced significant challenges in the field of IC manufacture and reliability. The requirements of portability include small size, light weight, low power consumption and ability to resist and recover from mechanical stress. This translates to increased packing density for electronic components, low power IC design and novel materials with the required mechanical and electrical characteristics. The demand for increased packing density has led equipment manufacturers to focus on fabricating interconnects on flexible substrates [36]. These substrates can then be deformed in order to reduce their footprint [37]. However, these efforts have led to reliability issues as the Young's modulus and the yield strength of the metal which is used to fabricate the interconnect is different from that of the substrate, resulting in strain-induced fractures of the interconnects, at the strains values as low as 5% [38]. Improving the reliability of interconnects on flexible interconnects is being addressed by current research. A number of different approaches have been suggested in order to overcome this problem. Some of these are listed in the sections below.

1. Structural solutions for stretchable and flexible electronics

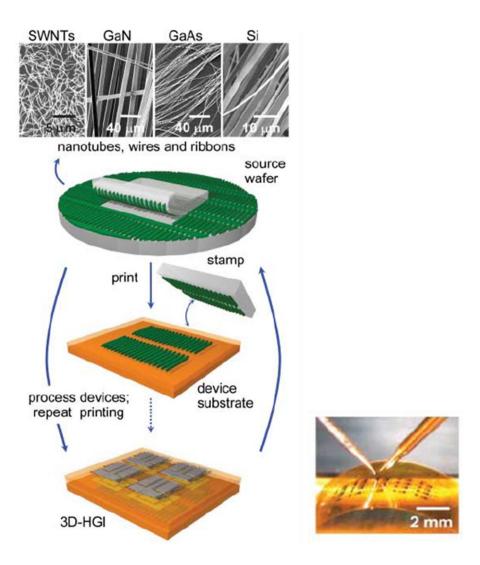

Fig. 2. Method for fabrication 3D vertical stacks of interconnects. The figure also shows the testing of these interconnects when mechanical stress is applied to it [40].

One of the solutions is to optimize the shape of the interconnect, or the interconnect layout, in order to be able to withstand a certain strain on the substrate. Optimization of the shape of the interconnect is done by detailed FEM analysis of different possible shapes and judicious selection of the right shape

based on the kind of application the circuit is likely to be used [39]. An optimized interconnect shape for withstanding longitudinal strain is shown in Fig. 1. The advantages of this solution is that it is the simplest to implement and can offer

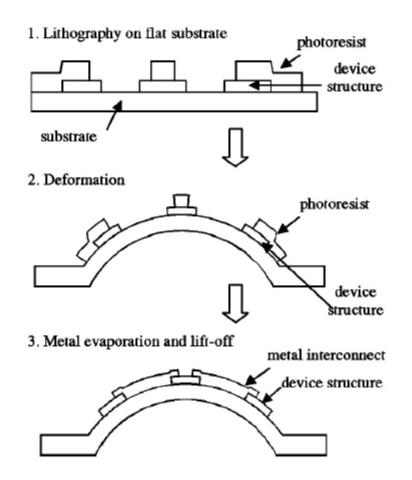

Fig. 3. Interconnect fabrication after pre-stressing in order to ensure connectivity at maximum tolerances [41].

considerable flexibility with little modification to the fabrication process. The greatest disadvantage is that the solution is not universal. If the circuit is deformed in ways that the designers did not foresee, then the advantage of the optimized design is lost and the device is just as prone to mechanical failure as a normal

interconnect. Secondly, almost every such interconnect would require more material than a normal interconnect line and the layout would have to be much more complicated in order to take into account shapes that are not normally encountered in semiconductor manufacturing. Finally, since the selection of the shape is based on a subjective selection based on FEM analysis, quality control of the devices becomes an issue as small changes in the shape of individual interconnects could greatly impact the reliability of the overall circuit.

3-D stacking of the circuit is a second structural approach that has been examined in research. In this approach, most of the critical interconnects are designed to run vertically downwards into the circuit. The metal lines are then supported by enclosing them in other materials like carbon nanotubes [40]. Fig. 2 shows how this can be implemented. This approach is considerably more complex in terms of fabrication than the previous methods. The reliability of this type of device is dependent on the kind of mechanical strain applied. It is best at withstanding longitudinal strain, rather than vertical strain.

A third structural approach to produce interconnects for flexible electronics would be to fabricate a set of sub-circuits on silicon islands deposited on a deformable substrate [41]. After fabricating the individual sub-circuits on the silicon islands, these islands are interconnected using metallization. However, although the interconnects are patterned before deforming the substrate, the deposition is done after deformation to maximum tolerances [41]. Fig. 3 demonstrates a fabrication process which implements this. This ensures that the islands remain interconnected even at high strains. The advantage of this approach is that maximum tolerances are met and the interconnects remain stable under strain. However, this fabrication method does not address the issues of directional strain. The designer must still understand how the circuit will be strained before it is applied in order to optimize the design of the interconnect. It is also unlikely

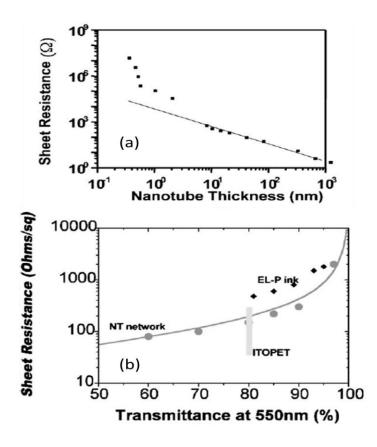

Fig. 4. (a) shows the decrease in sheet resistance with increasing nanotube thickness. (b) shows the increase in sheet resistance with increase in transmittance [47].

that this optimization can be carried out if the circuit is deformed in multiple directions.

#### 2. Material solutions for stretchable and flexible electronics

While the section above illustrates solutions that modify the structure and shape of the interconnect while still using materials found in the current IC fabrication processes, this section presents solutions that are based on novel materials that can be used for interconnects on flexible substrates. All these

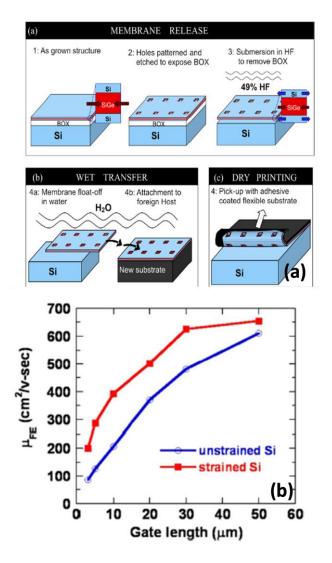

Fig. 5. (a) Fabrication of strained SiGe nanomembranes (b) Comparison of TFTs on nanomembranes with and without strain [49]

materials possess some properties that allow them to deform easily, without a marked change in resistance through them.

The most popular choice for interconnects in flexible electronics is gold. It has been used as an interconnect in a diverse range of applications in flexible electronics paper-based organic electronics [42], active-matrix displays based on organic transistors [43], carbon nanotube based semiconductor applications [44] and printed electronics [13]. Gold is useful because of its low Young's modulus [45] and very low resistance [46]. However, its disadvantages are that it is extremely expensive and that it is a deep-level impurity in CMOS processes, making it unviable in such manufacturing lines. A third problem with gold is that it sputters in molten form, thus increasing the chance of contamination within the deposition system.

Another material that can be used for interconnecting circuit elements on flexible substrates is a network of carbon nanotubes. Single-walled nanotubes (SWNTs) can be used as good conductors since they naturally take on the shape of a thin-walled tube when fabricated [47]. This material is especially useful because its optical properties are also tunable to make it transparent in the visible light range. This would produce a material that could compete with Indium-Tin-Oxide (ITO) in flexible display applications [47]. The disadvantage of this material is that the thickness of the carbon nanotubes determines both the sheet resistance of the film as well as the optical properties. In general, a trade-off needs to be made between the resistance and the optical properties [47]. Another disadvantage is the fabrication method of the carbon nanotube, which calls for new materials and processes to be added to a conventional fabrication facility, which can be expensive.

A few other options include other metal interconnects like chromium, silver, aluminum and copper, which are good conductors, but are much more brittle than gold. Some semi-conductor materials like gallium nitride (GaN) and gallium arsenide (GaAs) can also be doped to behave like conductors. The advantage is that these materials can be fabricated to form ribbons, wires and nanotube structures [40]. However, these have process integration issues without the very high conductivity of metallic materials.

A third option is to use nanomembranes of various semiconductor materials and engineer them for the required conductivities [48, 49]. The conductivity can be modified in various ways like controlling the doping in the material, controlling grain size [50] or by introducing strain [48] in the material. Fig. 5 shows the fabrication of SiGe nanomembranes and the change in fieldeffect mobility for TFTs fabricated on it, when strain is applied to the nanomembrane. The advantage of this approach is the high degree of control that can be achieved in terms of the sheet resistance of the device. The small size of the device, in the thickness of a few hundred nanometers, also means that the packing density of the circuits can be increased significantly, compared to other techniques, without significantly trading off sheet resistance. The disadvantage of this method is that the fabrication process differs significantly from conventional fabrication processes, which makes integration difficult in the short term. The fact that sheet resistance changes significantly in the nanometer regime [49] also places significant restrictions on the precision of the deposition and design processes.

### B. Processing techniques for flexible and stretchable electronics

The processing techniques that can be used on substrates which are used for flexible electronics applications are limited primarily by their low glass

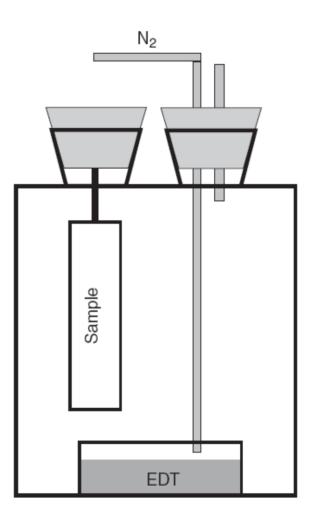

Fig. 6. Schematic of Organic vapor deposition, a variant of thermal vapor deposition, that improves film uniformity by making the deposition phase diffusion-limited. The nitrogen is heated as it is used to transport the source (EDT) to the sample [54].

transition temperatures and their tendency to flex and bow during the fabrication process. A new set of patterning and deposition techniques were designed specifically to deal with flexible substrates for the reasons stated above. Some of these techniques are discussed subsequently.

#### 1. Solution deposition of organic thin films

Most polymers are deposited using a solution deposition technique. The polymer is first dissolved in a compatible solvent and the solution is then sprayed on or spun on the substrate. The solvent is then evaporated off the substrate, leaving behind the required polymer film [51, 52]. This process produces very uniform films of thicknesses as low as 100 nm. The advantages are the very high deposition rates achieved and the relative ease with which the process can be modified in order to accommodate very large area films [51]. The disadvantages are the interference between the solvent and the previously deposited layers and the inability to locally pattern complex circuit elements [51]. The interference phenomenon can be ameliorated by functionalizing the solvent in order to deposit multiple films at the same time, or perform multiple processing steps at the same time. But the results are generally a compromise on the performance of the circuit [51]. An interesting advance in the solution processing technique is the ink-jet printing technique [50, 51]. This allows considerable flexibility in the local patterning of circuit elements. Recent advances in the inkjet printing of organic compounds have produced circuit elements that can be patterned with subfemtoliter accuracy [53]. This process places greater demands on polymer inks

including better uniformity and formulations that satisfy all the electrical and optical properties of the application, down to the micron level [51].

### 2. <u>Vapor-phase deposition of materials</u>

Vapor-phase deposition of thin layers is the most common form of processing for flexible electronics. It has been directly adapted from the semiconductor deposition technique called vacuum thermal deposition. The process involves the placing of the source in a boat and heating it in vacuum so that it sublimates. The substrate is placed in the path of the resulting gas flow and a thin layer of the source is deposited on the substrate [51]. The primary advantage of this method is that it is already a mature process in the semiconductor industry. The other advantage is that a potentially unlimited number of thin films can be grown as a stack using this method. The disadvantages are that there is a lot of wasted source material as the source not only coats the substrate, but also the entire chamber and the inherent film nonuniformity. The evaporation rate in different directions is non-uniform, resulting in a thinner film at the edges and a thicker film at the center. This can be a problem, particularly for large-area displays, where the substrate size is very large [51]. This problem is reduced considerably by using a variant of the thermal deposition technique called organic vapor-phase deposition (OVPD), where the film uniformity is controlled using a transport medium such as an inert gas or nitrogen [51, 54]. However, this is limited by the temperature required to vaporize the source and is typically used only for organic compounds. A third disadvantage relates to thermal deposition of compounds. As different elements within the

compounds have different partial pressures at a particular temperature, the rate of evaporation of each of these elements, and therefore, the deposition rates will be different. This results in a stoichiometric difference between the deposited film and the original source material [55]. Fig. 6 shows a schematic for a vapor-phase deposition system.

#### 3. <u>Thermal transfer of materials</u>

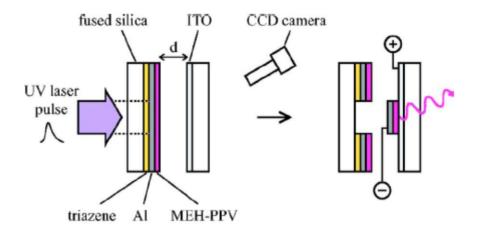

This technique works only with heat sensitive materials at significantly lower temperatures than the glass transition temperature of the substrate. Therefore, it is used mostly for patterning organic materials. These materials are

Fig. 7. Schematic of the thermal transfer principle. The laser decomposes the sacrificial triazene layer, resulting in the deposition of the remaining portion of the film on the receiving ITO layer. The UV laser is run in a pre-determined manner in order to transfer the required pattern onto the ITO film [56].

pre-deposited, without patterning, on a "donor" sheet. The donor sheet is then placed over the substrate and a localized heat source (like a laser) is run over the donor in a pre-determined pattern. The result is the transfer of the required material from the donor sheet to the substrate [51, 56].

### 4. Direct patterning of electronic devices

Direct patterning of thin films is the process of transferring patterns onto the substrate using processes that are analogous to printing. Such methods include

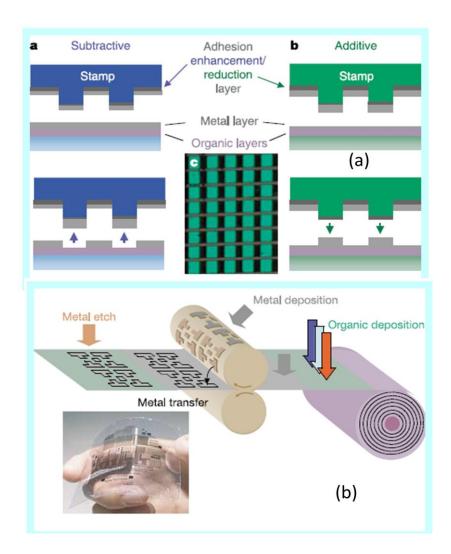

Fig. 8. (a) Schematic of cold welding. The figure demonstrates how a stamp can be used for selectively cold-welding patterns into the metal. (b) Schematic of roll-to-roll printing using equipment similar to a printing press, which makes the process very low cost [51].

imprinting a thin film of the functional material using a rubber or polymer stamp, cold welding, lithographically induced self-assembly or microcutting of the cathode metal after deposition of the underlying functional materials [50, 51, 57].

Cold welding is the binding of two clean surfaces of the same metal on contact or on the application of moderate pressure. By selectively applying the pressure, only certain parts of the second metallic film are allowed to stick, while the remaining portion may be removed easily. The stamp is made of a soft material, typically poly-dimethylsiloxane (PDMS), with a desired pattern embossed on it. An additional adhesion-prevention coating is placed on it to prevent the metal from sticking on the stamp [51].

Roll-to-roll printing is a very attractive form of processing flexible electronics. This process is very mature because the same equipment has been used in the printing industry for a long time. This processing technique can be easily adapted to flexible electronics because the substrate on which the electronic components need to be fabricated is flexible, making it similar to paper.

#### C. Review of properties of flexible substrates

Recent research has resulted in a number of materials that show promise as substrates for flexible electronics applications. However, there is no universal solution to the choice of a flexible substrate as different materials offer unique desirable properties for a particular application. As we make a choice of which substrate to use in order to fabricate flexible memory, we need to evaluate the criteria discussed below. A fundamental property of the chosen flexible substrate is mechanical and thermal stability [58]. Mechanical stability ensures that the substrate does not crack as it is bent. Ideally, the substrate should be capable of flexing repeatedly without any significant degradation. This property also extends to the fact that the material does not show fatigue i.e. the material remains stable dimensionally and does not change in its size as it is stressed over time. Thermal stability ensures that the material does not deform drastically when subjected to temperature changes. This is especially important during device fabrication, during which temperature changes are fairly common. The change in dimensions due to changes in temperature is measured as the Coefficient of Thermal Expansion (CTE).

A low CTE substrate ensures that the flexible circuit can be fabricated with relatively little change to the original silicon process and also is capable of operating over a wide range of temperature. One of the main points of failure for flexible circuits is at the interface of the substrate, which is usually organic, and the device layers, which are almost always inorganic. A large CTE for the substrate results in stresses developing in the inorganic thin film layers in contact with the substrate. The result is usually either cracking or poor adhesion of the device layers to the underlying substrate.

Surface properties of the substrate are also extremely important. For example, planar surfaces are a prerequisite for the fabrication of almost all devices on flexible substrates. This is because most devices are deposited as thin films, which tend to have very poor step coverage. A non-planar surface would result in parts of the substrate being exposed to the upper metallization layers. Another important surface property in the case of PMC devices is surface conductivity. The surface of the substrate on which the devices are fabricated should be conductive so that this can be the bottom electrode or cathode. A nonconductive surface, therefore, would have to be processed in order to make it conductive.

The final property that needs to be scrutinized is cost. This cost is not limited to the cost of the substrate, but also the cost of adapting the fabrication process to the substrate. One of the advantages of flexible substrates is cost savings. This is realized in most cases by migrating from the traditional wafer-bywafer fabrication approach to the roll-to-roll fabrication process. The feasibility of this approach depends on the robustness of the substrate and the ease with which the substrate can be aligned during fabrication.

Many substrates show potential for flexible electronics applications. The ultimate choice depends primarily on a compromise between mechanical and thermal stability and cost of the substrate and the materials involved in the fabrication of the electronic devices.

#### 1. <u>Stainless steel foil</u>

Stainless steel foil is a very attractive option as a flexible substrate. Metal foils generally have very high moduli of elasticity and are unlikely to deform during roll-to-roll processing. Stainless steel foils have a fairly high CTE, about 15-20 ppm higher than silicon. This may present problems when processing at elevated temperatures. The surface of metal films is usually extremely rough.

Planarization of metal films is usually a fairly involved process. The costs involved with procuring SS foils are usually low, but planarization usually elevates these costs [58]. Finally, the costs involved with processing SS foils are not much lower than processing other types of flexible substrates in preparation for device fabrication.

2. <u>Glass</u>

Thin glass substrates are extremely stable, both mechanically and thermally. The CTE of glass is extremely close to that of silicon, which makes the fabrication process very predictable and little change is required from the traditional silicon process in order to adapt it to the glass substrate. The engineering of the glass transition temperature for glass substrates is a very well understood process. The surface properties of glass are excellent as with polishing a very smooth surface can be obtained. Unfortunately, glass displays a reasonable degree only at thicknesses below 200  $\mu$ m, which can be achieved using the float glass process. For flexible electronics, the required flexibility is reached only at thickness of about 30  $\mu$ m [59]. These thicknesses can be achieved using Down Draw (DD) process [59]. However, producing glass at these thicknesses is extremely expensive and the surface becomes very rough. Additionally, flexible glass substrates are delicate and are not suitable for roll-to-roll processing. Glass substrates were not considered the ideal choice for substrates for flexible memory for all the reasons mentioned above.

#### 3. Polymers

Polymers are the most versatile and inexpensive circuit elements used in flexible electronics. They can be synthesized to have a wide variety of properties like high melting temperature, high flexibility, high strength, different CTEs and other properties [58]. In addition, their adhesion to metal thin films is usually good. They are also amenable to roll-to-roll processing because of their high flexibility, robustness and light weight. The low cost is because the polymer manufacturing process is a high volume process. The disadvantages of using polymers are that the glass transition temperature of most of these materials is quite low and the CTE of these materials is also quite high. Substantial changes have to be made to the traditional manufacturing process by replacing most unit processes with alternative low temperature unit processes. In spite of these disadvantages, these substrates showed the highest potential for use as substrates in flexible memory.

Polyimide is a polymer that has been used in the electronics manufacturing industry for a long time. It is extremely stable at high temperatures, allowing for processing temperatures as high as 350°C and strong enough to withstand the rigors of roll-to-roll processing. It does have a CTE of about 20 ppm, which is much higher than that of silicon. The fabrication process needs to be a low temperature process to prevent the substrate from deforming too much as the circuitry is manufactured over it. This polymer was used as a substrate for fabricating PMC flexible memory.

Polytetrafluoroethylene (PTFE) is another polymer that has traditionally been used in the electronics industry. It is also a higher temperature plastic and allows for processing temperatures up to 250°C. Unfortunately, it is not a very good dielectric. Also, it is not thermally stable because of a high CTE. While it shows flexibility, a few other polymers have already demonstrated a greater degree of flexibility. This substrate was not considered for manufacturing PMC memory.

Polyethylenes are a family of polymers that show significant promise as flexible substrates. Two of these in particular – polyethylene terephthalate (PET) and polyethylene naphthalate (PEN) are very flexible and have a reasonably low CTE. The disadvantage of these polymers is that the fabrication process have to be very low-temperature. These polymers have glass transition temperatures in the range of 100°C-200°C. These substrates have yet to be considered as substrates for flexible memory.

Polyimide is generally the most popular choice for a flexible substrate as it allows for more options when developing a manufacturing process. PET and PEN are the other two choices. However, they are only considered if transparency is a prerequisite.

# D. Review of solid electrolyte material systems and their compatibility with flexible substrates

A number of metal-glass combinations have been studied as solid electrolyte systems for some time now. A few of these electrolytes have shown great promise for use in memories, with the result that PMC devices with different material combinations can be fabricated on conventional rigid substrates. The choice of a solid electrolyte for flexible circuit applications is, however, significantly restricted by fabrication process considerations. Specifically, the solid electrolyte should conform to the following specifications:

- 1. The fabrication process of the material combination should be lower than the glass transition temperature of the substrate.

- 2. The material combination should adhere well to any underlying metal layer.

- 3. The modulus of elasticity of the solid electrolyte material should be comparable to the modulus of elasticity of the substrate to prevent cracking and de-adherence on flexing

- 4. The material combination must continue to retain its solid electrolyte properties even on flexing, so that the memory properties are reasonably stable even when the device is subjected to mechanical stress.

Some material combinations that are good candidates for the solid electrolyte are given below.

1. The silver-germanium selenide electrolyte

The Silver-Germanium Selenide (Ag-Ge-Se) electrolyte is extremely simple to fabricate. It is made by depositing a Germanium Selenide base glass (Ge<sub>x</sub>Se<sub>1-x</sub>, x < 0.33) layer on the bottom electrode by physical vapor deposition. A layer of silver, approximately 1/3rd the thickness of the glass layer, is then deposited over the glass. This material combination is then exposed to ultra-violet

Fig. 9. (a) Current-voltage characteristic of a PMC device with a programming current compliance of  $1\mu A$  (b) Resistance-voltage characteristic of the device. The ratio of the off to on state resistance is about 4 orders of magnitude [1].

(UV) light of wavelength 405 nm, at a power density of about 4 mW/cm<sup>2</sup> for about 20 minutes in order to dissolve the silver into the base glass to give the solid electrolyte [1]. In order to complete the device, the bottom electrode is made of an

electrochemically indifferent metal like nickel (Ni), while the top electrode is made of an easily oxidizable metal like silver (Ag).

The advantage of using the Ag-Ge-Se electrolyte stems primarily from the flexibility of the Ge-Se base glass, whose elastic modulus is very high and the low processing temperatures. The fabrication temperature of this electrolyte is almost room temperature, with the highest temperature being reached during physical vapor deposition of the glass and silver layers. No other high temperature processing step is required during fabrication as the electrolyte formation depends solely on the exposure to UV light. Another advantage of using this electrolyte is its low turn-on voltage of about 0.2 V for devices with a nickel (Ni) cathode [1].

#### 2. <u>The silver-germanium sulfide electrolyte</u>

The silver-germanium sulfide (Ag-Ge-S) electrolyte system produces much more stable resistance states than the Ag-Ge-Se system. The on-off resistance ratio is also about 50 times higher [2]. The turn-on (about 450 mV) and turn-off (about -250 mV) thresholds are also much higher [2], making this system a little more energy intensive than the Ag-Ge-Se system. The primary advantage of this system is that it is capable of withstanding the high back-end-of-line (BEOL) processing temperatures found in conventional silicon processing lines. However, the electrolyte needs an anneal at 430°C for about 15 minutes during fabrication [2], which makes it incompatible with most flexible substrates, especially those that are polymer-based. The higher processing temperatures and the higher energy requirements make this electrolyte system a less than ideal choice for the purpose of fabricating PMC memories on flexible substrates.

#### 3. <u>The copper-germanium sulfide electrolyte</u>

The Copper Germanium Sulfide (Cu-Ge-S) system exhibits lower programming resistance states than the Ag-Ge-S system, with the on-state resistance being about 15 k $\Omega$  and the off-state resistance being about 1 G $\Omega$  with a 10µA compliance current [2]. The write threshold (about 300 mV) and the erase threshold (less than 100mV) are also much lower than the Ag-Ge-S system [2], which makes it a low-power system. However, this system is very temperature sensitive, making the device characteristics very unpredictable as the temperature of operation is varied [2].

This is probably because copper is much more reactive electrochemically than silver, resulting electrochemical processes being much more dominant within the device than the externally applied programming currents and voltages. This system shows potential for use in the flexible substrate process. A greater understanding of the system is necessary before it can be used, however, since it is not known whether the electrochemical processes are accelerated when the system is subjected to mechanical stress.

#### 4. The copper-silicon dioxide electrolyte

The most important attribute that works in favor of the copper-silicon dioxide (Cu/SiO<sub>2</sub>) system is that the diffusion of copper through SiO<sub>2</sub> is very well-understood [26]. Another reason that this system is being investigated for applications as a solid electrolyte is that both materials are already available in conventional silicon manufacturing processes. However, this system is not suitable at all for flexible electronics applications. One reason for its

incompatibility is that the copper cannot diffuse into the SiO<sub>2</sub> matrix by photodiffusion as in the case of previous systems. This system requires a thermal diffusion step at  $610^{\circ}$ C for at least 15 minutes in order to form the solid electrolyte [60]. Another major disadvantage of this system is that the SiO<sub>2</sub> matrix is brittle and tends to crack rather than bend when subjected to mechanical stress. The on-off resistance ration is comparable to that of the Ag-Ge-S system with the write threshold (about 1.3 V) and the erase threshold (about -0.5 V) being slightly higher than those of the Ag-Ge-S system [60]. Thus, this electrolyte cannot be considered for flexible electronics applications, even though its switching behavior is comparable to the other electrolyte systems on conventional rigid substrates.

#### 5. <u>The copper-transition metal oxide electrolyte</u>

Thus far, the copper-tungsten oxide (Cu/WO<sub>3</sub>) system has been studied for applications as a solid electrolyte. This system shows great potential for use in flexible circuit applications. The primary reason for this conclusion is that the formation of this electrolyte is a room-temperature process, with the Cu diffusion into the WO<sub>3</sub> being governed only by exposure to UV light [3]. The off-state and on-state resistances differ by about 7 orders of magnitude and the programming currents are extremely low (about 1µA), resulting in very low power consumption [3]. The device exhibits a write threshold at around 400 mV and an erase threshold at around -200mV [3]. Preliminary retention testing shows that the devices based on this electrolyte show excellent performance, even at elevated temperatures. We are currently investigating the effects of mechanical stress on this system.

#### E. Mechanical properties of germanium selenide (Ge-Se) glass

Chalcogenide glasses are much less brittle than silicate glasses. This section discusses the mechanical properties of Ge-Se glasses as a specific

| Property                                            | Property value for various Ge/Se <sup>†</sup> |       |       |       |       |       |       |       |                    |

|-----------------------------------------------------|-----------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------|

|                                                     | 0/100 <sup>†</sup>                            | 5/95  | 10/90 | 15/85 | 20/80 | 25/75 | 30/70 | 40/60 | 100/0 <sup>±</sup> |

| $\langle r \rangle$                                 | 2                                             | 2.1   | 2.2   | 2.3   | 2.4   | 2.5   | 2.6   | 2.7   | 4                  |

| $\rho$ (g/cm <sup>3</sup> )                         | 4.28                                          | 4.31  | 4.34  | 4.36  | 4.37  | 4.36  | 4.32  | 4.36  | 5.15               |

| E (GPa)                                             | 10.25                                         | 11.05 | 12.08 | 13.80 | 14.73 | 16.05 | 17.90 | 22.38 | 123.5              |

| K (GPa)                                             | 9.60                                          | 10.01 | 10.43 | 11.22 | 11.47 | 12.21 | 12.64 | 16.43 | 70.95              |

| ν                                                   | 0.322                                         | 0.316 | 0.307 | 0.295 | 0.286 | 0.281 | 0.264 | 0.273 | 0.21               |

| H (GPa)                                             | 0.39                                          | 0.57  | 0.77  | 1.05  | 1.38  | 1.72  | 2.02  | 2.35  | 7.37               |

| H <sub>V</sub> (GPa)                                | 0.36                                          | 0.52  | 0.71  | 0.97  | 1.28  | 1.59  | 1.88  | 2.18  | 6.84               |

| $K_{*}$ (MPa·m <sup>1/2</sup> )                     | 0.16                                          | 0.09  | 0.12  | 0.22  | 0.28  | 0.22  | 0.20  | 0.16  | 0.59               |

| $K_{c,\text{theo}} (\text{MPa·m}^{1/2})^{\$}$       | 0.197                                         | 0.211 | 0.227 | 0.250 | 0.265 | 0.283 | 0.304 | 0.351 | 0.96               |

| $K_{c,\text{theo}} (\text{MPa·m}^{1/2})^{\text{T}}$ | 0.179                                         | 0.194 | 0.211 | 0.235 | 0.251 | 0.270 | 0.293 | 0.337 | 0.88               |

Table 1. Density, Elastic Modulus, Indentation Hardness and Toughness of Ge-Se glasses [61].

example of the properties of chalcogenide glasses. The goal of this section is to emphasize that chalcogenide glasses, and more specifically Ge-Se glasses, possess the necessary mechanical characteristics to be used in flexible electronics.

Ge-Se glasses are characterized by relatively low hardness values (0.39 GPa to 2.35 GPa) and fracture toughness values (0.1 MPa.m<sup>1/2</sup> and 0.28 MPa.m<sup>1/2</sup>) [61]. As a comparison, silicon dioxide (SiO<sub>2</sub>) films have hardness values between 7.9 GPa and 14.5 GPa [62] and fracture toughness values between 0.1 MPa.m<sup>1/2</sup> and 0.28 MPa.m<sup>1/2</sup> in air [63]. The low hardness values of Ge-Se films result in the brittleness factor being lower than that of silicate glasses. The brittleness factor is defined as shown below:

## Brittleness Factor= $\frac{\text{Hardness}}{\text{Fracture Toughness}}$ (1)

being lower than that of silicate glasses. Hardness and Young's Modulus of Ge-Se glasses increase with increasing germanium (Ge) content, but fracture toughness exhibits a maximum for  $Ge_{20}Se_{80}$  [61]. The Young's Modulus of Ge-Se glasses (between 10.25 GPa and 123.5 GPa) are also much lower than silicate glasses (between 73.1 GPa and 145 GPa) [61], which means that chalcogenide films demonstrate more elastic deformation for the same amount of stress than silicate glasses. The preceding discussion shows that chalcogenide glasses, and more specifically Ge-Se glasses, can be used in engineering applications that require that demand mechanical flexibility. Mechanical characteristics for different compositions of Ge-Se glass are given in Table 1.

#### *F. The memristance property*

The concept of the memristor was first introduced by Leon Chua in 1971 [64]. The original paper described the device as a two terminal device which relates the flux linkage with the charge. Two types of memristors were discussed in [64]. The flux-controlled memristor, which is of interest, is described by the set of equations given below:

$$i(t) = W(\Phi(t)) \cdot v(t)$$

(1)

$$W(\Phi) = \frac{dq(\Phi)}{d\Phi}$$

(2)

Here i(t) is the time-dependent current, v(t) is the voltage,  $\Phi(t)$  is the flux linkage and q(t) is the charge, which is dependent on the flux linkage. This was considered the fourth circuit element, along with the inductor, the capacitor and the resistor. Although an electromagnetic field interpretation was developed and active memristor circuits were demonstrated, no passive circuits, i.e. one without an internal power supply, were demonstrated by the original paper, and were unknown at the time. A later paper, by Chua and Kang [65], generalized the concept of the memristive system to a much broader class of systems which are described by a set of equations given below:

$$\frac{dx}{dt} = f(x,v,t) \quad (3)$$

$$i = G(x,v,t) \cdot v(t) \quad (4)$$

where i(t) and v(t) are the time-dependent current and voltage respectively and x is a state variable, which does not necessarily have any correlation with any physical quantity within the system. This set of equations describes a voltagecontrolled memristance system.

Interest in the memristance system was renewed when a team from HP published research demonstrating proof on concept for such a device [66]. The device comprised a thin film of titanium dioxide (TiO<sub>2</sub>) with platinum (Pt) electrodes. The memristive behavior was attributed to the movement of oxygen vacancies within the device in response to an applied voltage. The formation of conductive filament bridges because of the arrangement of oxygen vacancies was said to be responsible for the observed changes in resistance of the device [67].

Many other candidates for passive memristors have emerged since this time. These include the oxide-based memristor integrated with CMOS logic [68],

spin-torque based memristors [69], the flexible solution-processed memristor [70] and the gadolinium oxide ( $Gd_2O_3$ ) based memristor [71]. Each of these memristors can be optimized based on the requirements of the individual electronic application. The model that is proposed for PMC based switches in the subsequent sections demonstrates that these devices also show memristive behavior.

#### SILVER BASED SOLID ELECTROLYTE INTERCONNECTS

The previous section discussed the mechanical properties of chalcogenide glasses. It shows that the germanium selenide glass is the best candidate for a glass which is capable of withstanding mechanical stress as it is the most elastic. The silver doped germanium selenide system has been studied extensively as a solid electrolyte which can be used as a resistance change element. The ability of controlling device resistance based on the application of a voltage is a useful property for interconnects in flexible electronics applications. This property ensures that if a metal layer overlying a solid electrolyte layer fractures, then the signal voltages will promote the growth of a metallic electrodeposit between the edges of the fracture. Ideally, this would restore the resistance of the interconnect to its original value, thus greatly improving the reliability of the interconnect. This section discusses efforts in using this system to demonstrate self-healing interconnects. It discusses the fabrication, characterization and the reliability of these interconnect structures..

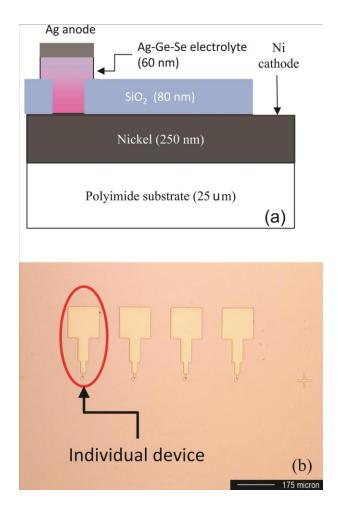

#### A. Fabrication

The interconnect test structures were fabricated directly on a R/Flex 1000 flexible substrate from Rogers Corp. which consists of a 25  $\mu$ m thick polyimide layer on a 500  $\mu$ m (approximate thickness) copper sheet. The polyimide has a glass transition temperature of approximately 250°C, which limits the processing temperatures used during subsequent processing. The fabrication process is based on the process outlined in [55]. However, the process has been adapted to be suitable for flexible substrates, based on previous work in this area [7, 72]. The

flexible material was first mounted on a rigid silicon substrate using double-sided carbon tape. This tape, typically utilized in electron microscope sample mounting applications, can withstand the moderate temperatures used in test structure fabrication while maintaining adhesion and minimizing any distortion in the flexible element due to temperature stresses. The multi-layer substrate was rinsed

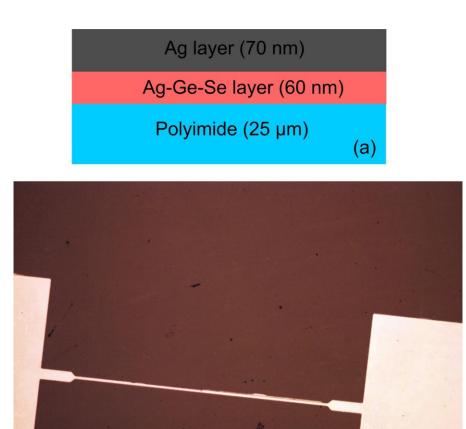

Fig. 10. (a) Schematic of the self-healing interconnect structure on polyimide, consisting of a 70 nm thick Ag layer on Ag-Ge-Se solid electrolyte. (b) Optical microscope image showing the top view of the structure. The test pattern is 10  $\mu$ m wide and 775 $\mu$ m long, terminating in probe pads at either end.

(b)

175 micron

using acetone, ethanol and methanol in a pre-fabrication cleaning step. As part of the lift-off patterning process, AZ 4330 photoresist was spun onto the surface of the polyimide at 3500 rpm for 30 sec. The sample was then soft-baked at 80°C for 17 min. in a convection oven in order to evaporate the resist solvent. This oven was used instead of a conventional hotplate because the thermal conductivities of the polyimide and mounting tape are low and hence hotplate soft-baking, as used for silicon substrates alone, would not be as effective. The photolithography step involved exposure of the resist to ultra-violet light at an intensity of 5 mW/cm<sup>2</sup> for 45 seconds through a dark field mask containing the interconnect pattern. Immersion in AZ 300 MIF developer for 90 sec was used to develop the pattern in the resist. The layers that make up the test structures were then deposited by thermal evaporation.

The thin films used to create the solid electrolyte comprised a 60 nm thick germanium selenide ( $Ge_{33}Se_{67}$ ) glass layer and a 30 nm thick silver (Ag) layer. The Ag layer was photo-dissolved into the  $Ge_{33}Se_{67}$  layer using a blanket UV exposure in the exposure system for 20 minutes to create the Ag-Ge-Se solid electrolyte [73]. The top Ag layer which forms the 70 nm thick interconnect lines was then deposited on the electrolyte.

A lift-off step was then carried out in acetone to pattern the electrolyte and interconnect layers. The flexible substrate was then de-bonded from the rigid substrate for stressing and characterization. The final device structure is shown in Fig. 10(a). A second set of control samples, with 70 nm thick Ag lines directly on the polyimide and no solid electrolyte layer, was also fabricated using the same mask. The average resistances of both types of interconnect (including contact resistance), as measured using tungsten probes on micromanipulators connected to an Agilent 4155C, were approximately 75  $\Omega$ . Note that the sub-100 nm thickness of the metal combined with the inherent elasticity of the Ag-Ge-Se electrolyte allows these structures to be highly flexible [61] but it is still possible to induce failure using high tensile stress via small radius bending.

#### B. Characterization

This section outlines the various characterization methods used to investigate the behavior of the device. The first few tests were used to validate the self-healing property of the Ag/Ag-Ge-Se bilayer interconnect. The second series of tests were used to characterize the reliability of such an interconnect. Preliminary results on the reliability of the interconnect to both DC and AC voltages were investigated.

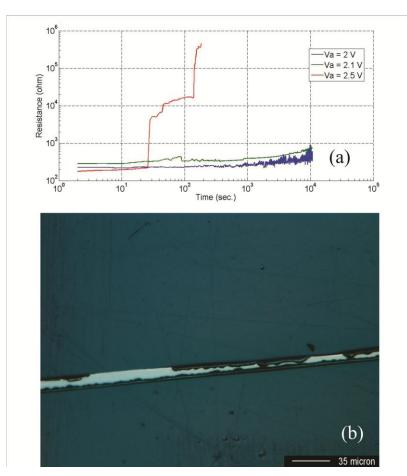

### 1. <u>Failure resistance and self-healing response of the solid electrolyte</u> interconnect

In order to test the self-healing response of the Ag/Ag-Ge-Se bilayer, a sample with these interconnects on polyimide was subjected to tensile stress by bending it around a mandrel of radius 5 mm for 5 minutes. The process was repeated 5 times to assure that a significant number of the interconnects had failed due to cracking. This process was repeated on a sample of Ag interconnects on polyimide. The stressed substrates were then flattened out for electrical characterization.

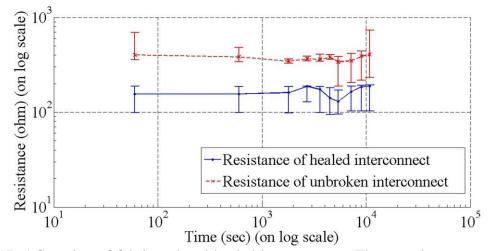

Fig. 11 shows examples of failed line resistance for both sample types. The resistance was measured using a 10 mV signal to minimize voltage-induced changes through electrochemical transport in the material. The measurement was

Fig. 11. Resistance of two failed Ag lines on Ag-Ge-Se solid electrolyte (red) and Ag directly on polyimide (blue).

made over a 100 second time period to ensure that the break resistances were stable. The results show that the failed interconnect lines formed on the solid

Fig. 12. Healed interconnect resistance plotted against the reciprocal of the current limit (2V DC healing bias).

electrolyte have significantly lower resistances (between  $10^6$  and  $10^7 \Omega$ ) than those deposited directly on polyimide (> $10^8 \Omega$ ). These results suggest that the solid electrolyte itself does not fracture during mechanical stressing due to its pliability and maintains at least partial continuity.

Fig. 12 shows the resistance of healed interconnect lines following the application of a 2V DC bias as a function of the reciprocal of the compliance current limit  $1/I_{lim}$ . The goal was to validate the fact that the electrochemical behavior of the device was consistent with the Ag-Ge-Se electrolyte system. As expected, the results reveal that the resistance of the healed interconnects decreases as the current limit increases. As described previously, this is a characteristic of devices based on PMC technology. The slope of the plot in Fig. 12 yields a V<sub>th</sub> of 122 mV for these interconnect samples, which is close to the electrodeposition voltage seen in Ag-Ge-Se memory devices [1].

#### 2. <u>Analysis of the self-healing process</u>

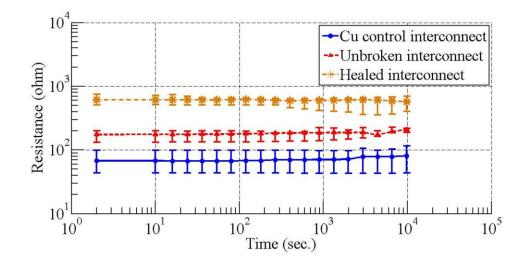

In the next set of experiments, three resistance states were examined in order to further characterize the self-healing process; (1) the resistance of the unbroken interconnect, (2) the resistance of the broken interconnect, and (3) the resistance of the interconnect after the healing voltage is applied. The samples were mechanically stressed as before and a 2V bias with a compliance current of 10 mA was used as the healing stimulus in all cases to ensure a low electrodeposit resistance. The resistance distribution shown in Fig. 13 is the result of testing 10 devices. The 3 phases of testing are shown: the as-fabricated resistance case, the resistances after the devices have been fractured and the resistances after the devices have been healed. The fabricated 70 nm thick Ag interconnect has a length of 775  $\mu$ m and a width of 10  $\mu$ m which gives a theoretical resistance of approximately 45  $\Omega$ , based on the thin film resistivity value of 127  $\mu\Omega$ .cm given

Fig. 13. Interconnect resistance distributions before fracture, after fracture and after healing. Each box represents the result of 10 samples.

in [74]. The average resistance measured before fracture is 30  $\Omega$  higher than this, which we believe is due to thickness variations in the film following deposition and the series resistance of the probe contacts and test system connections. We see that the resistances of the broken and healed states differ by about 3 orders of magnitude, however, the difference in resistance between the healed and unbroken interconnects is only a few tens of ohms on average for this compliance current. This validates the healing process, in which the goal is to restore the resistance of the interconnect close to its original value.

The elevated resistance after fracture given in Fig. 13 represents the resistance through the unbroken flexible solid electrolyte because of the lack of

continuity in the overlying Ag layer. This resistance can be used to estimate the size of the gap, assuming the crack spans the full width of the interconnect and the electrolyte maintains its original thickness and continuity after stressing. Since the resistivity of the solid electrolyte is in the order of 100  $\Omega$ .cm [4] and the resistance of the fracture (1.25 M $\Omega$ ) may be calculated as shown below:

$$\frac{\rho_{\text{Ge-Se}} \cdot L}{W \cdot t} = R_{\text{off}} \qquad (1)$$

The estimated length L for a 60 nm thick, 10  $\mu$ m wide (W) electrolyte in the gap is 750 nm. Note that such a small gap is difficult to image with an optical microscope and exposure to electrons in a scanning electron microscope stimulates electrodeposit growth which masks the gap features. Hence, we can only infer the break dimensions from the above calculations. The difference between the original and the healed resistance states ( $\Delta R$ ) is 37  $\Omega$  and this is the effective resistance of the electrodeposit itself. The bridging electrodeposit is likely to grow in a short dendritic pattern on the surface of the electrolyte between the fractured edges of the interconnect [75] but we can simplify this by assuming that the deposited connection can be approximated by a bar with an equilateral triangular cross-section which spans the length of the crack. Such geometry is typical in thick surface electrodeposits, in which the base of the feature is continually widened as the top is pushed upwards by the electrodeposition process [76]. For this geometry, we use the following set of equations to determine the dimensions of the electrodeposit:

$$\frac{\rho_{\text{electrodeposit}} \cdot L}{A} = \Delta R \qquad (2)$$

$$A = a^2 \frac{\sqrt{3}}{4} \qquad (3)$$

Here *a* is the length of the side and A is the area of the equilateral triangle respectively.

Using a value of 127  $\mu\Omega$ .cm for the resistivity of the Ag electrodeposit [74], the side of the equilateral triangle was calculated as 243 nm. The volume of the silver electrodeposit (V) is calculated to be  $19.3 \times 10^{-3} \ \mu\text{m}^3$  using V=A·L, where A is the area of cross-section of the electrodeposit and L is the crack length as before. The number of silver atoms that need to be reduced in order to produce this volume is then calculated using the following equation:

$$N_{Ag} = \frac{\text{Density}_{Ag} \times \text{Volume}_{Ag} \times \text{NA}}{\text{At. Wt}_{Ag}}$$

(4)

The density of Ag is 10.49 g/cm<sup>3</sup>, the atomic weight of Ag is 108, and the Avogadro number (NA) is  $6.023 \times 10^{23}$  atoms/mol. This gives us a value of  $1.13 \times 10^{9}$  atoms in the electrodeposit.

The electrodeposition current during the healing process is assumed to be limited by the initial fracture resistance (1.25 M $\Omega$ ) and the healing voltage (2V), i.e., 1.6  $\mu$ A. Note that the much higher compliance current is used to maintain sufficient voltage across the electrodeposit in order to continue the electrodeposition process and reach the lowest resistance. Most of this current flows through the metallic electrodeposit but the current responsible for continued deposition will still be flowing in the electrolyte and hence will remain in the  $\mu$ A range during the entire growth time. The number of Ag ions to be reduced is equivalent to the number of atoms in the electrodeposit. These ions are reduced according to

$$Ag \rightarrow Ag^+ + e^-$$

. (5)

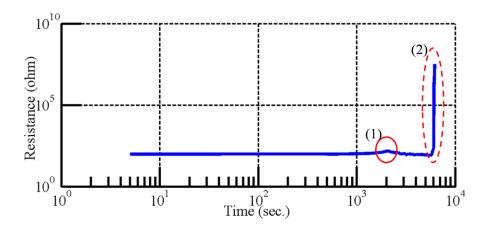

Fig. 14. Analysis of measured resistance values of interconnects with and without an underlying solid electrolyte layer. A constant current of 100 uA is applied to the interconnects for 3 hours.

requiring one electron per  $Ag^+$  ion for reduction. The time required for the break to heal is calculated using the equation given below:

$$t_{\text{heal}} = \frac{N_{\text{Ag}} \times 1.6 \times 10^{-19} \text{ C}}{I_{\text{min}}}$$

(6)

The numerator represents the total charge required to create the electrodeposit.

Using this, the calculated value for healing time is  $113 \ \mu s$ .

#### C. Reliability testing of the interconnects