# Predictive Modeling for Extremely Scaled CMOS and Post Silicon Devices

by

Chi-Chao Wang

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved March 2011 by the Graduate Supervisory Committee

Yu Cao, Chair Chaitali Chakrabarti Lawrence Clark Dieter Schroder

ARIZONA STATE UNIVERSITY

May 2011

#### **ABSTRACT**

To extend the lifetime of complementary metal–oxide–semiconductors (CMOS), emerging process techniques are being proposed to conquer the manufacturing difficulties. New structures and materials are proposed with superior electrical properties to traditional CMOS, such as strain technology and feedback field-effect transistor (FB-FET). To continue the design success and make an impact on leading products, advanced circuit design exploration must begin concurrently with early silicon development. Therefore, an accurate and scalable model is desired to correctly capture those effects and flexible to extend to alternative process choices.

For example, strain technology has been successfully integrated into CMOS fabrication to improve transistor performance but the stress is non-uniformly distributed in the channel, leading to systematic performance variations. In this dissertation, a new layout-dependent stress model is proposed as a function of layout, temperature, and other device parameters. Furthermore, a method of layout decomposition is developed to partition the layout into a set of simple patterns for model extraction. These solutions significantly reduce the complexity in stress modeling and simulation.

On the other hand, semiconductor devices with self-feedback mechanisms are emerging as promising alternatives to CMOS. Fe-FET was proposed to improve the switching by integrating a ferroelectric material as gate insulator in a MOSFET structure. Under particular circumstances, ferroelectric capacitance is effectively negative, due to the negative slope of its polarization-electrical field

curve. This property makes the ferroelectric layer a voltage amplifier to boost surface potential, achieving fast transition. A new threshold voltage model for Fe-FET is developed, and is further revealed that the impact of random dopant fluctuation (RDF) can be suppressed.

Furthermore, through silicon via (TSV), a key technology that enables the 3D integration of chips, is studied. TSV structure is usually a cylindrical metal-oxide-semiconductors (MOS) capacitor. A piecewise capacitance model is proposed for 3D interconnect simulation. Due to the mismatch in coefficients of thermal expansion (CTE) among materials, thermal stress is observed in TSV process and impacts neighboring devices. The stress impact is investigated to support the interaction between silicon process and IC design at the early stage.

# TABLE OF CONTENTS

| LIST OF T  | ΆE  | BLES   |                                               | Page<br>v |

|------------|-----|--------|-----------------------------------------------|-----------|

| LIST OF FI | IGI | URES   |                                               | vi        |

| CHAPTER    |     |        |                                               | 1         |

|            | 1.  | INTROE | DUCTION                                       | 1         |

| 2          | 2.  | MODEL  | ING OF LAYOUT-DEPENDENT STRESS EFFECT         | ·6        |

|            |     | 2.1.   | Introduction                                  | 6         |

|            |     | 2.2.   | Compact Stress Models                         | 12        |

|            |     |        | 2.2.1. Bathtub Stress Distribution            | 12        |

|            |     |        | 2.2.2. Layout Dependence                      | 15        |

|            |     |        | 2.2.3. Equivalent Low-Field Mobility          | 19        |

|            |     |        | 2.2.4. Velocity in the Saturation Region      | 23        |

|            |     |        | 2.2.5. Strain Induced Threshold Voltage Shift | 24        |

|            |     |        | 2.2.6. Other Secondary Effects                | 26        |

|            |     | 2.3.   | Model Validation                              | 28        |

|            |     | 2.4.   | Design Application                            | 33        |

|            |     |        | 2.4.1. Vertical Layout Decomposition          | 33        |

|            |     |        | 2.4.2. Lateral Layout Decomposition           | 35        |

|            |     |        | 2.4.3. Circuit Performance Benchmark          | 37        |

|            |     | 2.5.   | Chapter Summary                               | 39        |

| •          | 3.  | MODI   | ELING OF FE-FET AND IMPLICATIONS              | ON        |

|            |     | VARI   | ATION-INSENSITIVE DESIGN                      | 40        |

|            |     | 3.1.   | Introduction                                  | 40        |

| Chapter  |          | Pa                                            | age |

|----------|----------|-----------------------------------------------|-----|

|          | 3.2.     | Compact Modeling of Fe-FET                    | .45 |

|          | 3.3.     | Implication of Performance Variability        | .54 |

|          | 3.4.     | Chapter Summary                               | .60 |

| 4        | . MODEL  | ING OF THROUGH SILICON VIA CAPACITAN          | CE  |

|          | AND      | THE STRESS EFFECT                             | .62 |

|          | 4.1.     | Introduction                                  | .63 |

|          | 4.2.     | Modeling of TSV Resistance and Capacitance    | .66 |

|          |          | 4.2.1. TSV Resistance                         | .66 |

|          |          | 4.2.2. TSV Capacitance                        | .67 |

|          |          | 4.2.3. Trade-off between Performance and Area | 75  |

|          | 4.3.     | Impact of TSV Stress on Neighbor Devices      | .80 |

|          | 4.4.     | Chapter Summary                               | .86 |

| 5        | .CONCLUS | SION AND FUTURE WORK                          | .88 |

|          | 5.1.     | Thesis Conclusion                             | .88 |

|          | 5.2.     | Future Work                                   | .90 |

| REFERENC | CES      |                                               | 92  |

# LIST OF TABLES

| Table |                                                               | Page |

|-------|---------------------------------------------------------------|------|

|       | 4.1. Material property for Coefficients of Thermal Expansions | 80   |

# LIST OF FIGURES

| Figure |                                                                             | Page |

|--------|-----------------------------------------------------------------------------|------|

|        | 1.1. Illustration of strain technology.                                     | 2    |

|        | 2.1. Top view of stress contours in a five-finger layout pattern with       |      |

|        | SiGe embedded in source/drain area                                          | 8    |

|        | 2.2. The stress distribution in the channel and the equivalent stress       |      |

|        | levels for strain-induced shifts of $V_{\text{th}}$ and mobility            | 9    |

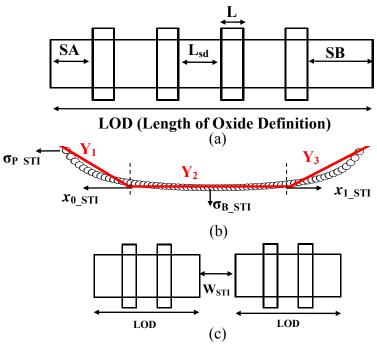

|        | 2.3. Modeling approach of the mechanical stress.                            | 12   |

|        | 2.4. Modeling of STI stress distribution                                    | 14   |

|        | 2.5. Modeling of the layout dependence on channel length and                |      |

|        | source/drain diffusion length.                                              | 17   |

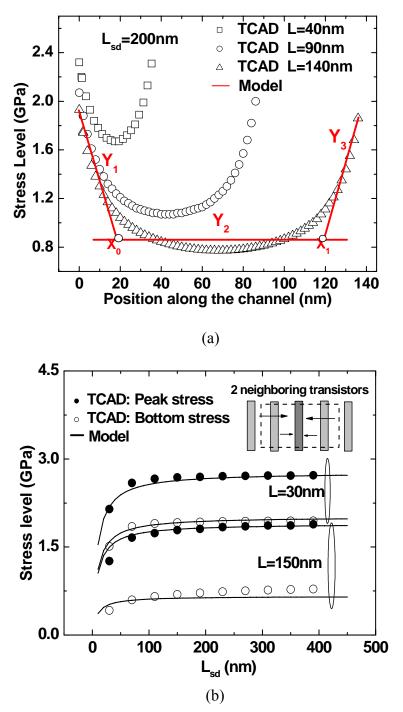

|        | 2.6. Modeling of width dependence on mobility                               | 22   |

|        | 2.7. Band diagram of strained-Si NMOSFET                                    | 24   |

|        | 2.8. Simulated band diagram along the channel.                              | 25   |

|        | 2.9. DSL induced hole mobility variation with dependence on                 |      |

|        | channel length and source/drain length                                      | 28   |

|        | 2.10. STI stress induced mobility variation with dependence on              |      |

|        | gate width                                                                  | 29   |

|        | 2.11. Equivalent mobility with dependence on temperature                    | 30   |

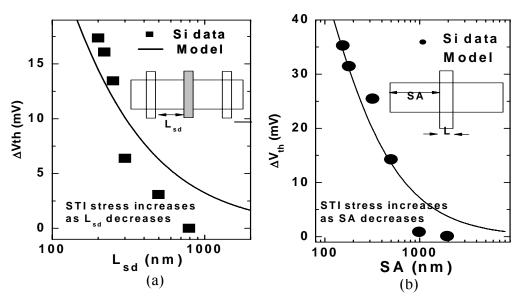

|        | 2.12. STI induced $V_{th}$ shift with dependence on $L_{sd}$ and $SA$       | 30   |

|        | 2.13. eSiGe induced $V_{\text{th}}$ shift with dependence on channel lenght |      |

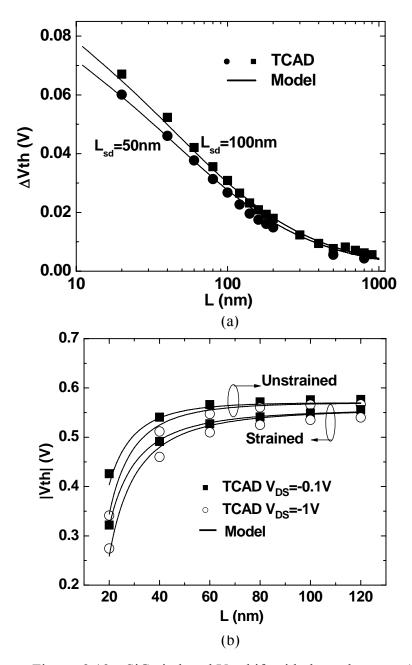

|        | and DIBL effect.                                                            | 31   |

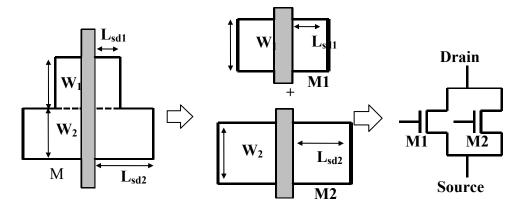

|        | 2.14. The decomposition along the width direction                           | 32   |

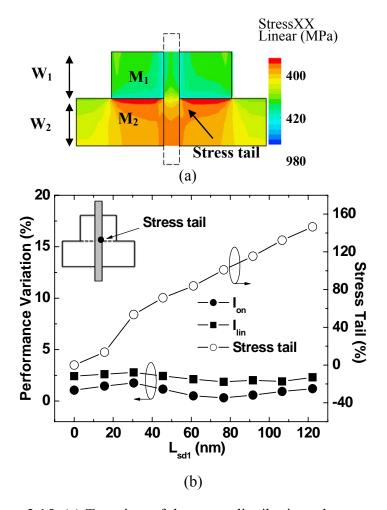

| Figure | 2.15. | Top view of the stress distribution with stressor applied to            | Page |

|--------|-------|-------------------------------------------------------------------------|------|

|        |       | S/D area                                                                | 34   |

|        | 2.16. | Method for lateral decomposition.                                       | 36   |

|        | 2.17. | Layout patterns of two NAND3 gates with the same size,                  |      |

|        |       | with SiGe in source/drain only.                                         | 37   |

|        | 2.18. | The systematic delay variation due to layout dependent                  |      |

|        |       | stress effect                                                           | 38   |

|        | 3.1.  | The energy landscape of a ferroelectric and regular capacitor           | 41   |

|        | 3.2.  | Series capacitance as a voltage divider                                 | 42   |

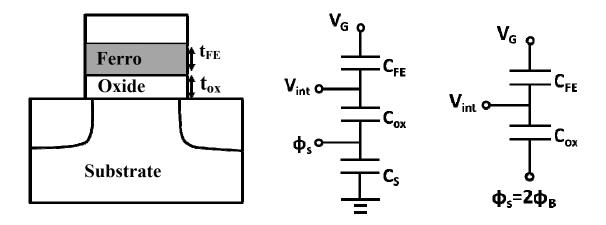

|        | 3.3.  | (a) Cross-section of Fe-FET. (b) The equivalent capacitance             |      |

|        |       | model in the sub- $V_{\text{th}}$ region (c) The capacitance model in   |      |

|        |       | the super-V <sub>th</sub> region.                                       | 46   |

|        | 3.4.  | Integration of the ferroelectric material into traditional              |      |

|        |       | MOSFET model                                                            | 49   |

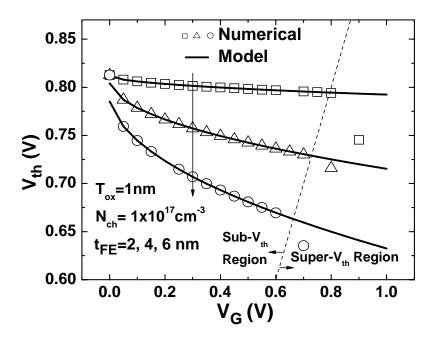

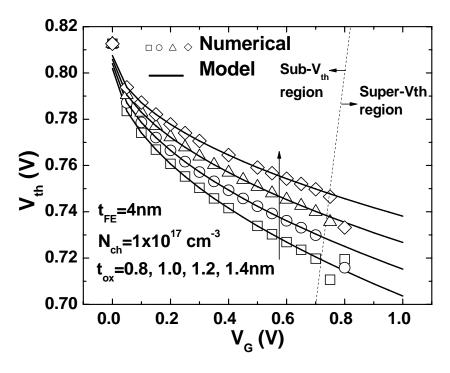

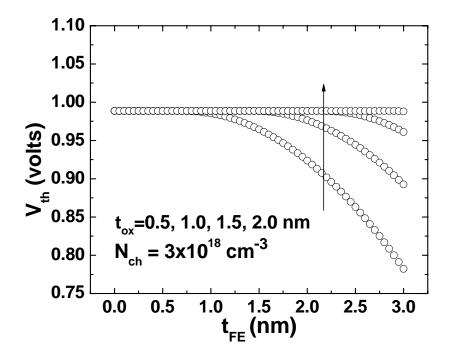

|        | 3.5.  | The dependence of $V_{th}$ on gate voltage and $t_{FE}$                 | 51   |

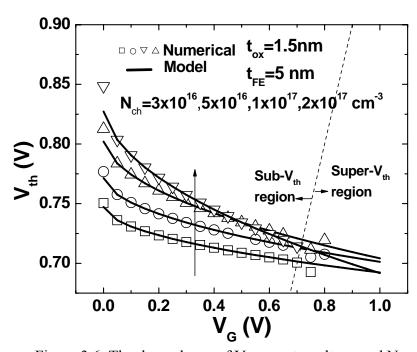

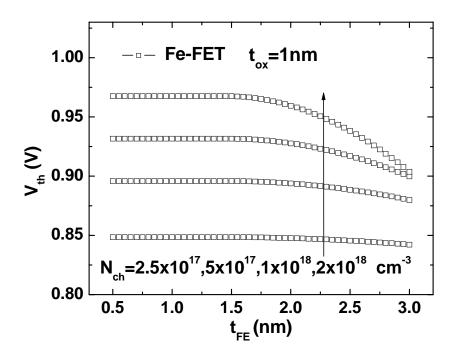

|        | 3.6.  | The dependence of $V_{th}$ on gate voltage and $N_{ch}$                 | 51   |

|        | 3.7.  | . The dependence of $V_{\text{th}}$ on gate voltage and $t_{\text{ox}}$ | 52   |

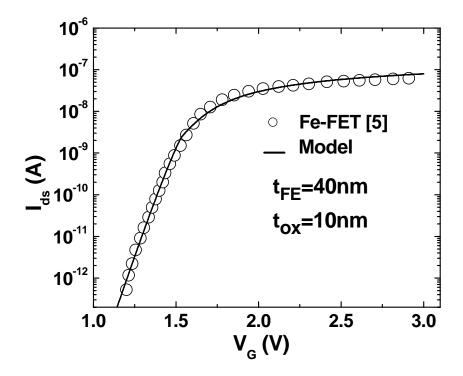

|        | 3.8.  | The matching between model prediction and measurement                   |      |

|        |       | data                                                                    | 53   |

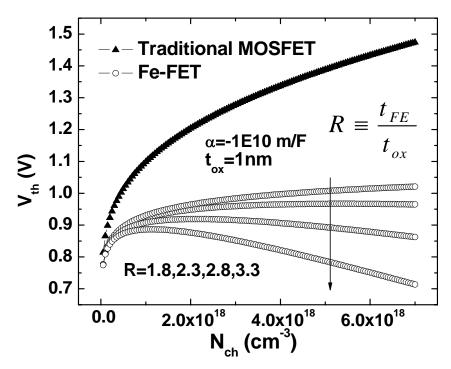

|        | 3.9.  | Dependence of $V_{th}$ on $N_{ch}$ . With the intrinsic feedback        |      |

|        |       | mechanism, $V_{th}$ can be tuned to be insensitive to channel           |      |

|        |       | doping                                                                  | 55   |

| Figure |                                                                                                 | Page |

|--------|-------------------------------------------------------------------------------------------------|------|

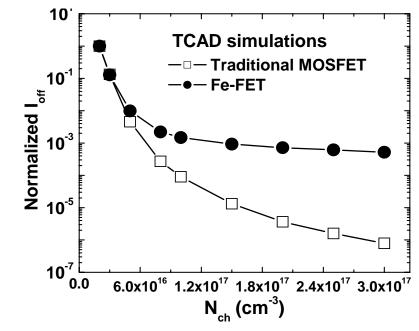

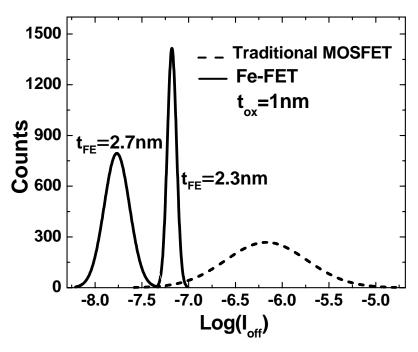

|        | 3.10. TCAD simulation of normalized off-state current for                                       |      |

|        | traditional MOSFET and Fe-FET                                                                   | 56   |

|        | 3.11. Dependence of $V_{th}$ on $t_{FE}$ and $t_{ox}$ in Fe-FET.                                | 56   |

|        | 3.12. Dependence of $V_{th}$ on $t_{FE}$ and $N_{ch}$ . Higher $N_{ch}$ increases $t_{FE}$ -    |      |

|        | induced V <sub>th</sub> variation                                                               | 58   |

|        | 3.13. The off-state current distribution under RDF, with the same                               |      |

|        | on- current                                                                                     | 59   |

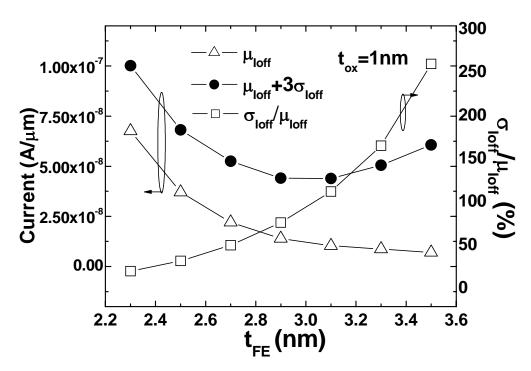

|        | 3.14. The mean value ( $\mu_{loff}$ ), standard derivation ( $\sigma_{loff}$ ), and the         |      |

|        | worst case ( $\mu_{\text{Ioff}} +  3\sigma_{\text{Ioff}})$ of off-state current, at a fixed on- |      |

|        | state current.                                                                                  | 60   |

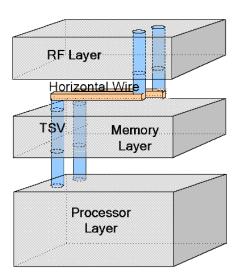

|        | 4.1. In 3D-IC, the heterogeneous chips are integrated vertically by                             |      |

|        | through silicon vias (TSVs).                                                                    | 63   |

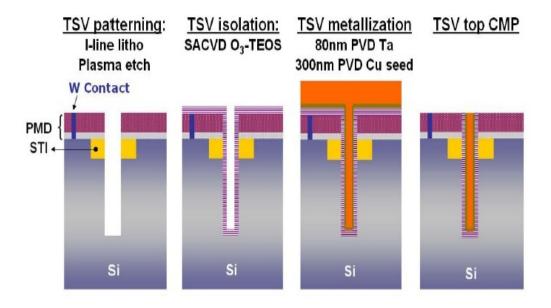

|        | 4.2. TSV process flow                                                                           | 64   |

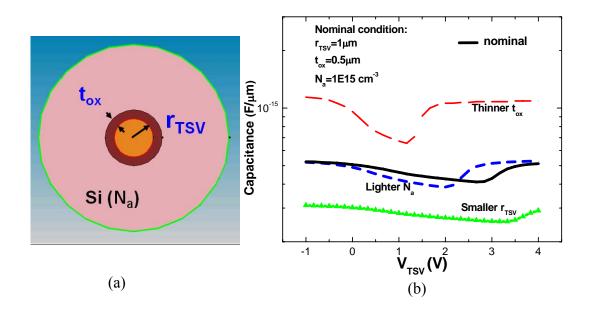

|        | 4.3. (a) TSV simulation structure with circular cross-section. (b)                              |      |

|        | TSV capacitance for different geometry parameters and                                           |      |

|        | dopant concentrations.                                                                          | 67   |

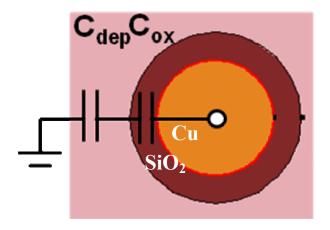

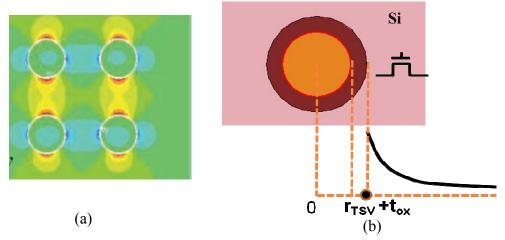

|        | 4.4. Contour of electrical field distribution in the silicon substrate                          | 71   |

|        | 4.5. Schematic of series capacitance of depletion capacitance and                               |      |

|        | oxide capacitance.                                                                              | 72   |

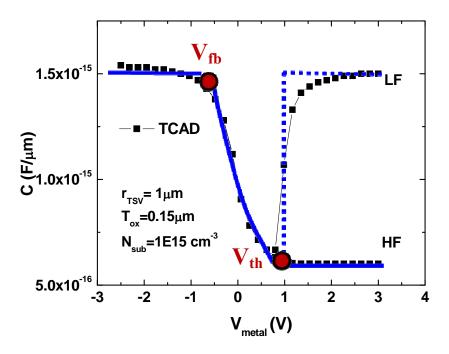

|        | 4.6. Compact capacitance model                                                                  | 73   |

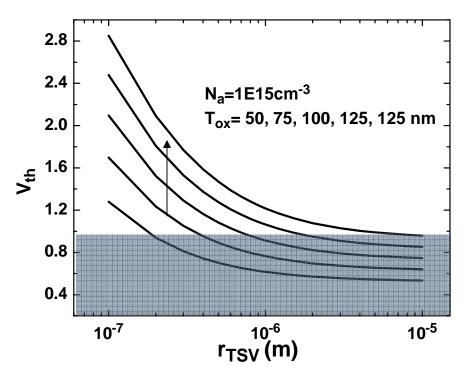

|        | 4.7. Threshold voltage varies with the radius of copper for different                           |      |

|        | ovida thickness                                                                                 | 74   |

| Figure |                                                                      | Page |

|--------|----------------------------------------------------------------------|------|

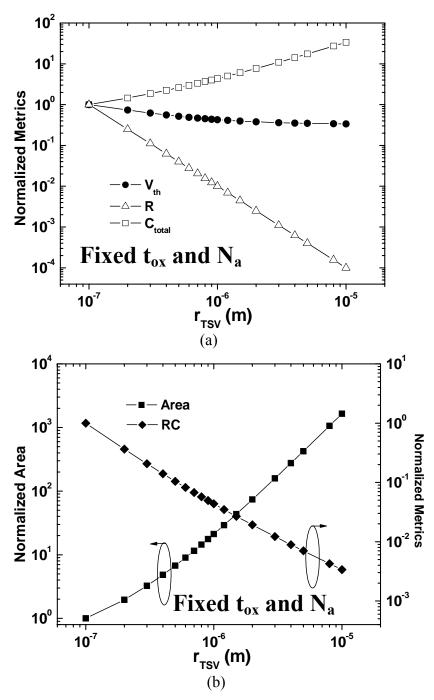

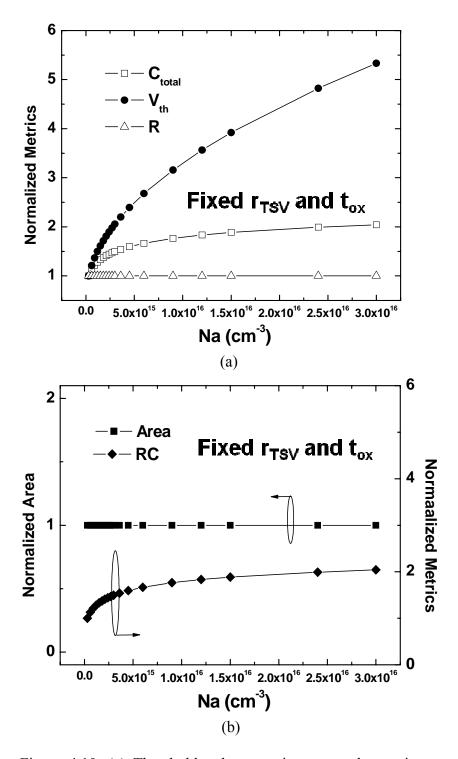

|        | 4.8. (a) threshold voltage, resistance, and capacitance change with  |      |

|        | various metal radiuses. (b) trade-off between RC delay and           |      |

|        | TSV area.                                                            | 76   |

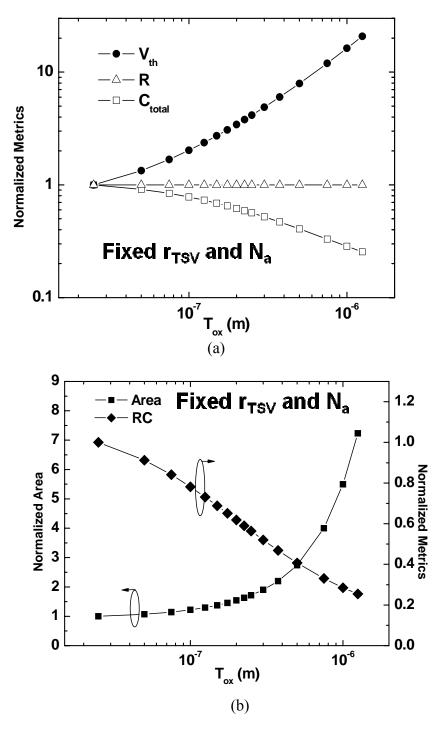

|        | 4.9. (a) threshold voltage, resistance, and capacitance change with  |      |

|        | various $T_{ox}$ . (b) trade-off between RC delay and TSV area       | 77   |

|        | 4.10. (a) threshold voltage, resistance, and capacitance change with |      |

|        | various N <sub>a</sub> . (b) N <sub>a</sub> does not impact TSV area | 79   |

|        | 4.11. (a) Stress distribution (b) schematic of stress profile in     |      |

|        | silicon substrate                                                    | 82   |

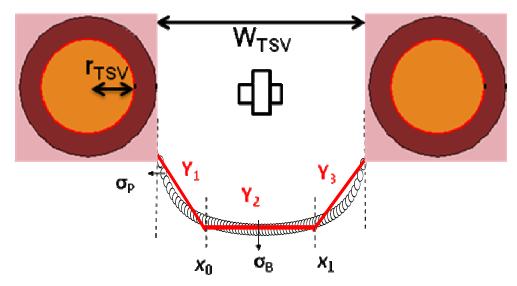

|        | 4.12. Linear piecewise stress model to capture the bathtub stress    |      |

|        | profile between two TSVs.                                            | 83   |

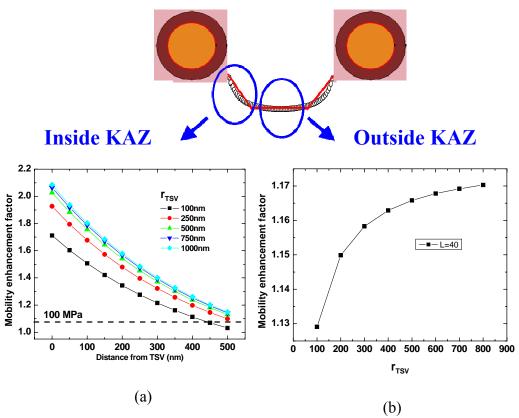

|        | 4.13. Characteristics for a device placed (a) inside the keep-away   |      |

|        | zone (b) outside the keep-away zone                                  | 84   |

|        | 4.14. Trade-off between TSV area and the influence of mobility       |      |

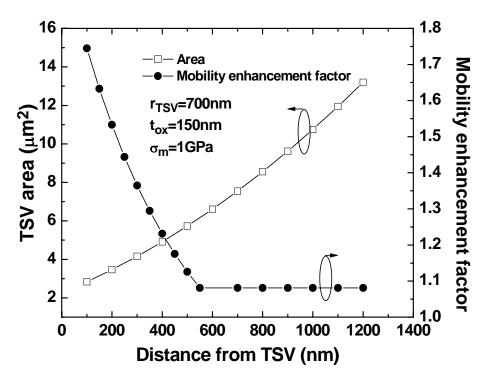

|        | enhancement factor                                                   | 86   |

#### CHAPTER 1

### INTRODUCTION

For the past decades, transistor performance has been consistently improved by scaling down the device feature size by following Moore's law stating that the number of transistors in an integrated circuit doubles every two years. The 2009 International Technology Roadmap for Semiconductors [1], predicts that the half pitch of high-performance logic technology will shrink to 11.9 nm and the equivalent oxide thickness (EOT) will scale down to 0.59 nm by 2020. When the device dimension is further scaled, the property of carrier transportation will change and enter the region of ballistic transportation. Moreover, the oxide thickness is scaled to 1nm, about twice the silicon lattice, implying the scaling is approaching the physical limits to the atomistic level. With the relentless scaling of CMOS technology, many secondary effects become more pronounced, such as drain induced barrier lowering (DIBL) effect, process variations, gate tunneling leakage, mobility degradation, and increasing power consumption. These secondary effects lead to dramatic challenges to robust circuit design and system integration.

To extend the lifetime of CMOS, emerging process techniques are proposed to conquer the manufacturing difficulties. Strain technology is being introduced to elevate carrier mobility to improve device performance by applying mechanical stress to the transistors [2]. On the other hand, novel devices with new structures and materials are proposed with superior electrical properties to traditional CMOS, such as CNT-FET [3] and FB-FET [4], for the nanometer era.

To continue the design success and make an impact on leading products, advanced circuit design exploration must begin concurrently with early silicon development. Therefore, an accurate and scalable model is desired to correctly capture those effects and is flexible to extend to alternative process choices.

With scaling of oxide thickness, threshold voltage decreases and results in an increasing off-state leakage. DIBL effect is another major challenge during scaling of CMOS technology. When drain voltage is applied to a short-channel device, the energy barrier height between source and drain is lowered, leading to the decrease of threshold voltage and increasing off-state leakage. To maintain the scaling criteria of leakage power consumption, V<sub>th</sub> needs to be kept in a certain value; therefore more channel dopants are introduced to maintain the threshold voltage. However, increased doping concentration degrades carrier mobility and

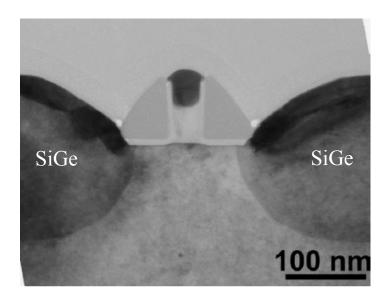

Figure 1.1 Illustration of eSiGe technology [75]

reduces the driving current. Strain technology, which employs mechanical stress to alter band structure of silicon and reduces carrier effective mass and scattering rate, is introduced to elevate carrier mobility for continual scaling, as shown in Fig. 1.1. Therefore, carriers can move faster and device performance is improved. Strain technology has been successfully integrated into CMOS fabrication to enhance carrier transport properties since 90nm node. However, since the stress is non-uniformly distributed in the channel, the enhancement in carrier mobility, velocity, and threshold voltage shift strongly depend on circuit layout patterns, leading to extra process variations. A compact stress model that physically captures this behavior is essential to bridge the process technology with design optimization.

The other scaling issue is management of power consumption. As the scaling is approaching the physical limit down to nanometer regime, the fundamental limits on minimum operational voltage and switching energy of transistors is restricted by the subthreshold slope [5]. In a MOSFET, the gate voltage must be changed at least by 2.3kT/q to change subthreshold current by ten times. At room temperature, 60mV is the minimum value required to modulate subthreshold current by an order of magnitude. To overcome this limit, new devices with self-feedback mechanism such as Ferro-electrical FET (Fe-FET) [6] is proposed to achieve the steep subthreshold slope, lowering the switching energy and operational voltage. A compact model is of significance to capture the behavior of steep subthreshold slope for early stage design exploration.

Meanwhile with scaling, device performance becomes more sensitive to manufacturing process and device parameters, contributing to the increasing process variations. The variation mainly results from the manufacturing imperfection and profoundly impacts all aspects of circuit performance, posing a grand challenge to future robust IC design, and become one of bottlenecks for further scaling [6]. Although in tradition variability issues are mostly controlled with improvements in the manufacturing process, the industry starts to accept the fact that some of the negative effects can be better mitigated during the design process. In this work, the variation mechanism in Fe-FET is investigated and shed a possibility that a device with internal feedback could suppress intrinsic variations.

On the other hand, through-silicon-via (TSV) is a promising technology that enables the 3D integration of chips with diverse functionalities, providing improved packing density, better noise immunity and faster speed due to reduced interconnect wire length. To evaluate the impact of TSV in circuit performance, a piecewise CV model is proposed for efficient simulation. Furthermore, a stress-aware design approach is utilized to optimize the required TSV area and the mobility variation influenced by the thermal stress during TSV process.

This dissertation is organized as following:

In chapter 2, compact modeling of mobility, velocity, and threshold voltage under eSiGe, DSL, and STI stresses is proposed for the first time. It physically captures the dependence on primary layout parameters, temperature, and other device characteristics. Methods of layout decomposition are proposed

for efficient stress extraction. The entire layout is decomposed into both vertical and lateral directions, reducing the analysis complexity while maintaining the accuracy.

In chapter 3, under particular circumstance, ferroelectric capacitance is effectively negative, due to the negative slope of its polarization-electrical field (P-E) curve. This property makes the ferroelectric layer a voltage amplifier to boost surface potential, achieving fast transition. A new threshold voltage model is developed to capture the subthreshold IV characteristics of Fe-FET. It is further revealed that the impact of random dopant fluctuation (RDF) on leakage variability can be significantly suppressed in Fe-FET.

In chapter 4, a piecewise capacitance model is proposed for efficient simulation to evaluate the impacts of TSV parameters on circuit performance. TSV interconnect capacitance varies with the applied voltage and is sensitive to the radius of TSV, thickness of barrier layer, and the doping concentration in the substrate. Besides TSV capacitance, TSV resistance also strongly depends on radius of conducting material. The dependences on TSV geometry parameters are discussed. TSV induced thermal stress is modeled and can be used to optimized the required TSV area.

The last chapter summarizes the major research results of this dissertation.

#### CHAPTER 2

### MODELING OF LAYOUT-DEPENDENT STRESS EFFECT

Strain technology has been successfully integrated into CMOS fabrication to improve carrier transport properties since 90nm node. However, since the stress is non-uniformly distributed in the channel, the enhancement in carrier mobility, velocity, and threshold voltage shift strongly depend on circuit layout, leading to systematic performance variations among transistors. A compact stress model that physically captures this behavior is essential to bridge the process technology with design optimization. In this chapter, starting from the first principle, a new layout-dependent stress model is proposed as a function of layout, temperature, and other device parameters. Furthermore, a method of layout decomposition is developed to partition the layout into a set of simple patterns for efficient model extraction. These solutions significantly reduce the complexity in stress modeling and simulation. They are comprehensively validated by TCAD simulation and Si data, including the state-of-the-art strain technologies and the STI stress effect.

### 2.1 INTRODUCTION

For the past decades, the miniature of device feature size has driven the improvement in transistor performance [1]. However, many secondary effects become pronounced during scaling. For example, threshold voltage (V<sub>th</sub>) decreases with scaling the channel length because of DIBL effect. To maintain the scaling criteria of leakage power consumption, V<sub>th</sub> needs to be kept in a certain value. Therefore, more channel dopants are introduced to maintain the threshold voltage. However, increased doping concentration degrades carrier mobility and

reduces the driving current. Strain technology, which employs mechanical stress to alter band structure of silicon and reduces carrier effective mass and scattering rate, is introduced to elevate carrier mobility for continual scaling. In general, such a technology can be classified into biaxial stress and uniaxial stress, both of which contribute significant mobility enhancement. Based on the lattice mismatch between Si and SiGe, the biaxial stress is exerted by depositing a pseudomorphic Si layer on a relaxed SiGe substrate [8]. On the other hand, the uniaxial stress is applied to one direction, usually to the direction of channel, and has been adopted as standard process since 90nm node because of lower integration complexity and smaller threshold voltage shift [9]. The major techniques to introduce uniaxial stress include embedded SiGe technology (eSiGe), dual stress liner (DSL), stress memorization technique (SMT), and the parasitic stress from shallow trench isolation (STI). eSiGe technology embedded SiGe in the source and drain area to introduce compressive stress for PMOS [9]. DSL introduces the stress by depositing a highly stressed silicon nitride layer, tensile stress for NMOS region and compressive stress for PMOS region, over the entire wafer to elevate carrier mobility [9]. In SMT, the stress in the channel is transferred from the stressed deposited dielectric and is memorized during the re-crystallization of the active area and poly-gate when thermal annealing is activated [10]. STI stress results from the difference in thermal expansion coefficients between SiO<sub>2</sub> and Si. It is an intrinsic stress source and not intentionally built up for enhancing device performance [11][12].

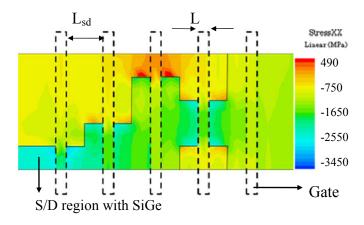

Figure. 2.1. Top view of stress contours in a five-finger layout pattern with SiGe embedded in source/drain area.

In the most strain technologies, the amount of performance enhancement depends on both the applied stress magnitude and circuit layout parameters, such as gate length, source/drain size, and the distance from gate edge to STI [13][14] because of the nature of mechanical stress in silicon; non-uniform distribution. Figure 2.1 illustrates the TCAD simulation [15] of stress distribution in a 45nm standard cell under restrictive design rules, where SiGe with 25% Ge composition is embedded in the S/D area. The stress level is widely different across the cell, depending on transistor size, layout pitch, etc. Such non-uniformity results in pronounced variations among transistors as well as circuit performance and further increases the complexity in modeling and simulation. To capture such a systematic effect, traditional efforts resort to TCAD simulation [16] to extract the stress level from the entire layout and analyze performance enhancement. This approach usually requires expensive computation, especially when chip complexity per unit area keeps increasing along with technology scaling. Therefore, it is necessary to develop a more effective modeling approach that is able to extract the stress effect for each device and embed it into standard model parameters for circuit simulation. On the other hand, the stress dependence provides designers another alternative to optimize the circuit performance. For example, higher gate density per unit area can be achieved by exploiting the stress effect [13]. The insertion and placement of active area are optimized by STI stress to improve the circuit performance [17]. A new stress-aware layout design is proposed to reduce leakage power [18]. Therefore, an accurate model that physically captures the stress effect is required to bridge the process technology and design communities.

The layout-dependent stress effect is first observed and reported from STI stress [11]. Models regarding layout-dependent STI effect are proposed on the basis of the experimental observation that the changes of drive current and threshold voltage follow the trend of the length of oxide definition area (LOD) [12]. The work in [19] indicates that the trend of STI stress effect is attributed to

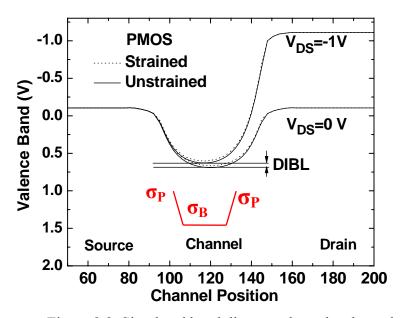

Figure 2.2 (a) The stress distribution in the channel, (b) the equivalent stress levels for strain-induced shifts of  $V_{th}$  and mobility.

the non-uniform stress distribution in the channel, but it does not quantitatively explain how this distribution impacts the electrical properties. Instead, an empirical model is proposed. Moreover, STI width effect is also investigated and modeled to enhance circuit performance. On the other hand, the layout dependent stress effects are also observed in the state-of-the-art strain technologies [13][14]. In Fig. 2.2 (a), TCAD simulation using eSiGe technology shows that the stress profile in the channel, with higher stress level at the edges and lower stress in the center of the channel [21]. The stress profile is sensitive to the primary layout parameters such as channel length and source/drain diffusion length. To capture this layout dependence, Dunga et al. [23] proposes a modeling approach to finding an equivalent stress level in the channel accounting for the mobility enhancement with an assumption that the mobility enhancement is proportional to the applied stress. However, this approach also results in empirical fitting and not adequate for strain-induced V<sub>th</sub> shift because the impacts of stress on different electrical properties are dominated by different stress regions. For example, the strain-induced threshold voltage shift is mainly dominated by the bottom stress level in the channel (more details in section 2.2.5), while the entire channel stresses are required to be taken into consideration for the enhancement of mobility. In Fig. 2.2(b), TCAD simulation [15][24] shows the obvious difference of the equivalent stresses between the shifts in threshold voltage and mobility for different devices with various channel lengths.

In this work, a new general modeling approach [76][77] is proposed to capture the layout-dependent stress effect. This model should physically capture

the impact of circuit layout on transistor performance such that model scalability is guaranteed for future technology generations. Although there are many layout parameters that affect the stress effect, recent trend in layout regularity suggests that it is feasible to decompose the entire layout into a pre-defined set of patterns. Therefore, the modeling efforts can be localized and only focus on pre-defined patterns for efficient extraction.

The important contributions of this chapter include:

- Compact modeling of mobility, velocity, and threshold voltage under eSiGe, DSL, and STI stresses. It physically captures the dependence on primary layout parameters, temperature, and other device characteristics.

- Layout decomposition methods for efficient stress extraction. The entire layout is decomposed in both vertical and lateral directions, reducing the analysis complexity while maintaining the accuracy;

- Circuit performance benchmark at the 45nm node. The interaction between layout and circuit performance is accurately predicted by the new stress models.

These solutions are developed and demonstrated in a 45nm design using restrictive design rules. They are comprehensively evaluated with TCAD simulations and published Si data. Based on them, the impact of the stress effect is well assessed and scalable into future technology generations.

The chapter is organized as following. Section 2.2 presents the model derivation for the dependence on layout and other parameters. In section 2.3, the proposed model is validated by TCAD simulation and Si data. Section 2.4

describes the method of layout decomposition, which systematically partitions the layout into simple patterns to analyze the stress impact on transistor performance. Section 2.5 concludes this chapter.

#### 2.2 COMPACT STRESS MODELS

Strain technology has been successfully implemented since 90nm node to improve transistor performance. However, compact modeling for the stress effect is still at the infant stage to analyze and predict the circuit performance. In this section, based on the mechanical properties of the stress and its impacts on electrical properties, an analytical model is proposed to capture the layout and temperature dependence in this section.

## 2.2.1. Bathtub Stress Distribution

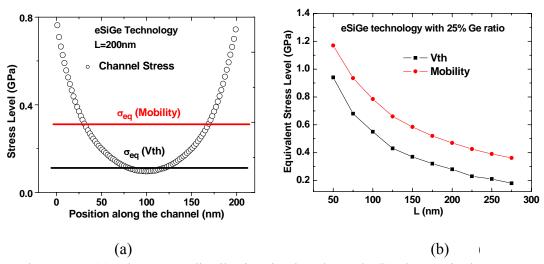

As investigated in [21], the magnitude of mechanical stress in a substrate with cubic symmetry, such as silicon, decays sharply from the edge of stress

(a) The stress induced by SiGe S/D

(b) The piecewise linear approximation of the stress distribution in the channel.

Figure 2.3 Modeling approach of the mechanical stress.

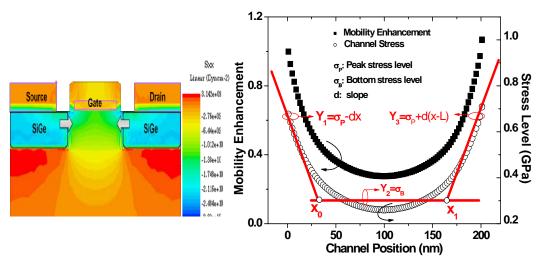

source and becomes less dependent on the distance when the location is far from the origin of the applied stress. For the state-of-the-art uniaxial strain technologies such as eSiGe and DSL, the stress in the channel mainly come from the source and drain area. Figure 2.3(a) shows the cross section of stress distribution for eSiGe technology, indicating that the stress in the channel results from the S/D stressors and non-uniformly distributed. Figure 2.3(b) shows the corresponding stress profile in the channel. Some models regarding the non-uniform stress distribution are proposed [12][25], but most of them are still too complicated for mobility analyses. Instead, in this work, without losing the generality we propose a piecewise linear model to capture the non-uniform stress distribution, as shown  $Y_1$ ,  $Y_2$ , and  $Y_3$  in Fig. 2.3(b) with expressions as Eqs. (2.1)-(2.3),

$$Y_1 = \sigma_P - dx \tag{2.1}$$

$$Y_2 = \sigma_B \tag{2.2}$$

$$Y_3 = \sigma_P + d(x - L) \tag{2.3}$$

where  $\sigma_P$  and  $\sigma_B$  denote the peak and bottom stress levels in the channel, respectively. d is the slope.  $Y_1$  and  $Y_3$  intercept with  $Y_2$  at points of  $x_0$  and  $x_1$ , respectively. Thus,  $x_0$  and  $x_1$  are expressed by Eqs. (2.4) and (2.5).

$$x_0 = \frac{\sigma_P - \sigma_B}{d} \tag{2.4}$$

$$x_1 = L - \frac{\sigma_P - \sigma_B}{d} \tag{2.5}$$

Figure. 2.4. Modeling of STI stress distribution: (a) layout pattern of MOSFET, (b) piecewise linear model for the lateral STI stress, (c) Definition of STI width  $(W_{STI})$

In addition, STI stress is one of the important stress sources and originates from the edges of the oxide definition region. Figure 2.4(a) shows a layout pattern of a MOSFET. SA and SB represent the distances of the leftmost and rightmost fingers to STI boundary. LOD is the length of oxide definition. Figure 2.4(b) illustrates the corresponding STI stress distribution along the region of oxide definition. STI stress distribution is similar to eSiGe, and can be captured by Eqs. (2.1)-(2.5). To clearly express STI stress, the channel length (L) in Eqs (2.1)-(2.5) is replaced by LOD. Meanwhile, the peak and bottom stress levels are attached with subscripts of STI ( $\sigma_{P\_STI}$  and  $\sigma_{B\_STI}$ ), making them distinguishable from eSiGe stress. Moreover, the piecewise linear model is capable of capturing the stress profile along the width direction because the similar bathtub stress distribution is observed in width direction [41]. These equations capture the

essential behavior of the stress distribution, as well as their important dependence on device size. Furthermore, they are simple enough to support further model derivation without losing sufficient model scalability.

## 2.2.2. Layout Dependence

Since the stress is non-uniformly distributed in the channel, the enhancement in carrier mobility, velocity, and threshold voltage shift strongly depend on circuit layout, leading to systematic performance variations among transistors. In this sub-section, the stresses from both lateral direction and width direction are discussed and modeled for further model derivation.

#### 2.2.2.1. Stresses from lateral direction

Based on the piecewise linear model, the stress distribution in the channel is determined by peak and bottom stress levels as well as the decreasing rate of stress from the channel edge. Peak and bottom stresses are highly correlated to layout parameters and the manufacturing process [13][14]. For example, as channel length shrinks, the overall channel stress grows up because the channel is closer to the origin of the stressor in the source and drain regions, as shown in Fig. 2.5(a). Therefore, peak and bottom stress levels are accordingly elevated. Moreover, when S/D diffusion length ( $L_{sd}$ ) decreases,  $\sigma_P$  and  $\sigma_B$  decline since the amount of stressor material in the source and drain regions is lower [14], as shown in Fig. 2.5(b). Note that when S/D diffusion length reaches a critical length, the stress level becomes saturated [14]. To combine these issues,  $\sigma_P$  is modeled as functions of channel length (L) and S/D diffusion length ( $L_{sd}$ ) as Eq. (2.6),

$$\sigma_{P} = \left(1 + \frac{m}{L} + \frac{m}{L + L_{sd}} + \frac{m}{2L + L_{sd}}\right) \cdot \frac{L_{sd}}{A + L_{sd}} \cdot \sigma_{m}$$

(2.6)

where  $\sigma_m$  is the saturation stress level. A and m are fitting parameters accounting for the dependence on  $L_{sd}$  and the stress decreasing rate over distance from neighboring transistors, respectively. Each term in the parenthesis represents the contribution by a diffusion region, depending on their separation distance to the channel. The first two terms in Eq. (2.6) account for the contribution from the source/drain area of the target transistor, as shown the middle finger in Fig. 2.5(b)), while the rest two terms represent the stress sources from the closest two neighboring transistors. Equation (2.6) assumes that all diffusion regions in the neighboring transistors have the same size  $L_{sd}$ . If they are different,  $L_{sd}$  should be replaced with the exact value. The other important stress parameter is  $\sigma_B$ . As channel length becomes shorter and approaches zero,  $\sigma_B$  grows up to the limit of peak stress level. This dependence can be modeled by Eq. (2.7) with a fitting parameter C:

$$\sigma_B = \frac{C}{C + L} \cdot \sigma_P \tag{2.7}$$

Model coefficients are dependent on the fabrication technology. Figure 2.5(b) shows the excellent agreement with the TCAD simulation results.

Similar to  $L_{sd}$  dependence for eSiGe/DSL, larger the STI width ( $W_{STI}$ ), the distance between regions of oxide definition shown in Fig. 2.4(c), introduces more STI stress [16]. The peak stress level of STI can be modeled as Eq. (2.8),

$$\sigma_{P_{\_STI}} = \left(1 + \frac{m}{LOD}\right) \cdot \frac{W_{STI}}{A_{STI} + W_{STI}} \cdot \sigma_{m_{\_}STI}$$

(2.8)

where LOD is the length of oxide definition,  $W_{STI}$  denotes the STI width and  $\sigma_{m\ STI}$  represent the STI saturation stress.  $A_{STI}$  is a fitting parameter to capture the

Figure. 2.5. Modeling of the layout dependence on (a) channel length (b) source/drain diffusion length.

dependence on STI width. Moreover, the bottom stress level of STI is related to  $\sigma_{P\_STI}$ , and can be modeled as Eq. (2.9),

$$\sigma_{B\_STI} = \frac{C_{STI}}{C_{STI} + LOD} \cdot \sigma_{P\_STI}$$

(2.9)

where  $C_{STI}$  is a fitting parameter accounting for the LOD dependence. Note that the STI stress in the channel, which directly impacts the device performance, does not distribute as a bathtub curve. Instead, the stress distribution in the channel is part of the whole stress along the oxide definition area.

### 2.2.2.2. Stresses from width direction

The stress from the width direction also impacts the device performance. For example, STI stress from the width direction leads to hole mobility degradation. Similar to the stress in the lateral direction, the stress profile in width direction follows the bathtub curve as well, and the dependence on layout parameters can be modeled through the peak and bottom stress levels, as shown in Eqs. (2.10)-(2.11):

$$\sigma_{PW} = \left(1 + \frac{m}{W}\right) \cdot \frac{W_W}{A_W + W_W} \cdot \sigma_{mW} \tag{2.10}$$

where W denotes the channel width.  $A_W$  is a fitting parameter to capture width dependence, and  $\sigma_{mW}$  is the saturation stress.  $W_w$  is the width of stress source from vertical direction and determines the stress magnitude at the edge channel width. Moreover, the bottom stress is modeled in Eq. (2.11),

$$\sigma_{BW} = \frac{C_W}{C_W + W} \cdot \sigma_{PW} \tag{2.11}$$

where C<sub>W</sub> is a fitting parameter accounting for the width dependence.

## 2.2.3. Equivalent Low-Field Mobility

In this sub-section, starting from the first principle, an equivalent mobility is derived to account for the non-uniform mobility enhancement in the channel. When the stress is applied, the band structure is altered and further changes the symmetrical ellipsoids of constant energy of silicon. This results in carrier redistribution and reduction of carrier scattering rate. At low applied stress, the mobility enhancement is modeled proportional to the applied stress by the piezoresistance coefficient [26][27]. However, piezoresistance coefficient is insufficient to predict at larger applied stress because the mobility enhancement becomes saturated [28]. Moreover, in scaled devices, due to the strong quantum confinement, the piezoresistance coefficients cannot be used to calculate the channel mobility [28]. On the other hand, the valley-occupancy model based on the strain-induced band splitting is proposed to account for the mobility enhancement [29], and can be expressed in a general form, as Eq. (2.12).

$$\frac{\mu}{\mu_0} = 1 + B \cdot \left[ \exp(\frac{\Delta E}{kT}) - 1 \right] \tag{2.12}$$

where B is a function of electron longitudinal and transfer masses in the subvalley. For the hole mobility, B is corrected with the light and heavy hole masses.  $\mu_0$  is the unstrained low field mobility. k and T represent Boltzmann constant and the temperature.  $\Delta E$  denotes the strain-induced energy splitting of conduction band or valence band and can be calculated based on the deformation potential theory [9][30] by Eq. (2.13).

$$\Delta E = P \cdot \sigma \tag{2.13}$$

where P is a function of deformation potential constants [9][30] and depends on the directions of the applied stress as well as the temperature [41]. Therefore, the temperature-dependent behavior can be modeled as Eq. (2.14),

$$P(T) = P_0 \cdot \left(\frac{T}{T_0}\right)^{\alpha} \tag{2.14}$$

where  $P_0$  denotes its value at room temperature  $(T_0)$  and  $\alpha$  is a fitting parameter.

Since the stress level varies along the channel, the enhancement in mobility is also non-uniform. Based on the principle of current continuity, the non-uniform mobility can be modeled as an equivalent mobility [31],  $\mu_L$ , by using Eq. (2.15),

$$\frac{1}{\mu_L} = \frac{1}{L} \int_0^L \frac{1}{\mu(x)} dx \tag{2.15}$$

where  $\mu(x)$  denotes the mobility distribution along the channel. Furthermore, if the channel stress is symmetrically distributed, only half of the channel is required to determine the impact of layout parameters. Otherwise, a linear superposition will be used to sum the contribution from both sides. Based on the linear piecewise models of Eqs.(2.1)-(2.5) and valley-occupancy mobility model in Eq. (2.12), the mobility enhancement factor is expressed as Eq. (2.16),

$$\frac{1}{M_L} = \frac{\mu_0}{\mu_L} = \frac{2kT}{dPL(B-1)} \cdot \left\{ \frac{-dPx_0}{kT} + \ln \left[ \frac{1 + B\left(\exp\left(\frac{P\sigma_P}{kT}\right) - 1\right)}{1 + B\left(\exp\left(\frac{P\sigma_B}{kT}\right) - 1\right)} \right] \right\}$$

$$+\frac{L-2x_0}{L\cdot\left[1-B+B\exp\left(\frac{P\sigma_B}{kT}\right)\right]}$$

(2.16)

where the first term denotes the contribution of the stress distributing from the channel edge to the bottom, which is modeled in Eq. (2.1).  $\sigma_P$  denotes the stress at the source end while  $\sigma_B$  represents the bottom stress in the center of channel. The second term contributes from the bottom stress as modeled in Eq. (2.2). On the other hand, for STI stress shown in Fig. 2.4, if the transistor is located in the region of Y<sub>1</sub>, only the first term in Eq. (2.16), with the term -dPx<sub>0</sub>/kT replaced by -dPL/kT, is responsible for the mobility enhancement. For example, the stress effect on the leftmost finger shown in Fig. 2.4 only takes the first term in Eq. (2.16) into account. Moreover, if the transistor is placed within the region of  $Y_2$ , only the second term in Eq. (2.16) is required for stress calculation. Furthermore, if the transistor is located in the transition region between Y<sub>1</sub> and Y<sub>2</sub>, then both terms in Eq. (2.16) are required. In this final equation for mobility enhancement, the physical dependence on L and temperature (T) is well preserved during the derivation, ensuring the model scalability. Moreover, the impact of stress variation due to different layout parameters such as L and L<sub>sd</sub> is modeled through  $\sigma_P$  and  $\sigma_B$  in Eqs. (2.6)-(2.9).

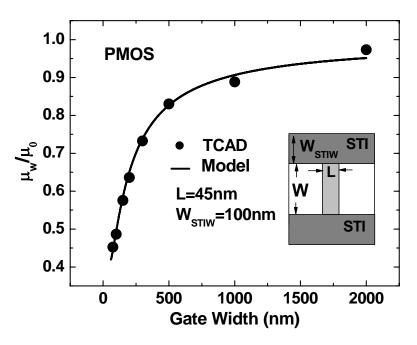

Figure 2.6. Modeling of width dependence on mobility.

On the other hand, the stress from the width direction also impacts the device performance. To capture the non-uniform mobility distribution along the channel width, the transistor is equivalently regarded as several sub-transistors with small slice width in parallel as shown in Fig. 2.6. Therefore, the equivalent mobility considering the stress from width direction is modeled as Eq. (2.17):

$$\mu_{W} = \frac{1}{W} \int_{0}^{W} \mu(y) dy$$

(2.17)

where  $\mu(y)$  denotes the mobility distribution in vertical direction and W is the channel width. By integrating the proposed piecewise stress models and the valley-occupancy mobility model, the equivalent mobility enhancement factor is expressed as Eq. (2.18):

$$M_{W} = \frac{\mu_{W}}{\mu_{0}} = \frac{2BkT}{WPd} \cdot \left[ \exp\left(\frac{P\sigma_{PW}}{kT}\right) - \exp\left(\frac{P\sigma_{PW}}{kT}\right) \right] + \frac{W - 2By_{0}}{W} + \left(\frac{BW - 2By_{0}}{W}\right) \left[ \exp\left(\frac{P\sigma_{BW}}{kT}\right) - 1 \right]$$

$$(2.18)$$

where  $\sigma_{PW}$  and  $\sigma_{BW}$  are the peak and bottom stress levels in the width direction and modeled by Eqs. (2.10)-(2.11).  $y_0$  and d are the intercept point and the edge

stress decreasing rate in the vertical direction, with a similar expression to that in lateral direction. By considering the stress effect from lateral and vertical directions, the total mobility enhancement factor is expressed as Eq. (2.19).

$$M_{total} = 1 + B \left[ \left( 1 + \frac{M_L - 1}{B} \right) \cdot \left( 1 + \frac{M_W - 1}{B} \right) - 1 \right]$$

(2.19)

where  $M_L$  and  $M_W$  are the mobility enhancement factors for lateral and width directions, respectively.

## 2.2.4. Velocity in the Saturation Region

The effect of stress-induced mobility enhancement with layout dependence is modeled in section 2.2.3. However, carrier mobility is mainly responsible for the linear operation region, but not adequate to explain the carrier behavior of high electrical field in the saturation region. Instead, velocity is usually used to describe the high E-field behavior. Equation (2.20) is a simplified solution of the energy balance equation [33], which accounts for the velocity overshoot behavior in a short channel device. This simplified solution considers how mobility influences the high E-field behavior:

$$V_{sat} = V_{sat 0} + 0.13 \,\mu_{eff} \,\sqrt{\tau \mu_{eff} \,kT \,/\, q} \cdot \left(V_d \,/\, L^2\right) \tag{2.20}$$

where  $V_{\text{sat0}}$  is the saturation velocity in a long channel device.  $\mu_{\text{eff}}$  is the effective mobility and is a linear function of low-field mobility [20].  $\tau$  is the relaxation time and L is the channel length. By Eq. (2.20), the layout dependence on velocity can be modeled through the mobility variation.

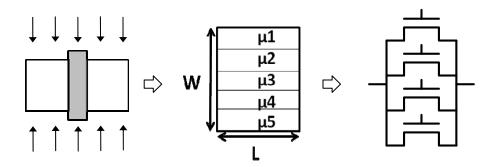

## 2.2.5. Strain Induced Threshold Voltage Shift

In addition to strain-induced mobility variation, strain-induced threshold voltage shift ( $\Delta V$ th) is also observed in the strained devices. The change in threshold voltage is attributed to strain-induced variation of energy bandgap, electron affinity, and density of states (DOS) [34]. Note that the effect of density of states is ignored due to its insignificant impact. As the band diagram shown in Fig. 2.7, the strain-induced flat-band voltage shift is expressed as Eq. (2.21)

$$\Delta V_{FB} = \Delta E_G - \Delta E_C \tag{2.21}$$

where  $\Delta E_C$  and  $\Delta E_G$  denote the strain-induced change in conduction band and bandgap. Based on the deformation potential theory [9][30], the strain-induced change in flat-band voltage is proportional to the applied stress magnitude. Moreover, in principle, applying stress affects the intrinsic carrier density  $(n_i)$ ,

Figure 2.7. Band diagram of strained-Si NMOSFET

which is an exponential function of bandgap, further changing the barrier between source and channel area ( $qV_{bi}$ ) and the bulk potential ( $\Phi_B$ ) [35]. The expression for  $V_{bi}$  and  $\Phi_B$  are in Eqs. (2.22)-(2.23).

$$V_{bi} = \frac{kT}{q} \ln \left( \frac{N_S N_{ch}}{n_i^2} \right)$$

(2.22)

$$\phi_B = \frac{kT}{q} \ln \left( \frac{N_{ch}}{n_i} \right) \tag{2.23}$$

where  $N_S$  and  $N_{ch}$  denote the doping concentrations in source and channel regions. Note that the flat-band voltage and bulk potential are the major components of threshold voltage. Therefore, to the first order, the strain-induced threshold voltage shift equals the summation of the changes from flat-band voltage and bulk potential. The flat-band voltage shift and the bulk potential change are modeled linearly proportional to the applied mechanical stress by Eq.(2.24),

Figure 2.8. Simulated band diagram along the channel

$$\Delta V_{th} \approx VTH \ \_STR \cdot \sigma_B$$

(2.24)

where  $VTH\_STR$  is a fitting parameter to capture the linear relationship between threshold voltage shift and the applied stress magnitude. Note that the bottom stress level is responsible for threshold voltage shift because the barrier peak between source and substrate  $(qV_{bi})$  is controlled by  $\sigma_B$ , as shown the band diagram of PMOS in Fig. 2.8. The simulated valence bands of unstrained/strained PMOS indicate that energy barrier between channel and source is lowered and thus it becomes easier for holes to pass through the channel. This lowering valence band confirms the strain-induced threshold shift.

## 2.2.6. Other Secondary Effects

Drain induced barrier lowering (DIBL) effect is becoming pronounced with scaling the device feature size, and to the first order can be modeled as Eq. (2.25) [36],

$$\Delta V_{th}(DIBL) \approx [3(V_{bi} - 2\phi_R) + V_{ds}]e^{-L/l}$$

(2.25)

where  $V_{bi}$  and  $\Phi_B$  have the same meaning as discussed in the previous section.  $V_{ds}$  is the applied drain bias. L denotes the channel length and l is the DIBL characteristic length as expressed in Eq. (2.26),

$$l = \sqrt{3T_{ox}X_{dep}} \tag{2.26}$$

where Tox denotes the oxide thickness and Xdep is the depletion depth with expression in Eq. (2.27),

$$X_{dep} = \sqrt{\frac{2\varepsilon_{si}(2\phi_B - V_{BS})}{qN_{ch}}}$$

(2.27)

$V_{bi}$  and  $\phi_B$  are major factors to DIBL effect. Although applying stress changes  $V_{bi}$  and  $\phi_B$ , the impact of stress on DIBL effect is canceled. The term of  $(V_{bi} - 2\phi_B)$  in Eq. (2.25) is independent of  $n_i$ , i.e., the applied stress. On the other hand,  $\Phi_B$  is changed and influences the depletion depth  $(X_{dep})$ , further affecting DIBL characteristic length. Therefore, DIBL effect is modulated through Eq. (2.25). Note that DIBL characteristic length (l) is the major factor to account for stress effect and is proportional to Eg<sup>1/4</sup>, making DIBL effect relatively insensitive to the applied mechanical stress. Due to the change of depletion depth caused by the applied stress, the capacitance between substrate and channel ( $C_{dep}$ ) is subject to be changed by Eq. (2.28).

$$C_{dep} = \frac{\mathcal{E}_{si}}{X_{dep}} \tag{2.28}$$

Therefore, the the impact of stress on subthreshold swing is modified through Eq. (2.29).

$$S.S. = 2.3 \frac{kT}{q} \left( 1 + \frac{C_{dep}}{C_{or}} \right) \tag{2.29}$$

where  $C_{ox}$  represents the oxide capacitance. k and T represent Boltzmann constant and the temperature. Moreover, the threshold voltage shift induced by body bias is also modified and is modeled through the change of bulk potential ( $\phi_B$ ) in Eq. (2.30).

$$\Delta V_{th} = \frac{\sqrt{2\varepsilon_{si}qN_{ch}\cdot(2\phi_B - V_{bs})}}{C_{or}}$$

(2.30)

# 2.3 MODEL VALIDATION

In this section, the newly developed models are validated by TCAD simulations as well as Si data. To capture the stress effect, the process simulator [15] is performed to include process induced mechanical stresses, which are further loaded into device simulator [24] to evaluate the impacts of stresses on

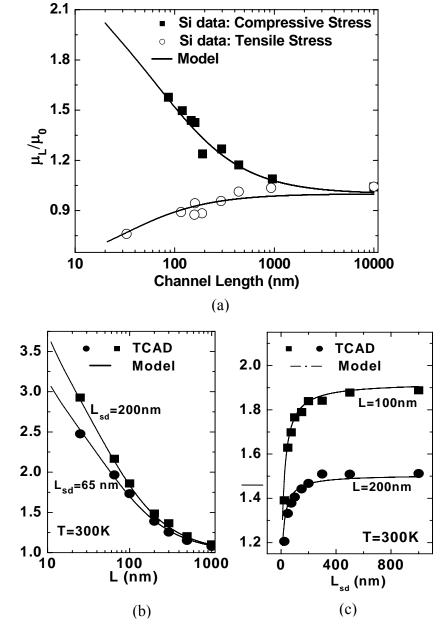

Figure. 2.9. (a) DSL induced hole mobility variation with dependence on L; (b) eSiGe induced hole mobility changes with dependence on L and (c)  $L_{sd}$ .

device performance. During the simulation, the mobility is extracted in the linear region with gate bias at -1 volt and drain voltage at -0.1volt for PMOS.

In Fig. 2.9 (a), the experimental data shows DSL induced mobility enhancement has a strong dependence on channel length [40]. By applying compressive stress liner, the enhancement of hole mobility increases with scaling channel length. On the other hand, the tensile stress liner degrades hole mobility. Moreover, in Fig. 2.9 (b), TCAD simulation regarding eSiGe technology shows similar layout dependence to DSL technique. As channel length becomes shorter, the enhancement grows up, i.e., strain technology is more effective. On the other hand, in Fig. 2.9 (c) as L<sub>sd</sub> becomes smaller, the enhancement becomes lower because of lower stressor material in the source and drain regions.

Figure. 2.10. STI stress induced hole mobility variation with dependence on gate width.

Figure 2.10 shows the width dependence on mobility. Given a constant vertical stress source, higher stress magnitude is observed in the device with smaller channel width. Higher compressive stress applied in the width direction leads to more hole mobility degradation. Excellent agreement between the new model and Si data and TCAD simulation are achieved.

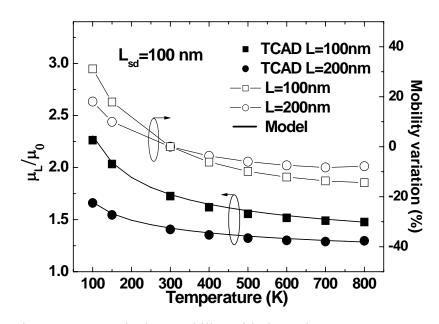

Figure. 2.11. Equivalent mobility with dependence on temperature

Figure. 2.12. STI induced  $V_{th}$  shift with dependence on (a)  $L_{sd}$  and (b) SA.

Figure. 2.13. eSiGe induced  $V_{\text{th}}$  shift with dependence on (a) L and (b) DIBL effect.

In addition to layout parameters, the stress effect depends on the temperature (Eqs. (2.12) and (2.14)). Figure 2.11 demonstrates the temperature dependence on strain enhanced mobility. To assess this effect, the device is operated at different temperatures from 100K to 800K. TCAD simulation shows

that at 100K, the mobility enhancement increases 31% more than that at room temperature for the device with both L and  $L_{sd}$  at 100nm. On the contrary, as temperature increases more than the room temperature, the mobility enhancement declines. The sensitivity of mobility enhancement to temperature is higher at lower temperatures. This behavior can be explained by Eq. (2.12), where the temperature term is in the exponential function, so that the change is more dramatic under low temperatures. In addition, simulation results illustrate that the device with longer channel length is less sensitive to the temperature variation.

In Fig. 2.12, the experimental data regarding STI stress show the strain-induced  $V_{th}$  shift is dependent on the layout parameters,  $L_{sd}$  and SA [39]. As  $L_{sd}$  and SA increase, the stress in the channel area decreases and results in lower  $V_{th}$  shift. In Fig. 2.13 (a), TCAD simulation based on eSiGe technology shows that the strain-induced  $V_{th}$  shift also correlates to the L and  $L_{sd}$ ; the strain-induced  $\Delta V_{th}$  increases as L decreases, and lower  $\Delta V_{th}$  is observed for a smaller  $L_{sd}$  due to lower S/D stressors. Figure 2.13 (b) shows  $V_{th}$  decrease as L decreases due to the DIBL effect for strained and unstrained devices. Simulation results show the

Figure 2.14. The decomposition along the width direction.

well modeled in the proposed analytical solutions.

# 2.4 DESIGN APPLICATION

Although applying mechanical stress improves the device performance, it introduces extra variation among transistors because of their different size and layout parameters. In this section, a decomposition method is proposed to partition a large layout into several sections, in order to simplify the extraction procedure without losing the accuracy. This study uses a 45nm technology that is customized from PTM [37]. Gate length (L) and source/drain diffusion length ( $L_{sd}$ ) are assumed at 40nm and 130nm, respectively, following regular layout rules [38]. TCAD stress simulations are conducted on layout samples to determine the distribution in both vertical and lateral directions, and to evaluate the decomposition methods. For the process simulation, a typical eSiGe stress technology is used with 25% of Ge composition. After the process simulation, the device simulation is conducted to investigate how the stress process impacts the electrical characteristics of a transistor. The maximum on-current (I<sub>on</sub>) and linear current (I<sub>lin</sub>) are sampled at the gate bias at -1 V and drain biases at -1 and -0.1 V, respectively, from a PMOS device.

# 2.4.1. Vertical Layout Decomposition

The first step is to decouple the layout along the vertical direction, as shown in Fig. 2.14. By separating a transistor with an irregular diffusion region in the width direction, it can be regarded as two transistors with different width in parallel. An equivalent circuit representation is shown in Fig. 2.14. All subtransistors now have a regular diffusion region that defines the stress, i.e.,  $L_{sd1}$  and

$L_{sd2}$ , and each individual section can be described by the same stress model, as in Section 2.2.

Figure. 2.15. (a) Top view of the stress distribution when stressor is only applied to S/D area of M1, (b) the stress tail only has a marginal impact on currents. ( $W_1$ =100nm,  $W_2$ =200nm)

Such decomposition is feasible only if the performance enhancement due to the stress effect is localized and does not impact the neighbors along the width direction. For the distribution of the mechanical stress, this may not be true: Fig. 2.15 (a) illustrates the stress distribution induced by adding SiGe only in  $M_1$ ; yet it shows a stress tail penetrating into  $M_2$ .

This effect becomes more significant when the diffusion size of  $M_1$ ,  $L_{sd1}$ , increases, but degrades fast along width direction, as shown in Fig. 2.15(b). Fortunately, this tail only has a marginal influence on the IV characteristics of  $M_2$ , which are determined by the average stress level throughout the entire channel. As shown in Fig. 2.15 (b), the change of  $I_{on}$  and  $I_{lin}$  of  $M_2$  is only 1-2% due to this tail, even when  $L_{sd1}$  is comparable to  $L_{sd2}$ . It is safe to neglect the influence of the stress tail from the vertical neighbors when evaluating the device performance and thus, this decomposition method is valid.

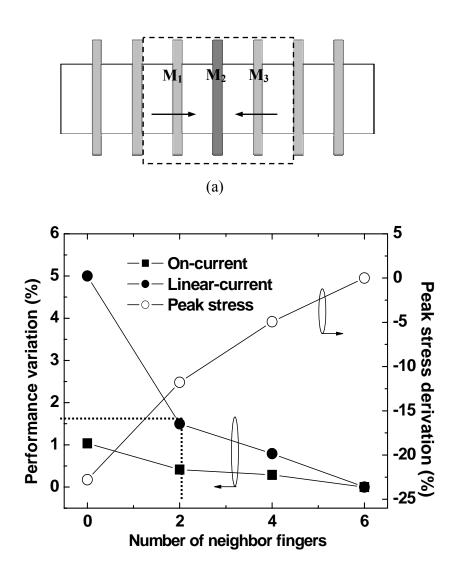

# 2.4.2. Lateral Layout Decomposition

To determine the stress influence from horizontal neighboring transistors, a seven-finger pattern, as shown in Fig. 2.16 (a), is used as the basic test layout. The middle transistor (M2) is served as the target transistor for model extraction. TCAD simulation in Fig. 2.16 (b) shows that more than 20% derivation of the peak stress is observed when no neighboring transistors are considered, leading to a large performance error. The error in IV prediction is reduced when more neighboring stresses are included. This indicates that different from the vertical decomposition, it is not accurate to only consider each individual gate in the lateral direction. Figure 16 (b) further illustrates that the error in I<sub>on</sub> and I<sub>lin</sub> decreases to 1-2% if the nearest two neighboring transistors are included into the stress calculation. Based on this observation, it is concluded that a pattern with three fingers is an appropriate set for stress modeling and extraction (i.e., M1 M2 and M3 in Fig. 2.16 (a)). This is the basic pattern for the lateral decomposition layout pattern.

From the above discussions, the irregular layout can be decomposed into several basic layout components in order to reduce the complexity in model

Fig. 2.16. Method for lateral decomposition: (a) The basic pattern for lateral decomposition (b) Performance variation with different numbers of neighboring gates

development. They are general enough to cover all layouts under restrictive design rules. After the decomposition, a general and physical model is applied to model the performance enhancement in each sub-transistor, as presented in the following section. These sub-transistors will be combined for further circuit simulation and analysis.

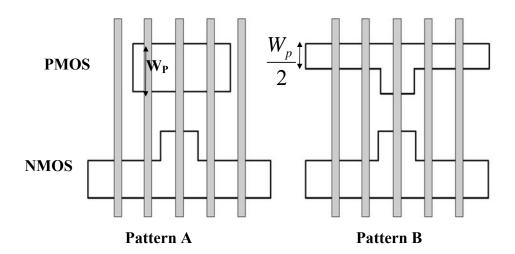

# 2.4.3. Circuit Performance Benchmark

A physical layout-dependent stress model is developed and is comprehensively verified by the Si data and TCAD simulation. In this section, we combine the decomposition approach together with the stress model, and demonstrate its capability in circuit simulation as well as performance analysis. As the first step, the stress model is calibrated with IV characteristics from TCAD simulations, in order to attain the accurate device behavior under irregular stress distribution. The enhancement in mobility and velocity as well as the  $V_{th}$  shift are

Figure. 2.17. Layout patterns of two NAND3 gates with the same size, with SiGe in source/drain only.

Figure 2.18. The systematic delay variation due to layout dependent stress effect.

accordingly embedded into standard device models. Given a circuit layout, it is decomposed in both directions; each sub-transistor is then translated by the stress model for further circuit simulation, depending on their size and layout parameters.

To benchmark the layout effect on circuit performance, two different layout patterns of NAND3 are generated as shown in Fig. 2.17. They are decomposed and modeled by the procedure described above. Figure 2.18 shows SPICE simulation results of high-to-low switching. The delay in Pattern B is longer than that in Pattern A because the pull-up network of Pattern B is stronger, benefiting from the larger and closer diffusion area, therefore leading to stronger

stress from neighboring gates. The performance difference increases at lower  $V_{DD}$  as the linear region is more sensitive to the stress effect. The decomposition method together with the layout dependent stress model demonstrates an excellent accuracy as compared to TCAD simulations.

# 2.5 Chapter Summary

With the scaling of device dimension, the strain-induced variation becomes more pronounced. Therefore, it is essential to develop compact models of the stress effect for circuit analysis and optimization. In this work, we propose the solution that significantly reduces the complexity in modeling and simulation:

(i) compact models of stress-induced mobility, velocity, and threshold voltage, which are general enough to model the scalability to layout, temperature and other device parameters for different strain technologies (ii) the decomposition method to partition a large layout into simple patterns for easy model extraction and localize the modeling effort. As demonstrated in circuit benchmark, these solutions can be easily integrated into physical design tools to predict circuit performance under layout-dependent stress effect.

### **CHAPTER 3**

# MODELING OF FE-FET AND IMPLICATIONS ON

# VARIATION-INSENSITIVE DESIGN

Semiconductor devices with self-feedback mechanisms are considered as a promising alternative to traditional CMOS, in order to achieve faster operation and lower switching energy. Examples include IMOS and FBFET that are operated in a non-equilibrium condition to rapidly generate mobile carriers. More recently, Fe-FET was proposed to improve the switching by integrating a ferroelectric material as gate insulator in a MOSFET structure. Under particular circumstance, ferroelectric capacitance is effectively negative, due to the negative slope of its polarization-electrical field (P-E) curve. This property makes the ferroelectric layer a voltage amplifier to boost surface potential, achieving fast transition. In this chapter, a new threshold voltage model is developed to capture the feedback of negative capacitance and IV characteristics of Fe-FET. It is further revealed that the impact of random dopant fluctuation (RDF) on leakage variability can be significantly suppressed in Fe-FET, by tuning the thickness of the ferroelectric layer.

#### 3.1. INTRODUCTION

It is of significant importance to have a device with a steep subthreshold slope to achieve low supply voltage and power dissipation. However, in a traditional MOSFET structure, the subthreshold swing (SS) is defined as Eq. (3.1):

$$SS = \frac{\partial V_g}{\partial (\log I_d)} = 2.3 \frac{k_B T}{q} \cdot \left(1 + \frac{C_S}{C_{ox}}\right)$$

(3.1)

where  $k_B$  is Boltzmann constant, T is the absolute temperature, and q is the unit charge.  $C_S$  and  $C_{ox}$  denote the depletion capacitance and oxide capacitance, respectively. Eq. (3.1) indicates that a fundamental limit of 2.3  $k_BT/q$  of gate voltage change is required to modulate the subthreshold current by 10 times, which is also known as Boltzmann tyranny [43]; 60mV is needed at room temperature.

New device structures such as Impact Ionization MOS (IMOS) [44] and Feedback FET (FBFET) [45] are proposed to circumvent this limit. IMOS, a partially gated reverse biased p-i-n diode, is operated in the region of avalanche breakdown by modulating the electrical field to generate a vast amount of electron-hole pairs (EHPs), contributing to the fast subthreshold transition. On the other hand, in FBFET the charge is deliberately implemented and stored in the spacer regions to form the built-in potential barriers, creating an internal feedback loop to achieve the fast subthreshold switch.

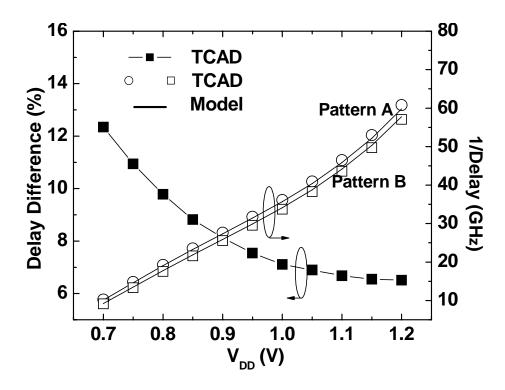

Different from IMOS and FBFET, Fe-FET is proposed by integrating

Figure 3.1. The energy landscape of a ferroelectric and regular capacitor. [46].

ferroelectric material in a traditional MOSFET structure to achieve the fast transition in subthreshold region [46]. Under particular circumstance, ferroelectric capacitance is effectively negative, due to the negative slope of its polarization-electrical field (P-E) curve [47]. Figure 3.1 shows the energy landscapes for a ferroelectric and regular capacitor, respectively. The curvature of energy landscape is negative in the ferroelectric insulator while a regular capacitor presents a positive one. The capacitance of the ferroelectric is negative. This property makes the ferroelectric layer an internal voltage amplifier to boost surface potential, leading to fast channel formation. The concept of negative capacitance as a voltage amplifier can be understood by two capacitances in series, shown in Fig. 3.2, where the charge stored in both capacitances are the same. When  $C_1$  and  $C_2$  are regular capacitances and the voltage drops in  $C_1$  and  $C_2$  follow the ratio of  $C_2/C_1$  as expressed in Eqs. (3.2) and (3.3). This scheme is usually served as a voltage divider in the circuit.

$$V_1 - V_2 = \frac{C_2}{C_1 + C_2} \cdot V_1 \tag{3.2}$$

$$V_2 = \frac{C_1}{C_1 + C_2} \cdot V_1 \tag{3.3}$$

$$\begin{matrix} V_1 \\ \circ \end{matrix} \begin{matrix} V_2 \\ C_1 \end{matrix} \begin{matrix} C_2 \end{matrix} \begin{matrix} \bot \end{matrix}$$

Figure 3.2. Series capacitance as a voltage divider.

$V_2$  is determined by the capacitances and the applied voltage,  $V_1$ . As  $V_1$  increases,  $V_2$  also increases because the overall charge is increased. The overall charge is expressed in Eq. (3.4).

$$Q_{total} = \frac{C_1 C_2}{C_1 + C_2} \cdot V_1 \tag{3.4}$$

Moreover, since  $C_1$  and  $C_2$  are in series, the charges stored in  $C_1$  and  $C_2$  are the same and can be expressed in Eqs. (3.5) and (3.6).

$$Q_1 = C_1 \cdot (V_1 - V_2) \tag{3.5}$$

$$Q_2 = C_2 \cdot V_2 \tag{3.6}$$

Now, let us consider the scheme with positive  $C_1$  and negative  $C_2$ . As  $V_1$  increases, the overall charge increases as long as the equivalent capacitance ( $C_1$  and  $C_2$  in series) remains positive and  $Q_1$  equals  $Q_2$ . To maintain the charge conservation,  $V_2$  is required to stay negative to ensure that  $Q_2$  equal to  $Q_1$ . Note that the voltage drop in  $C_1$ , ( $V_1$ - $V_2$ ), becomes larger than the originally applied voltage,  $V_1$ , owing to the negative  $V_2$ . Therefore, more voltage is allocated to regular capacitance when in series with negative capacitance and the system remains stable. This behavior is explicitly different from scheme of regular capacitance in series and can be served as an internal voltage amplifier in a MOSFET device to boost the surface potential, implying the channel can be formed quickly. On the other hand, back to Eq. (3.1), if the  $C_{ox}$  is replaced by the negative ferroelectric capacitance, it is possible to break down the limit of Boltzmann tyranny and achieve the subthreshold swing lower than 60 mV/dec.

To investigate the device performance, traditional efforts resort to TCAD simulation to analyze the dependence of geometry and process on electrical characteristics. This approach usually requires expensive computation, especially when chip complexity per unit area keeps increasing along with technology scaling. To enable the early-stage exploration of Fe-FET on circuit design and its impact on performance variability, it is necessary to develop an effective model that is able to physically capture the steep subthreshold slope and embed it into standard model parameters for circuit simulation.

On the other hand, the aggressive scaling of CMOS technology inevitably leads to a drastic challenge in process variations, such as channel length variation [48], channel dopant fluctuations [49], and other layout-dependent proximity effects [50]. Among these variations, random dopant fluctuation (RDF) represents the intrinsic variation source in CMOS structure, posed by fundamental physical and manufacturing limits. RDF has become one of the most major barriers in the progress of large-scale integration scaling. In this work, a new threshold voltage model of Fe-FET is proposed to capture the steep subthrehsold behavior and is used to study the performance variation. This model is derived from the first principle and physically captures the subthreshold behavior of Fe-FET such that model scalability is guaranteed for future technology generations [78].

The important contributions of this chapter include:

i. A new threshold voltage model is developed to capture the feedback of negative capacitance and IV characteristics of Fe-FET;

ii. It is further revealed that the impact of random dopant fluctuation (RDF) on leakage variability can be significantly suppressed in Fe-FET, by tuning the thickness of the ferroelectric layer.

The chapter is organized as following. Section 3.2 presents the basics of Fe-FET and compact  $V_{th}$  model derivation to describe the subthreshold behavior. In section 3.3, the performance variability of Fe-FET is investigated by using the new threshold voltage model and TCAD simulation. Section IV concludes this chapter.

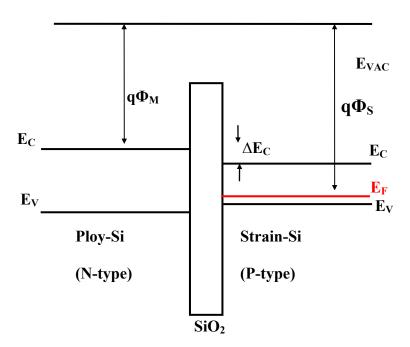

# 3.2. COMPACT MODELING OF FE-FET

Fe-FET is proposed to speed up the transition by stacking a ferroelectric material on top of silicon dioxide as an internal voltage amplifier to boost surface potential in a MOSFET structure, as shown in the schematic in Fig. 3.3 (a). In effect, this ferroelectric layer amplifies the gate voltage internally because of a negative gate capacitance; the inversion layer charge actually increases at lower gate voltages. Fig. 3.3 (b) illustrates the equivalent capacitance model for a Fe-FET device, where the ferroelectric capacitance ( $C_{FE}$ ) is in series with the oxide capacitance ( $C_{OX}$ ) and the substrate depletion capacitance ( $C_{S}$ ).  $V_{int}$  denotes the internal voltage between  $C_{FE}$  and  $C_{OX}$ . Since  $C_{OX}$  and  $C_{FE}$  are in series, the amount of charge stored in three capacitances is the same and is expressed in Eq. (3.7)

Figure 3.3. (a) Cross-section of Fe-FET. (b) The equivalent capacitance model in the sub- $V_{th}$  region (c) The capacitance model in the super- $V_{th}$  region.

$$Q = C_{eq} \cdot (V_g - \phi_s)$$

$$= C_{ox} \cdot (V_g - V_{int})$$

$$= C_{FE} \cdot (V_{int} - \phi_s)$$

$$= C_s \cdot \phi_s$$

(3.7)

where  $C_{eq}$  is the equivalent capacitance of  $C_{ox}$  and  $C_{FE}$  in series. If the equivalent capacitance is positive, the charge increases with applying gate voltage. The applied voltage is divided into three components in  $C_{FE}$ ,  $C_{ox}$ , and  $C_s$  and the sum of voltage drops on each capacitance is equal to the outer gate voltage. However, since  $C_{FE}$  is negative, the voltage drop in ferro-capacitance ( $V_{int} - \Phi_s$ ) stays negative, implying the voltage drops on the other two regular capacitances,  $C_{ox}$  and  $C_s$ , increase. Therefore, the voltage drop on substrate depletion capacitance, equivalent as surface potential in a MOSFET structure, is increasing, leading to the fast formation of channel.

The negative capacitance of the ferroelectric dielectric originates from the intrinsic feedback mechanism between the induced charge and the voltage drop on the capacitance; this feedback between charge and voltage drop is modeled by Eq. (3.8) [46].

$$V_G - V_{\text{int}} \approx \alpha_0 Q + \beta_0 Q^3 + \gamma_0 Q^5 + \rho_0 \frac{dQ}{dt}$$

(3.8)

where Q denotes the charge stored in the capacitance. The internal voltage ( $V_{int}$ ), which accounts for the change of voltage drop in  $C_{FE}$ , is formulated in Eq. (3.9).

$$V_{\text{int}} = \phi_s + \frac{\sqrt{2\varepsilon_{si}qN_{ch}\phi_s}}{C_{ox}}$$

(3.9)

where the q is the unit charge and  $N_{ch}$  is the channel doping concentration. Note that the second term in Eq. (3.9) accounts for the voltage drop on  $C_{ox}$  and only stays valid in the subthreshold region. On the other hand,  $\alpha_0$  and  $\beta_0$  are negative to account for the negative capacitance.  $\gamma_0$  is positive to describe the behavior of normal capacitance.  $\rho_0$  is the resistivity for the voltage drop. Those parameters ( $\alpha_0$ ,  $\beta_0$ ,  $\gamma_0$ , and  $\rho_0$ ) are proportional to the thickness of ferroelectric material ( $t_{FE}$ ), and are modeled in Eqs. (3.10) - (3.13) [46],

$$\alpha_0 = 2\alpha t_{FE} \tag{3.10}$$

$$\beta_0 = 4\beta t_{FE} \tag{3.11}$$

$$\gamma_0 = 6 \gamma t_{FE} \tag{3.12}$$

$$\rho_0 = \rho \ t_{FE} \tag{3.13}$$

where  $\alpha$ ,  $\beta$ ,  $\gamma$  and  $\rho$  are material coefficients of the ferroelectric material. When the ferroelectric dielectric layer is integrated into the MOSFET structure, the feedback mechanism is enabled and starts to interact with other elements.

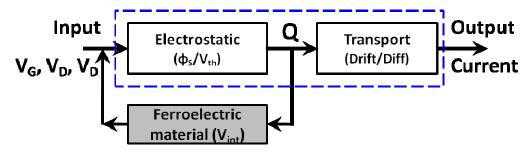

In general, the device performance of traditional MOSFET is modeled by electrostatic behavior and carrier transportation. In a device numerical solver, for example Sentaurus Device [30], both electrostatics and transport properties are self-consistently solved to analyze the device performance. This modeling approach is also known as Technology Computer-Aided Design (TCAD). Expensive computation is required to perform TCAD simulation. On the other hand, compact models such as BSIM [20] and PSP [51] are proposed to efficiently analyze the device performance with closed-form solutions, instead of self-consistent iterative solution. As illustrated in the dash box in Fig. 3.4, the electrostatic property such as surface potential or threshold voltage is analytically calculated to estimate the carrier transportation for device performance prediction. Compact model is very effective in analyzing a VLSI chip, where more than one billion transistors are integrated.

When the ferroelectric dielectric layer is integrated into the MOSFET system, the feedback mechanism is enabled and interacting with other elements in the traditional MOS system. This can be modeled by inserting an additional feedback path in a traditional CMOS model, as shown in Fig. 3.4. The induced charge in the substrate will impact the electrostatic properties through the feedback loop. By combining Eqs. (3.8)-(3.13) and ignoring the high-order

# **Traditional MOSFET Model**

Figure 3.4. The integration of the ferroelectric material into traditional MOSFET model.

feedback effects, the surface potential ( $\Phi_S$ ) in the subthreshold region is derived as Eqs. (3.14) and (3.15) in a steady state condition.

$$\phi_s = \left(\frac{-A + \sqrt{A^2 + 4V_G}}{2}\right)^2 \tag{3.14}$$

$$A = \sqrt{2\varepsilon_{si}qN_{ch}} \cdot \left(\frac{1}{C_{ox}} + \alpha_0\right)$$

(3.15)