# CMOS Integrated Power Amplifiers for RF Reconfigurable and Digital Transmitters

by

Soroush Moallemi

# A Dissertation Presented in Partial Fulfillment of the Requirement for the Degree Doctor of Philosophy

Approved July 2019 by the Graduate Supervisory Committee:

Jennifer Kitchen, Chair Sayfe Kiaei Bertan Bakkaloglu Trevor J. Thornton

ARIZONA STATE UNIVERSITY

August 2019

#### ABSTRACT

This dissertation focuses on three different efficiency enhancement methods that are applicable to handset applications. These proposed designs are based on three critical requirements for handset application: 1) Small form factor, 2) CMOS compatibility, and 3) high power handling. The three presented methodologies are listed below:

- 1) A transformer based power combiner architecture for out-phasing transmitters

- A current steering DAC-based average power tracking circuit for on-chip power amplifiers (PA)

- A CMOS-based driver stage for GaN-based switched mode power amplifiers applicable to fully digital transmitters

This thesis highlights the trends in wireless handsets, the motivates the need for fully-integrated CMOS power amplifier solutions, and presents the three novel techniques for reconfigurable and digital CMOS-based PAs. Chapter 3, presents the transformer based power combiner for out-phasing transmitters. The simulation results reveal that this technique is able to shrink the power combiner area, which is one of the largest parts of the transmitter, by about 50% and as a result, enhances the output power density by 3dB.

The average power tracking technique (APT) integrated with an on-chip CMOSbased power amplifier is explained in Chapter 4. This system is able to achieve up to 32dBm saturated output power with a linear power gain of 20dB in a 45nm CMOS SOI process. The maximum efficiency improvement is about  $\Delta\eta$ =15% compared to the same PA without APT. Measurement results show that the proposed method is able to amplify

i

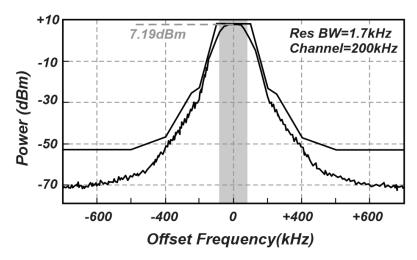

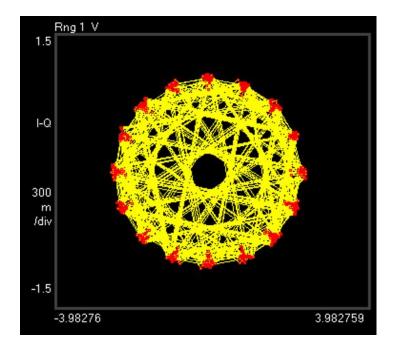

an enhanced-EDGE modulated input signal with a data rate of 70.83kb/sec and generate more than 27dBm of average output power with EVM<5%.

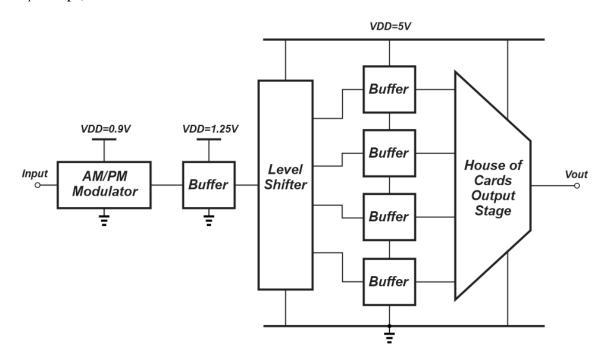

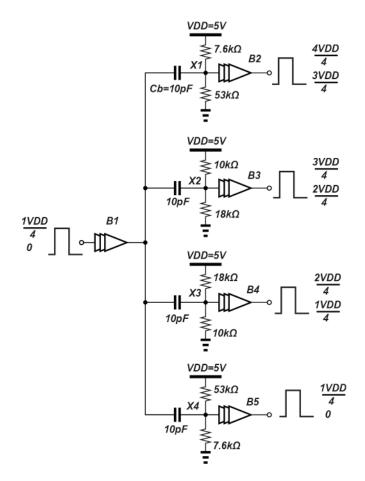

Although small form factor, high battery life time, and high volume integration motivate the need for fully digital CMOS transmitters, the output power generated by this type of transmitter is not high enough to satisfy the communication standards. As a result, compound materials such as GaN or GaAs are usually being used in handset applications to increase the output power. Chapter 5 focuses on analysis and design of two CMOS based driver architectures (cascode and house of cards) for driving a GaN power amplifier. The presented results show that the drivers are able to generate  $\Delta V_{out}=5V$ , which is required by the compound transistor, and operate up to 2GHz. Since the CMOS driver is expected to drive an off-chip capacitive load, the interface components, such as bond wires, and decoupling and pad capacitors, play a critical role in the output transient response. Therefore, extensive analysis and simulation results have been done on the interface circuits to investigate their effects on RF transmitter performance. The presented results show that the maximum operating frequency when the driver is connected to a 4pF capacitive load is about 2GHz, which is perfectly matched with the reported values in prior literature.

ii

# DEDICATION

To my kind father, beloved mother, and dear brother.

### ACKNOWLEDGMENTS

I would like to thank my professor "Dr. Jennifer Kitchen" for providing me a great opportunity to learn and get familiar with different topics during my PhD and grow in analog and RF domain. Also, I would like to thank my committee members, "Dr. Sayfe Kiaei", "Dr. Bertan Bakkaloglu", and "Dr. Threvor J. Thornton" for their technical support and also for providing a well-equipped lab for practical measurements. In addition, I would like to thank my friends, Payam Mehr, Ashwath Hedge, Sumit Bhardwaj and Kevin Grout for their great technical help during my education at ASU. But before everyone, I would like to thank my dear family for their kindness and support at all times throughout my entire life. Because I strongly believe that without their help, I could never be able to be in this position in my life.

# TABLE OF CONTENTS

Page

| 1 | INT | FRODUCTION                                             | . 1 |

|---|-----|--------------------------------------------------------|-----|

|   | 1.1 | Wireless Handset Hardware Trends                       | . 1 |

|   | 1.2 | Challenges of PA Design for Cellular Applications      | . 4 |

|   | 1.3 | Silicon CMOS versus Other Compound Materials           | .7  |

|   | 1.4 | Thesis Objectives                                      | 11  |

| 2 | BA  | CKGROUND AND PRIOR ART                                 | 12  |

|   | 2.1 | The Importance of PA Efficiency Improvement            | 12  |

|   | 2.2 | PAPR Reduction Techniques                              | 13  |

|   | 2.3 | Dynamic Range Control                                  | 14  |

|   | 2.4 | Doherty Power Amplifier                                | 15  |

|   | 2.5 | Envelope Elimination and Restoration (EER)             | 17  |

|   | 2.6 | Envelope Tracking (ET)                                 | 18  |

|   | 2.7 | Linear Amplification Using Non-linear Component (LINC) | 21  |

|   | 2.8 | RF DAC-based PAs                                       | 21  |

| 3 | OU  | T-PHASING PA                                           | 23  |

|   | 3.1 | Introduction                                           | 23  |

|   | 3.2 | Power Combiner                                         | 24  |

|   | 3.3 | Power Combining Using Transformers                     | 27  |

# Page

|   | 3.4 | Proposed Power Combining Technique                   | 31 |

|---|-----|------------------------------------------------------|----|

|   | 3.5 | Out-phasing Transmitter Challenges                   | 33 |

|   | 3.6 | State of the Art Analysis                            | 35 |

|   | 3.7 | Conclusion                                           | 38 |

| 4 | AV  | ERAGE POWER TRACKING                                 | 39 |

|   | 4.1 | Introduction                                         | 39 |

|   | 4.2 | Average Power Tracking vs. Envelope Tracking         | 39 |

|   | 4.3 | Proposed Technique and Design                        | 43 |

|   | 4.4 | Metal-Semiconductor Field Effect Transistor (MESFET) | 46 |

|   | 4.5 | Implementation                                       | 52 |

|   | 4.6 | Measurement Results                                  | 58 |

|   | 4.7 | MESFET-MESFET architecture                           | 70 |

|   | 4.8 | MESFET leakage current challenge                     | 74 |

|   | 4.9 | Conclusion                                           | 77 |

| 5 | FU  | LLY DIGITAL TRANSMITTER                              | 79 |

|   | 5.1 | Introduction                                         | 79 |

|   | 5.2 | System level description                             | 79 |

|   | 5.3 | Driver architectures                                 | 82 |

|   | 5.4 | House of Cards (HoC) analysis and design             | 86 |

# Page

| 5.5 Case  | scode analysis and design | 101 |

|-----------|---------------------------|-----|

| 5.6 Inter | erface Discussion         |     |

| 5.7 Boa   | ard design                | 114 |

| 5.7.1     | RF Track design           | 114 |

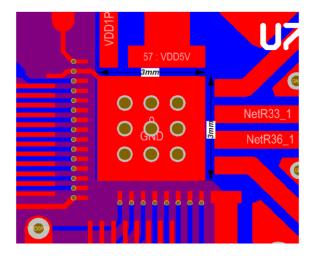

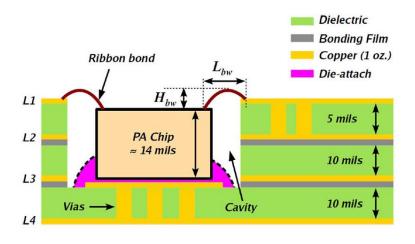

| 5.7.2     | Die Flag Design           | 116 |

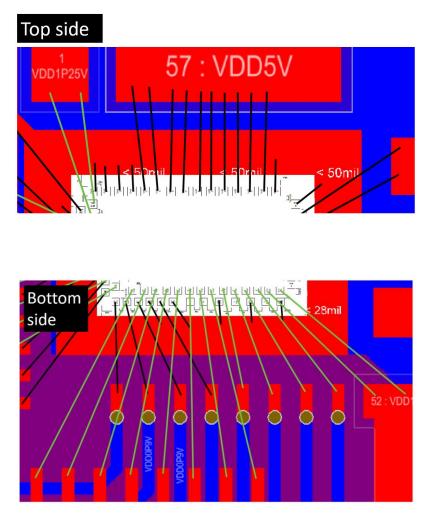

| 5.7.3     | Programmer connection     | 121 |

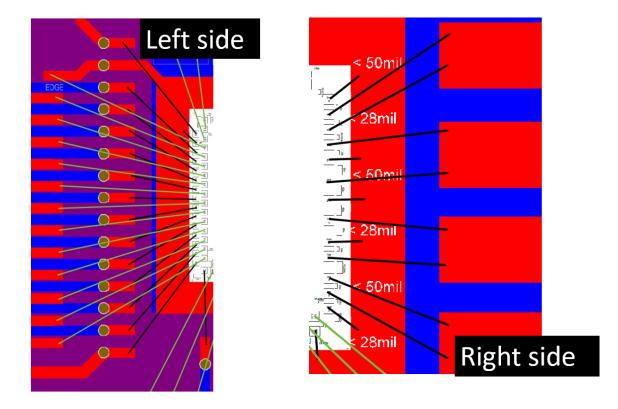

| 5.7.4     | Full board configuration  | 121 |

| 5.8 App   | plication                 | 124 |

| 5.9 Mea   | easurement Results        | 131 |

| 5.10 C    | Conclusion                | 141 |

| 6 REFERE  | ENCES                     |     |

# LIST OF TABLES

| Table                                                                     | Page     |

|---------------------------------------------------------------------------|----------|

| 4-1, Properties of the MESFET under different gate-drain and gate-source  |          |

| distances                                                                 | 47       |

| 5-1, The board specifications                                             | 114      |

| 5-2, Comparison table between the proposed transmitter architecture and t | he state |

| of the art designs                                                        | 140      |

# LIST OF FIGURES

| Figure Page                                                                            |

|----------------------------------------------------------------------------------------|

| 1-1, Number of cell-phone users over time                                              |

| 1-2, Number of cell-phone users over time for different regions                        |

| 1-3, a) Percentage of smart phone usage, b) Comparison between the wireless and device |

| usage2                                                                                 |

| 1-4, Power consumption comparison in different blocks in a low power CMOS              |

| transceiver at 755-928MHz a) Receiver section, b) Transmitter section, Power           |

| consumption comparison in different blocks in a low power CMOS transceiver at          |

| 84-87GHz (Since the transmitter is fully digital, the PLL block has been utilized as   |

| the mixer and therefore, no power dissipation is assigned to the mixer block) c) TX    |

| with BPSK modulation, d) QPSK modulation                                               |

| 1-5, Wireless standard trend over time                                                 |

| 1-6, LTE and 5G standard trend over time                                               |

| 1-7, Movement of the $\pi/4$ QPSK on the constellation diagram                         |

| 1-8, Probability density function of common communication standards a) EDGE, b)        |

| UMTS, c) HSPA, OFDM, e) comparison between the PAPR values of common                   |

| standards7                                                                             |

| 1-9, Properties comparison between Silicon, Gallium-Arsenide and Gallium-Nitride       |

| materials                                                                              |

| 1-10, Cost versus quantity comparison between different materials                      |

| 1-11, Performance (speed, power and efficiency) versus frequency comparison between    |

| the most common materials                                                              |

| 2-1, Linear PA efficiencies as a function of normalized output voltage for different         |

|----------------------------------------------------------------------------------------------|

| classes of operation as well as the pdf of the OFDM signal                                   |

| 2-2, a) The constellation of $\pi/4$ QPSK, b) $3\pi/16-8$ PSK                                |

| 2-3, a) Doherty load modulation basic idea, b) Doherty PA architecture, c) Doherty PA        |

| efficiency versus normalized output power16                                                  |

| 2-4, Envelope elimination and restoration circuit diagram                                    |

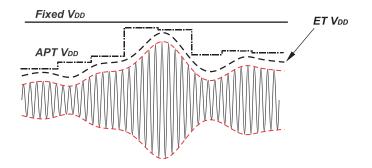

| 2-5, Conventional constant supply voltage PA, variable supply voltage amplifier              |

| 2-6, Out-phasing amplifier system architecture                                               |

| 2-7, RF-DAC overall circuit diagram                                                          |

| 3-1, a) Out-phasing vectors, b)out-phasing system diagram                                    |

| 3-2, a) Isolated power combiner (Wilkinson), b) non-isolated power combiner                  |

| 3-3, a) Out-phasing non-isolating power combiner, b) effective reflection coefficients at    |

| ports V <sub>1, 2</sub>                                                                      |

| 3-4, Output power versus frequency for most common power combiners                           |

| 3-5, a) Series architecture of transformer combiner, b) parallel architecture of transformer |

| combiner                                                                                     |

| 3-6, Power combiner implementation using the package bondwires                               |

| 3-7, Parallel architecture of transformer combiner                                           |

| 3-8, Parallel-series combiner layout architecture                                            |

| 3-9, a) Efficiency comparison between SCT, PCT and PSCT, b) power transmission ratio         |

| comparison between SCT, PCT and PSCT                                                         |

| 3-10, a) circuit diagram of the PSCT for out-phasing architecture, b) the effective          |

|----------------------------------------------------------------------------------------------|

| reflection coefficient at the input ports of the combiner (compensation at 20°) 33           |

| 3-11, Mixed mode (out-phasing and linear) vector description                                 |

| 3-12, a) 4-way outphasing vector diagram, b) comparison between the conventional 2-          |

| way and 4-way effective reflection coefficients                                              |

| 3-13, Comparison between the power factors $(K_p)$ of 2-way and 4-way out-phasing 36         |

| 3-14, Series transformer combiner implementation for 4-way out-phasing                       |

| 4-1, A sample PA circuit diagram                                                             |

| 4-2, A sample semi-sinusoidal wave form                                                      |

| 4-3, Variation of I <sub>D</sub> and V <sub>DS</sub> of the transistor                       |

| 4-4, Full power $I_D$ - $V_{DS}$ movement at full power, power back off (PBO) and when ET is |

| applied                                                                                      |

| 4-5, Comparison between the fixed supply voltage, average power tracking and envelope        |

| tracking                                                                                     |

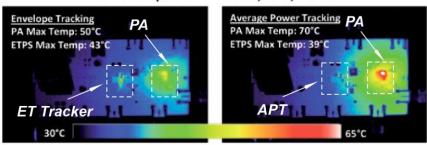

| 4-6, Comparison between the thermal generation of envelope tracking and average power        |

| tracking                                                                                     |

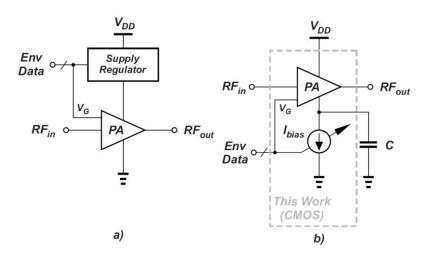

| 4-7, a) conventional envelope tracking technique, b) the proposed power tracking             |

| architecture                                                                                 |

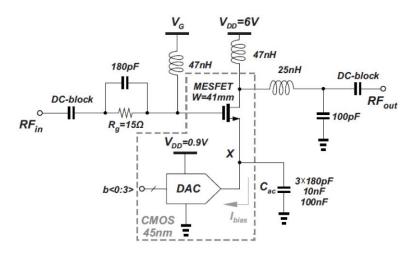

| 4-8, Proposed architecture circuit diagram                                                   |

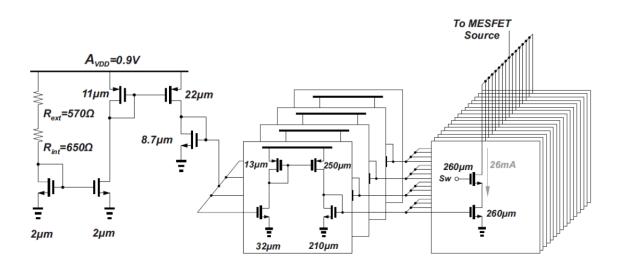

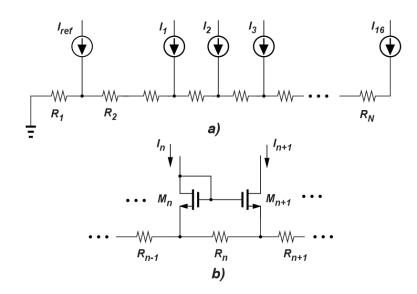

| 4-9, The digital to analog converter (DAC) circuit diagram                                   |

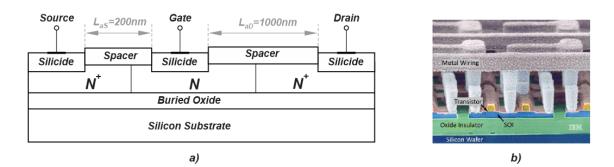

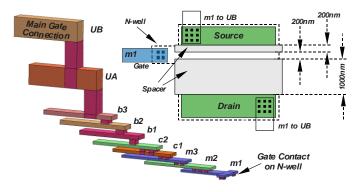

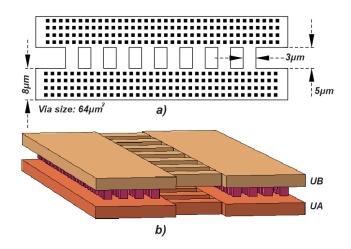

| 4-10, a) MESFET transistor device configuration b) 3D view of the actual device              |

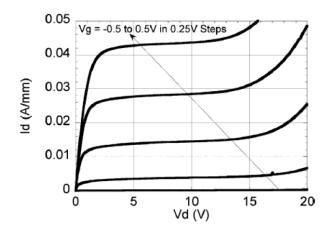

| 4-11, Current density versus V <sub>DS</sub> of the minimum size MESFET transistor           |

| Figure Pa                                                                                | age  |

|------------------------------------------------------------------------------------------|------|

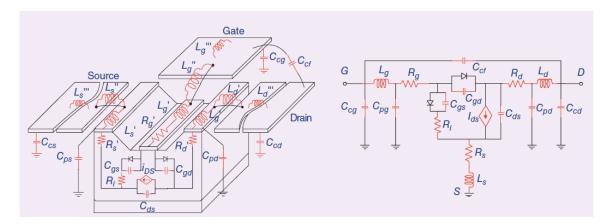

| 4-12, MESFET parasitic modeling and circuit model                                        | . 48 |

| 4-13, Metallization diagram on the gate connections and the fabrication of the MESFE     | Т    |

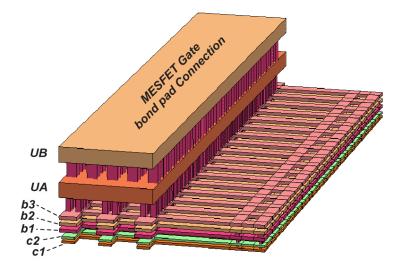

|                                                                                          | . 49 |

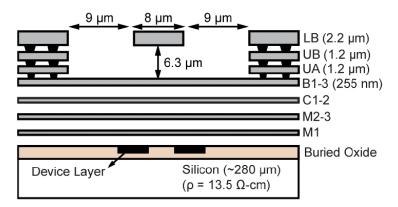

| 4-14, Metal stack up in the 45nm CMOS SOI process                                        | . 49 |

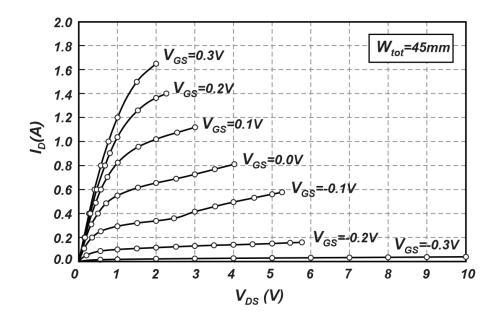

| 4-15, Measured ID-VDs of the MESFET device (W=45mm)                                      | . 50 |

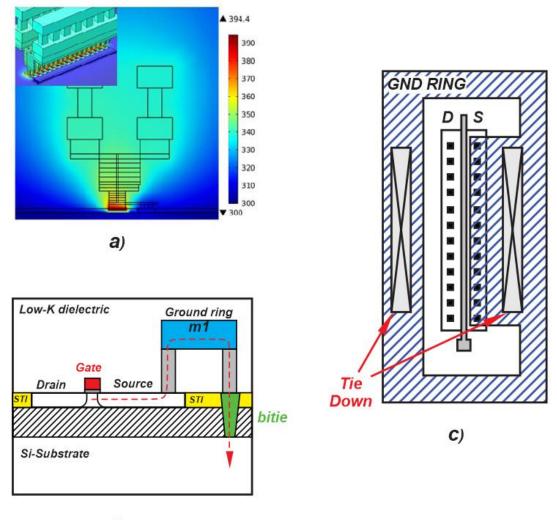

| 4-16, a) Thermal issues in the SOI process, b, c) the methods to release the temperature | e51  |

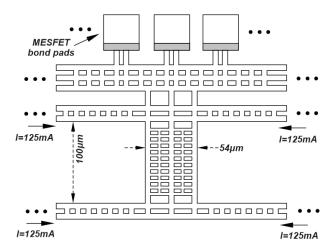

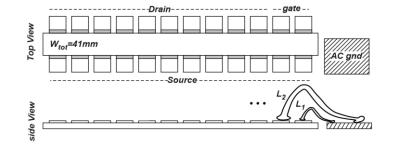

| 4-17, Low impedance routing structure                                                    | . 52 |

| 4-18, The H-shape routing from the DAC to the MESFET                                     | . 52 |

| 4-19, The gate metallization routing on the custom made bond pads                        | . 53 |

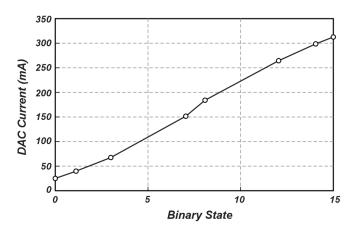

| 4-20, The DAC output current level as a function of the input binary state               | . 53 |

| 4-21, a) Metal routing distributed parasitic resistance, b) The effect of parasitic      |      |

| distributed resistance on the current mirror voltage value                               | . 54 |

| 4-22, The pad arrangement around the MESFET as well as the AC ground connection.         | . 55 |

| 4-23, Providing ac ground at the source of the MESFET                                    | . 55 |

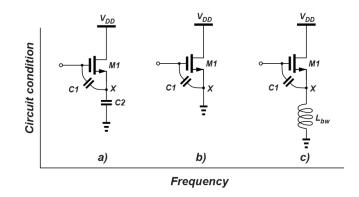

| 4-24, PA condition at different frequencies a) low frequency, b) desired frequency, c)   |      |

| high frequency                                                                           | . 56 |

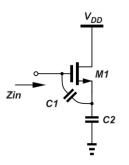

| 4-25, Capacitive feedback configuration in the proposed structure                        | . 56 |

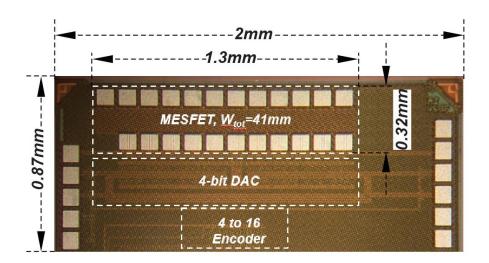

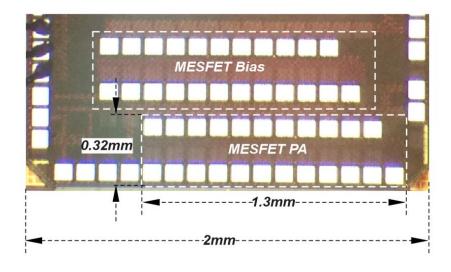

| 4-26, DAC MESFET die photograph                                                          | . 58 |

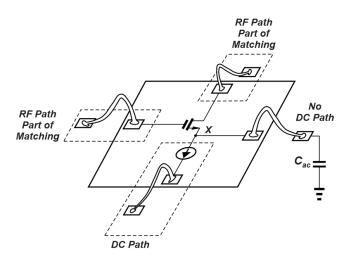

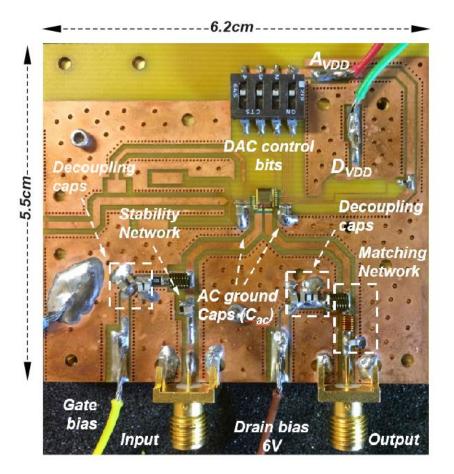

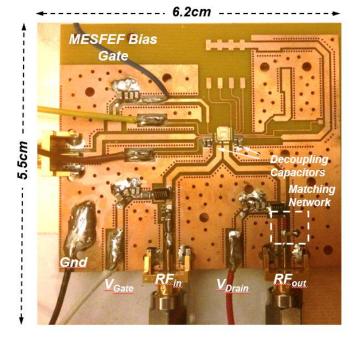

| 4-27, The evaluation PCB configuration                                                   | . 59 |

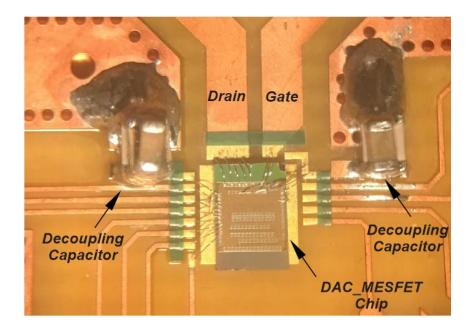

| 4-28, Wire bonded die photograph on the PCB                                              | . 60 |

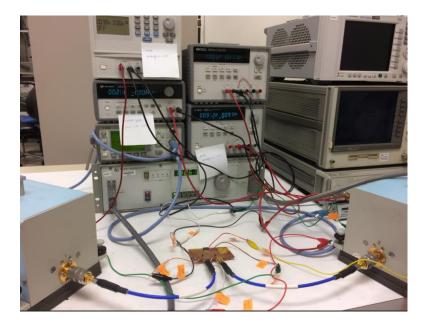

| 4-29, Measurement setup                                                                  | . 61 |

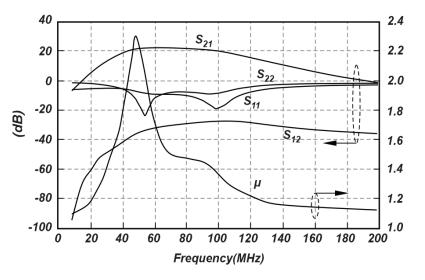

| 4-30, S-parameter measurement result as well as the stability factor over frequency      | . 61 |

| Figure Page                                                                           |

|---------------------------------------------------------------------------------------|

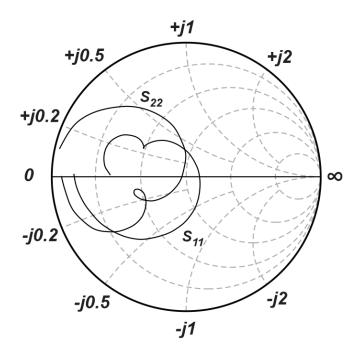

| 4-31, Input and output reflection coefficients                                        |

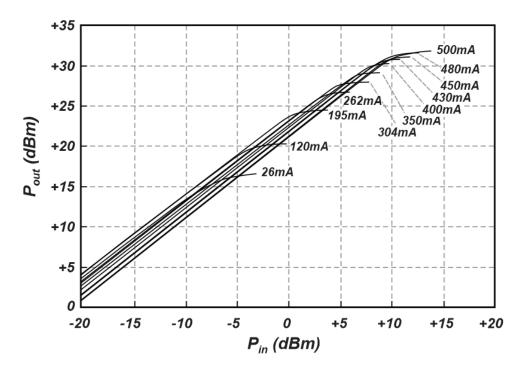

| 4-32, Input-output relationship of the proposed technique                             |

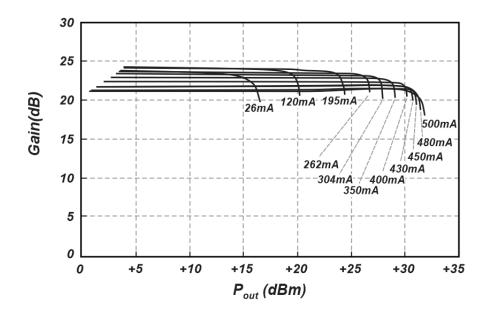

| 4-33, Power gain as a function of output power for different DAC current levels       |

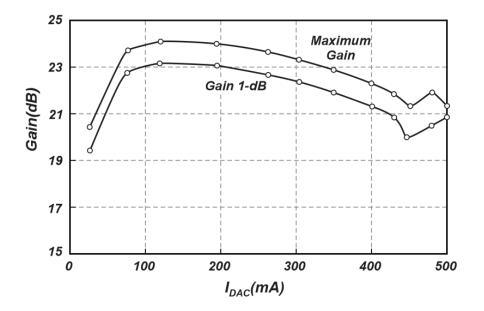

| 4-34, Maximum gain and gain at the 1-dB compression point as a function of DAC        |

| current                                                                               |

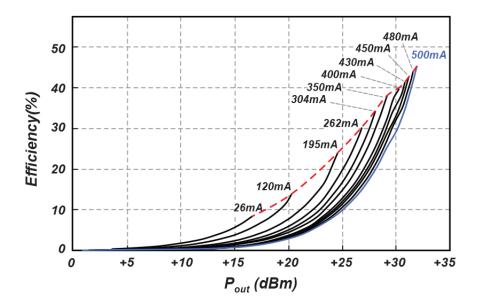

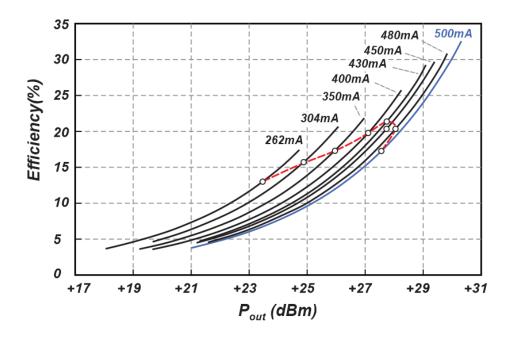

| 4-35, Efficiency versus output power for different DAC current level                  |

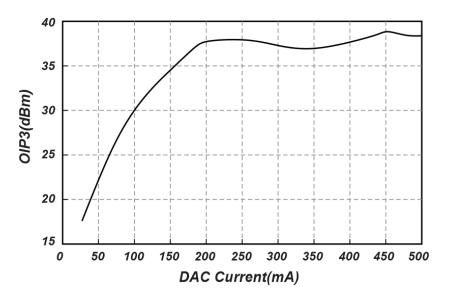

| 4-36, The output intercept variation as a function of DAC current level               |

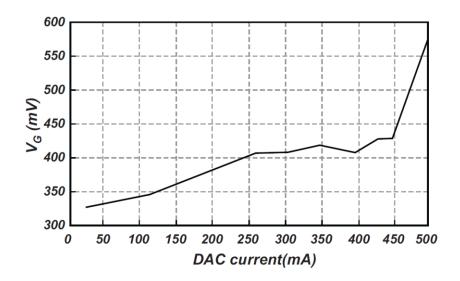

| 4-37, Required voltage on the MESFET gate for proper operation                        |

| 4-38, Efficiency of the modulate waveform as a function of output power for different |

| DAC current levels                                                                    |

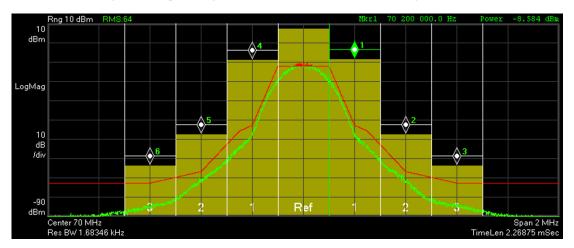

| 4-39, Output spectrum of the EDGE signal                                              |

| 4-40, Output voltage variation over time on the modulated signal constellation        |

| 4-41, The snap shot of the output modulated signal                                    |

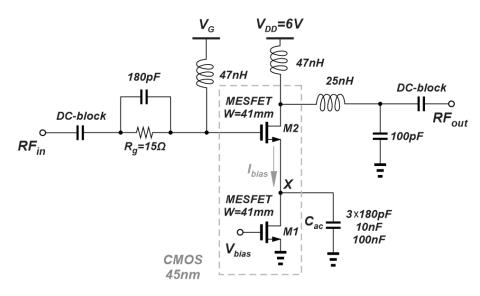

| 4-42, The MESFET-MESFET circuit architecture                                          |

| 4-43, The MESFET-MESFET chip photograph71                                             |

| 4-44, The evaluation board of MESFET-MESFET architecture                              |

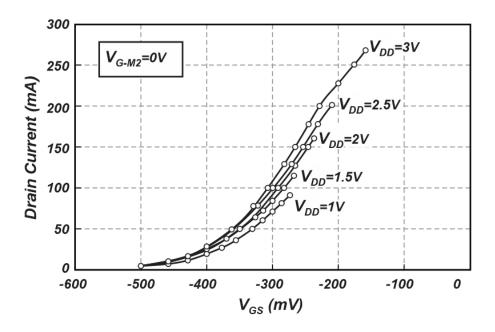

| 4-45, I <sub>D</sub> -V <sub>GS</sub> of the MESFET-MESFET structure                  |

| 4-46, I <sub>D</sub> -V <sub>GS</sub> of the MESFET-MESFET structure                  |

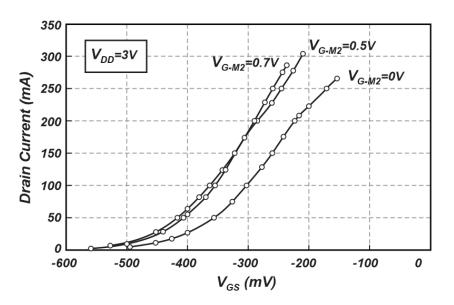

| 4-47, The mid node "X" variation as a function of $V_{GS}$ of the bottom MESFET for   |

| different gate voltage values74                                                       |

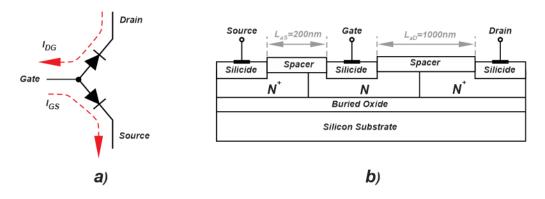

| 4-48, a) The MESFET Schottky diode model, b) MESFET transistor architecture           |

| 4-49, a) diode model of the MESFET transistor, b) Gate leakage current density        |

| Figure                                                                                 | Page |

|----------------------------------------------------------------------------------------|------|

| 4-50, The gate stability resistance placement                                          | 77   |

| 5-1, Conventional transmitter architecture                                             | 80   |

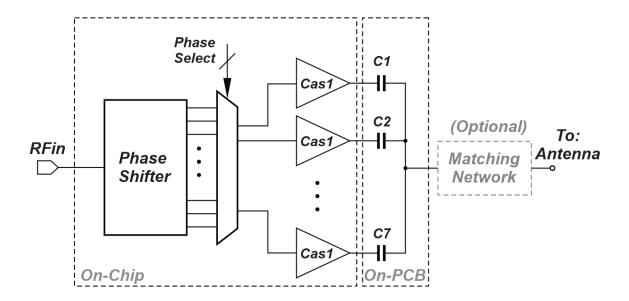

| 5-2, Overall digital transmitter architecture                                          | 80   |

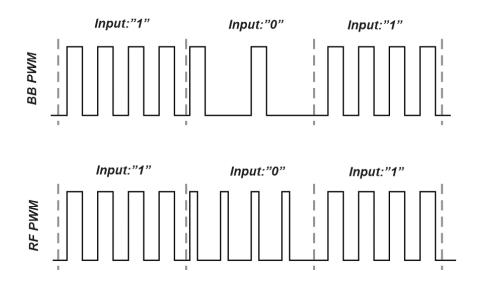

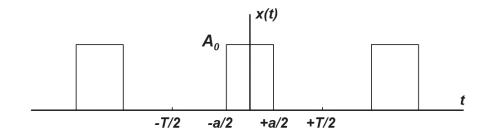

| 5-3, Base band and RF PWM signal wave forms                                            | 81   |

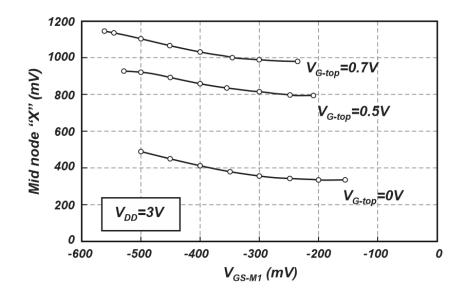

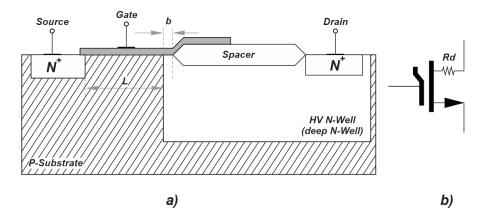

| 5-4, EDMOS transistor a) device structure, b) transistor symbol                        | 83   |

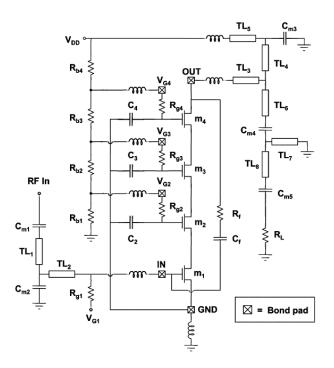

| 5-5, The cascode driver architecture with external biasing on the gates                | 84   |

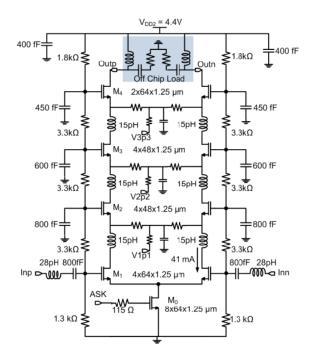

| 5-6, The differential cascode structure                                                | 85   |

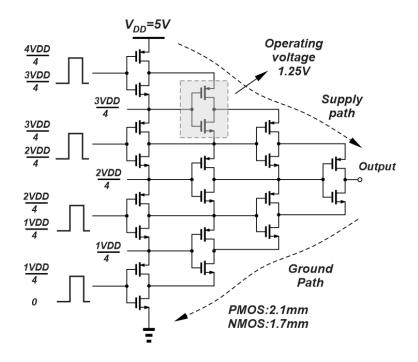

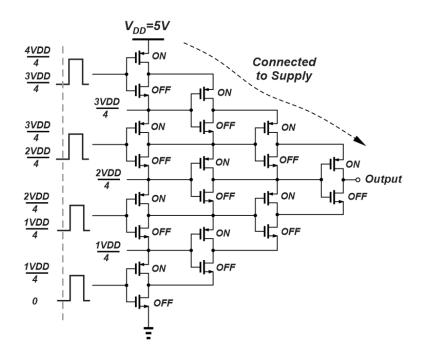

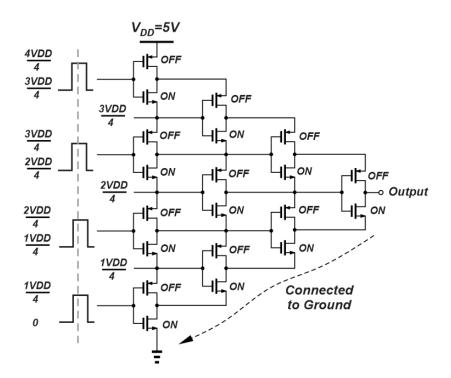

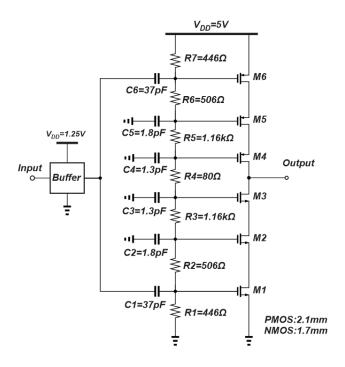

| 5-7, The house of cards architecture                                                   | 85   |

| 5-8, The full house of cards architecture                                              | 86   |

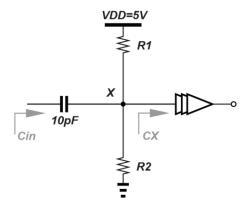

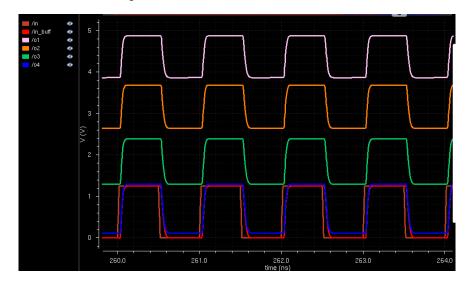

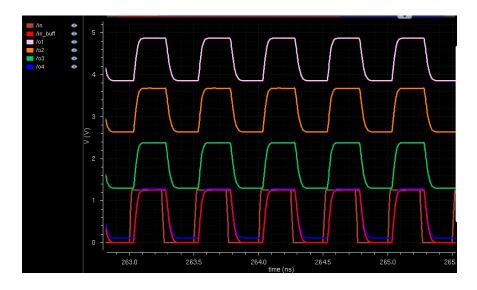

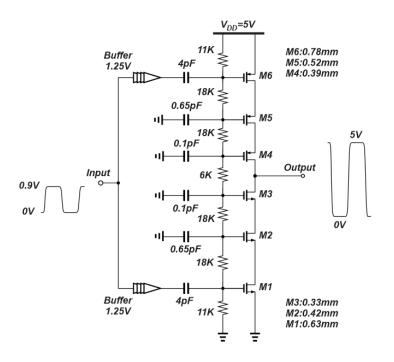

| 5-9, The ideal and post extracted transient response of the input buffer stage         | 87   |

| 5-10, The second stage buffer                                                          | 88   |

| 5-11, The integrated level shifter and input capacitance of the next stage             | 89   |

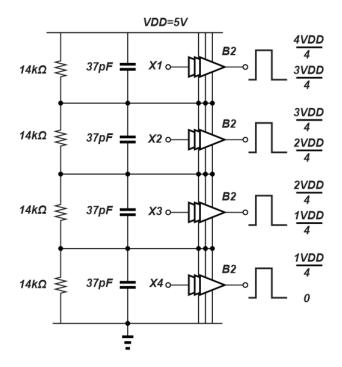

| 5-12, The four cascoded buffer stages                                                  | 90   |

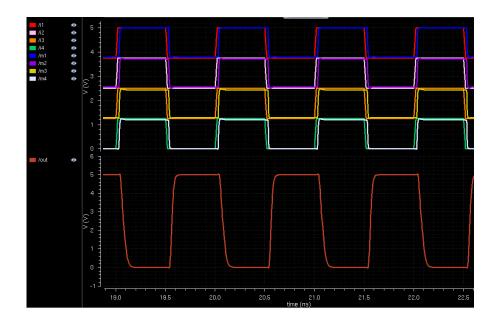

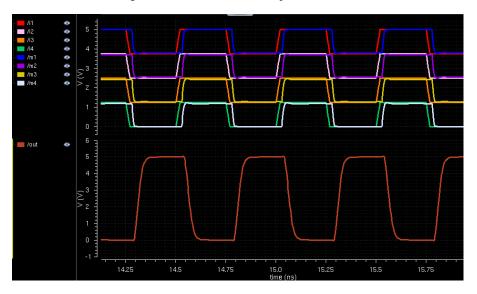

| 5-13, Simulation results of cascode buffer stages                                      | 90   |

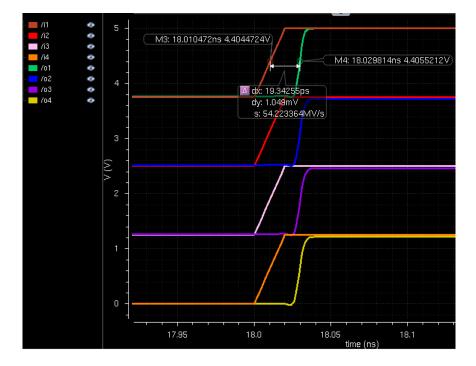

| 5-14, The level shifter simulation results at 500MHz                                   | 91   |

| 5-15, The level shifter simulation results at 1GHz                                     | 91   |

| 5-16, The level shifter simulation results at 2GHz                                     | 92   |

| 5-17, The main house of cards structure                                                | 93   |

| 5-18, The house of cards transistor states when the output is connected to high value. | 94   |

| 5-19, The house of cards transistor states when the output is connected to low value   | 94   |

| 5-20, The house of cards output simulation at 1GHz                                     | 95   |

| 5-21, The house of cards output simulation at 2GHz                                     | 95   |

| Figure Page                                                                               |

|-------------------------------------------------------------------------------------------|

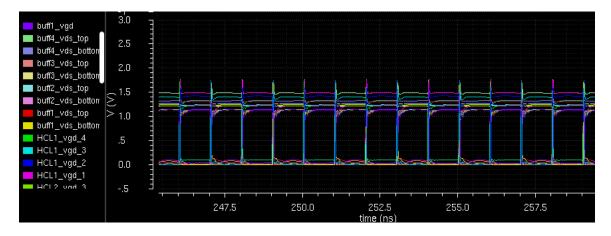

| 5-22, The transistor's terminals voltage                                                  |

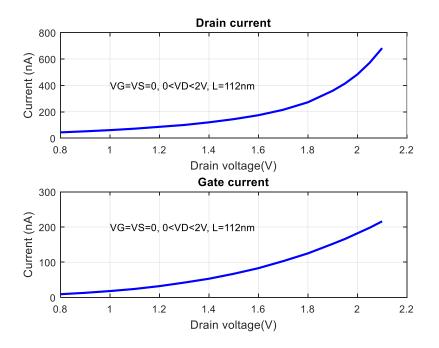

| 5-23, CMOS SOI transistor drain and gate current as a function of the drain voltage       |

| (V <sub>G</sub> =0V)                                                                      |

| 5-24, CMOS SOI transistor drain and gate current as a function of the drain voltage       |

| (V <sub>G</sub> =0.5V)                                                                    |

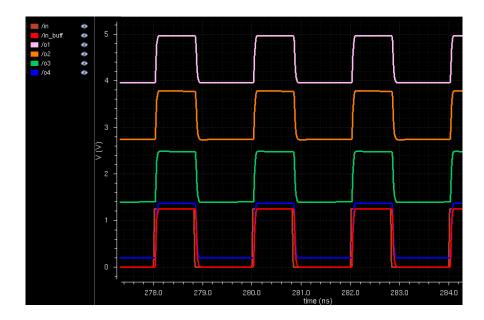

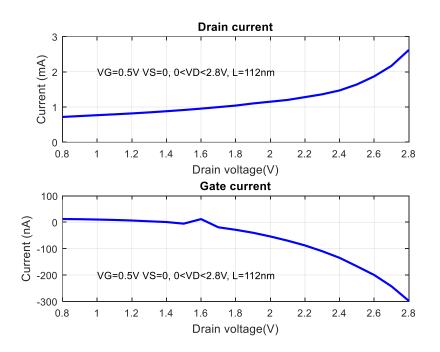

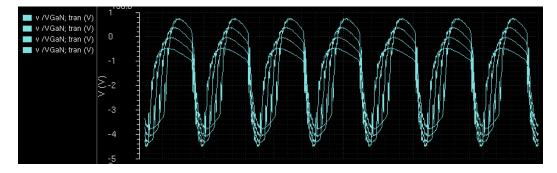

| 5-25, The simulation reslts of the HoC structure for different input signal duty cycle 98 |

| 5-26, GaN transistor modeling for transient simulation                                    |

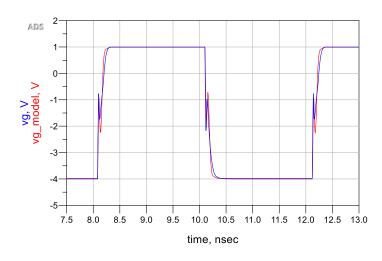

| 5-27, The transient simulation of the actual GaN and the circuit model                    |

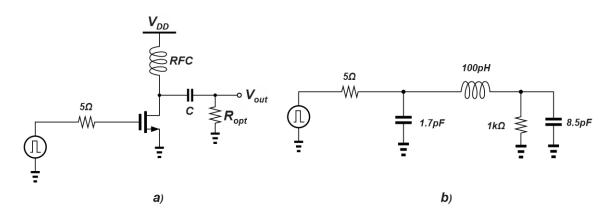

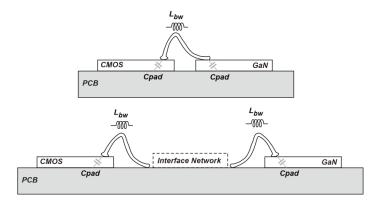

| 5-28, The interface option for CMOS-GaN connection                                        |

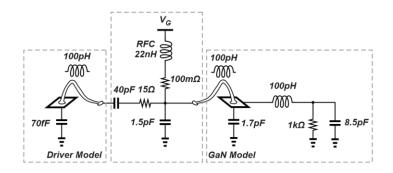

| 5-29, The lumped component model used in the simulation 100                               |

| 5-30, The transient response of the signal at the GaN input node 100                      |

| 5-31, A sample rectangular wave form for duty cycle analysis 101                          |

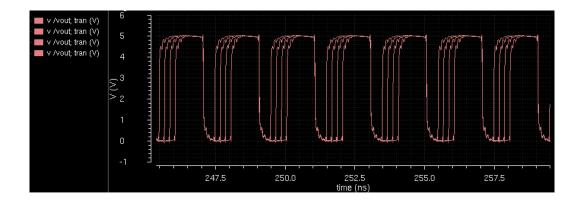

| 5-32, The cascode driver architecture 102                                                 |

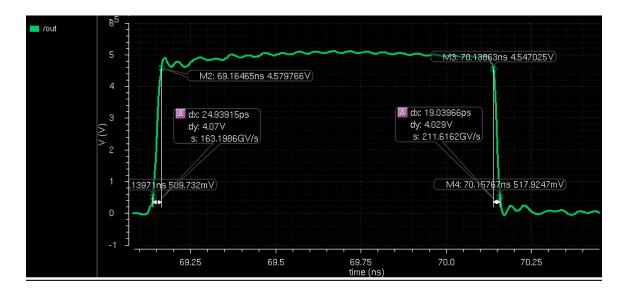

| 5-33, The cascode transient simulation result                                             |

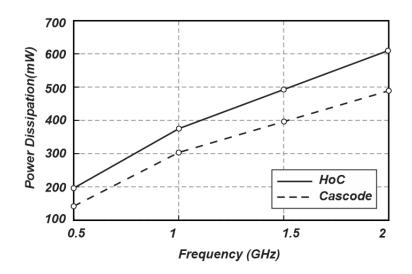

| 5-34, Power dissipation comparison between the cascode and HoC architecture 103           |

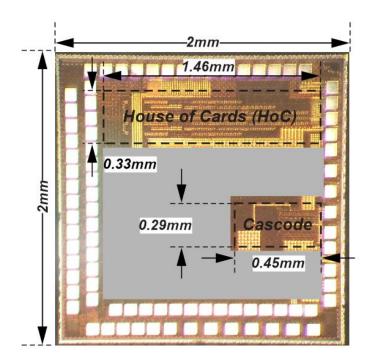

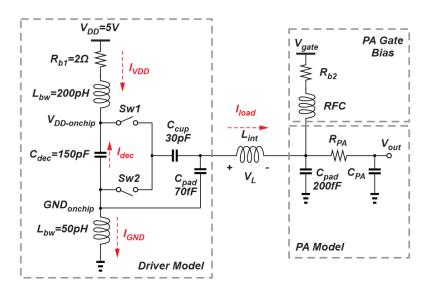

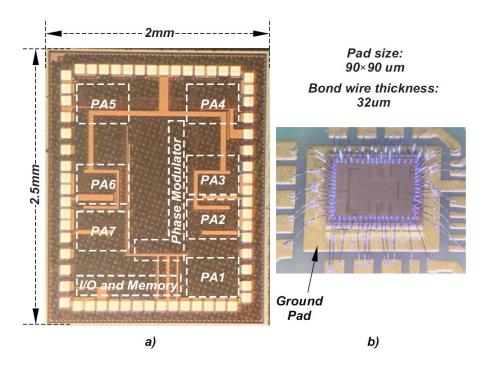

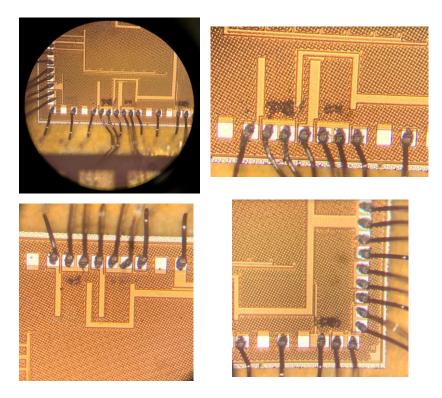

| 5-35, The driver stages chip micrograph 104                                               |

| 5-36, A basic inverter circuit diagram including all the chip connection and decoupling   |

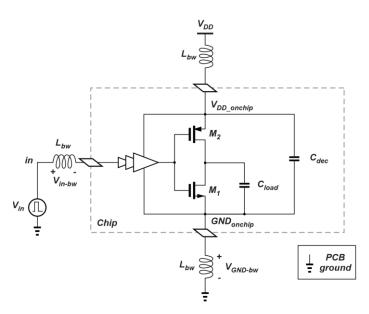

| capacitor with on-chip load 105                                                           |

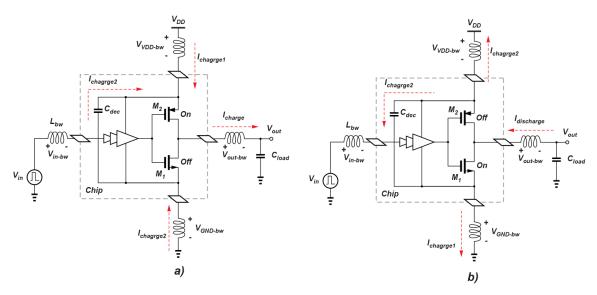

| 5-37, The inverter transient current direction during a) charging and b) discharging      |

| process                                                                                   |

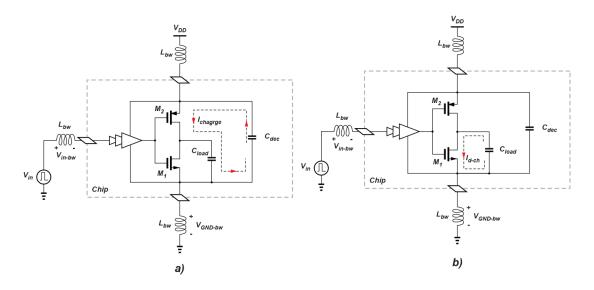

| 5-38, A basic inverter circuit diagram including all the chip connection and decoupling   |

| capacitor with off-chip load 107                                                          |

| 5-39, The inverter transient current direction during a) charging and b) discharging       |

|--------------------------------------------------------------------------------------------|

| process                                                                                    |

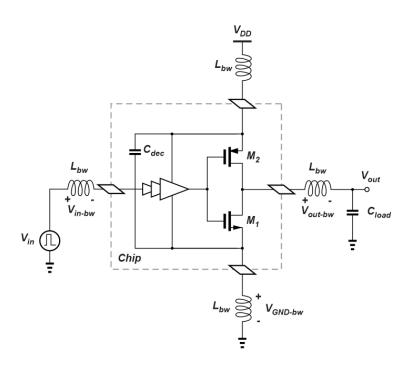

| 5-40, A circuit implementation of a driver stage connected to a general switched mode      |

| PA                                                                                         |

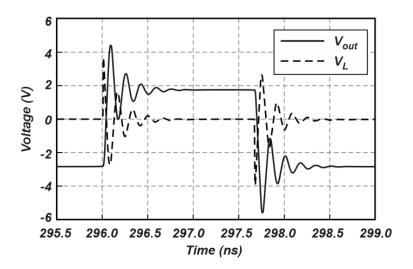

| 5-41, Transient simulation result of the output voltage and the voltage across the output  |

| bond wire                                                                                  |

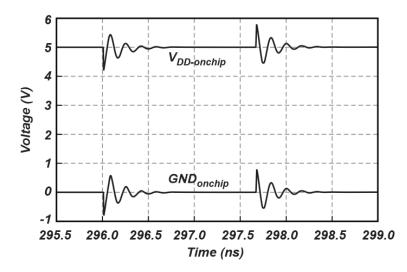

| 5-42, Transient simulation result of on-chip supply and ground 111                         |

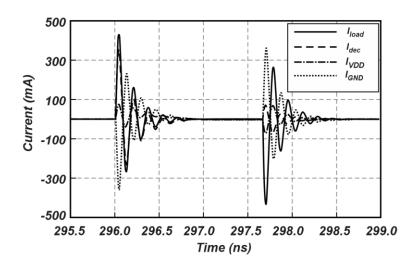

| 5-43, Transient simulation result of the current that passes through the load, decoupling, |

| supply and ground                                                                          |

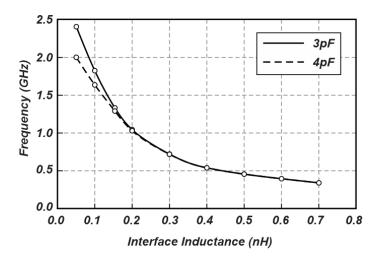

| 5-44, Maximum frequency of operation as a function of load interface inductance for two    |

| different load capacitance 112                                                             |

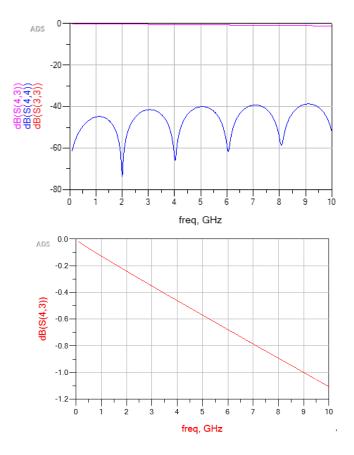

| 5-45, The input return loss as well as the insertion loss of the RF-tracks 115             |

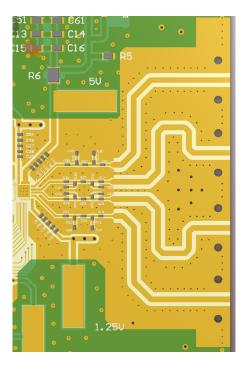

| 5-46, The RF track section on the PCB 116                                                  |

| 5-47, Dimension of the die flag on the PCB 117                                             |

| 5-48, The die attach configuration used in [89] 118                                        |

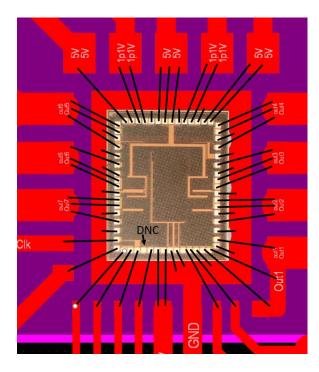

| 5-49, The bonding diagram on the top and bottom of the PCB 119                             |

| 5-50, The bonding diagram at the left and right side of the die 120                        |

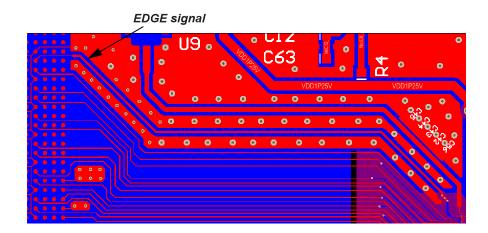

| 5-51, The isolation around clock edge signal                                               |

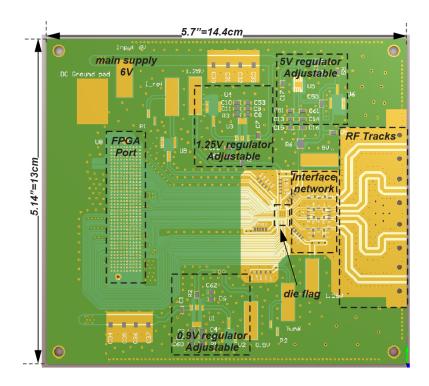

| 5-52, The whole board configuration (Top view)                                             |

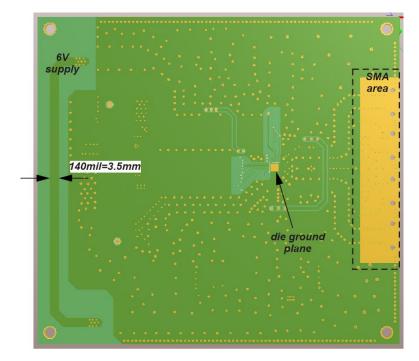

| 5-53, The whole board configuration (Bottom view)                                          |

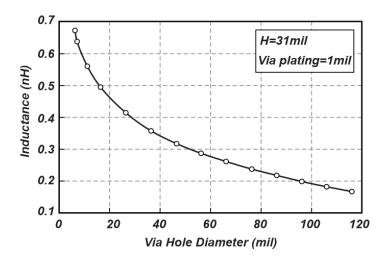

| 5-54, The inductance of a via as a function of hole diameter                               |

| 5-55, Fully digital transmitter architecture                                               |

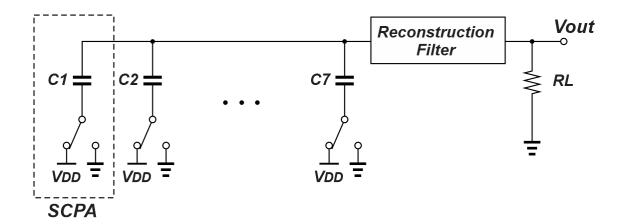

| 5-56, Simplified model of the switched capacitor transmitter architecture 125             |

|-------------------------------------------------------------------------------------------|

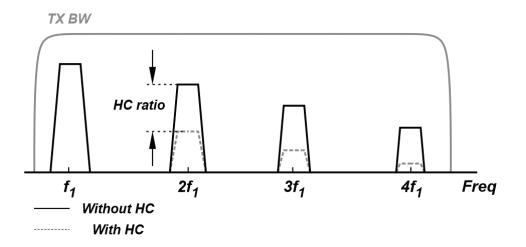

| 5-57, Conceptual explanation of harmonic cancellation (HC) technique 126                  |

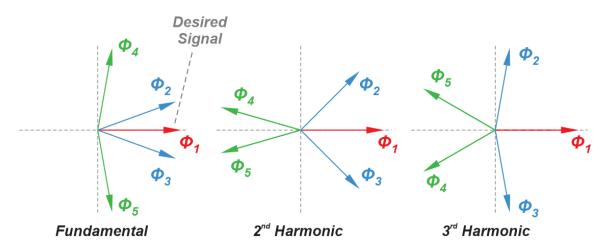

| 5-58, Poly phase harmonic cancellation method description 127                             |

| 5-59, Cascode architecture, optimized for the phase modulator 128                         |

| 5-60, a) Chip photograph of the polyphaser harmonic cancellation transmitter, b) wire-    |

| bonded chip to the PCB 129                                                                |

| 5-61, Bonding map of the proposed switched capacitor driver IC 130                        |

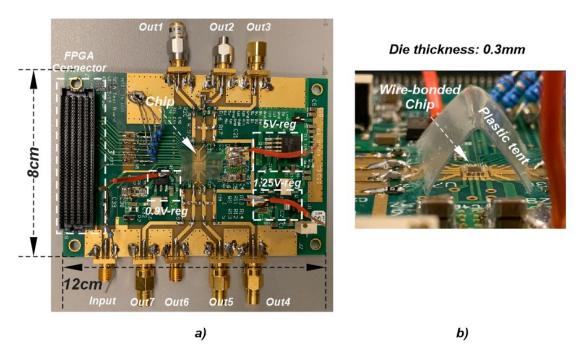

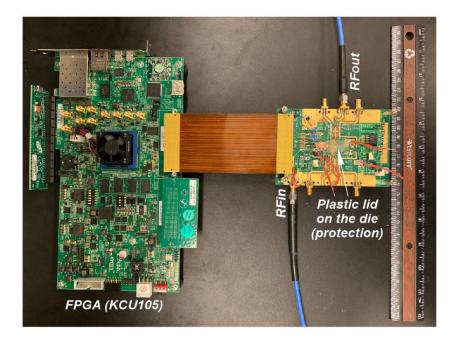

| 5-62, a) PCB configuration, b) plastic cap is placed on top of the die for protection 131 |

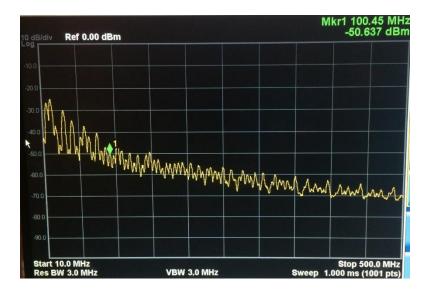

| 5-63, The spectrum of the randomly generated PWM signal (after 20dB attenuation) 132      |

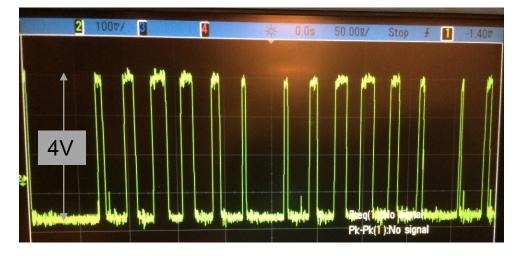

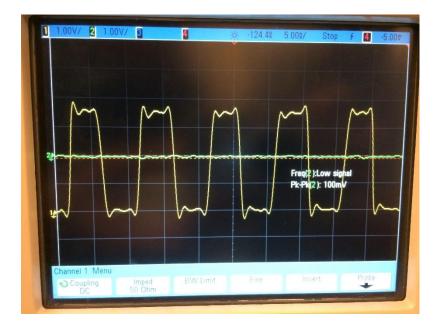

| 5-64, Transient response of the HoC driver stage (after 20dB attenuation) 132             |

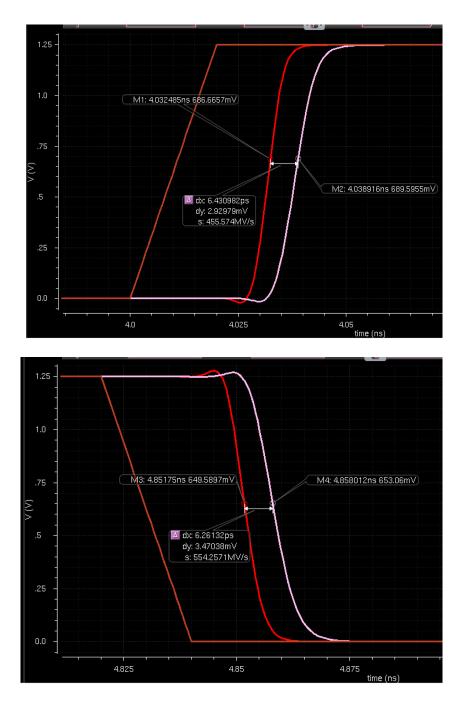

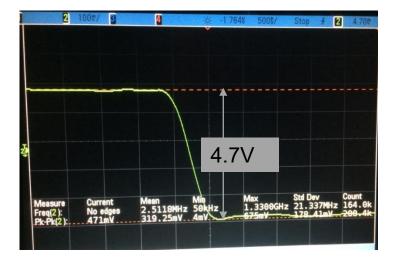

| 5-65, Transient response of the HoC stage (switching speed) 133                           |

| 5-66, Cascode measurement setup                                                           |

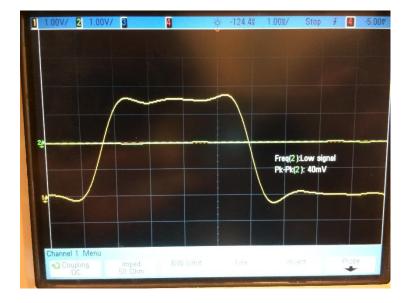

| 5-67, Transient response of one of the cascode driver stages                              |

| 5-68, Transient response of one of the cascode driver stages (zoomed version)             |

| 5-69, The chip micrograph after applying 7V on the chip 135                               |

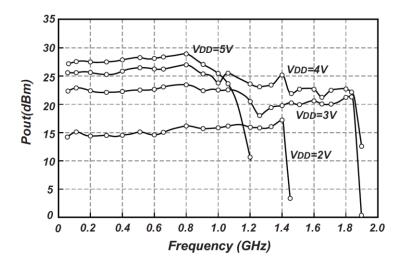

| 5-70, Output power as a function of switching frequency for different supply voltage      |

| levels                                                                                    |

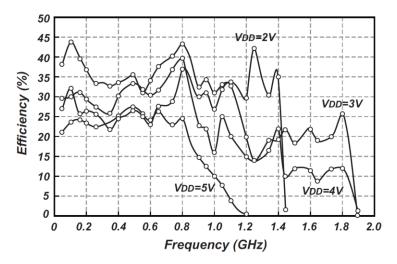

| 5-71, The efficiency of the transmitter module                                            |

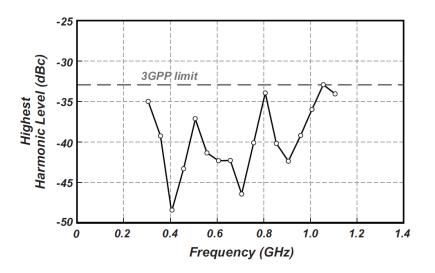

| 5-72, The highest harmonic cancellation level as a function of frequency 137              |

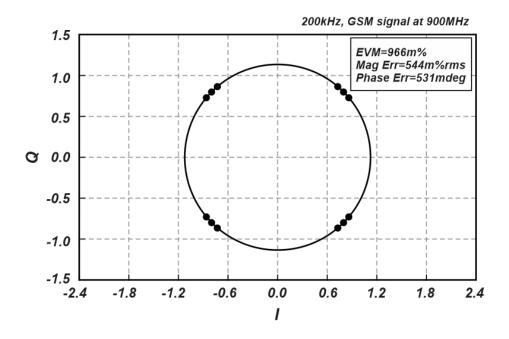

| 5-73, Output constellation of the transmitter when excited by a GSM signal 138            |

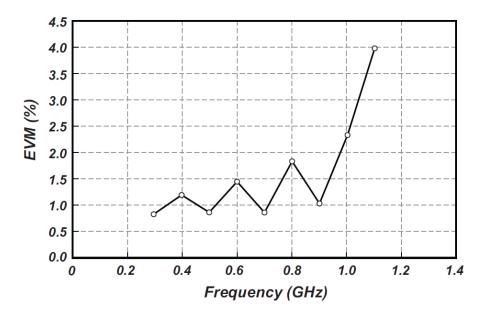

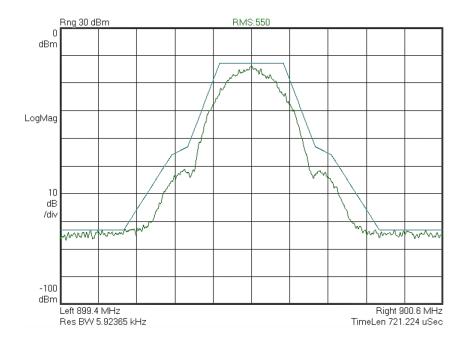

| 5-74, error vector magnitude of the GSM signal as a function of frequency 138             |

| 5-75, The output spectrum of the transmitter (Channel BW=200kHz and carrier |    |

|-----------------------------------------------------------------------------|----|

| frequency=900MHz)1                                                          | 39 |

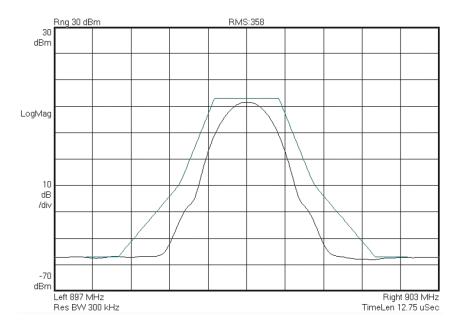

| 5-76, The output spectrum of the transmitter (Channel BW=1MHz and carrier   |    |

| frequency=900MHz)1 | 40 |

|--------------------|----|

|--------------------|----|

### CHAPTER 1

#### INTRODUCTION

## 1.1 Wireless Handset Hardware Trends

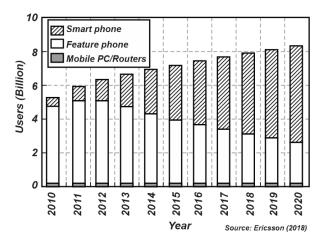

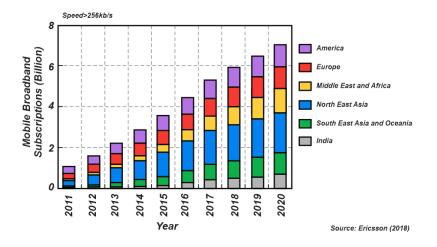

The number of cell phone users has already surpassed the world's population and is expected to reach over 8 billion by 2020, as shown in Fig. 1-1. Furthermore, the number of mobile broadband subscriptions (256kb/s or greater) is continuously increasing over time and becoming more diverse across different areas (Fig. 1-2). With the exponentially growing market for wireless mobile communication, optimizing the performance of the cellphone device, such as processing speed, video quality, memory capacity, power dissipation, linearity, sensitivity and physical size, is critical to the single-user experience as well as to the advancement of wireless technology and overall energy efficiency.

Fig. 1-1, Number of cell-phone users over time

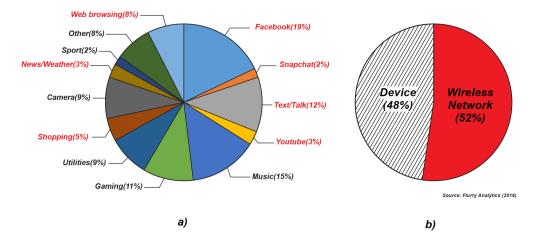

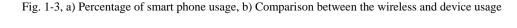

Fig. 1-3a shows a usage breakdown for the different applications on a general smart phone in the United States for an adult in a single day. As can be seen in Fig. 1-3b, the cellular phone is connected to the wireless network over half the time to support the

typical applications. This wireless connection is done through Wi-Fi, Bluetooth or the cellular network using protocol such 4G, LTE. Therefore, to reduce overall power consumption in the handset and increase its battery lifetime, there is a strong need to minimize the wireless transceiver's power consumption.

Fig. 1-2, Number of cell-phone users over time for different regions

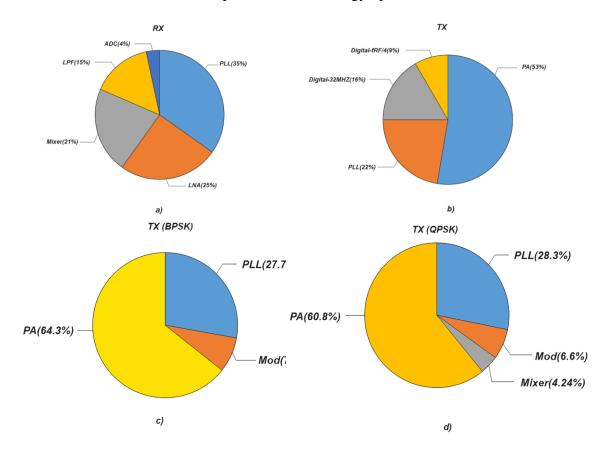

Fig. 1-4 a, b show the power dissipation breakdown of a sample low power receiver (RX) and transmitter (TX) that has been designed in a 40nm CMOS process to meet the IEEE 802.11a and IEEE 802.11h standard requirements with operating frequency from 755MHz to 928MHz [1]. The total power consumption of the RX and TX are  $P_{RX}$ =4.43mW and  $P_{TX}$ =7.2mW respectively. It is quite clear that although the phase

locked loop circuit consumes most of the power in the RX section (P<sub>PLL</sub>=1.55mW), the other stages such as the low noise amplifier (LNA) and the mixers consume approximately the same amount of power.

Unlike the receiver section, the power dissipation in the transmitter has quite a different pattern. As shown in Fig. 1-4b, most of the energy in the transmitter (almost 53%) is dissipated by the power amplifier (about 86% of the energy dissipated by the entire receiver). This unequal power distribution between the PA and the other blocks in the TX section illustrates the importance of PA energy optimization.

Fig. 1-4, Power consumption comparison in different blocks in a low power CMOS transceiver at 755-928MHz a) Receiver section, b) Transmitter section, Power consumption comparison in different blocks in a low power CMOS transceiver at 84-87GHz (Since the transmitter is fully digital, the PLL block has been utilized as the mixer and therefore, no power dissipation is assigned to the mixer block) c) TX with BPSK modulation, d) QPSK modulation

Since 5G communications and beyond is moving toward millimeter wave frequencies for transmission, Fig. 1-4 c, d show the power dissipation breakdown of a low power transmitter at the W-band (84-87GHz) for BPSK and QPSK modulations in a 65nm CMOS process [2]. The PA again dissipates a significant portion of the power consumption (more than 60%), and this example also demonstrates the need for increasing efficiency in millimeter wave power amplifiers. The work of this thesis presents efficiency-enhancement methodologies for CMOS power amplifiers and predrivers.

## 1.2 Challenges of PA Design for Cellular Applications

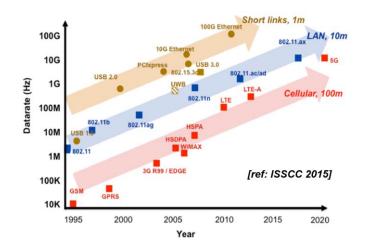

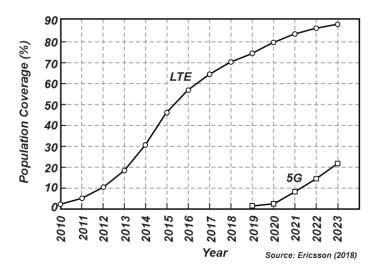

In recent years, the demand for high speed communication has grown significantly, with 100 times data rate increase within a 10-year span. This significant expansion is illustrated in Fig. 1-5, which plots the data rate trend for three main communication networks (short links, LAN and cellular). Fig. 1-6 shows the percentage utilization of the new generation communication standards (LTE and 5G), demonstrating that LTE is popular among the total wireless users in the US and 5G is expected to become operational in 2019.

Fig. 1-5, Wireless standard trend over time

Fig. 1-6, LTE and 5G standard trend over time

One of the main solutions to increase the data bit rate in cellular networks is to utilize digital communication standards such as GSM, WCDMA and LTE [3]. In order to satisfy the required data rate, these communication protocols use advanced digital modulation techniques such as OOK, PSK, QPSK, 16QAM and OFDM. Due to the fact that these techniques modulate the signal in amplitude and phase domains, the transmitted RF signal continuously varies in output power. The average transmitted output power is mainly set based on the distance between the cell phone (handset) and the base station tower. Whereas the peak power with respect to the average power will depend upon the wireless modulation scheme.

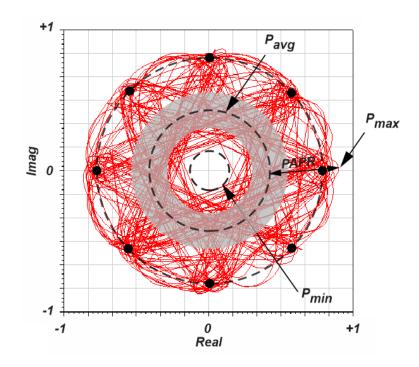

Fig. 1-7, Movement of the  $\pi/4$  QPSK on the constellation diagram

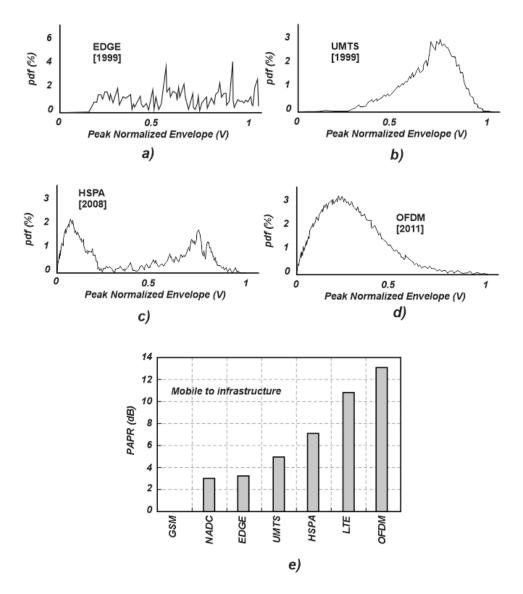

The ratio between the maximum (peak) output power and the average power is defined as peak to average power ratio (PAPR). PAPR is a critical parameter in wireless telecommunications because higher PAPR typically correlates to higher linearity requirements and power consumption in a wireless transceiver. Fig. 1-7 shows the movement of the output signal vector on the constellation diagram over time for  $\pi/4$  QPSK modulation. This example illustrates that the maximum output power (P<sub>max</sub>) does not happen very often, and most of the time the output power level is below the P<sub>max</sub>. In order to characterize the power distribution of a wireless modulation scheme (standard) over time, the probability density function (pdf) of the transmitted output signal is used. Fig. 1-8 a-d show the pdf of different digital communication standards. As can be seen, the peak of the pdf moves towards the left for more advanced schemes such as OFDM, which means high PAPR value in recent wireless systems. Fig. 1-8e summarizes the PAPR values for the most common digital standards [4]. There is a significant need to

develop high efficiency power amplifiers that process these high PAPR signals for supporting future-generation communications standards.

Fig. 1-8, Probability density function of common communication standards a) EDGE, b) UMTS, c) HSPA, OFDM, e) comparison between the PAPR values of common standards

# 1.3 Silicon CMOS versus Other Compound Materials

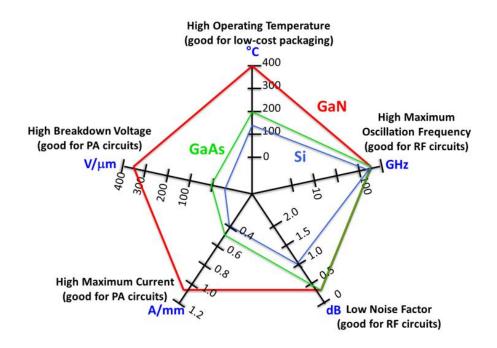

Traditionally, compound devices such as SiGe and GaAs have been utilized for high power generation in handset applications because of their superior device performances, including high break down voltage capability, high unity gain frequency (f<sub>T</sub>), low substrate loss, low source path resistance to ground, high thermal conductivity through the substrate, and low loss metallization (thick metal layers). Fig. 1-9 compares most of the important parameters in the compound devices to the silicon process.

Fig. 1-9,Properties comparison between Silicon, Gallium-Arsenide and Gallium-Nitride materials Although the compound processes show benefits over silicon technology in some aspects, there are several advantages associated with silicon IC processes that motivate designers to use this technology over the compound processes. These important aspects are listed below:

- Low yield loss of silicon integrated circuits compared to the compound materials

- 2) High component-count integration of silicon devices

- 3) Silicon's low cost final price [5]

- Capability for integrating the digital processing unit and the PA on the same substrate

### 5) Available high speed CMOS architectures

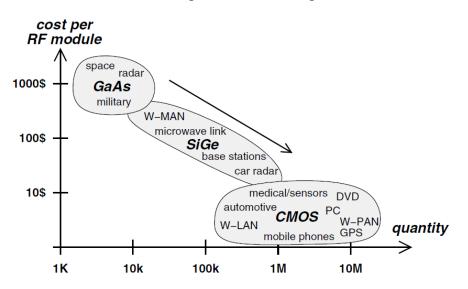

Since silicon-based architectures have high yield compared to compound processes, designers prefer to use silicon technology when integrating a large numbers of transistors. When compared with GaN, the cost of silicon-based products is much lower because GaN requires higher purity silicon/SiC substrate material, is implemented on smaller wafer size, and has significantly lower yield. Fig. 1-10 compares CMOS process technology with two of the most common compound processes (GaAs and SiGe) in terms of number of products and applications [5]. Fig. 1-10 demonstrates that the CMOS based RF modules are more cost effective compared to other compound materials.

Fig. 1-10, Cost versus quantity comparison between different materials

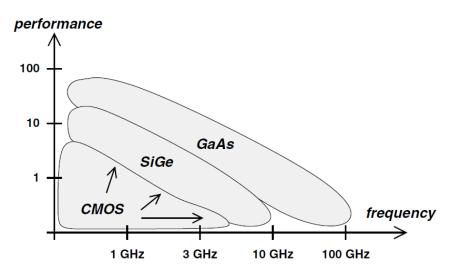

Furthermore, the number of integrated transistors in GaAs and GaN compound technologies has typically been limited to less than 40 devices per die. But, the CMOS process provides the capability of fabricating millions of transistors on the same substrate. As a result, CMOS processes are the most promising option for high volume fabrication. Recently, novel techniques have been proposed to design highly efficient CMOS PAs at high frequencies [6], therefore enabling integration of the digital signal processor with the high-frequency wireless transmitter (PA). Fig. 1-11 compares CMOS with SiGe and GaAs [5] in terms of frequency (speed) and performance (power and efficiency). Although the compound transistors intrinsically provide high performance, new circuit and system level techniques in CMOS are enabling higher power levels and pushing the performance of CMOS to compare with that of SiGe and GaAs.

Fig. 1-11, Performance (speed, power and efficiency) versus frequency comparison between the most common materials

# 1.4 Thesis Objectives

The availability and popularity of mobile handsets has been discussed, and it has been shown that the reliability and cost of wireless modules motivates the desire for using CMOS PAs instead of compound materials.

The main purpose of this dissertation is to investigate and analyze small form factor CMOS based efficiency enhancement techniques for high PAPR signals that are applicable to handset applications. This research proposes three different efficiency enhancement methods: 1) average power tracking (APT) using a current steering DAC, 2) implementation of a digital driver for a GaN power amplifier and 3) small form factor transformer based power combiner for out-phasing transmitters.

This dissertation organized as follows: Chapter 2 reviews the background and prior works for efficiency enhancement techniques in handsets. Chapter 3 explains the out-phasing efficiency enhancement method and proposes an implementation technique for a small form factor power combiner that is suitable for CMOS integration. In chapter 4, the APT technique will be discussed and the proposed current steering DAC based efficiency improvement technique will be explained. Chapter 5, introduces a CMOSbased driver (digital power amplifier) that is suitable for fully digital transmitters and all the challenges associated with the implementation will be analyzed and discussed.

11

### CHAPTER 2

#### BACKGROUND AND PRIOR ART

This chapter reviews the most popular techniques that have been utilized to enhance the efficiency of the PA block, focusing on the techniques that are applicable to CMOS PAs for handset applications. These techniques include PAPR reduction [7-9], Dynamic range control [4], Doherty [10], envelope elimination and restoration (EER) [11], envelope tracking (ET) [12] and Out-phasing [13].

2.1 The Importance of PA Efficiency Improvement

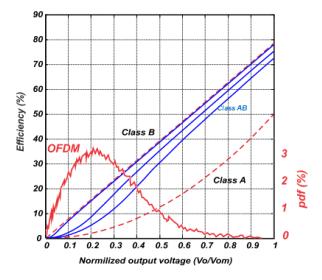

As mentioned in Chapter 1, the utilization of advanced digital modulation techniques in new communication standards increases the PAPR of the output signal. In order to understand the degradation effect of high PAPR on the PA performance, Fig. 2-1 plots the pdf of the OFDM (PAPR≈13dB) signal on top of the efficiency versus normalized output voltage for different classes of linear PAs.

Fig. 2-1, Linear PA efficiencies as a function of normalized output voltage for different classes of operation as well as the pdf of the OFDM signal

From the pdf of Fig. 2-1, it is apparent that the OFDM signal spends the majority of its time at voltage levels where linear PAs are highly inefficient. Although moving from class "A" toward class "AB" and "B" improves the PA efficiency, the best effective efficiency is still less than 20% (a value that does not satisfy most of the cell-phone transmitter requirement). Therefore, there is a trade-off between the linearity and efficiency of the PAs. Class "A" PA, which is the most linear type of PA, has the lowest efficiency among the class "AB, B" counterpart. In order to improve the low efficiency of the PAs at high PBO levels several system and circuit level techniques have been proposed.

#### 2.2 PAPR Reduction Techniques

The efficiency of the PA reduces significantly when the output power of the PA is highly backed off from the maximum available output power. This degradation in efficiency affects the overall transmitter efficiency when it processes a digital signal with high PAPR value. In [7-9], some techniques have been presented to reduce the PAPR value of the OFDM signal. The principle of this technique is based on analyzing the modulated signal statistically over time and checking how often the signal has a high PAPR value. If the high PAPR value occurs very infrequently, then the signal predistortion techniques such as peak windowing can be applied on the modulated signal to reduce the PAPR value. It has been shown in [7] that the PAPR of about 4dB can be achieved with this technique for an arbitrary number of subscribers at the cost of a slight increase in bit error rate (BER). In [8] it has been shown that by increasing the number of channels in the OFDM system, the probability of high PAPR reduces. Mainly, the PAPR reduction techniques can be organized into two different categories: 1) Signal scrambling

13

techniques (ex. partial transmission sequence (PTS)), 2) signal distortion techniques (ex. Clipping) [9].

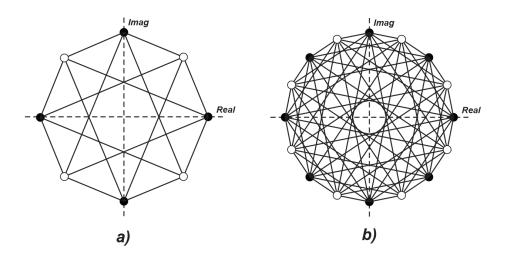

## 2.3 Dynamic Range Control

It is required that the signal applied to the PA does not have a zero envelope (zero power) value. Otherwise, the phase of the input signal has discontinuity and as a result, the transmitted signal becomes highly nonlinear [4]. Under this condition, the PA must be highly linear, especially at zero magnitude. Implementing the PA with a wide range of linearity requires high power dissipation and eventually degrades the overall efficiency of the transmitter. Since the zero envelope value means passing through the origin of the constellation diagram of the modulated input signal, traditionally a technique, called constellation rotation, has been proposed [4]. In this method, two similar constellation diagrams are put on top of each other with some phase rotation between them. By assigning one symbol to one of these constellations and the adjacent one to the other constellation the origin transition will be prevented. The other technique that prevents origin crossing is to set an offset of about half of the symbol time between the in-phase (I) and quadrature (Q) signals [4]. As an example, two of the most common digital modulations that are  $\pi/4$ -QPSK (used in NADC, TETRA and Bluetooth) and  $3\pi/16$ -8PSK (used in EDGE) are shown in Fig. 2-2 a, b respectively.

Fig. 2-2, a) The constellation of  $\pi/4$  QPSK, b)  $3\pi/16$ -8PSK

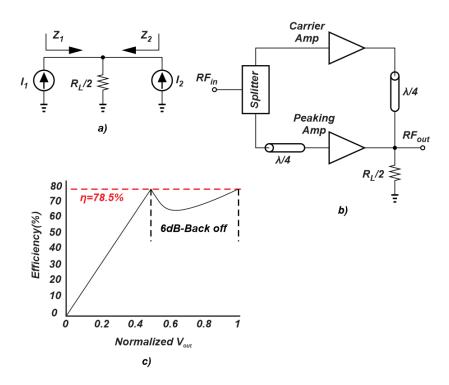

#### 2.4 Doherty Power Amplifier

This type of efficiency enhancement technique, which is proposed in [10] for the first time, is based on load modulation. The basic concept, the architecture and the efficiency of this amplifier are shown in Fig. 2-3. The linear amplifiers are modeled with current sources and the load is set to  $R_L/2$ . When the input power is at high backed off power, the I<sub>2</sub> current source is zero and all the output current is provided by the I<sub>1</sub>. When the input power is close to the maximum power, the I<sub>2</sub> starts to conduct and provides some portion of the output current. If at the full input driver power level these two currents are equal, the Doherty amplifier is called symmetric. Otherwise, it is called asymmetric Doherty PA. The effective input impedances seen from each current source are:

$$Z_1 = \frac{R_L}{2} \left(1 + \frac{I_2}{I_1}\right) \tag{2-1}$$

$$Z_2 = \frac{R_L}{2} \left(1 + \frac{I_1}{I_2}\right) \tag{2-2}$$

When  $I_2=0$ ,  $Z_1=R_L/2$  and the impedance seen by the  $I_2$  current source  $Z_2=\infty$  and when both current sources generate the same amount of current ( $I_2=I_1$ ) they see similar impedances ( $Z_1=Z_2=R_L$ ). It is quite clear that the I<sub>2</sub> current source changes the impedance that the I<sub>1</sub> current source sees or in another word, I<sub>2</sub> modulates the impedance that the I<sub>1</sub> sees (load modulation). By placing the quarter wave length transmission lines, increasing the I<sub>2</sub> reduces the impedance seen by I<sub>1</sub> current source. Since there are two points within the I<sub>2</sub> transition (from zero to the maximum) that provide the optimum impedance required by the I<sub>1</sub> (carrier amplifier) the overall efficiency curve has two peak points. Note that since in this analysis the maximum available currents are equal, the back off peak efficiency point is 6dB lower than the peak at the full output power. This simple analysis reveals that the symmetric Doherty amplifier improves the efficiency at 6dB PBO. Adjusting the I<sub>2</sub> current value into a larger levels, moves the PBO efficiency improvement point to the lower output power levels (higher PAPR values) and vice versa.

Fig. 2-3, a) Doherty load modulation basic idea, b) Doherty PA architecture, c) Doherty PA efficiency versus normalized output power

Although the Doherty PA architecture improves the efficiency of the overall PA, since it requires transmission lines for impedance transformation, at low operating frequency this architecture is quite bulky. Therefore, the Doherty PA is not area efficient for handset mobile phones. This is why the Doherty PAs are commonly used only in base stations. In [14, 15], it has been shown that by implementing the transmission lines via lumped components, the size of the Doherty PA can be optimized for the mobile applications. Reference [16] provides a great review of the most recent Doherty PAs improvement.

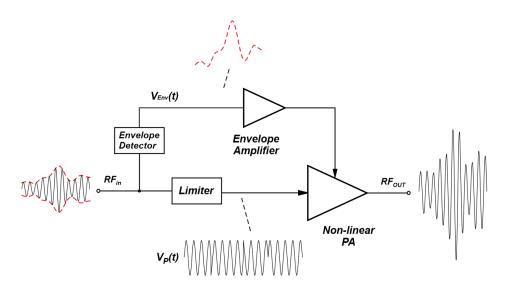

## 2.5 Envelope Elimination and Restoration (EER)

Envelope Elimination and Restoration (EER) was introduced in [11] for the first time and is shown in Fig. 2-4. This technique splits the input RF signal into phase and amplitude via an envelope detector and a limiter. Since the phase information signal has a constant envelope this signal can be processed by a non-linear amplifier such as class-C PA. As shown, the envelope of the input signal (V<sub>Env</sub>) amplifies by an amplifier and modulates the supply node of the main non-linear PA. Since the output of the non-linear PA is a direct function of the supply voltage [12], varying the supply node of the main PA with the envelope information, modulates the amplified version of the phase signal (the input to the PA). As a result, at the output node, the amplified version of the input signal delivers to the load impedance.

Fig. 2-4, Envelope elimination and restoration circuit diagram

One of the major disadvantages of this type of amplifier is the envelope tracking and amplification. Since the envelope of the signal is a non-linear function of the main input RF signal ( $V_{env} = \sqrt{I^2 + Q^2}$ ), where I and Q are the in-phase and quadrature components of the input signal, the bandwidth of the envelope signal is 3-4 times wider than the bandwidth of the input signal. As a result, the envelope path, especially the envelope amplifier, needs to be wide band. Enhancing the bandwidth of the envelope amplifier increases the power dissipation of this block, which affects the overall efficiency of the transmitter.

# 2.6 Envelope Tracking (ET)

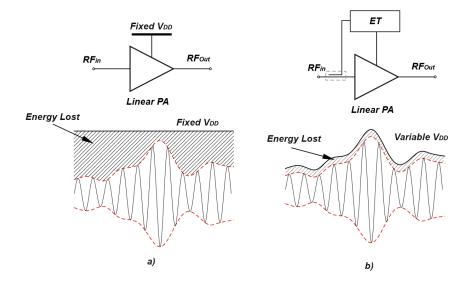

The idea behind the envelope tracking PA, which is show in Fig. 2-5, is similar to the EER method. The main difference between these two methods is the type of amplifier in the transmitter. Unlike the EER, which uses non-linear PA, ET amplifier utilizes a linear mode PA since it processes the amplitude and phase of the input signal at the same time [4, 12]. In this technique the supply modulator changes the supply voltage of the PA

instantaneously with the input signal envelope. As a result, the DC power dissipation of the PA reduces when low output power level is required.

Fig. 2-5, Conventional constant supply voltage PA, variable supply voltage amplifier Because of the maximum RF output power is a strong function of the supply voltage and the DC power dissipation is a function of transistor DC current:

$$P_{Out-max} = \frac{1}{2} \frac{(V_{DD} - V_K)^2}{R_{opt}}$$

(2-3)

$$P_{DC} = V_{DD} \times I_{DC}$$

(2-4)

where  $V_K$  is the transistor knee voltage and  $R_{opt}$  is the PA required optimum impedance, when low output power is required, in order to keep the efficiency high, the  $P_{DC}$  reduces by decreasing the  $V_{DD}$  value.

In order to modulate the supply voltage, multiple techniques have been proposed. In [17], a low drop-out (LDO) has been utilized as the supply modulator. However, due to the fact that the bandwidth of the envelope signal is 5-6 times wider than the bandwidth of the original input signal, the regulator must be quite fast to track the envelope properly. Implementing a high speed regulator makes the supply modulator quite power hungry and reduces the overall efficiency of the transmitter. In addition, as stated in [18] the efficiency of the regulators are not high enough for high PAPR signals and as a result, utilizing the stand alone LDO or a DC-DC converter in advanced modulated RF signal is not a suitable option [19]. In [20] a class-S modulator, which is a switching supply regulator, has been used to modulate the PA supply voltage. Nevertheless, in order to reduce the ripples, high switching frequency must be utilized that increases the switching loss of the design and as a result, it degrades the overall efficiency of the transmitter. In [21-26], by combining the linear and switching supply regulators and therefore a highly efficient supply modulator has been made.

Although the ET technique increases the efficiency of the transmitter, since the envelope and the RF input signal pass through two different paths (regulator and the main PA), and the delay between them is not equal, they might experience some misalignment, delay at the main PA. In [27] it has been shown that if there is any difference/mismatch between these two paths, the amplified output spectrum is not symmetric.

In order to increase the output power in the cellular applications it is common to use compound devices such as GaN, GaAs and HBT. However, the ET modulator is commonly implemented in CMOS substrate. The difference between the materials in these two sections, lead to different processes, voltage and temperature variation that affects the overall performance. In [28] a full CMOS ET PA has been presented for 10MHz, 16-QAM and LTE application. But the supply modulator and the PA are separate chips.

20

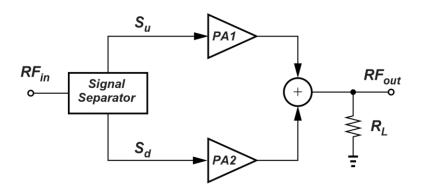

### 2.7 Linear Amplification Using Non-linear Component (LINC)

In this technique that is presented in [13] for the first time and is shown in Fig. 2-6, non-linear circuits such as saturated or switched mode PAs have been utilized to generate the output signal. The input RF signal separates into two constant envelope signals to drive the PAs. The signal separator block basically modulates the amplitude information of the input signal into two phase modulated signals (Su, p). Since the PAs do not need to process a variable envelope signal, they do not need to be linear. As a result, non-linear PAs that are inherently highly efficient can be utilized instead.

Fig. 2-6, Out-phasing amplifier system architecture

Since the PA process only the phase modulated signal, this type of implementation is known as out-phasing (OP) PA. As mentioned in [29], most challenges in the OP amplifier design are the implementation of the output power combiner and low achievable dynamic range (DR). In [30] it has been shown that DR=60dB requires the phase accuracy of about 0.1°, which is quite difficult to achieve. In the next chapter, extensive analysis on this type of amplifier will be provided.

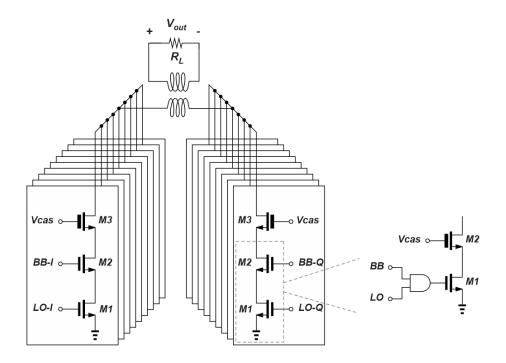

# 2.8 RF DAC-based PAs

This type of PA that is shown in Fig. 2-7 provides the ability of integrating the digital processor as well as the PA on the same chip. As reported in [31-34] the RF DACs

are able to operate at a wide range of frequency from RF ( $\approx$ 1GHz) mm-wave ( $\approx$ 60GHz) and output power (up to 29.1dBm). Since the RF DAC structures are done in digital domain, they are inherently more efficient than the other types of aforementioned PAs. In addition, the digital implementation capability of the RF DACs make them a good candidate to operate on the same Si substrate along with the digital processing units. As a result, it is expected that this type of PA is the best candidate for the next generation of communication systems.

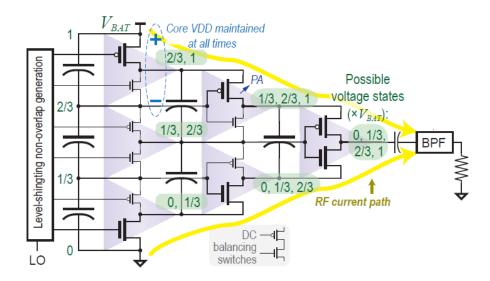

Fig. 2-7, RF-DAC overall circuit diagram

### CHAPTER 3

#### **OUT-PHASING PA**

This chapter analyzes the out-phasing architecture in more detail and discusses the main challenges and solutions. A new method of power combining, which is typically the bottleneck to implementing out-phasing PAs, is presented. The proposed method is capable of reducing the physical area of the overall circuit by about 50%.

3.1 Introduction

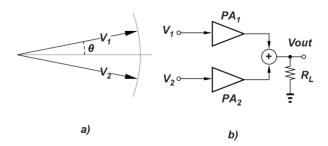

The out-phasing amplification generates two signals with constant amplitude and differential phase (with respect to each other). The relative phase between these two signals is then used to generate the desired variable amplitude RF signal. The equations below shows the relationships between the desired output signal and required relative phase.

$$y(t) = A(t)\cos(\omega t + \varphi)$$

(3-1)

$$V_1 = 1/2 V_0 \cos(\omega t + \varphi + \theta) \tag{3-2}$$

$$V_2 = 1/2 V_0 \cos(\omega t + \varphi - \theta) \tag{3-3}$$

$$y(t) = V_1 + V_2, \theta = \cos^{-1}(A(t)/V_0)$$

(3-4)

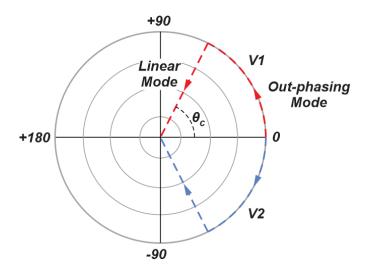

In order to clarify this concept, the out of phased signals are shown as phasors in Fig. 3-1. In two extreme cases when  $V_{1,2}$  are in-phase with each other the output power is at maximum and when  $V_{1,2}$  have 180° phase shift with respect to each other, the output power level is minimum (theoretically zero power).

Fig. 3-1, a) Out-phasing vectors, b)out-phasing system diagram

Since the input signals do not carry any amplitude information, switched mode power amplifiers can be utilized to process the inputs ( $V_{1,2}$ ). Because the output power level of the switched mode PAs is a direct function of the supply voltage ( $V_{DD}$ ), this type of amplifier can be modeled as voltage source instead of a power source (a voltage source in series with an impedance) [35].

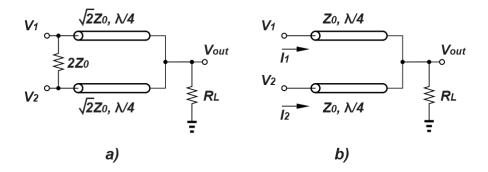

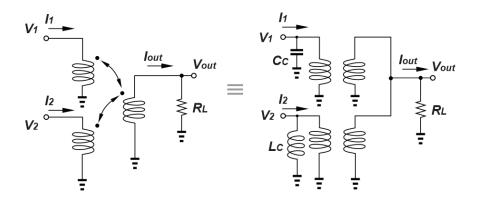

## 3.2 Power Combiner

One of the most important parts of the out-phasing amplifiers is the power combiner. Unlike in-phase power combining, a Wilkinson power combiner as shown in Fig. 3-2a is not an efficient method when the signals are out of phase. Because this type of combiner has a nulling impedance (2Z<sub>0</sub>) to provide 50 $\Omega$  termination at all terminals, when the signals are out of phase this resistance acts as a load to the input sources, hence increasing the power dissipation and reducing the overall PA efficiency [29, 36].Therefore, out-phasing combiners require alternative architectures. The most common type of combiner for the out-phasing transmitters is shown in Fig. 3-2b.

Fig. 3-2, a) Isolated power combiner (Wilkinson), b) non-isolated power combiner This combiner is implemented by removing the nulling impedance in Wilkinson power combiners and modifying the characteristic impedance of the transmission lines (T-lines) [29, 36-38].

One of the challenges associated with this type of combiner is that unlike a Wilkinson power combiner, the input impedances are not fixed and vary as a function of out-phasing angle. The ABCD matrix and the relationships between the input current and voltage at the input ports of the combiner are calculated as:

$$ABCD = \begin{bmatrix} \cos\beta L & jZ_o \sin\beta L \\ j/Z_o \sin\beta L & \cos\beta L \end{bmatrix}$$

(3-5)

$$\begin{bmatrix} v_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} 0 & JZ_0 \\ j/Z_0 & 0 \end{bmatrix} \begin{bmatrix} v_2 \\ I_2 \end{bmatrix}$$

(3-6)

$$\begin{bmatrix} V_o e^{j\theta} \\ I_1 \end{bmatrix} = \begin{bmatrix} 0 & jZ_o \\ j/Z_o & 0 \end{bmatrix} \begin{bmatrix} V_{out} \\ I'_1 \end{bmatrix}$$

$$\begin{bmatrix} V_o e^{-j\theta} \\ I_2 \end{bmatrix} = \begin{bmatrix} 0 & jZ_o \\ j/Z_o & 0 \end{bmatrix} \begin{bmatrix} V_{out} \\ I'_2 \end{bmatrix}$$

$$(3-7)$$

where  $Z_0$  is the T-line characteristic impedance,  $I_{1,2}$  are the currents injecting from the input voltage sources and I'<sub>1,2</sub> are the currents coming out of the T-lines.

$$I'_{1} = V_{o}e^{j\theta}, I'_{2} = V_{o}e^{-j\theta}$$

(3-8)

$$V_{out} = R_L (I'_1 + I'_2) = \frac{2R_L V_o \cos\theta}{jZ_o}$$

(3-9)

$$I_{1,2} = j/Z_o V_{out} = \frac{2R_L V_o cos\theta}{Z_o^2}$$

(3-10)

$$Y_{eff1} = \frac{I_1}{V_1} = \frac{2R_L V_o cos\theta}{Z_o^2 (cos\theta + jsin\theta)}$$

$$Y_{eff2} = \frac{I_2}{V_2} = \frac{2R_L V_o cos\theta}{Z_o^2 (cos\theta - jsin\theta)}$$

$$Y_{eff1} = \frac{2R_L}{Z_o^2} cos^2\theta - j\frac{R_L}{Z_o^2} sin2\theta$$

$$Y_{eff2} = \frac{2R_L}{Z_o^2} cos^2\theta + j\frac{R_L}{Z_o^2} sin2\theta$$

(3-11)

$$P_{out} = \frac{2V_o^2 \cos^2\theta}{Z_o^2/R_L} \tag{3-12}$$

$$Y_{eff1-Comp} = \frac{2R_L}{Z_o^2} \cos^2\theta - j\frac{R_L}{Z_o^2} \sin 2\theta + j\omega C$$

(3-13)

$$Y_{eff2-Comp} = \frac{2R_L}{Z_o^2} \cos^2\theta + j\frac{R_L}{Z_o^2} \sin 2\theta + \frac{1}{j\omega L}$$

(3-14)

As can be seen, the output power has a direct relationship with the out-phasing angle. It is quite clear that the real parts of the effective input admittances are the same and as a result, the real power generated by the PAs are the same. But, PAs also see imaginary components and therefore, some reactive power generates and degrades the efficiency of the overall system. In order to improve the efficiency, the imaginary terms must be removed from the input admittances. A common method of doing this is to put compensation components (capacitor and inductor) in parallel with the input ports. Fig. 3-3a shows the implementation of the out-phasing compensation. Since impedance compensation happens at a specific out-phasing angle, the effective input admittances cross the real axis (on the smith chart) twice. Fig. 3-3b shows the variation of the effective input admittances as a function of the out-phasing angle on the smith chart. Since the required capacitor and inductor admittance values to cancel the imaginary parts are frequency dependent, the compensation is sensitive to the frequency. This figure shows the simulation result of the effective input impedances at the input of the combiner at 2.4GHz. In this simulation the  $L_c=4.9nH$ ,  $C_c=0.9pF$ .

Fig. 3-3, a) Out-phasing non-isolating power combiner, b) effective reflection coefficients at ports V<sub>1,2</sub> Although implementing the out-phasing PA is quite straight forward, using T-line structures at cellular frequencies (2.4-5GHz) requires board level implementation since implementing the T-lines requires a large area (L= $\lambda/4$ ). Therefore, another more integrated method of combining is required to realize small form-factor PAs.

# 3.3 Power Combining Using Transformers

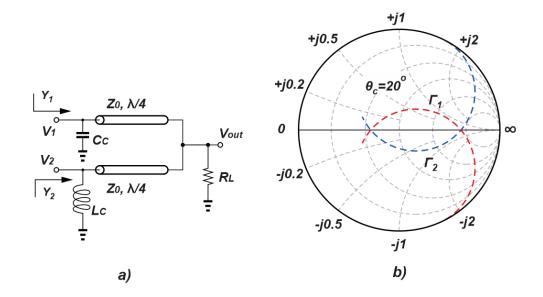

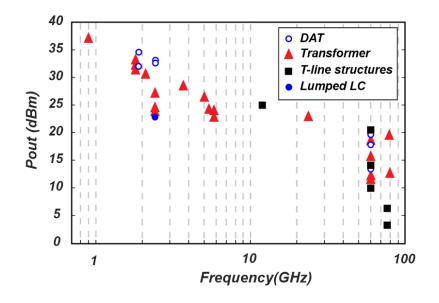

Since the out-phasing technique is based on summing the voltages, transformers can be utilized. Unlike the T-lines, transformer-based combiners relax the physical implementation limitation in cellular frequency. As explained in [39] and shown in Fig. 3-4, transformer-based combiners cover a wide range of frequency from sub GHz up to mm-wave applications. Fig. 3-5 shows two of the most common circuit diagrams of combiner implementation using transformers.

Fig. 3-4, Output power versus frequency for most common power combiners

Fig. 3-5, a) Series architecture of transformer combiner, b) parallel architecture of transformer combiner Considering the 1:1 transformer ratio for simplicity in Fig. 3-5a, the output voltage and effective input impedance with and without the compensation components can be written as:

$$V_{out} = V_1 + V_2 = 2V_o \cos\theta \tag{3-15}$$

$$I_{out} = V_{out} / R_L = \frac{2V_o \cos\theta}{R_L} = I_{1,2}$$

(3-16)

$$Y_{eff1} = I_1 / V_1 = \frac{2}{R_L} \left( \cos^2 \theta - j \frac{1}{2} \sin 2\theta \right)$$

(3-17)

$$Y_{eff2} = I_2 / V_2 = \frac{2}{R_L} \left( \cos^2 \theta + j \frac{1}{2} \sin 2\theta \right)$$

(3-18)

$$Y_{eff1-Comp} = I_1/V_1 = \frac{2}{R_L} \left( \cos^2\theta - j\frac{1}{2}\sin^2\theta \right) + j\omega C$$

(3-19)

$$Y_{eff2-Comp} = I_2/V_2 = \frac{2}{R_L} \left( \cos^2\theta + j\frac{1}{2}\sin^2\theta \right) + \frac{1}{j\omega L}$$

(3-20)

where  $I_{1,2}$  are the input currents coming from the voltage sources and  $I_{out}$  is the load current. As can be seen, the effective input admittances seen by the input sources have imaginary parts and in order to enhance the overall efficiency, the parallel capacitor and inductor must be placed at the input of the primary coils of the transformers.

Due to the inductive nature of the actual transformers, in practical implementation only capacitors are being used to provide compensation. In [40], a transformer-based outphasing transmitter at 5.9GHz has been implemented that consumes only 0.8mm<sup>2</sup> of area. This implementation achieved 22.2dBm of output power and almost 35% of drain efficiency.

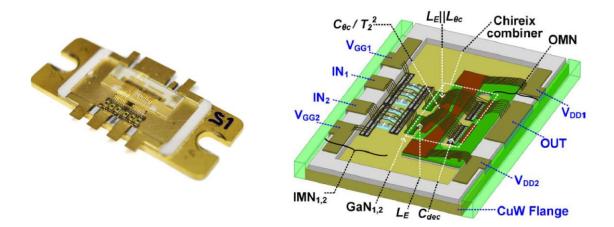

In [41, 42], it has been shown that instead of implementing the actual transformer, bond wires can be utilized to mimic the behavior of the transformer to save the area. This structure is shown in Fig. 3-6. Nevertheless, the coupling factor in this case highly depends on the shape of the bondwires and the positions of them with respect to each other. As a result, this type of implementation is quite sensitive compared to the on-chip integration of the transformers.

Fig. 3-6, Power combiner implementation using the package bondwires

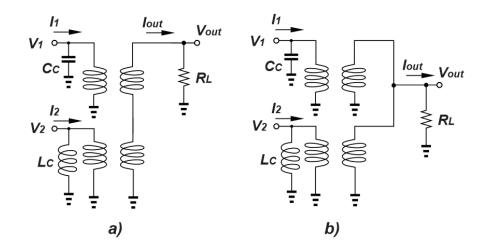

Instead of combing the RF signals in voltage domain, transformers can be arranged such that the signals add in current domain [6, 43]. Fig. 3-7 shows the circuit diagram of this architecture. Unlike voltage combining, adding the signals in current domain can reduce the area significantly since the transformer coils can be placed in parallel with each other by stacking them on top of one another. However, due to the CMOS process limitations such as number of available routing layers and the maximum thickness of each metal layer, creating more than 2 transformers is not practical.

Fig. 3-7, Parallel architecture of transformer combiner

Although combining the powers in current domain is quite efficient in terms of area, this method of integration is applicable only to in-phase combining. As shown in

Fig. 3-7, the transformers' basic equations enforce the output voltage ( $V_{out}$ ) to be in-phase with the signals at the primary coils (A requirement that does not satisfy the out-phasing nature since at the inputs the signals have different phases). Therefore, the parallel combining is not a practical solution in out-phasing systems.

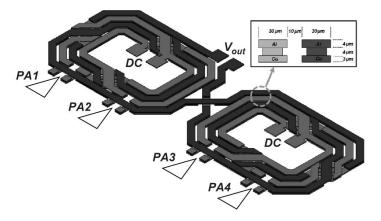

#### 3.4 Proposed Power Combining Technique

In order to take advantage of the current and voltage combining properties, the transformer implementation that is proposed in [43] has been used. Utilizing the series-parallel configuration conventionally has been proposed only for in-phase power combining and it shows some benefits over series and parallel combining such as: low form factor (almost 50%), less sensitivity in the efficiency (compare to pure series or parallel implementation) and high mutual coupling between the adjacent primary coils that enhances the efficiency. In order to visualize the structure of this combiner, Fig. 3-8 illustrates the layout view of the transformers.

Fig. 3-8, Parallel-series combiner layout architecture

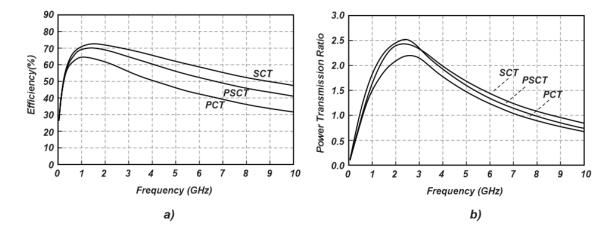

In this implementation most of the routing is done on the top most metal layer (Al) to reduce the routing resistance. Fig. 3-9 compares the efficiencies of the series, parallel and the proposed PSCT. As illustrated, the efficiency of the PSCT is between the other types of combiner. Another important parameter that is commonly being used in

transformer comparison is the power transmission ratio (PTR). This parameter indicates how efficiently the transformer is incorporated with parallel PA cores but does not reflect the efficiency of the transformer [43].

$$PTR = M\eta(1 - |\Gamma|) \tag{3-21}$$

where M is the number of transformers in parallel with each other,  $\eta$  is the efficiency of each transformer and  $\Gamma$  is the reflection coefficient at the input terminal.

Fig. 3-9, a) Efficiency comparison between SCT, PCT and PSCT, b) power transmission ratio comparison between SCT, PCT and PSCT

Due to the advantages of the PSCT over the other conventional transformer combiners, this research proposes to use this combiner in the out-phasing transmitter. This configuration is illustrated in Fig. 3-10a. Since most of the CMOS processes provide 2 thick metal layers, only two transformers have been placed at each input port (M=2). Because the input signals at each port are in phase with each other, parallel combining is practical. Finally, in order to sum the out-phased signals, series combining has been utilized at the secondaries of the transformers. The simulation result, which is done at 5GHz with L<sub>c</sub>=5nH and C<sub>c</sub>=200fF with R<sub>L</sub>=50 $\Omega$  and shown in Fig. 3-10b, reveals that the input effective reflection coefficients seen from each input port behave similarly to the conventional out-phasing structure and cross the real axis on the smith chart twice. Note that for this simulation the compensation angle is set to  $\theta_c=20^\circ$ , which is a common value in most of the communication applications.

Fig. 3-10, a) circuit diagram of the PSCT for out-phasing architecture, b) the effective reflection coefficient at the input ports of the combiner (compensation at 20°)

Since two transformers have been placed at the input ports instead of one, 3dB more power can be achieved with this arrangement. In addition, compared to the putting of 4 transformers in series with each other, the proposed configuration consumes 50% less area than the conventional implementation methods.

## 3.5 Out-phasing Transmitter Challenges

One of the main issues associated with the out-phasing transmitters reveals when a low output power level is desired at the output. Since it is quite difficult to generate two out-phased vectors to cancel out each other completely, the dynamic range (DR) of the system is limited by the phase accuracy of the transmitter. In [30] it has been shown that in order to meet 60dB of DR, the phase error should be controlled by 0.1° that requires 10-bit DAC resolution, which of course has a quite challenging implementation.

In order to increase the DR of the system and generate low output power levels easily, [29, 37, 38] proposed combining the linear amplification and out-phasing techniques, which is called mixed-mode out-phasing. When the output power level is close to the maximum, out-phasing technique is being used to enhance the efficiency and when low output power level is of interest, the linear amplification is used to reduce the output power. As a result, instead of using pure switched mode PAs such as class E and  $E^{-1}$ , saturated linear PAs must be utilized. Fig. 3-11 graphically shows how this technique operates.

Fig. 3-11, Mixed mode (out-phasing and linear) vector description

The other critical challenge that the out-phasing amplifier has is the amount of power generated by the PAs at low output power levels. Since the power generated by the switched mode PAs are fixed, if low output power level is required, the energy generated by the PAs should dissipate somehow (one PA acts as a load of the other PA), which is completely in oppisition of the efficiency enhancement idea.

## 3.6 State of the Art Analysis

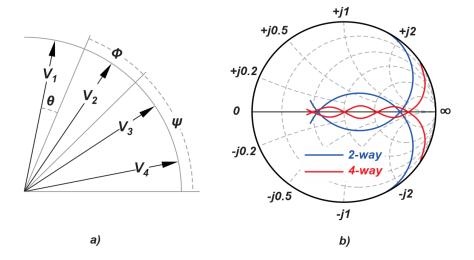

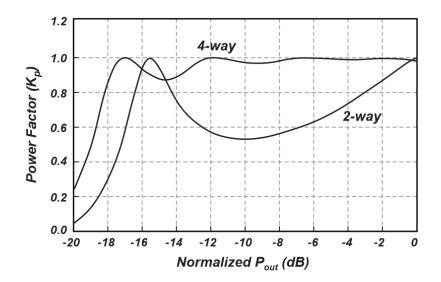

Although combining two out-phased signals improves the overall efficiency of the power amplifier, in [44], a new power combining technique in the out-phasing TX has been proposed, which is called 4-way out-phasing, and is based on generating 4 vectors instead of 2 vectors. Fig. 3-12a conceptually illustrates the concept of 4-way out-phasing. As shown in Fig. 3-12b it is quite clear that the variation of the effective input impedances of the 4-way out-phasing is less than the conventional 2-way out-phasing on the smith chart. The 4-way out-phasing technique, by keeping the effective reflection coefficients close to the horizontal axis, reduces the total reactive power generation. Therefore, the overall efficiency of the out-phasing PA increases. In order to compare the performance of these two types of out-phasing PAs the power factor (PF) has been used that is defined as:

$$K_p = \frac{Re(Y_{eff})}{|Y_{eff}|}$$

(3-22)

Fig. 3-12, a) 4-way outphasing vector diagram, b) comparison between the conventional 2-way and 4-way effective reflection coefficients

Fig. 3-13, Comparison between the power factors (K<sub>p</sub>) of 2-way and 4-way out-phasing As shown in Fig. 3-13, the PF of the 2-way and 4-way out-phasing touches the K<sub>p</sub>=1 twice and 4 times respectively. Also, it is quite clear that the 4-way out-phasing, compared to the conventional 2-way, reduces the power factor variation significantly. In [45-48] multiple methods of implementation of 4-way out-phasing such as lumped component, T-line with lumped component and T-line utilizing radial stubs have been proposed. Although implementing the 4-way out-phasing PA improves the efficiency of the transmitter, it has two main challenges: 1) generating the phase between the vectors and 2) shrinking the size of the combiner.

The phase difference between the out-phased vectors must be set accurately. Otherwise, the desired performance deviates from the desired values. In [44] the reverse implementation of the output combiner has been used as the input signal separator. Nevertheless, it increases the size of the overall transmitter board and makes it quite area inefficient. In order to reduce the size of the signal separator, [49, 50] proposed a technique to generate the 4 out-phased vectors with accurate phase difference. This technique is based on implementing the non-linear network whose impedance is a function of the input voltage value.

Implementing the power combiner via the methods presented in [45-48] makes the design quite bulky and completely area inefficient, especially for CMOS fabrications in telecommunication frequency. Reference [39] investigated the transformer-based implementation of the 4-way out-phasing. By considering the out-phasing vectors as:

$$V_1 = V_0 e^{+j\varphi} e^{+j\theta} \tag{3-23}$$

$$V_2 = V_0 e^{+j\varphi} e^{-j\theta} \tag{3-24}$$

$$V_3 = V_0 e^{-j\varphi} e^{+j\theta} \tag{3-25}$$

$$V_4 = V_0 e^{-j\varphi} e^{-j\theta} \tag{3-26}$$

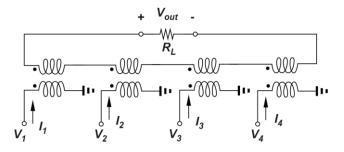

where V<sub>0</sub> is the fixed output vector, it can be seen that the output voltage is the summation of all of these vectors ( $V_{out} = \sum_{i=1}^{4} V_i$ ). This summation can be simply implemented via series combination of 4 transformers as shown in Fig. 3-14.

Fig. 3-14, Series transformer combiner implementation for 4-way out-phasing

Although the series combination of the transformers can make the desired output vector, the effective input impedances/admittances must satisfy the PA outputs. As an example, the input admittances of the first and second ports are calculated:

$$Y_{1} = \begin{cases} Re = \frac{4}{R_{L}} \left( \cos^{2}\varphi\cos^{2}\theta - \frac{1}{4}\sin^{2}\varphi\sin^{2}\theta \right) \\ Im = \frac{-4}{R_{L}} \left( \frac{1}{2}\cos^{2}\varphi\sin^{2}\theta + \frac{1}{2}\sin^{2}\varphi\cos^{2}\theta \right) \end{cases}$$

(3-27)

$$Y_{2} = \begin{cases} Re = \frac{4}{R_{L}} \left( \cos^{2}\varphi\cos^{2}\theta + \frac{1}{4}\sin^{2}\varphi\sin^{2}\theta \right) \\ Im = \frac{-4}{R_{L}} \left( \frac{1}{2}\sin^{2}\varphi\cos^{2}\theta - \frac{1}{2}\cos^{2}\varphi\sin^{2}\theta \right) \end{cases}$$

(3-28)

where  $R_L$  is the output load of the combiner. As shown in this equation and mentioned in [39], in order to generate an equal amount of power at each PA port, the real parts of the admittances should be equal. In addition, the stability requirement forces the real parts to be positive at each PA output terminal for all output power levels. These criterion limit the out-phasing angle selection and as mentioned in [39] the summation of the outphasing angles ( $\varphi$ + $\theta$ ) must be less than  $\pi/2$  in order to keep the resistive input admittances positive. Therefore, in order to design the output combiner for the outphasing transmitter not only the output vector must be set correctly, the combiner structure must be compatible with the PA requirements.

# 3.7 Conclusion

In this chapter, one of the PA efficiency enhancement techniques has been introduced and analyzed. It has been shown that the transformer based power combiner is one of the most popular ways of combining, especially in CMOS processes. A new implementation technique has been introduced to increase the output power level by the factor of 2 and reduce the area by the same amount. The state of the art implementation is explained and showed that the conventional transformer power combiner is not a promising implementation for 4-way power combiner.

## **CHAPTER 4**

#### AVERAGE POWER TRACKING

## 4.1 Introduction

The importance of amplifier design in CMOS process is well discussed in [51-53]. In this chapter, a new method of efficiency enhancement technique that uses average power tracking (APT) is proposed. In addition, the proposed technique has been implemented via a custom made metal-semiconductor field effect transistor (MESFET) to generate watt-level output power in CMOS processes. Furthermore, unlike the conventional envelope tracking technique that utilizes the CMOC process for implementing the supply regulator and GaN, GaAs or HBT devices as the PA, both the power amplifier and supply modulator are integrated on the same substrate.

4.2 Average Power Tracking vs. Envelope Tracking

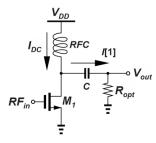

As we know, the power dissipation of the PA is a function of average current pulls from the supply multiplied by the V<sub>DD</sub> and the RF power generated by the PA is a function of the fundamental current at the drain of the transistor. As an example, a linear PA that is biased in class B and is shown in Fig. 4-1 has been analyzed. Because the transistor gate in this class of operation is biased at the threshold voltage, any voltage that exceeds the threshold voltage at the gate of the transistor turns it on and generates current at the drain. By considering the sample wave forms shown in Fig. 4-2, the average and fundamental currents can be calculated as:

Fig. 4-1, A sample PA circuit diagram

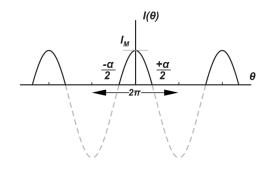

Fig. 4-2, A sample semi-sinusoidal wave form

$$I(\theta) = I_P \cos \theta + I_{DC}, I(0) = I_m, \left(\frac{\alpha}{2}\right) = 0$$

(4-1)

$$I(\theta) = \frac{I_m}{1 - \cos\frac{\alpha}{2}} (\cos\theta - \cos\frac{\alpha}{2})$$

(4-2)

$$I_{DC} = \frac{I_m}{2\pi (1 - \cos \alpha/2)} (2\sin \alpha/2 - \alpha \cos \alpha/2)$$

(4-3)

$$I[1] = \frac{I_m}{\pi (1 - \cos \alpha/2)} (\alpha/2 - \frac{1}{2} \sin \alpha)$$

(4-4)

$$@ \alpha = \pi, \qquad I_{DC} = \frac{I_m}{\pi}, \quad I[1] = \frac{I_m}{2}$$

(4-5)

$$P_{DC} = V_{DD} \times I_{DC} = \frac{V_{DD} \times I_m}{\pi}$$

(4-6)

$$P[1] = \frac{1}{2} R_{opt} I^2[1] \tag{4-7}$$

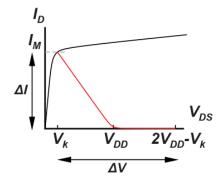

where  $I_P$  is the peak value of the sine wave,  $I_{DC}$  is the DC level of the sine wave current,  $I_m$  is the maximum of the output current,  $\theta$  is the angular frequency and  $R_{opt}$  is the optimum impedance the PA requires to generate the maximum power. This impedance can be easily calculated by dividing the maximum voltage variation on the drain of the transistor by the maximum drain current variation. This analysis is shown graphically in Fig. 4-3b.

Fig. 4-3, Variation of  $I_D$  and  $V_{DS}$  of the transistor

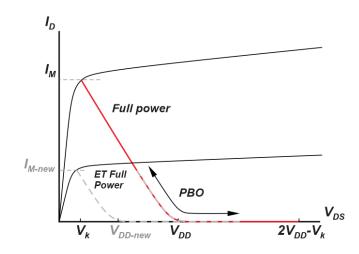

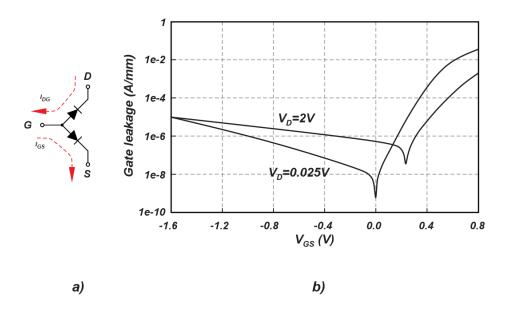

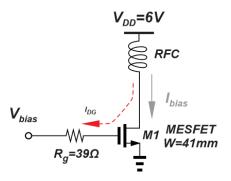

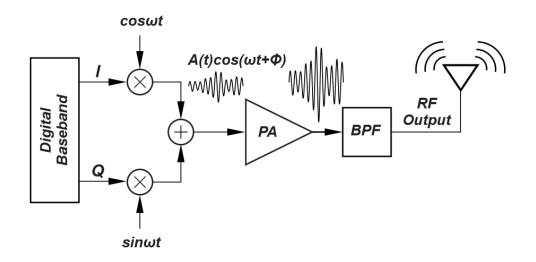

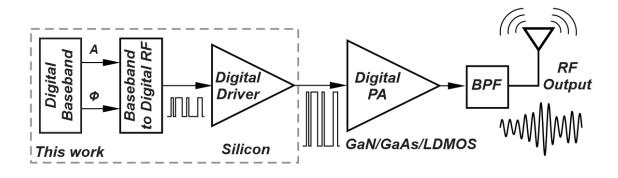

By considering the I-V characteristic shown in Fig. 4-3, the output power and efficiency of the PA can be calculated as: