Optimized Stress Testing for Flexible Hybrid Electronics Designs

by

Hang Gao

A Thesis Presented in Partial Fulfillment of the Requirements for the Degree Master of Science

Approved November 2018 by the Graduate Supervisory Committee:

Sule Ozev, Chair Umit Y Ogras Jennifer Blain Christen

ARIZONA STATE UNIVERSITY

December 2018

#### ABSTRACT

Flexible hybrid electronics (FHE) is emerging as a promising solution to combine the benefits of printed electronics and silicon technology. FHE has many high-impact potential areas, such as wearable applications, health monitoring, and soft robotics, due to its physical advantages, which include light weight, low cost and the ability conform to different shapes. However, physical deformations that can occur in the field lead to significant testing and validation challenges. For example, designers have to ensure that FHE devices continue to meet specs even when the components experience stress due to bending. Hence, physical deformation, which is hard to emulate, has to be part of the test procedures developed for FHE devices. This paper is the first to analyze stress experience at different parts of FHE devices under different bending conditions. Then develop a novel methodology to maximize the test coverage with minimum number of text vectors with the help of a mixed integer linear programming formulation.

## ACKNOWLEDGMENTS

First, I would like to express my deep gratitude and respect for my professor, Dr. Sule Ozev. I have been extremely lucky to have a professor who cared so much about my work, and who gave me invaluable guidance to my thesis. It is a great honour to work under her supervision.

Second, I would like to thank Dr. Umit Y Ogras for accessing me to use the machine and give me invaluable advice. In addition, I would like to thank my committee member, Dr. Jennifer Blain Christen for attending my defense and gave her invaluable feedback.

Finally, I would like to thank my parents who support me spiritually throughout my life and my friends who experienced all of the ups and downs of my research.

|      |      | F                                    | Page |

|------|------|--------------------------------------|------|

| LIST | OF T | ABLES                                | iv   |

| LIST | OF F | IGURES                               | v    |

| CHA  | PTER |                                      |      |

| 1    | INT  | RODUCTION                            | 1    |

|      | 1.1  | History of Flexible Electronics      | 1    |

|      | 1.2  | Testing of Flexible Electronics      | 2    |

|      | 1.3  | Purpose of Thesis                    | 3    |

| 2    | REL  | ATED WORK                            | 5    |

| 3    | MET  | THODOLOGY                            | 7    |

|      | 3.1  | Stress in Cantilever                 | 10   |

|      | 3.2  | Radius of Curvature and Displacement | 11   |

|      | 3.3  | Optimization Algorithm               | 13   |

| 4    | RES  | ULTS AND DISCUSSION                  | 15   |

|      | 4.1  | COMSOL Multiphysics                  | 15   |

|      | 4.2  | MATLAB                               | 20   |

| 5    | CON  | ICLUSIONS                            | 22   |

| REFI | EREN | CES                                  | 23   |

# TABLE OF CONTENTS

# LIST OF TABLES

| ble                                               | Page |

|---------------------------------------------------|------|

| 4.1 All Blocks Parameters( Unit: mm )             | 16   |

| 4.2 Required Displacement( Unit: mm )             | 19   |

| 4.3 Number of Selected Mechanical Stress Patterns | 21   |

# LIST OF FIGURES

| Figure |                                                                   | Page |

|--------|-------------------------------------------------------------------|------|

| 3.1    | Illustrative Example Of An FHE Board                              | . 8  |

| 3.2    | Flow Of The Proposed Mechanical Stress Optimization Methodology . | . 9  |

| 3.3    | Bending Stress                                                    | . 10 |

| 3.4    | Rectangle Model                                                   | . 11 |

| 3.5    | Bending FHE Based On A Given ROC                                  | . 12 |

| 3.6    | Determining Required Displacement                                 | . 13 |

| 4.1    | Prototype FHE Layout                                              | . 16 |

| 4.2    | Pins And Wires On Substrate                                       | . 17 |

| 4.3    | Stress On Entire Board Layout For Diagonal Beam                   | . 17 |

| 4.4    | Stress On Entire Board Layout For Parallel Beam                   | . 18 |

| 4.5    | All Beams On Entire Board Layout                                  | . 18 |

| 4.6    | Beams Are Selected                                                | . 21 |

### Chapter 1

## INTRODUCTION

Flexible hybrid electronics (FHE) is emerging as a promising solution to combine the benefits of printed electronics and silicon technology. FHE has many high-impact potential areas, such as wearable applications, health monitoring, and soft robotics, due to its physical advantages, which include light weight and the ability conform to different shapes by bending and stretching.

### 1.1 History of Flexible Electronics

In 1960s, the first flexible electronics was made by a silicon wafer on plastic substrates. Then in 1980s, roll-to-roll fabrication of a Si:H solar cells on flexible steel and organic polymer substrate was introduced. Next in 1990s, a Si:H thin film transitors were made on flexible stainless steel foil. Recent years Samsung announced a 7" flexible liquid crystal panel [1]. However, the performance of flexible devices is still not up to par with performance of integrated circuit components, thus limiting their use for highperformance devices.

To ensure specified functionality under various bending and twisting conditions, FHE devices impose new design, test, and design automation challenges [2][3]. For example, bending can reduce the maximum power generated by a photovoltaic cell by more than 50% [4] and increase the mechanical stress [5]. Similarly, it can damage the connection between the pins of the rigid ICs and flexible substrate. To account for this effect, the specifications of the design need to be augmented into a new dimension that defines the flexibility of the substrate. This specification needs to include worst case bending and twisting conditions. In order to take this requirement into account during the design phase, a new metric, called *flexibility* has been defined and constraint-based optimization algorithms have been developed for designing FHE boards [6].

## 1.2 Testing of Flexible Electronics

FHE devices pose additional burdens on the board test process as well. Traditionally, rigid boards are tested through the application of pre-defined test patterns with the help of a tester along with on-board and on-chip structures, such as the JTAG interface [7][8]. During testing, the boards are kept on a flat surface without any mechanical stress. Unfortunately, this form of testing is not adequate for FHE devices for two reasons. First, the characteristics of traces and solder joints on FHE substrates change when the devices are bent or twisted [9][10]. Electromechanical simulations can help determine the worst case bending/twisting conditions and predict the stress induced by the mechanical stimulus. However, it is not possible to fully correlate the electrical parameters measured in neutral and bent/twisted states due to process variations. Second, mechanical stress can cause fractures after manufacture, which will make the devices fail only after bending and twisting [11][12]. Due to these two issues, FHE devices must be tested under bending conditions, which induce different levels of stress on different locations of the FHE boards. Therefore, a thorough test procedure needs to apply many types of mechanical stress to FHE devices to cover worst case scenarios [10][11][12].

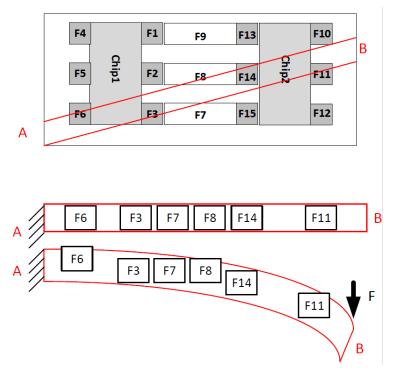

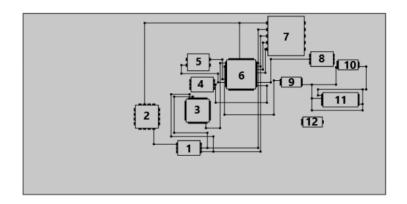

The application of mechanical stress on the FHE devices can be accomplished via a specialized test set-up [13] where one side of the FHE board is fixed and a force is applied to the other side. From this perspective, the fixed location of the board and the location where the force is applied can take on many values. For instance, one edge of the board can be fixed at multiple locations, spread out by centimeters, where the force can be applied from any other edge, and location. Figure 3.1 shows this concept for a simplified board layout with 12 solder joints, and 3 traces, each of which can be a fault. Point A is chosen as the fixed location, and Point B is chosen as the moving location. Points AB generate a mechanical stress pattern with the faults distributed along the cantilever formed by these two points. When the force, F, is applied, the faults will be stressed to varying degrees depending on their location on the cantilever. The choice of the fixed and moving positions (AB) results in  $O(n^2)$  potential stress patterns, where n is the number of distinct positions along the edges of the board. Application of multiple mechanical stress patterns necessitates re-positioning the board, with a large test time overhead (hundreds of milliseconds to seconds), thereby increasing test cost and reducing the throughput. Thus, methodologies are needed to reduce this mechanical test overhead for FHE boards as much as possible to keep the overall product cost at a manageable level.

### 1.3 Purpose of Thesis

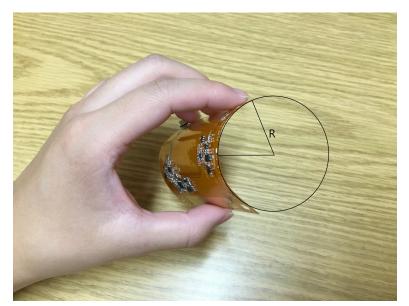

This paper addresses the problem of optimizing the mechanical stress patterns for FHE boards such that all potential fault locations are stressed adequately during testing to ensure proper operation in the field. Our goal is the reduce the number of bending and twisting conditions (defined by one fixed and one moving location) to eliminate the unnecessary combinations. We observe that each trace or solder joint will reside on the path of multiple mechanical stress patterns. Hence, there is considerable redundancy in mechanical stress application when all  $n^2$  combinations are taken into account. We define the minimum stress conditions based on the specification of bending and twisting curvature as dictated by the application. We determine the maximum stress in each potential fault location based on this curvature and optimize mechanical stress patterns to cover all fault locations with this level of stress. We conduct our experiments on a prototype FHE [2] designed as a device wearable around the wrist. We use the COMSOL multiphysics environment to evaluate the stress conditions for each fault location and integer linear programming (ILP) to optimize the stress patterns.

### Chapter 2

## RELATED WORK

Flexible electronics refer to integrated circuits implemented on bendable, rollable, conformable, or elastic substrates [14][15], while the term *flexible hybrid electronics* implies integration with rigid ICs [16][17]. This integration aims at combining the physical advantages of flexible electronics with the superior performance and power consumption of traditional silicon technology [2].

Flexible devices introduce new challenges to design automation and test due to the need to apply mechanical stress during testing [9]. Mechanical stress is needed to ensure proper operation in the field and can be in the form of bending and twisting [11]. In several recent studies, flexible devices are tested under three types of mechanical stress, convex and concave radius of curvature, and torsional stress [11][18]. It is shown that the parameters of a flexible OPAMP change significantly under various stress conditions, necessitating multiple stress test patterns.

In [19], a bending characteristic inspection system is designed for electrical characterization under mechanical stress. This system can bend or twist the FHE in multiple ways. An apparatus that can bend the FHE device along its length or width is presented in [20][10]. The board is placed between two parallel plates, where one plate is moving to enable the bending operation. The movable plate is moved with a speed of 50 mm/s to enable bending. Electrical characteristics of the traces on the board show significant shift under mechanical stress. In [12], a test mechanism is generated to duplicate an application-specific operation condition, i.e. bending of the arm. The part is placed on this apparatus and electrical test are conducted before, during, and after bending. The experiments show significant shifts in trace and solder characteristics during bending. Majority of these shifts recover in the flat position while a subset of traces and solder joints experience irreversible damage. In [21], a 4- point bending insert mounted on a microscope tensile stage, this mechanism is developed to bend and twist the board in multiple axes. Again, the authors report change in electrical characteristics of the traces and solder joints.

Prior and ongoing work in the testing of FHE devices clearly show the need for mechanical stress testing. However, application of all possible stress patterns would be costly in terms of test time and would limit throughput. The goal of this paper is to determine an optimum set of critical mechanical stress patterns to exercise the board as specified.

### Chapter 3

## METHODOLOGY

FHE devices need to be mechanically stressed during test process in order to ensure their correct operation in the field. This stress that results from bending or twisting can be modeled in general by fixing a point along one of the edges of the FHE board, and applying a force at another location, creating a curvature pattern along the beam formed by the two ends. We use COMSOL, a multi-physics simulator, to evaluate the stress along the beam at various locations. During testing, we stress the solder joints as well as traces to make sure their electrical characteristics are up to specifications and to detect any latent fractures. Thus, each solder joint or trace is a potential fault, either parametric or catastrophic, that needs to be tested, as illustrated in Figure 3.1. The faults are stressed to different levels depending on their location along each beam.

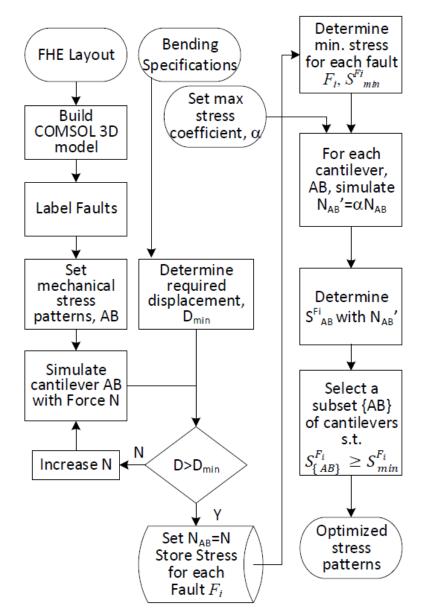

The flow of the proposed optimization approach is outlined in Figure 3.2. We start with the FHE layout as well as the bending/twisting specification, which is expressed as a radius of curvature (ROC) [22]. We also set a stress multiplier,  $\alpha$ , which is the allowed *overstress* amount. The minimum value of  $\alpha$  is 1, and the maximum value determined is experimentally. We build the FHE layout in COMSOL multiphysics simulator and label potential fault locations. We simulate various bending/twisting conditions (by bending the device between two points, AB) to determine a critical spacing parameter, k, where the stress is almost identical through vertical dimension with respect to the line formed by AB. Next, we choose exhaustive mechanical stress patterns through dividing each edge by this increment, k, forming potential end points for mechanical stress. Thus, if the FHE dimensions are  $W \times L$ , there are

Figure 3.1: Illustrative Example Of An FHE Board

2(W + L)/k potential fixed (A) and moving (B) positions for the entire FHE board. Each combination AB forms a cantilever for mechanical stress application. Then, we determine the displacement amount, D, that provides the specified ROC for each cantilever AB. Each cantilever AB is simulated with progressively increasing force to meet this displacement requirement. Once the necessary force is found, it is stored along with the stress it causes at each fault location.

Next, we analyze the stresses at fault locations. For each fault,  $F_i$ , we determine the minimum required stress,  $S_{min}^{F_i}$  as the maximum stress that fault experiences under any of the cantilevers. We form a new matrix where the force is increased by its stress multiplier,  $\alpha$  and the new stress amounts are determined. Our optimization goal after this step is to determine a minimum set of chosen stress patterns,  $\{AB\}$ , such that each fault undergoes the required minimum stress.

Figure 3.2: Flow Of The Proposed Mechanical Stress Optimization Methodology

Figure 3.3: Bending Stress

3.1 Stress in Cantilever

Normal stress is a stress that when a member is loaded by an axial force, which is typically expressed in terms of " $N/m^{2}$ " [23], equation as shown in:

$$\sigma = \frac{F}{A} \tag{3.1}$$

where F is the applied force and A is the cross-sectional area.

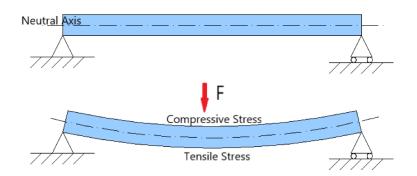

Bending stress is a more specific type of normal stress. Adding a load on a beam, top fibers undergo a compressive stress, the bottom fibers undergo a tensile stress. On the neutral axis, the stress is zero, as shown in Figure 3.3 [23]. We can express the stress along a cantilever as:

$$\sigma_b = \frac{My}{I_c} \tag{3.2}$$

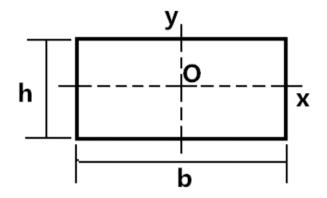

where M is the bending beam moment,  $I_c$  is moment of inertia of the beams cross section, and y is vertical distance away from the neutral axis. For a more realistic rectangle model, as shown in Figure 3.4, the moment of inertia in two dimensions, x-axis, and y-axis, can be expressed as in Equation 3.3:

$$I_{cx} = \frac{bh^3}{12} \quad I_{cy} = \frac{hb^3}{12} \tag{3.3}$$

Figure 3.4: Rectangle Model

Equation 3.3 can be used to pre-select a subset of cantilevers where stress at potential fault locations are maximized. Since relying on first-level approximations is not adequate, we also use the COMSOL multiphysics simulator to determine the actual stress exerted by a given stress pattern AB.

#### 3.2 Radius of Curvature and Displacement

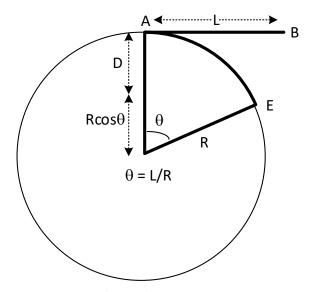

Each application has its own flexibility specifications. For instance, a device designed to be worn on the wrist has different bending requirements than a device designed to be worn on the arm. Similarly for a wrist-wearable device, the bending requirements depends on whether it is intended for adults, children, or infants. Based on the application needs, one can determine the worst case bending scenario. Along the same example, a wearable device for infants (e.g. used in hospitals for tracing) has a much more stringent bending requirement, where a radius of curvature can be determined based on the average size of an infant. The ROC therefore is a specification dictated by the application. Based on the specified ROC, we can determine the simulation parameters. This process is illustrated in Figure 3.5. The flexible device is bent to fit an average adult wrist with a given radius, R.

Figure 3.5: Bending FHE Based On A Given ROC

In our simulation platform, we need to fix one end of the cantilever and apply force on the other end, causing a displacement. This displacement amount needs to match the given ROC requirements. This is illustrated in Figure 3.6, where the points AB represent the two ends of the cantilever under no stress conditions and points AE represent the same two ends under the stress conditions. D represents the displacement of cantilever's moving end, and R represents the radius of curvature. The slice of the circle with end points AE have the same length, L, as the cantilever, which results in an central angle,  $\theta$ . Thus, for a given cantilever with length, L, and the radius of curvature specification, R, we can determine the displacement, D, using Equation 3.4. The required displacement amount varies with the length of each cantilever.

$$D = R(1 - \cos\frac{L}{R}) \tag{3.4}$$

Figure 3.6: Determining Required Displacement

## 3.3 Optimization Algorithm

After simulating each cantilever in COMSOL with the required displacement amount, we determine the stress experienced by each fault. For a given fault, there may be multiple cantilevers that stress it to various degrees. Since we are trying to meet a maximum ROC requirement, we need to ensure that each fault undergoes the maximum stress amount taken over all cantilevers. That will be our minimum stress requirement.

While we can move forward with our optimization with the minimum stress requirement, this may result in the selection of all cantilevers. Thus, we provide a margin to allow faults to be covered with multiple cantilevers. We define a stress multiplier factor,  $\alpha$ , to stress faults beyond their required minimum. The parameter  $\alpha$ , which is determined experimentally from initial characterization samples, can be any number greater than 1. By increasing the force applied by a factor of  $\alpha$ , we ensure that fewer cantilevers are selected for stress. We use Integer Linear Programming (ILP) formulation for the optimal selection of cantilevers. In ILP, we first define a coverage matrix denoted by A. In our formulation, A is an  $N \times M$  matrix, where N is the number of faults, and M is the number of simulated cantilevers. If cantilever j stresses a given fault  $F_i$  to the minimum required amount  $S_{min}^{F_i}$ , it is said to cover that fault. Hence, the corresponding entry in A is set to 1, while all the other entries of A in that row remain as 0. We also define three additional matrices as follows. b is  $N \times 1$  matrix and c is an  $M \times 1$  matrix with all entries equal to 1. Finally, the entries of the  $M \times 1$  matrix x are set to either 0 or 1 by the optimization process to minimize  $c^T x$  subject to the following constraints:

min  $c^{\mathrm{T}}\mathbf{x}$ , subject  $\begin{cases} A\mathbf{x} \ge \mathbf{b} \\ x_i \in 0,1 \end{cases}$

### Chapter 4

## **RESULTS AND DISCUSSION**

### 4.1 COMSOL Multiphysics

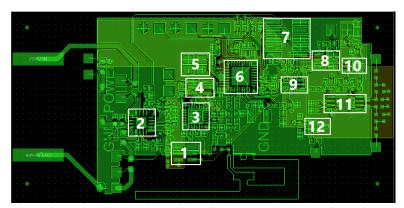

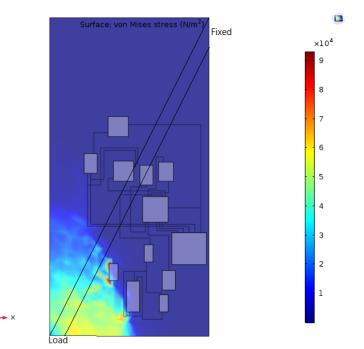

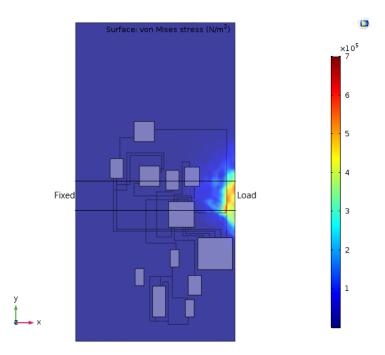

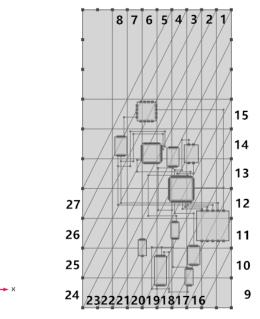

We illustrate the simulation setup and the optimization process through an FHE prototype built at ASU [2]. The dimension of the board is  $3\text{cm}\times6\text{cm}$ . As shown in Figure 4.1, the prototype contains 12 rigid chips and various interconnects between them. Table 4.1 shows the location and parameters of the 12 chips on the prototype. We construct a 3D model of the layout in COMSOL (as illustrated in two dimensions in Figure 4.2) and simulate this layout under multiple bending/twisting combinations. This process is illustrated in Figure 4.3 and Figure 4.4 for two mechanical stress patterns. We observe that stress occurs mostly along the cantilever formed by the endpoints of the stress pattern. We also observe that the layout can be divided into grids where the stress is nearly identical. Based on this observation, we determine a minimum spacing to form the cantilevers. We set this spacing to where stress along the *width* of the cantilever is nearly identical (less than 1% difference in stress). This enables us to determine the potential mechanical stress patterns (AB) to exhaustively explore the entire layout. Through simulations, we find the critical spacing to be 1.5cm.

Before simulating each cantilever, we also observe that some of the stress patterns do not exert sufficient stress on any of the fault locations. We use Equation 3.2 and Equation 3.3 to eliminate cantilevers that will not exert sufficient stress on any of the fault locations. Next, we construct the 3D model of each viable cantilever, which includes solder joints and traces along the cantilever, to simulate under varying

| Block     | Width | Depth | Height | Х     | Y    | Ζ   |

|-----------|-------|-------|--------|-------|------|-----|

| Substrate | 30    | 60    | 0.3    | 0     | 0    | 0   |

| 1         | 2.45  | 3.7   | 0.6    | 6.5   | 30.7 | 0.3 |

| 2         | 3.8   | 3.8   | 0.6    | 11    | 37.6 | 0.3 |

| 3         | 3.8   | 3.8   | 0.6    | 12    | 29.2 | 0.3 |

| 4         | 2.45  | 3.7   | 0.6    | 17    | 28.5 | 0.3 |

| 5         | 2.8   | 3.6   | 0.6    | 20.5  | 29.2 | 0.3 |

| 6         | 4.8   | 4.8   | 0.6    | 17.5  | 21.5 | 0.3 |

| 7         | 6.5   | 6     | 0.6    | 23    | 13.5 | 0.3 |

| 8         | 2.45  | 3.7   | 0.6    | 21.2  | 8.7  | 0.3 |

| 9         | 1.65  | 3.25  | 0.6    | 17.8  | 14   | 0.3 |

| 10        | 1.65  | 3.25  | 0.6    | 20.65 | 4.6  | 0.3 |

| 11        | 2.4   | 5.8   | 0.6    | 14.5  | 4.6  | 0.3 |

| 12        | 1.65  | 3.2   | 0.6    | 11.2  | 10.5 | 0.3 |

Table 4.1: All Blocks Parameters( Unit: mm )

Figure 4.1: Prototype FHE Layout

Figure 4.2: Pins And Wires On Substrate

y

Figure 4.3: Stress On Entire Board Layout For Diagonal Beam

Figure 4.4: Stress On Entire Board Layout For Parallel Beam

Figure 4.5: All Beams On Entire Board Layout

| Cantilevers | Diaplacement          |

|-------------|-----------------------|

| Cantilevers | Diaplacement          |

| Parallel    | $9.14 \times 10^{-4}$ |

| Vertical    | $3.66 \times 10^{-3}$ |

| Diagonal 1  | $2.86 \times 10^{-4}$ |

| Diagonal 2  | $6.00 \times 10^{-4}$ |

| Diagonal 3  | $9.25 \times 10^{-4}$ |

| Diagonal 4  | $1.38 \times 10^{-3}$ |

| Diagonal 5  | $1.93 \times 10^{-3}$ |

| Diagonal 6  | $2.57 \times 10^{-3}$ |

| Diagonal 7  | $3.30 \times 10^{-3}$ |

| Diagonal 8  | $4.12 \times 10^{-3}$ |

| Diagonal 9  | $4.12 \times 10^{-3}$ |

| Diagonal 10 | $3.30 \times 10^{-3}$ |

| Diagonal 11 | $2.57 \times 10^{-3}$ |

| Diagonal 12 | $1.93 \times 10^{-3}$ |

Table 4.2: Required Displacement( Unit: mm )

applied force.

Analysis of the prototype layout results in 192 faults, including all the traces and solder joints. In this work, we assign one fault for each vertical and horizontal segment. However, if the trace is long, it can be divided into more segments, resulting in more faults in the layout. We set the required radius of curvature as 15cm. Setting the cantilever width 1.5cm generates 84 potential cantilevers (excluding fixed/movable pairs on the same edge). Majority of these cantilevers do not stress any component or generate stress conditions that are too weak.

After the initial analysis of stress using Equations 3.2 and 3.3, we determine 27 cantilevers that stress the fault locations as shown in Figure 4.5. Note that application of all 27 mechanical stress patterns would result in unreasonably long test time as the device needs to be re-positioned between subsequent stress patterns. From the given ROC requirement, and using Equation 3.4, we determine the required displacement amount for each cantilever as shown in Table 4.2. We then form the 3D COMSOL model of each cantilever and simulate the stress under various force conditions. We find the force needed to obtain the required displacement amount. For each cantilever and fault location, we determine the mechanical stress under this necessary force.

## 4.2 MATLAB

We use the stress coefficient,  $\alpha$ , to increase the force for each cantilever. The coverage matrix, A is determined based on this new force amount. In MATLAB, we built-in ILP optimizer to select the subset of cantilevers that provide the necessary stress.

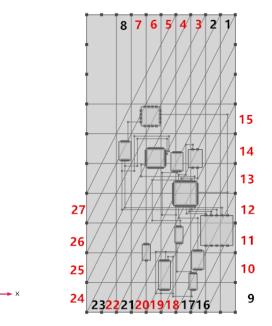

Table 4.3 summarizes the results on the experimental device. When  $\alpha$  is 1, we only apply the necessary amount of force based on the ROC specifications, severely limiting the number of cantilevers that can provide this level of stress. Under this condition, 19 out of 27 cantilevers are selected as shown in Figure 4.6 (red color shows selected cantilevers), resulting in roughly 30% reduction in the number of mechanical stress patterns. As  $\alpha$  increases, more cantilevers cover each fault, and the number of selected stress patterns decreases accordingly.

Figure 4.6: Beams Are Selected

Table 4.3: Number of Selected Mechanical Stress Patterns

| α           | 1  | 5  | 10 | 50 | 100 |

|-------------|----|----|----|----|-----|

| Cantilevers | 19 | 14 | 13 | 10 | 10  |

#### Chapter 5

## CONCLUSIONS

FHE devices are expected to proliferate into the consumer market with explosive growth. However, testing of FHE devices introduces the additional complexity of needing to use mechanical stress patterns in the form of bending and twisting. Since electrical characteristics may shift during mechanical stress and traces and solder joints can fracture, it is necessary to apply multiple stress patterns to ensure that all traces and joints are tested under worse case conditions. Application of mechanical stress almost always involves a moving part, which takes time to settle. Hence, the number of such stress patterns needs to be minimized while still ensuring that all traces and solder joints on the board are stressed adequately.

This paper presented a methodology to enable selection of an optimum set of mechanical stress patterns to cover all potential fault locations and exert the required mechanical stress as dictated by the application. The proposed methodology is validated using an FHE prototype and COMSOL simulations.

#### REFERENCES

[1] William S. Wong and Alberto Salleo. Flexible Electronics: Materials and Applications, chapter 1. Springer US, Boston, 2009.

[2] Ujjwal Gupta, Jaehyun Park, Hitesh Joshi, and Umit Y Ogras. Flexibility-aware system-on-polymer (sop): Concept to prototype. IEEE Transactions on Multi-Scale Computing Systems, 3(1):3649, 2017.

[3] Kwang-Ting (Tim) Cheng and Tsung-Ching (Jim) Huang. Design, analysis, and test of low-power and reliable flexible electronics. In 2010 28th VLSI Test Symposium (VTS), page 82. IEEE, 2010.

[4] Jaehyun Park et al. Flexible PV-cell Modeling for Energy Harvesting in Wearable IoT Applications. ACM Transactions on Embedded Computing Systems (TECS), 16(5s):156, 2017.

[5] N Bednar, A Caviasca, P Sevela, N Severino, and N Adamovic. Modelling of Flexible Thin-Film Modules for Building and Product Integrated Photovoltaics. Solar Energy Materials and Solar Cells, 181:3845, 2018.

[6] Ganapati Bhat, Ujjwal Gupta, Nicholas Tran, Jaehyun Park, Sule Ozev, and Umit Y Ogras. Multi-objective design optimization for flexible hybrid electronics. In Computer-Aided Design (ICCAD), 2016 IEEE/ACM International Conference on, pages 18. IEEE, 2016. [7] Chi W Yau and Najmi Jarwala. A unified theory for designing optimal test generation and diagnosis algorithms for board interconnects. In 1989 International Test Conference, pages 7177. IEEE, 1989.

[8] Be Van Ngo, Peter Law, and Anthony Sparks. Use of jtag boundary-scan for testing electronic circuit boards and systems. In AUTOTESTCON, 2008 IEEE, pages 1722. IEEE, 2008.

[9] Tsung-Ching Jim Huang, Jason Marsh, Scott H. Goodwin, and Dorota S. Temple. Innovative practices on design test for flexible hybrid electronics. In 2018 IEEE 36th VLSI Test Symposium (VTS), page 1. IEEE, 2018.

[10] Rui Chen, Justin Chow, Christine Taylor, Jeffrey Meth, and Suresh Sitaraman.Adaptive curvature flexure test to assess flexible electronic systems. In 2018 IEEE68th Electronic Components and Technology Conference, pages 236242. IEEE, 2018.

[11] Richard L. Chaney, Douglas R. Hackler, Dale G. Wilson, and Brian N. Meek. Physically exible high performance single crystal cmos integrated with printed electronics. In 2014 IEEE Workshop On Microelectronics And Electron Devices (WMED), pages 14. IEEE, 2014.

[12] Pradeep Lall, Jinesh Narangaparambil, Amrit Abrol, Ben Leever, and Jason Marsh. Development of test protocols for the flexible substrates in wearable applications. In 2018 17th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, pages 11201127. IEEE, 2018. [13] Warren C Young and Richard G Budynas. Roarks Formulas for Stress and Strain, chapter 8. McGraw-Hill, New York, London, 7 edition, 2002.

[14] Tsung-Ching Huang, Jiun-Lang Huang, and Kwang-Ting Cheng. Robust Circuit Design for Flexible Electronics. IEEE Design and Test of Computers, 28(6):815, 2011.

[15] Arokia Nathan, Arman Ahnood, Matthew T Cole, Sungsik Lee, Yuji Suzuki, Pritesh Hiralal, Francesco Bonaccorso, Tawfique Hasan, Luis Garcia-Gancedo, Andriy Dyadyusha, Samiul Haque, Piers Andrew, Stephan Hofmann, James Moultrie, Daping Chu, Andrew J. Flewitt, Andrea C. Ferrari, Michael J. Kelly, John Robertson, Gehan A. J. Amaratunga, and William I. Milne. Flexible Electronics: The Next Ubiquitous Platform. Proc. of IEEE, 100(Special Centennial Issue):14861517, 2012.

[16] Jayna Sheats. Truly wearable electronics. In Presented at the FlexTech Alliance Workshop: Flexible Hybrid Electronics Challenges and Solutions, July 2014.

[17] Richard L Chaney, Douglas R Hackler, Dale G Wilson, and Brian N Meek. FleX Silicon-on-Polymer: Flexible (Pliable) ICs from Commercial Foundry Processes. In Proc. of GOMACTech (Government Microcircuit Applications and Critical Technology) Conf., March 2013.

[18] Darrell E. Leber, Brian N. Meek, Seth D. Leija, Dale G. Wilson, Richard L. Chaney, and Douglas R. Hackler. Electromechanical reliability testing of flexible hybrid electronics incorporating flex silicon-on-polymer ics. In 2016 IEEE Workshop on Microelectronics and Electron Devices (WMED), pages 14. IEEE, 2016.

[19] Bor-Jiunn Wen and Tzong-Shi Liu. Bending-characteristic measurement of flexible electronics by using fast optimal sliding mode control method. In Proceedings of SICE Annual Conference 2010, pages 18721874. IEEE, 2010.

[20] Sonia Grego, Jay Lewis, Erik Vick, and Dorota Temple. Development and evaluation of bend-testing techniques for flexible splay applications. Journal of the Society for Information Display, 13(7):575581, 2005.

[21] Daan van den Ende1, Frits Verhoeven, Pepijn van der Eijnden, Roel Kusters, Ashok Sridhar, Maarten Cauwe, and Jeroen van den Brand. High curvature bending characterization of ultra-thin chips and chip-on-foil assemblies. In 2013 Eurpoean Microelectronics Packaging Conference (EMPC), pages 16. IEEE, 2013.

[22] R. C. Stephens. Strength of Materials: Theory and Examples, chapter 3. Edward Arnold, London, England, 1971.

[23] Josh Parker. Normal stress, bending stress, & shear stress, 2010. http://www.str-ucalc.com/normal-stress-bending-stress-shear-stress