# Hybrid Multiresolution Simulation & Model Checking: Network-On-Chip Systems

by

Soroosh Gholami

## A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved October 2017 by the Graduate Supervisory Committee:

Hessam S. Sarjoughian, Chair Georgios Fainekos Umit Ogras Aviral Shrivastava

ARIZONA STATE UNIVERSITY

December 2017

#### ABSTRACT

Designers employ a variety of modeling theories and methodologies to create functional models of discrete network systems. These dynamical models are evaluated using verification and validation techniques throughout incremental design stages. Models created for these systems should directly represent their growing complexity with respect to composition and heterogeneity. Similar to software engineering practices, incremental model design is required for complex system design. As a result, models at early increments are significantly simpler relative to real systems. While experimenting (verification or validation) on models at early increments are computationally less demanding, the results of these experiments are less trustworthy and less rewarding. At any increment of design, a set of tools and technique are required for controlling the complexity of models and experimentation.

A complex system such as Network-on-Chip (NoC) may benefit from incremental design stages. Current design methods for NoC rely on multiple models developed using various modeling frameworks. It is useful to develop frameworks that can formalize the relationships among these models. Fine-grain models are derived using their coarse-grain counterparts. Moreover, validation and verification capability at various design stages enabled through disciplined model conversion is very beneficial.

In this research, Multiresolution Modeling (MRM) is used for system level design of NoC. MRM aids in creating a family of models at different levels of scale and complexity with well-formed relationships. In addition, a variant of the Discrete Event System Specification (DEVS) formalism is proposed which supports model checking. Hierarchical models of Network-on-Chip components may be created at different resolutions while each model can be validated using discrete-event simulation and verified via state exploration. System property expressions are defined in the DEVS language and developed as *Transducers* which can be applied seamlessly for model checking and simulation purposes.

Multiresolution Modeling with verification and validation capabilities of this framework complement one another. MRM manages the scale and complexity of models which in turn can reduces V&V time and effort and conversely the V&V helps ensure correctness of models at multiple resolutions. This framework is realized through extending the DEVS-Suite simulator and its applicability demonstrated for exemplar NoC models. This dissertation is dedicated to:

my parents, for their unconditional love and support my brothers, for being the best mentors and role models and my true friend whom I always regarded as family

The five of you are the reason for who I am today.

#### ACKNOWLEDGMENTS

I would like to express my deepest appreciation to Dr. Hessam Sarjoughian for the guidance and help he generously provided me throughout these past few years. I am very thankful for the freedom I was given to explore various research directions and for his patience in times of disagreement. From the long list of qualities I hope to have acquired from him, above all were his integrity and ethics: qualities in very short supply these days.

I would also like to thank my committee members: Dr. Georgios Fainekos, Dr. Umit Ogras, and Dr. Aviral Shrivastava for their open mind, insightful advices, and constructive feedback which assisted me in the completion of this research. In addition to that, I give thanks to their exceptional one-on-one meetings which definitely improved the quality of this research leading to this point.

Furthermore, I must acknowledge members of the ACIMS, present and past, for their friendship, assistance, and support. I must specifically thank Abdurrahman Alshareef, William Boyd, Masudul Quraishi, Savitha Sundaramoorthi, and Chao Zhang, my labmates at ACIMS with whom I have great memories, for tolerating my presence in the lab in times of frustration or despair. Among past members, I express my thanks to Dr. Gary Godding for everything I learned from him in our collaborative project and my great appreciation toward Dr. Gary Mayer for his assistance toward finding the right career upon graduation. I wish all these individuals the best of luck and I hope our paths cross each other again soon.

Next, I must thank all my colleagues at PayPal especially my immediate manager Brian Bogard for his support and for the great times I had there as an intern. Everything I learned from my colleagues during this internship did nothing but teach me new things about myself which helped me better myself even more as a PhD student.

Also, I must thank all my close friends (they know who they are) who made my

PhD experience much more enjoyable and these years away from my loving family tolerable. One great benefit of my PhD experience was all the new friends I made here from each of whom I learned a lot. I wish all of them the best in their future endeavors and thank their indirect but great contributions to this dissertation.

Last but not least, I would not have been able to do this dissertation without the help of many others here at ASU, some of whom are unknown to me. That is why I would like to extend my appreciation toward the administrative staff especially Monica Dugan, Pamela Dunn, and Christina Sebring whom I troubled a lot but were always there to help me. Thank you.

|      |      |        | F                                                 | Page |

|------|------|--------|---------------------------------------------------|------|

| LIST | OF T | TABLES | 5                                                 | ix   |

| LIST | OF F | IGURE  | ES                                                | х    |

| CHAI | PTER | t      |                                                   |      |

| 1    | INT  | RODU   | CTION                                             | 1    |

|      | 1.1  | Proble | em Description                                    | 6    |

|      |      | 1.1.1  | NoC Multiresolution Modeling                      | 7    |

|      |      | 1.1.2  | NoC V&V                                           | 11   |

|      |      | 1.1.3  | Realization in a DEVS-Suite Tool                  | 12   |

|      | 1.2  | Disser | tation Goals and Scope                            | 14   |

| 2    | BAC  | CKGRO  | UND                                               | 19   |

|      | 2.1  | Netwo  | rk-on-Chips                                       | 19   |

|      |      | 2.1.1  | Network-on-Chip Model Validation and Verification | 20   |

|      |      | 2.1.2  | Deadlock in Network-on-Chips                      | 21   |

|      | 2.2  | Simula | ation and Validation                              | 24   |

|      | 2.3  | Model  | Checking                                          | 26   |

|      |      | 2.3.1  | Support for Non-determinism and Stochasticity     | 27   |

|      |      | 2.3.2  | Limited Property Checking Capability              | 28   |

|      | 2.4  | Multir | resolution Modeling                               | 29   |

|      | 2.5  | Homo   | morphic Mapping                                   | 31   |

| 3    | REL  | LATED  | WORK                                              | 35   |

|      | 3.1  | Netwo  | rk-on-Chip Validation and Verification            | 35   |

|      | 3.2  | Model  | Checking                                          | 39   |

|      |      | 3.2.1  | DEVS-based Model Checking                         | 40   |

|      | 3.3  | Multir | resolution Modeling                               | 44   |

# TABLE OF CONTENTS

# Page

| 4 | MUI | LTIRESOLUTION MODELING46 |                                                             |    |

|---|-----|--------------------------|-------------------------------------------------------------|----|

|   | 4.1 | Multir                   | esolution modeling                                          | 47 |

|   | 4.2 | Multir                   | esolution NoC Models                                        | 54 |

|   |     | 4.2.1                    | Link                                                        | 56 |

|   |     | 4.2.2                    | Switch                                                      | 59 |

|   |     | 4.2.3                    | Network Interface                                           | 61 |

| 5 | CON | ISTRA                    | INED MODELING AND VERIFICATION                              | 64 |

|   | 5.1 | DEVS                     | and Model Checking                                          | 64 |

|   |     | 5.1.1                    | DEVS Modeling                                               | 65 |

|   |     | 5.1.2                    | DEVS Simulation                                             | 68 |

|   |     | 5.1.3                    | Requirements for DEVS Model Checking                        | 70 |

|   | 5.2 | Constr                   | ained modeling                                              | 71 |

|   |     | 5.2.1                    | State Configuration                                         | 72 |

|   |     | 5.2.2                    | Port Configuration                                          | 73 |

|   |     | 5.2.3                    | Finite Number of Internal/External Events                   | 74 |

|   | 5.3 | Model                    | Checking Protocol                                           | 75 |

|   | 5.4 | Additi                   | onal Features of Constrained-DEVS Modeling and Verification | 80 |

|   |     | 5.4.1                    | Selective State Exploration                                 | 80 |

|   |     | 5.4.2                    | Trace Analysis                                              | 82 |

|   |     | 5.4.3                    | Property Expressions                                        | 83 |

|   | 5.5 | Integra                  | ating MRM and V&V                                           | 85 |

| 6 | IMP | LEME                     | NTATION                                                     | 87 |

|   | 6.1 | Constr                   | rained-DEVS and Model Checking in DEVS-Suite                | 87 |

|   |     | 6.1.1                    | Constrained-DEVS Modeling in DEVS-Suite                     | 88 |

|      |      | 6.1.2  | State Space Exploration Protocol                           | 0 |

|------|------|--------|------------------------------------------------------------|---|

|      |      | 6.1.3  | Circular Buffer Model 99                                   | 9 |

|      | 6.2  | MRM    | NoC Library in DEVS-Suite                                  | 1 |

|      |      | 6.2.1  | NoC Components                                             | 2 |

|      |      | 6.2.2  | Topologies                                                 | 2 |

|      |      | 6.2.3  | Routing Methods and VC Allocation                          | 3 |

|      |      | 6.2.4  | Flow Control Mechanisms103                                 | 3 |

|      |      | 6.2.5  | Data Types104                                              | 4 |

|      |      | 6.2.6  | Transducers                                                | 6 |

|      |      | 6.2.7  | Other Aspects                                              | 6 |

|      | 6.3  | Model  | ing Comparison: UPPAAL vs. DEVS-Suite                      | 6 |

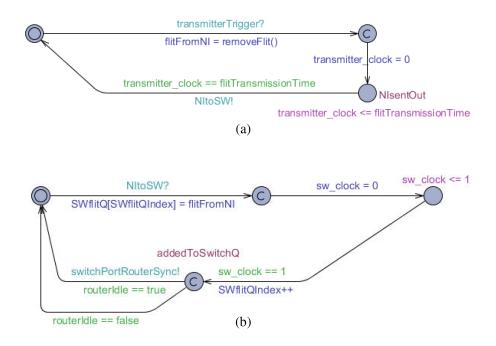

|      |      | 6.3.1  | NoC modeling: Timed Automata & UPPAAL10                    | 7 |

|      |      | 6.3.2  | NoC modeling: Constrained DEVS & DEVS-Suite110             | 0 |

|      | 6.4  | Exper  | imentation                                                 | 2 |

|      |      | 6.4.1  | NoC Verification: PE Utilization and Task Distribution 113 | 3 |

|      |      | 6.4.2  | Deadlock Avoidance Verification                            | 5 |

|      |      | 6.4.3  | Deadlock Detection                                         | 5 |

|      |      | 6.4.4  | Performance analysis                                       | 7 |

| 7    | CON  | ICLUS  | ION AND FUTURE WORK                                        | 0 |

|      | 7.1  | Future | e Work                                                     | 1 |

|      |      | 7.1.1  | Homomorphic Mapping13                                      | 1 |

|      |      | 7.1.2  | Gate-level Models                                          | 3 |

|      |      | 7.1.3  | DEVS to Hardware Description Language                      | 4 |

| REFE | EREN | CES    |                                                            | 6 |

# LIST OF TABLES

| Table | Page                                                                      |

|-------|---------------------------------------------------------------------------|

| 2.1   | Evaluation Measures for NoC Simulation Environments                       |

| 4.1   | Application Software with Accuracy/Precision Resolutions 51               |

| 5.1   | Sample Simulation Scenario for Circular Buffer                            |

| 6.1   | Sample Runs of the Circular Buffer Verification101                        |

| 6.2   | Maximum and Minimum Processor Utilization Using Round Robin               |

|       | (RR) and Adaptive Task Distributors with Total Execution Time $\dots 114$ |

| 6.3   | Deadlock Avoidance for Mesh with X-Y Routing                              |

| 6.4   | Deadlock Avoidance for The Balanced Tree with Shortest Path Routing124    |

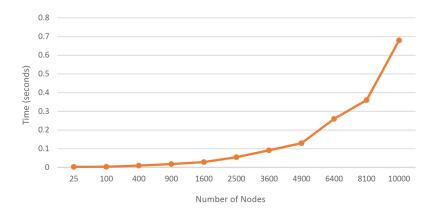

| 6.5   | Duration of Model Checking and Size of the Reachable State Space for      |

|       | Various Network Sizes                                                     |

# LIST OF FIGURES

| Figure | Page                                                                     | Э |

|--------|--------------------------------------------------------------------------|---|

| 1.1    | 3-phase Chip Design Approach                                             | 2 |

| 1.2    | NoC Model Categorization Using 1) System Specification Hierarchy,        |   |

|        | 2) NoC Model Abstraction Levels, and 3) Multiresolution Dimensions.      | ) |

| 1.3    | The Role of a Designated Tool in Model Development and V&V $\dots$ 13    | 3 |

| 1.4    | V&V in MRM-based for ESL Chip Design Phase 14                            | 1 |

| 1.5    | NoC Pieces and Their Abstraction Levels 16                               | 3 |

| 1.6    | Model Validation and Verification Processes at Each Abstraction Level 18 | 3 |

| 2.1    | Abstraction Levels for NoC Modeling and Simulation 20                    | ) |

| 2.2    | Deadlock Condition Implicating 4 Nodes 22                                | 2 |

| 2.3    | Wait-for Graph for the Network Shown in Figure 2.2 23                    | 3 |

| 2.4    | Increasing Object Resolution for the Switch Component 31                 | L |

| 2.5    | Two Isomorphic Models with Different Structures                          | 3 |

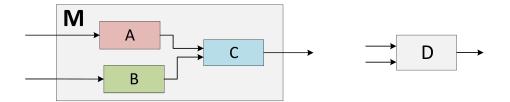

| 4.1    | Mid-resolution Application Software Model                                | 3 |

| 4.2    | Changing Five Aspects of Resolution Visualized for Noc. (A) Increas-     |   |

|        | ing Object Resolution via Compartmentalization, (B) Increasing the       |   |

|        | Temporal Resolution by Increasing the Granularity of Time, (C) In-       |   |

|        | creasing Process Resolution (in a Routing Algorithm) by Suggesting a     |   |

|        | More Intricate Approach, (D) Increasing Spatial Resolution by Adding     |   |

|        | Physical Information (Vertical Interconnection and Size), (E) Increas-   |   |

|        | ing the Resolution of Data by Incorporating More Granular Data Chunks 55 | 5 |

| 4.3    | Low-resolution Link Model with the Type of Data It Communicates 57       | 7 |

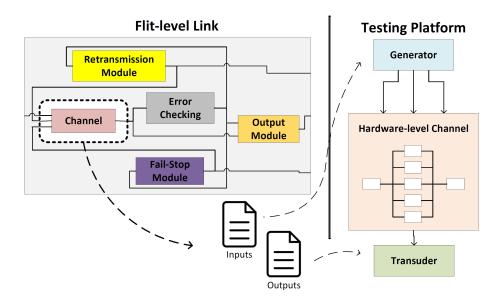

| 4.4    | Link Models at the Flit and Hardware Abstraction Levels                  | ) |

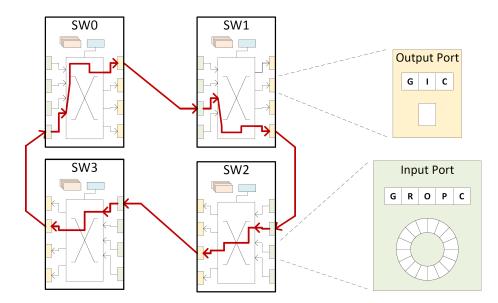

| 4.5    | Capacity and Flit Level NoC Hardware Model Abstractions                  | ) |

| 4.6    | High-resolution Models of Input/Output Ports in the Switch               | L |

# Figure

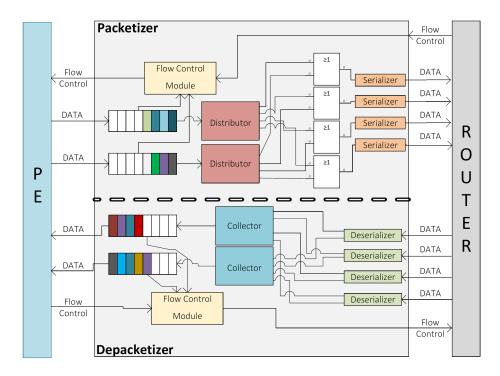

| 4.7 | IO System, Flit-level Model of NI                                        | 62 |

|-----|--------------------------------------------------------------------------|----|

| 4.8 | IO System, Hardware-level Model of NI                                    | 63 |

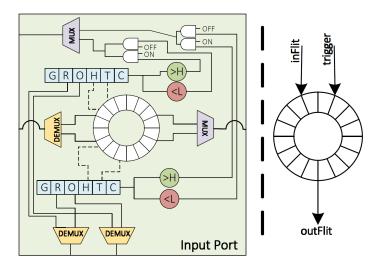

| 5.1 | NoC switch input module utilizing a circular buffer (left) with its sim- |    |

|     | plified diagram (right)                                                  | 66 |

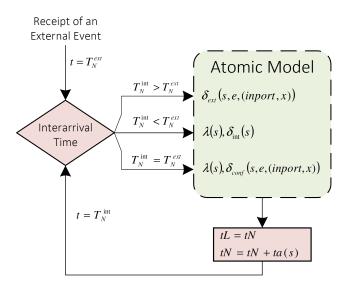

| 5.2 | Time management in the coordinator module (with solid borders and        |    |

|     | in red) and invocation of the atomic model functions (with dashed        |    |

|     | borders and in green) in the simulator module                            | 69 |

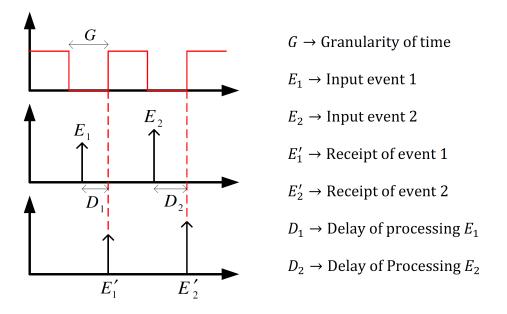

| 5.3 | Discrete-time Processing of Events                                       | 75 |

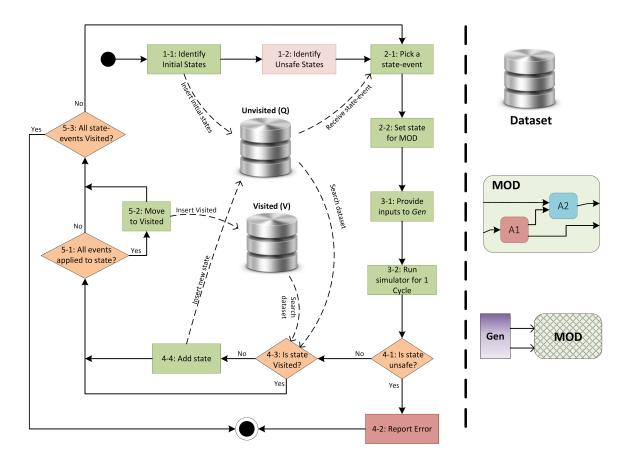

| 5.4 | A Flowchart for the Constrained-DEVS Model Checking Protocol in          |    |

|     | DEVS-Suite                                                               | 80 |

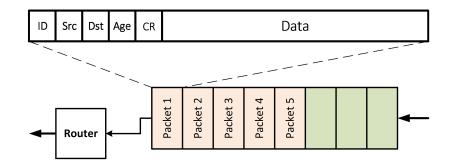

| 5.5 | Waiting Queue of a Switch and the Structure of Packets It Stores         | 81 |

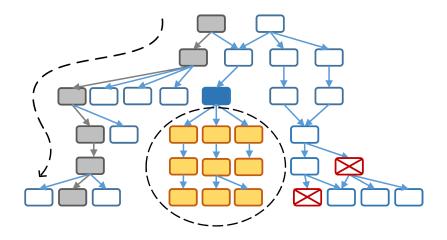

| 5.6 | Trace Analysis on a Pruned Reachability Graph                            | 83 |

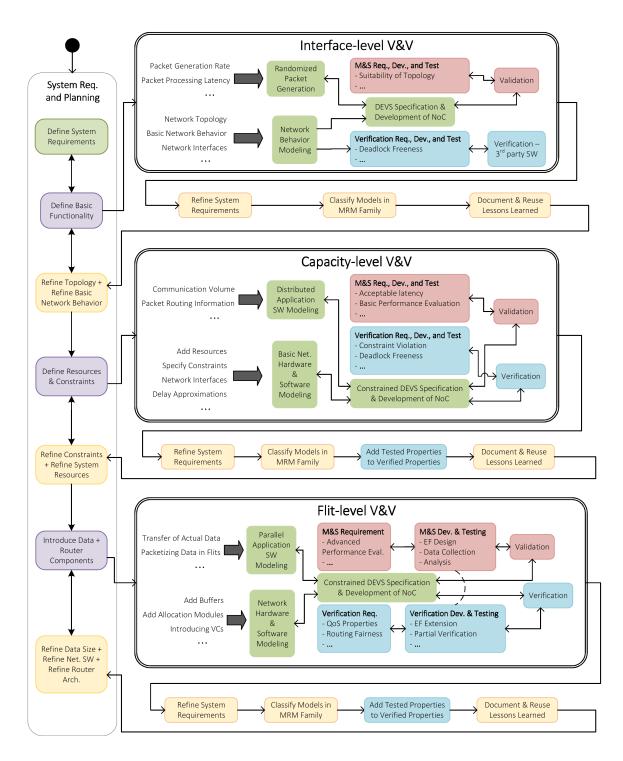

| 5.7 | MRM-based Chip Design at ESL Phase with V&V Steps at Each Ab-            |    |

|     | straction Level                                                          | 86 |

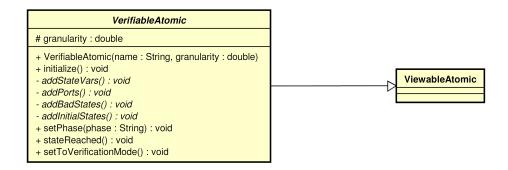

| 6.1 | VerifiableAtomic Class for Validation and Verification                   | 88 |

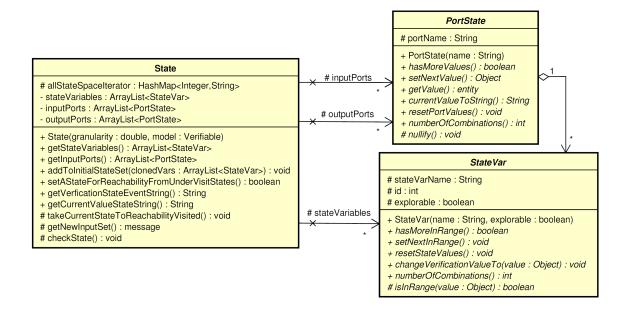

| 6.2 | State, StateVar, and PortState Classes for State Space Exploration       | 90 |

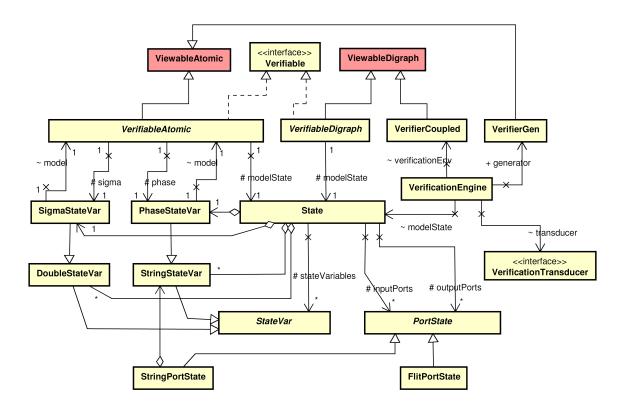

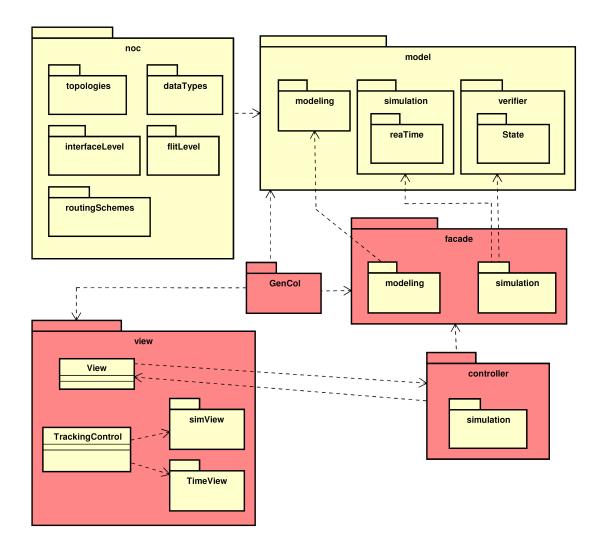

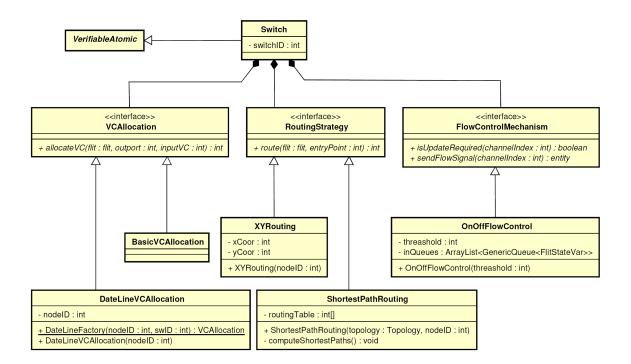

| 6.3 | Partial UML Diagram of DEVS-Suite Modeling Class Structure (New          |    |

|     | Classes in Yellow)                                                       | 92 |

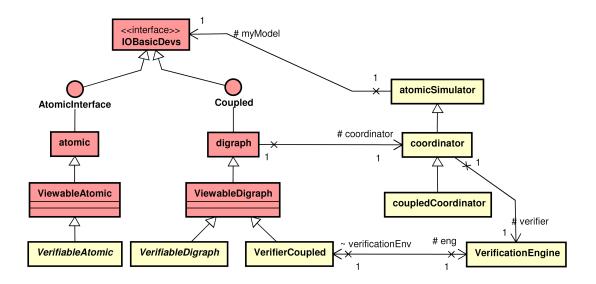

| 6.4 | Partial UML Diagram of DEVS-Suite Model, Simulation, and Verifier        |    |

|     | Packages (New and Modified Classes in Yellow)                            | 93 |

| 6.5 | Partial Package Diagram of DEVS-Suite (New and Modified Packages         |    |

|     | in Yellow)                                                               | 94 |

|     |                                                                          |    |

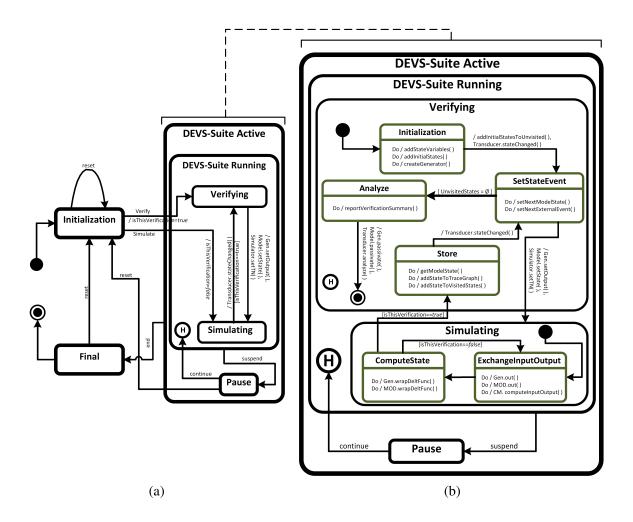

| 6.6  | DEVS-Suite V&V Statechart: (a) Partial Statechart Diagram for DEVS-        |

|------|----------------------------------------------------------------------------|

|      | Suite From Initialization to Termination, (b) Detailed View of the         |

|      | "DEVS-Suite Active" State (Containing Verification and Simulation          |

|      | Sub-states)                                                                |

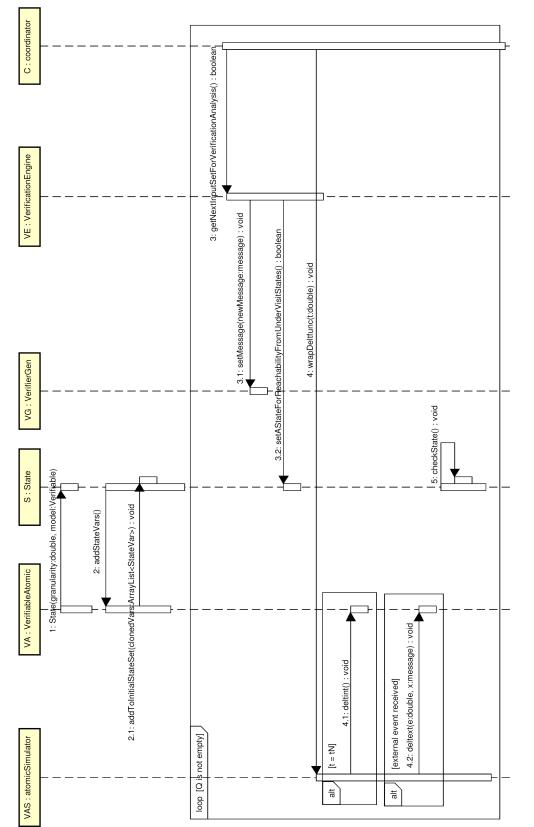

| 6.7  | Partial UML Sequence Diagram Exemplifying the Execution of State           |

|      | Space Exploration Protocol                                                 |

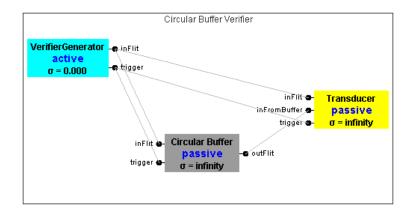

| 6.8  | Circular Buffer Model Verification                                         |

| 6.9  | Strategy Design Pattern for Detaching Behavior from Structure and          |

|      | Flexibility                                                                |

| 6.10 | Detailed View of NoC as Modeled in Timed Automata. Each Compo-             |

|      | nent is a Separate Process                                                 |

| 6.11 | Two Sample Components of NoC and How They Are Connected via                |

|      | TA Channels: (a) NI Transmitter, (b) Swith Input Port109                   |

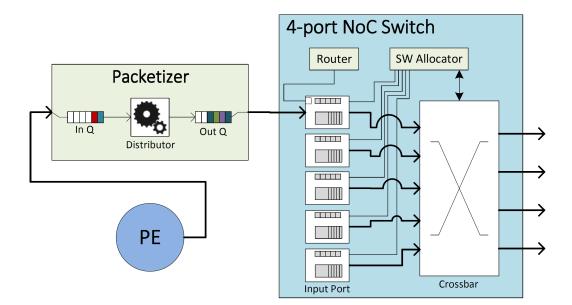

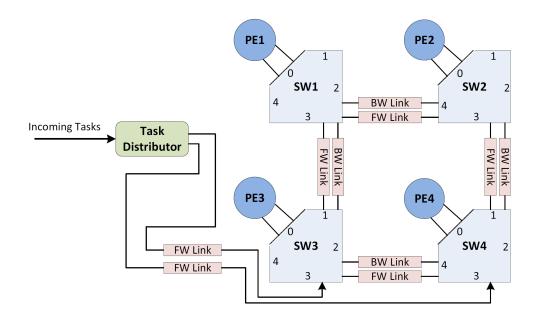

| 6.12 | A 4-node Model of NoC With the Task Distributor Component111               |

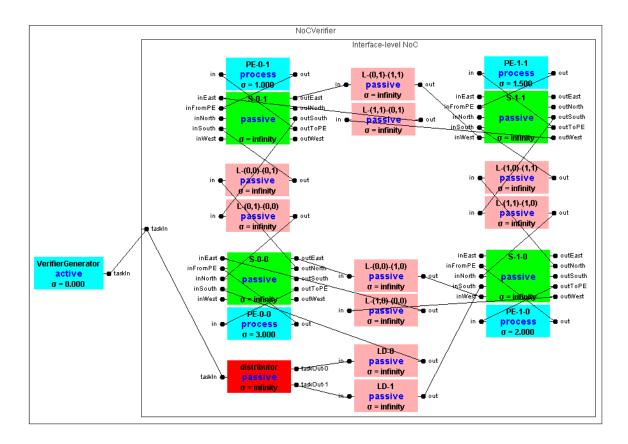

| 6.13 | The Verification Environment for a 4-node Model of NoC With Major          |

|      | Components: PE, Switch, Link, and Task Distributor in DEVS-Suite 112       |

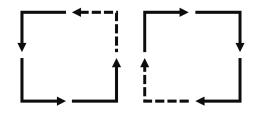

| 6.14 | A Turn-model Rule Where Dashed Lines Show Forbidden Turns116               |

| 6.15 | Deadlock Scenario for the Turn-model in Figure 6.14. (a) The Cycle         |

|      | Caused by the Turn-model, (b) The Deadlock in Effect in a Mesh             |

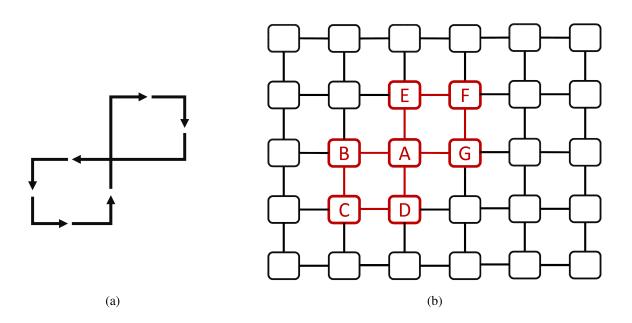

|      | Network with the Following Simultaneous Transmissions: $A \rightarrow C$ , |

|      | $B \to D, C \to E, D \to F, A \to F, E \to G, F \to A, G \to B \dots 116$  |

| 6.16 | 2D NoC Custom Topology 121                                                 |

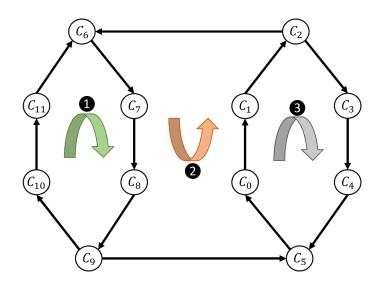

| 6.17 | CDG For the Network Topology in Figure 6.16, Shortest Path Routing,        |

|      | and Simple VC Allocation                                                   |

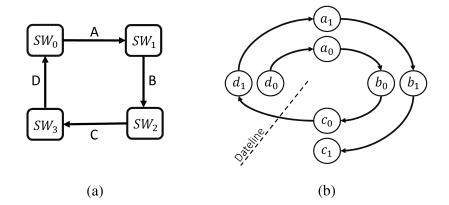

| 6.18 | Simple Ring with Two Virtual Channels and Dateline at Link $D$ . (a)        |

|------|-----------------------------------------------------------------------------|

|      | The Ring Network with 4 Nodes (Refer to Figure 2.2) (b) CDG For             |

|      | the Network with Virtual Channels Divided into Dateline Classes $\dots 122$ |

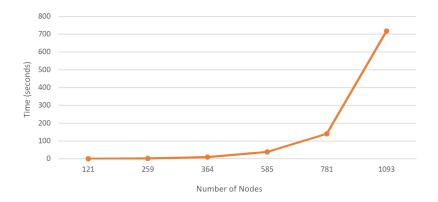

| 6.19 | Plot for the Execution Times Presented in Table 6.3                         |

| 6.20 | Plot for the Execution Times Presented in Table 6.4                         |

| 6.21 | Deadlock Condition in a 4-node Flit Level Network. Input/Output             |

|      | Status Arrays and Buffers are Shown in Detail                               |

| 7.1  | A Coupled Model and an Atomic One as Homomorphic Models $\ldots \ldots 131$ |

| 7.2  | Validation of Simulation Models Across Different Resolution Using Ho-       |

|      | momorphic Mapping                                                           |

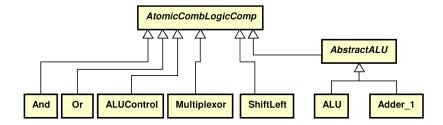

| 7.3  | Select Combinational Logic Models from MIPS-DEVS Library133                 |

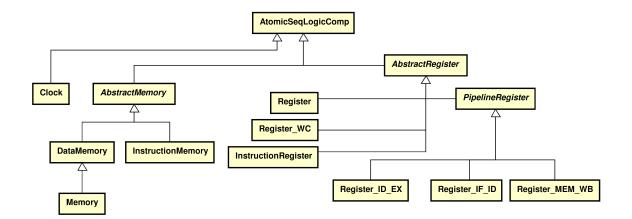

| 7.4  | Select Sequential Logic Models from MIPS-DEVS Library                       |

#### Chapter 1

### INTRODUCTION

Development of any complex discrete network system involves a design phase in which multiple models of the system are created and experimented with. Each model may focus on some aspect of the system and is specified at a certain abstraction level. The models that are created and the evaluations that are conducted all depend on the nature of the target system. As for discrete network systems, models and evaluations focus on the structure, functionality correctness, and QoS satisfaction. Designing network systems also requires multiple models to be created at different abstraction levels, each focusing on certain structural and behavioral aspects.

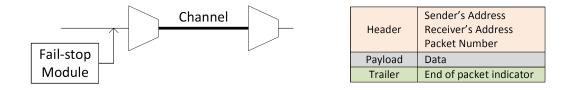

Systems on Chips (SoC), as a complex discrete network system, has several interconnected intellectual properties (IP) on a 2-D or 3-D chip. The IPs may communicate with one another using shared buses. Shared buses require complex scheduling or prioritized access as each bus can be only driven by one component at a time. An alternative to this approach is Network on Chip (NoC) (Hemani *et al.*, 2000) in which communication among IPs (cores) are treated as series of packets sent and received using an underlying network.

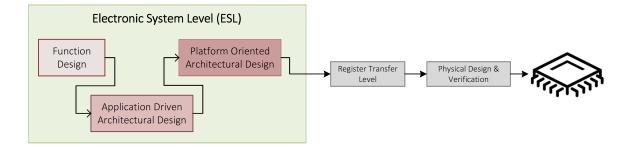

Development process of typical Integrated Chip (IC) designs can be categorized into three major phases. The process starts with the Electronic System Level (ESL) phase (Martin *et al.*, 2010). There are three steps within the ESL phase: 1) function design, 2) application-driven architectural design, and 3) platform-oriented architectural design (Martin *et al.*, 2010). In the first step, a functional model of the application is devised. The second step is dedicated to creating high-level description of the platform and verifying it with the functional application. Finally, in the third

Figure 1.1: 3-phase Chip Design Approach

step, low-level description of the platform is created and the architecture is fine-tuned (Bricaud, 2012). After the completion of the ESL phase, a Register Transfer Level (RTL) design phase will follow in which gate-level descriptions are created based on the resulting architecture from the ESL phase. Finally, in the physical design phase, the gate-level representation is converted into geometric representations. This three-phase approach toward chip design is demonstrated in Figure 1.1.

Similar to the ESL phase, the RTL and Physical Design phases introduce a number of steps to IC design. There is generally strict dependencies between these tasks. In order to design a computer chip from scratch, one cannot automate or bypass these tasks as each of them is responsible for key design decisions. However, a systematic transition from system-level to physical-level specifications is highly desired.

Currently, various tools in different levels of abstraction are used to design new chips or improve existing ones. High-level decisions (such as number of nodes and topology) can be made using coarse-grain models while low-level decisions (such as operating frequency, flow control policy, and hardware brands) should be taken using fine-grain models. Models are developed using two approaches: 1) formal specifications that are implementation-independent (not specific to a certain programming language) and 2) semi-formal specifications written in programming languages (Bricaud, 2012). In order to produce system design at the end of the Electronic System Level (ESL) phase, the user may use a number of these specifications, languages, and tools.

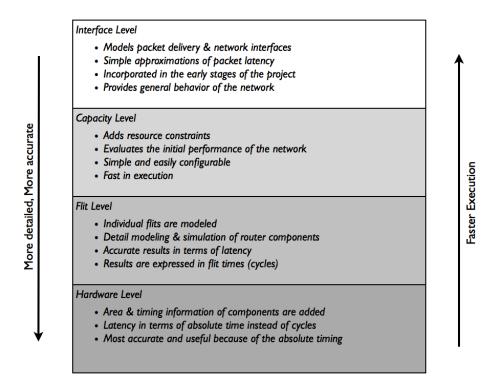

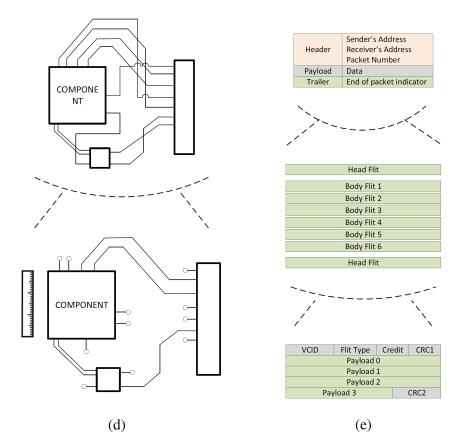

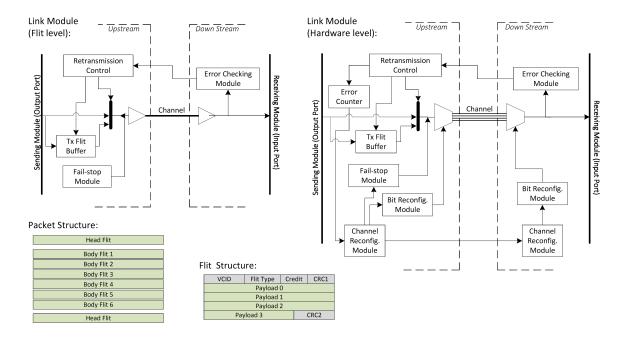

The concept of abstraction levels for NoC is well-established. The NoC community has introduced four levels of abstraction. From the highest to lowest, abstractions are defined at Interface, Capacity, Flit, and Hardware levels (Dally and Towles, 2004). Hardware-level models have the most details while interface-level models have the least. Designers develop models at various (fine-grain to coarse-grain) granularities during the ESL phase. NoC models at each level are evaluated to ensure correctness and compatibility with their respective requirements using verification and validation methods.

Ideally, a desired design process for NoC should provide a systematic transition from coarse-grain models to fine-grain models while providing the designer with V&V capabilities. Models should be parameterized and easily modifiable. MRM and V&V should complement one another to facilitate a systematic design process. In this process, MRM assists the V&V process by providing a family of models at different resolutions each of which can be used for validation or verification of some properties. This way, verification or validation of some properties can be conducted in higher abstractions which are computationally less demanding and may hold for lower abstractions. On the other side of this equation, V&V assists the MRM process by ensuring correctness and therefore facilitating the creation of finer-grain model from coarse-grain counterparts.

In reality, the design process remains ad-hoc requiring designers to create numerous models at various levels of abstraction often using a number of tools/languages. Some these models are so different from others that there is no well-established way for deducting similarity relationships between them. Without established relationships, creating new models based on existing ones is a manual and ad-hoc process compromised by human error and incompatible modeling frameworks. Multiresolution modeling is the candidate toward our goal for transitioning from high-level requirements to low-level design specifications of NoCs. Resolution is defined as the degree of detail used to model systems (Department of Defense, 1998). Fidelity of models can be varied in terms of NoC time, object, process, and space characteristics of interest. In Multiresolution Modeling (MRM), a single model or an integrated family of models describe the physical system/phenomena in various levels of fidelity (Davis and Bigelow, 1998). Potentially, these multiresolution models can be leveraged to validate and verify a system in different levels of detail. As opposed to ad-hoc modeling at various abstraction levels, MRM aim is to clearly define the relationship between models at various levels of detail. An MRM provides a set of predefined levels of abstractions within which the designer can create models.

The terms abstraction level and resolution may be used interchangeably. Highly abstracted models hold less details within their specifications and therefore they have lower resolutions. Similarly, models specified in low abstractions contain detailed specifications and can be referred to as high-resolution models. One problem standing in the way of NoC modeling is that the relationships among the Interface, Capacity, Flit, and Hardware abstraction levels are not formalized. Models at these levels of abstraction are distinct in some aspects such as functionality, timing, attributes, entities, and logical dependencies. Multi-Resolution Modeling can help manage specifying models at various levels of resolution and can define relationships between them based on the aspects that are changed moving from one resolution to another. Models at different resolutions are similar in some aspects and different in others. As mentioned, MRM attempts to categorize and form relationships based on the differences between models.

Using semi-formal specifications is very common in modeling and simulation of Network-on-Chips. SystemC (SystemC, 2017) is widely used for modeling and simulation of hardware and software architectures for System-on-Chips. One important aspect of semi-formal specifications is the integration of the modeling method and the simulation engine. Models are created directly in an executable programming language. This is different from formal approaches in which a modeling formalism is used to create the models. The formalism is implementation independent and can be later developed within any execution environment supporting that formalism. Separation of model and simulation is one of the main features of formal specifications. Establishing relationships between models at different resolutions using MRM and homomorphic mapping is one of the benefits of separating model and simulation. One can reuse verification or validation efforts applied to one model on another model with established relationships. This may not be as straightforward on semi-formal languages.

Researchers in various domains have made use of Modeling and Simulation (M&S) for analysis and design of very large, complex systems. These systems range from environmental systems (Antle *et al.*, 2001; Mayer *et al.*, 2006), to virtual environments for training purposes (Basdogan *et al.*, 2001; Norlin, 1995). Although validation through simulation is widespread, the coverage of simulation scenarios is incomplete. Therefore, it is possible to miss some scenarios in which some models do not behave as intended. In the case of verification, model checking may theoretically explore the entire state space of the model. Therefore, through model checking approach one can guarantee that the verification coverage is complete. A weakness of model checking is the amount of time it can take for exhaustively exploring a models state space. Complex models may possess an enormous state space. It may not be possible to verify these models using model checking due to the unreasonable amount of time it may take. For verifying large and complex models, one can reduce the size of state space by developing coarser grain models. Verification using model checking may be

achievable for these coarse grain models.

Designers use both validation and verification techniques in order to achieve some degree of assurance that the model is an accurate representation of the reference model and its specifications. Model validation is based on some reference model which could be mental (expectations of the designer from the model) or physical (the real system which is cloned into a model). However, for verification, one focuses on whether the model accurately reflects the specifications of the system. Based on the nature of the models, the system they represent, and the type of input/outputs, one can use various techniques for V&V (Sargent, 2005; Whitner and Balci, 1989) such as stress testing (Myers *et al.*, 2011), Turing tests (Schruben, 1980), and induction (Stoy, 1977). In this research we focus on 1) simulation scenarios and 2) model checking as main methods for validation and verification of models at each resolution. A simulation scenario validates the operation of the model based on references such as the expectation of the modeler, previously gathered data, or another model (Sargent, 2005).

Analyses on a specification of models at each level of resolution provide a set of useful results for making design decisions. The analyses for each level of abstraction could be simulation or model checking. The results of these analyses are reported in various ways. For a network system, these analyses may be reported in average latency, throughput, data loss rate, and average queuing time.

### 1.1 Problem Description

Marculescu *et al.* have identified four major categories of open research and future challenges for NoC design: 1) application specification and modeling, 2) application optimization for communication, 3) communication architecture analysis and evaluation, and 4) NoC design validation and synthesis (Marculescu *et al.*, 2009). Our work in this research focuses on the categories 3 and 4. In the third category, performance models are used to recognize communication issues such as congestion points. This is possible through V&V. Upon reaching a certain level of confidence with the model, the designer may move forward with layout design. In the fourth category of research problems, the focus is on design validation and synthesis. Various methods of validation such as simulation, prototyping, and testing exist to ensure the designed NoC will operate as expected.

In this section, we describe the research problems we are trying to address. Our contributions relate to the following research solutions: 1) NoC multiresolution modeling and 2) NoC model validation and verification.

## 1.1.1 NoC Multiresolution Modeling

Currently, IC designers start with identifying requirements and developing systemlevel specifications of the desired system and then gradually add details to it toward a synthesizable specification (one which can be synthesized on physical hardware). During this process, the designer may use various modeling methods. In addition, evaluation of a design introduces the need for use of several tools/languages throughout the design process. Over the course of the design process, the modeler may end up with a set of disconnected models in various levels of abstraction, each evaluating a crucial aspect of the system under design. In the end, all design decisions made and evaluations performed on these models in various abstractions contribute to developing a synthesizable specification that is used for physical hardware implementation.

The design process for NoC is similar to the one described for integrated computer chips. Complexity of NoC design is amplified due to having software components (network software and application software) in addition to hardware components. The requirements of software impacts hardware design and vice versa. Each major component in NoC (whether a SW or HW component) can be modeled at different abstraction levels. Considering all components in a NoC, the number of models that can be created at various levels of abstraction is very large. Finding the right abstraction to model NoC in this large space so that it can be used for validation/verification is by itself a challenge.

There are various methods/tools with support for modeling the NoC at different abstraction levels. A collection of these tools is necessary for the designer to create accurate system-level models. To our knowledge, there exists no established modeling process that can support modeling NoC from system specification to low-level designs. Of course, one can use programming languages with a semi-formal structure (Bricaud, 2012); however, the design process would be difficult. There is less support for validation and verification of semi-formal specifications developed using programming languages. Also, programming languages are less extensible for specifying models in multiresolution compared to formal specifications.

A similar problem exists even for frameworks supported by formal modeling approaches such as DEVS-based approaches. Existing IOS (input-output system) DEVS-based modeling frameworks do not provide the basis for applying both verification and validation techniques on models. There are many simulation engines created for DEVS models; a few of them are robust and being used. In our view, we believe the user should be able to develop models at different levels of abstraction, identify and categorize the similarity relationships between these models, use the similarity relationships to identify simulation scenarios for validation purposes, and finally constrain the DEVS models for verification.

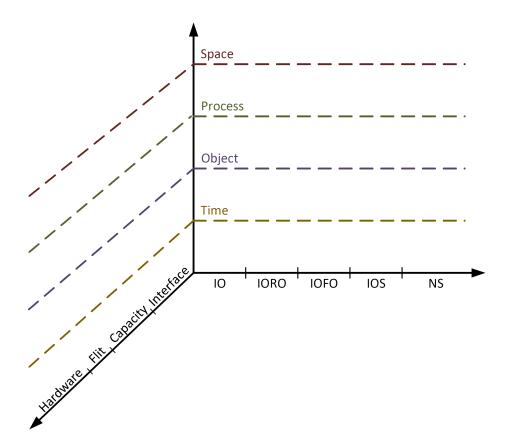

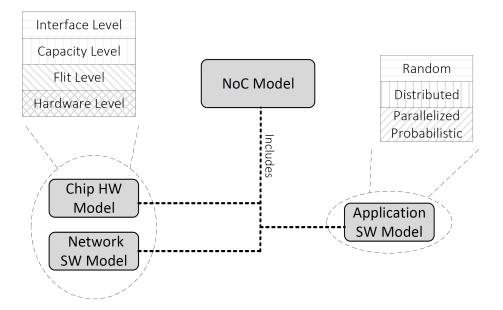

Figure 1.2 depicts a multidimensional space by which models of NoC can be categorized. The horizontal axis embodies the system specification hierarchy. This dimension captures the level by which the structure and behavior of models are specified. A model can be in one of the following five categories: input/output observation,

Figure 1.2: NoC Model Categorization Using 1) System Specification Hierarchy, 2) NoC Model Abstraction Levels, and 3) Multiresolution Dimensions

input/output relation observation, input/output function observation, input/output system, and network system (Zeigler *et al.*, 2000). The Input/Output Observation (IO) models only have input and output sets. IO Relation Observation (IORO) adds a set of relations between input and output sets. IO Function Observation (IOFO) replaces the relation set with a set of functions each from input segment  $\omega$  to a unique output segment  $\rho = f_i(\omega)$ . IO System adds a state set, time advance, and replaces the function set with a state transition and output functions. Finally, multi-component network system (NS) is made up of a set of IO systems connected through ports (influencers and influencees) (Zeigler *et al.*, 2000). The second axis captures NoC abstraction level using the four categories introduced in (Dally and Towles, 2004) as interface, capacity, flit, and hardware. Finally, resolution of the model is captured in the third axis and is identified by dimensions of resolution. Davis and Bigelow identify four dimensions necessary to identify the resolution of a model: Time, Object, Process, and Space (Davis and Bigelow, 1998). We use Figure 1.2 as our reference for NoC multiresolution modeling.

Since these models belong to a family of multiresolution models, evaluation of models (in the form of validation or verification) at one level of detail may influence the evaluation steps at other levels of detail. However, using the current ad-hoc approach, the similarity relationships between models at different levels of detail are not leveraged and therefore the validation or verification efforts are independent of each other. This independence leaves a lot of room for redundancy and human error. The desired modeling approach should enable the designer to substitute models of a design with models of higher or lower resolutions without disrupting the V&V analyses (simulation and model checking). The new model, in higher resolution may be different with respect to resolution of time, the functionality, models/couplings, or even data.

The paragraph above demonstrates the problems we have with current methods and tools for system design. The relationships between models at various resolutions are not well established. In addition, we do not reuse the evaluation efforts applied to one model cannot in the evaluation of another model in a higher or lower level of resolution. In a complete design process of a system, the designer may end up with a number of models without proper relationships between them specified in one or several tools/languages.

### 1.1.2 NoC V&V

NoC specifications are usually validated using simulation. Designers specify various scenarios with which they can evaluate the operations of models. One can control the simulation by changing a configuration file containing all the simulation parameters supported by that tool. Few tools offer limited support for NoC model checking which are for properties such as deadlock (Taktak *et al.*, 2008; Verbeek and Schmaltz, 2010). In case the designer requires verifying some aspects of a model, he/she can use one of these tools; however, new models may be created solely for model checking. These models are different from simulation models, although they are both describing the same system/phenomenon. The designer needs to convert the simulation model to a verification model or create a new verification model while considering the simulation model as reference. There are many challenges associated model conversion. Automated model conversion is limited. Although one can convert individual models from one specification to another, universal and automated model conversion for different modeling formalisms cannot be guaranteed. Manual conversion is also challenging as it suffers from human error and is not straightforward for incompatible modeling formalisms. Although the validation and verification techniques remain separate efforts for evaluating the correctness of models, it is still desirable to suggest a single modeling approach for both validation and verification and reduce the need for creating new models or converting one to another.

What we see as important in the landscape of NoC modeling approach is MRM support for both simulation and model checking. We aim at this goal by suggesting a formal specification in which models at different resolutions can be both verified and validated. However, validation using a simulation model is different from model checking of a verification model. To manage the differences, we intend to put restrictions on some aspects of the validation model and extend it to support verification. When validation is targeted, the restrictions are ignored and the extensions are not used. For verification, on the other hand, those restrictions and extensions are taken into consideration. We also intend to use the simulation protocol as a part of the model checking engine in order to stay consistent with the simulation engine. In addition, Experimental Frame (EF) as the method of experimentation in DEVS is reused in the verification protocol for property checking. It is important to be able to apply simulation or model checking to the NoC as a whole or to selective components. Both simulation and model checking can be applied to selective components of NoC. In addition to this, models used for model checking can be easily reconfigured to control the size of the state space which is explored.

### 1.1.3 Realization in a DEVS-Suite Tool

Various tools and M&S simulation environments exist for network system modeling, validation, and verification. Most of these tools operate at a certain level of abstraction and have capabilities for a subset of validation or verification methods. While Sections 1.1.1 and 1.1.2 introduce research problems concerning multiresolution modeling and NoC validation/verification, they discuss the theoretical aspects. Another research problem would be the development of these in a tool. Therefore, another important element of this research is the realization of a tool with capabilities for MRM and V&V for DEVS-NoC.

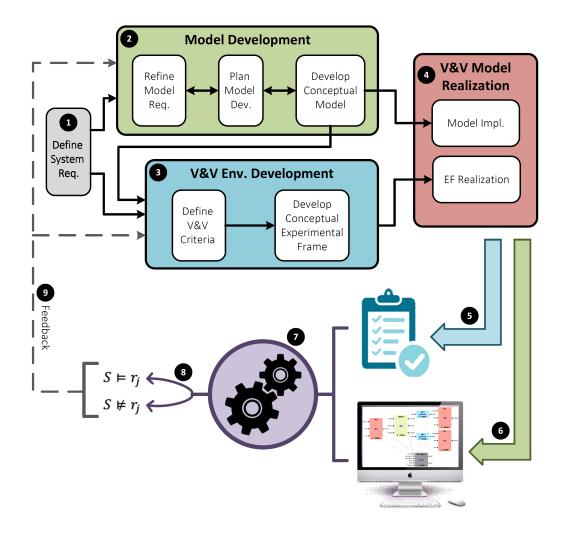

Figure 1.3, depicts various steps in the modeling, realization, and tool execution. The use of the tool is depicted in steps 5, 6, 7, and 8. The entire process starts with defining target system requirements is step 1. Using these requirements, one develops conceptual models (in step 2) and experimental frames (EF) for the properties of the system (in step 3). Characteristics of the model developed impacts how experi-

Figure 1.3: The Role of a Designated Tool in Model Development and V&V

mentation (in the form of simulation or model checking) is conducted; therefore, the conceptual model feeds into step 3 for EF development. During step 4, the model and EFs are implemented. In steps 5 and 6, these implementations are realized in the tool. The tools is responsible for executing the model (for either simulation or model checking) in step 7 and checking whether the model satisfies properties (deducted from requirements) in step 8. The result of this assessment is fed back into the model and V&V development in step 9.

As mentioned earlier, we incorporate DEVS for model and EF development. We

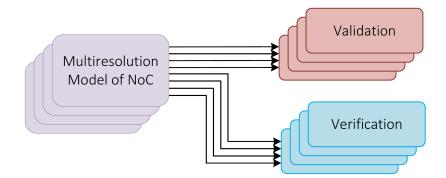

Figure 1.4: V&V in MRM-based for ESL Chip Design Phase

intend to extend DEVS-Suite (ACIMS, 2017) to support steps 5, 6, 7, and 8 shown in Figure 1.3

#### 1.2 Dissertation Goals and Scope

The needs mentioned in Section 1.1 motivated us toward developing an approach and a prototype tool for NoC modeling and simulation based on MRM and V&V capabilities. We do not claim that this approach completely fills the gap between highlevel requirements and RTL models. However, it provides a methodology by which one can create a family of related NoC models (using a formal modeling language) at various resolutions. These models can be validated using simulation scenarios or verified via model checking capabilities. We propose a unified approach toward property expression. Properties are expressed in DEVS language and developed as *Transducers* in the model. Transducers can be used in both simulation and model checking efforts for validation/verification of properties without any change.

Figure 1.4 depicts a high-level view of NoC ESL design phase. During the ESL phase, models of the NoC (at different resolutions) are developed and evaluated using validation or verification techniques. The results of these evaluations may be used again to refine the models. Multiresolution process starts with coarse-grain models of

NoC and gradually moves toward finer-grain models. We categorize models based on the categorization introduced in Figure 1.2. Based on the category of the model, one should apply a suitable set of evaluations. These evaluations may be in the form of simulation scenarios (validation) and model checking (verification). One the category of a model is known, simulation scenarios or verification properties of the models in the same category may be used to evaluate the model. This is our primary effort in MRM validation and verification.

Applying the same experiments to a model at a different resolution may not be as straightforward as above. Many aspects of the model may change in a fine-grain model such as the type of input data, the type of output data, and number of ports. A part of our effort in the MRM front is providing methods for reusing validation techniques in a family of multiresolution models.

- Definition 1 Application Software: is the software, which is executed on the intellectual properties. It is a single or a collection of tasks. If there are more than one task with dependencies between them, they use the network for the purpose of communication. A multi-tasked decoder application is an example of application software

- Definition 2 Network Software: is the communication software controlling the interactions among IPs in the network. This software makes low-level decisions on routing of flits and error handling. Components within a switch are examples of network software

- Definition 3 Hardware: is a physical entity within the NoC with simple functionality. Examples of hardware components are MUX or DEMUX. We usually avoid specifying these components except for very fine-grain models

Figure 1.5: NoC Pieces and Their Abstraction Levels

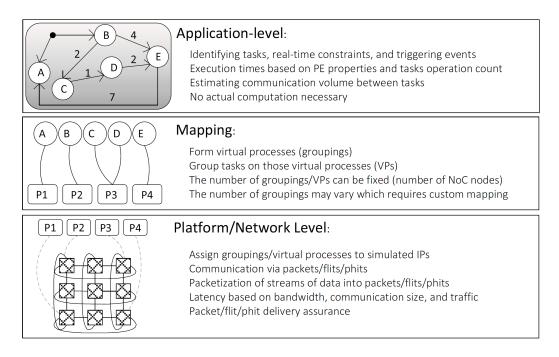

We categorize NoC it into 3 pieces: pure hardware, network software, and application software. These three pieces are defined in **Definition 1** to **Definition 3**. Based on the level of abstraction, the designer devises a model of application software and another for the hardware and network software. Figure 1.5 categorizes NoC model into the aforementioned three pieces and presents the abstraction levels for each of them. For application software model, we consider three levels of abstraction: random, distributed, and parallelized probabilistic (Butler, 1994). As for network software and chip hardware, we consider four levels of abstraction: interface, capacity, flit, and hardware (Dally and Towles, 2004). One can create numerous models by matching various abstractions of application software with those of hardware models and network software models. Each combination is useful in for certain design evaluations. The abstraction levels and methods of design evaluation will be discussed in detail later in this proposal.

Discrete EVent System Specification (DEVS) is chosen as the main modeling lan-

guage and DEVS-Suite (ACIMS, 2017; Kim *et al.*, 2009) as the modeling and execution tool. There are multiple reasons for choosing this pair (DEVS and DEVS-Suite) for this research. First, DEVS supports hierarchical and parallel modeling of systems which is particularly useful for complex systems. Second, a number of DEVS variants (with support for characteristics such as cellular, fuzzy, real-time) are proposed covering a wide range of systems. Third, while various formalisms are suggested on the modeling side, extended tool support for all these varieties of DEVS makes it a suitable choice for system modeling. Fourth, DEVS-Suite is an open-source, platform-independent tool for DEVS modeling and simulation. Finally, DEVS-Suite is enhanced with a variety of features such as animation, graphical trajectories, simulation view, and multiple addon libraries (for real-time M&S, activity modeling, EMF DEVS, and hardware modeling) makes DEVS-Suite an ideal choice as the modeling and execution tool.

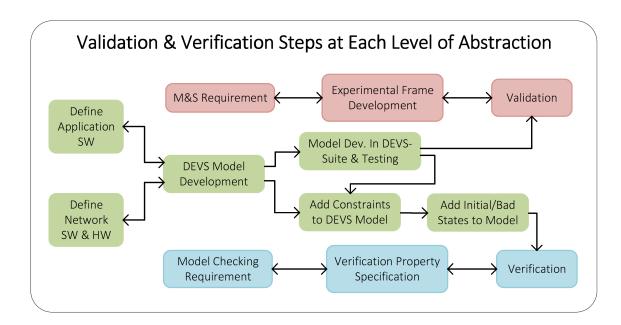

A more detailed view of the verification and validation analyses at each level of resolution is depicted as a block diagram in Figure 1.6. The process starts with the modeling of NoC. This is the hardware, the network software, and the application software. The designer specifies these models in the DEVS modeling formalism and develops them in the DEVS-Suite simulator. Parallel to this, based on the M&S requirements, experimental frames (EF) are devised containing a set of experiments and measurement tools within. Similarly, based on the model checking requirements, a verification engine containing a set of properties to be checked are developed. The validation step uses the DEVS model and the experimental frame (EF) in order to test the model against requirements. As for the verification step, the DEVS model is extended (to constrained variant of DEVS) in order to make model checking possible. The state space of the resulting model is exhaustively traversed for verifying the properties specified earlier.

Figure 1.6: Model Validation and Verification Processes at Each Abstraction Level

#### Chapter 2

### BACKGROUND

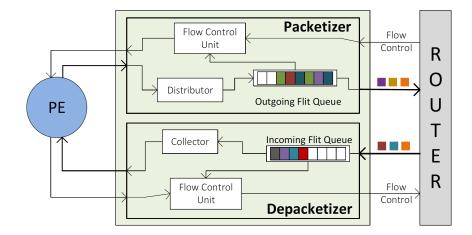

#### 2.1 Network-on-Chips

A Network-on-Chip (NoC) is a communication subsystem, which connects processing elements of a System-on-Chip (Hemani *et al.*, 2000). Communication and message passing between processing elements are packetized and sent over the network as flits or phits (Dally and Towles, 2004). Flits/phits are routed in the network using NoC routing schemes (oblivious or adaptive) to reach their destination (Rantala *et al.*, 2006). These flits are then assembled in the destination node and form the original message sent from the source node.

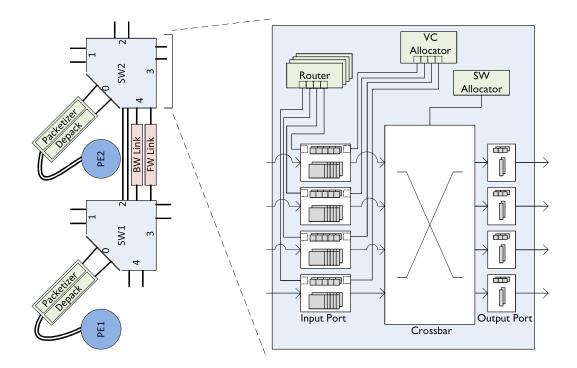

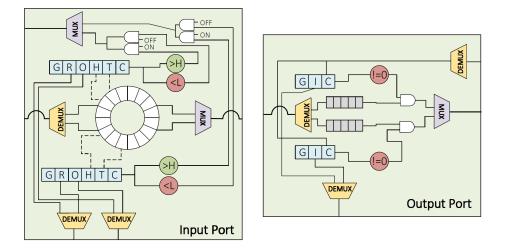

NoC models are developed in four levels of abstraction (Dally and Towles, 2004) as shown in Figure 2.1. At the highest level, the interface level, a highly abstracted specification of NoC is incorporated which models packet delivery, packet latency approximations, and network interface. At his level, decisions such as topology, delivery/retransmission policy, and number of nodes on the chip can be decided upon. The next level is capacity level in which new details such as buffer size, component latency, and error rate. At this level, the models are still lightweight. The next level is Flit level. This level is named after the unit of data, which is transferred between components. Since links in NoC are much smaller in bandwidth compared with largescale networks, real NoCs use flits, which are smaller pieces of data transferrable on those links. In addition to the change in the unit of data, the components within the switch component (such as buffers, crossbar, and allocators), more accurate timing and latency information based on clock cycles, and virtual channels are specified

Figure 2.1: Abstraction Levels for NoC Modeling and Simulation

within Flit level NoC models. Finally, in Hardware level, the components are modeled closer to hardware by adding area information. The latency and timing aspects of components are also specified in terms of physical time, which is more realistic. A common trend in abstraction levels of any system is that the finer-grain the model, the lower the speed of evaluation. Whether the evaluation is of type simulation or model checking, the process is more time consuming due to the number of events and the size of the state space.

### 2.1.1 Network-on-Chip Model Validation and Verification

Evaluation of NoC may be done using validation or verification techniques. Validation of NoC models using simulation is very common in the community. NoC frameworks provide modeling/simulation capabilities for various designs of NoC. These M&S environments enable designer/engineers to predict the performance and behavior before physical implementation. Verification techniques such as model checking may also be used for evaluating NoC models. Using model checking one can verify the correctness of certain important properties within the model such as deadlock freeness.

Evaluations via validation or verification greatly reduce the cost and time of developing new architectures. However, it is not always about developing new NoCs from scratch. In many cases, the designers change a few aspects of NoC as opposed to the entire system. These aspects may be routing schemes, flow control mechanisms, new buffers, links, flit sizes, bandwidths, etc. In these cases, NoC models at the right abstraction level can be used to evaluate the new aspect(s).

Existing NoC evaluation environments serve different purposes based on the abstraction level they support. NoC models specified at the Register Transfer Level (RTL) are closer to their physical realizations and therefore better for making RTLlevel design decisions. Coarse-grain models provide a higher-level abstraction of models and are useful for a different set of design decisions such as routing algorithm and flow control mechanism. As shown in Figure 2.1, fine-grain models provide greater insight in the details of the system; therefore, evaluations (whether in the form of model checking or simulation) of finer-grain models are more time consuming for comparable scenarios.

### 2.1.2 Deadlock in Network-on-Chips

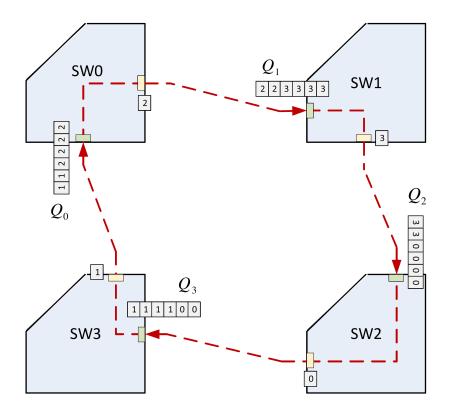

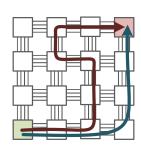

Deadlocks occur when a group of packets in an NoC are unable to progress toward destination while waiting indefinitely on resources. The deadlock condition is due to a circular dependency sequence among packets. Packets may be *waiting* for a resource or *holding* one. These are called *wait-for* and *holds* relations. Deadlock occurs when

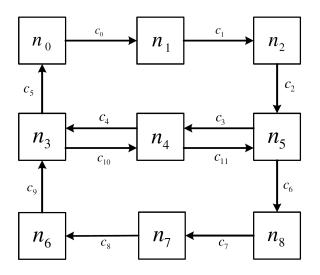

Figure 2.2: Deadlock Condition Implicating 4 Nodes

there is a loop in the resource *wait-for graph* (Dally and Towles, 2004). Without a proper deadlock recovery method, the packets in a deadlock scenario will never progress.

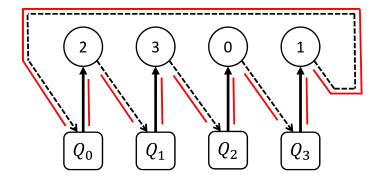

Figure 2.2 demonstrates a deadlock condition implicating four nodes. The input queues (FIFO) of each switch  $(Q_0, Q_1, Q_2, \text{ and } Q_3 \text{ respectively})$  are shown with the flits currently stored in them (the numbers are the destinations of the flits). Similarly, the output buffers (the output port of these switches are single-buffered) and what is stored in them are depicted. This is a deadlock case since no packet can proceed due to circular waiting. We prove this deadlock using the wait-for graph for the state of the network is depicted in Figure 2.3. Circles are agents (packets), squares are resources (input queues), solid lines are *hold* relationships (allocated), and dashed lines are *wait-for* relationships. As mentioned earlier, a cycle in the wait-for graph is

Figure 2.3: Wait-for Graph for the Network Shown in Figure 2.2

proof of a deadlock. The red dashed line in Figure 2.3 marks the cycle in this graph.

There are two methods for dealing with deadlock: 1) deadlock avoidance and 2) deadlock detection and recovery. In deadlock avoidance, one intends to design a network which is deadlock free. In this scenario the designer eliminates the possibility of deadlock occurrence by imposing restrictions on resource allocation. All avoidance methods introduce some sort of resource ordering to avoid forming cycles in the resource wait-for graph Dally and Towles (2004). In Deadlock detection and recovery, on the other hand, deadlocks may occur but the purpose is to detect and recover from them in an efficient manner. This may be more appealing to designers because of the excessive performance degradation of deadlock avoidance methods Dally and Towles (2004). Designers may choose not to impose many restrictions on the operation of the network but deal with deadlock cases if they occur during runtime to improve average-case performance.

Various methods for deadlock avoidance and detection/recovery are suggested. For deadlock avoidance, methods such as resource classes (such as distance or dateline) and restricted physical routes (such as dimension order routing and the turn model (Glass and Ni, 1992)) are used. As for deadlock recovery, *regressive* and *progressive* methods exist. Regressive methods break a deadlock cycle by dropping a number of flits. In order to reduce the cost of deadlock recovery, progressive methods resolve the deadlock situation without dropping flits. An example is the use of escape buffers in DISHA (Anjan and Pinkston, 1995).

### 2.2 Simulation and Validation

Validation aims at determining whether the model is an accurate representation of the real system/phenomenon. In other words, validation ensures that the right model is built while using verification techniques (Section 2.3) we verify whether the model is built right. There are various techniques by which models can be validated such as historical data validation, Turing tests, and predictive validation (Sargent, 2005). At the core of many of these approaches is a simulation model. Comparing the input/output relationships in the simulation model and the real system is the validation method using simulation (Naylor and Finger, 1967). A simulation model is an executable representation of a real system in a modeling framework. Some simulation models can be created in specialized tools such as BookSim (Dally and Towles, 2004), GEM5 (Binkert et al., 2011), Modelica (Modelica Association et al, 2017). Some others may be based upon mathematical formalisms such as DEVS, Timed Automata, and Markov Chains. While specialized tools provide fast and easy simulations with animation, they cannot be easily generalized for other uses. Models developed using mathematical formalisms, on the other hand, are very customizable and platform independent. Simulation models may also be of different types with respect to the way they handle time, compositions, and control. Examples are hybrid models, agent based models, discrete event specifications, and continuous time specifications. The choice between the type of simulation, the modeling framework, and the simulation tool is all on the shoulders of the modeler. To make an informed decision on the validation environment, the modeler should evaluate the tools modeling capabilities,

| Simulation Performance | Area         | Area requirements of the design                              |

|------------------------|--------------|--------------------------------------------------------------|

|                        | Frequency    | Minimum frequency to satisfy the application needs           |

|                        | Latency      | Average latency of delivering flits                          |

|                        | Power/energy | Average power usage w.r.t frequency                          |

|                        | Throughput   | Transfer capability in the network                           |

|                        | Runtime      | Application run-time                                         |

|                        | Utilization  | Utilization of the network capability                        |

| Modeling               | Elements     | Hardware components, network software, workload support      |

|                        | Abstractions | Levels of abstraction supported in modeling components       |

|                        | Co-design    | SW and HW are modeled together, co-simulated, and verified   |

|                        | MRM          | Supporting spatial, temporal, object, and process dimensions |

Table 2.1: Evaluation Measures for NoC Simulation Environments

the simulation types it supports, and validation mechanisms it possesses.

As an example, in this research the target system is NoC. This kind of system is commonly characterized to have discrete dynamics, even though it also has continuous dynamics. Therefore, discrete event simulation is a suitable choice for developing and validating NoC models. One may choose a NoC modeling and simulation tool by examining its support for modeling alternative, complementary kinds of atomic and composed NoC components. For example, support for modeling software (as a necessity toward HW/SW co-design) is an advantage. Detailed modeling and simulation tools exist that support actual brands of hardware, real software, and physical characteristic modeling capabilities (e.g. GEM5). Table 2.1 highlights some key metrics for system performance evaluation and complementary modeling support.

### 2.3 Model Checking

Formal model checking aims at exhaustively determining whether a model of a system meets certain requirements. Theorem-proving approaches for mathematically proving a certain property for a certain model is undecidable and generally restrictive (Halpern and Vardi, 1991). Therefore, exhaustive model checking is usually used for critical systems as a full-proof verification method. State explosion problem is a common issue when model checking is applied to a complex system (Burch *et al.*, 1990). However, the use of model checking method is not entirely abandoned. In particular, for safety critical systems, it is still necessary to explore the entire state space. Methods for tackling the state explosion problem are introduced by the community and will be discussed later in this proposal. In addition, model checking can benefit large-scale, complex systems by applying it selectively to some parts of the model. In this approach, the modeler can separately verify the operation of some components, which are vital to the correct operation of the system.

Model checking of hardware systems corresponds to the reachability graph as one can convert the state space to a directed graph with nodes corresponding to states and edges to transitions. Many formal modeling approaches such as Timed Automata (Alur and Dill, 1994) and Petri net (James, 1981) can be verified exhaustively as they correspond to a finite state machine. As for DEVS, because of the continuity of time (for external inputs) and boundless state variables, the state space is unlimited. DEVS-based models, as normally specified, are well suited for simulation purposes. However, model checking algorithms require bounded state space in order to iterate all possible states and transitions.

The general DEVS formalism does not put any constraints on the range of values any of its state variables can have which results in unbounded state space. Unbounded state values are one of the reasons why the DEVS formalism does not lend itself to model checking. Even if the state values are finite, the total state Q is infinite i.e., input events can arrive at any instance of time. Furthermore, there are no restrictions on the input and output values for both atomic and coupled models.

However, constrained versions of DEVS are introduced to address this issue. There has been previous efforts such as FD-DEVS (Hwang and Zeigler, 2009) for supporting model checking. Although this approach is promising, there are two major shortcomings associated with it that we are trying to address. These two shortcomings are discussed below.

# 2.3.1 Support for Non-determinism and Stochasticity

DEVS formalism has comprehensive support for both deterministic and nondeterministic systems. In a non-deterministic model, several transitions could be possible for a set of internal/external events. Non-determinism adds a large number of possibilities to the state space, which could lead to the state explosion problem (Valmari, 1998). FD-DEVS is developed to address this problem. Predictability of deterministic systems is significant towards verification via model checking. Similar to non-determinism, stochasticity is another obstacle toward model checking. In Parallel DEVS (P-DEVS), internal and external transition functions are deterministic. However, non-determinism exists for external inputs. External inputs may be injected at any instance of time. This is the most obvious form of non-determinism in DEVS.

The randomness for choosing one transition among many, as defined in Finite Probabilistic DEVS (FP-DEVS), can also increase the state space of a model. One can reduce the stochasticity of the system by removing randomness. For example, consider a variation of Petri net (James, 1981) in which the firing of a transition is based on a random variable (Ciardo *et al.*, 1989; Marsan and Chiola, 1986). Compare this, with another variation in which a firing must take place if a transition is enabled such as deterministic timed Petri net (Marsan and Chiola, 1986). For the stochastic Petri net, any event can happen at any instance of time. It is decidable to solve reachability problems for both forms of Petri nets and they are both EXPSPACE hard (Mayr, 1984). However, the deterministic one possesses a much smaller state space. The smaller the state space, the less space it takes to verify the model and the faster it can be carried out.

### 2.3.2 Limited Property Checking Capability

Models are verified against properties that are defined by some reference model. In most model checking environments, a formal language encodes these properties such as Timed Computation Tree Logic (Alur *et al.*, 1993) in UPPAAL (Larsen *et al.*, 1997) or DEVS Natural Language (DNL) in MS4 Me (Seo *et al.*, 2013). Inventing a language or using a mathematical format are common ways for encoding properties. However, these methods have their own limitations. It can be challenging to encode a complex property in these formal languages. As an example, encoding the reachability problem, may not be so difficult as it deals with the collective state of the system which is already formally modeled. However, what if one needs to verify whether all flits in a Network-on-a-Chip can be delivered within some time window (satisfying a predefined QoS)? Or what if one needs to ensure whether all traffic is distributed fairly within the network and the load on one link (or a set of links) never exceeds a pre-determined threshold (to avoid overheating)? In these cases, formal languages such as DNL and LTL are helpless.

As mentioned earlier, Marculescu *et al.* categorize research issues in four major groups. In the 4th category, the authors briefly explore NoC verification and point out that this field has received less attention compared with other 3 major categories (Marculescu *et al.*, 2009). There have been many works in this area, which mostly verify properties such as packet delivery and deadlock/livelock freedom. Although verification capability for packet delivery and deadlock/livelock is very useful, it is also limited considering the expected functionality of NoC. It would be helpful if one could perform model checking to verify the operation of the model for other properties such as worst-case flit latency and packet/flit loss ratio.

## 2.4 Multiresolution Modeling

Multi-resolution modeling (Davis and Bigelow, 1998) is used in various field of research such as graphics (Garland, 1999) and defense systems (Davis and Bigelow, 1998). The challenges associated with MRM have been recognized for many years and application domains (Davis and Tolk, 2007; Yilmaz *et al.*, 2007). MRM is concerned with gradual progression from low-resolution to high-resolution models where the elements of the system withstand appropriate details as measured by the modeling tasks. We can observe that lower-level resolution models are suited for verification using model checking while higher-level resolution models are suited for validation using simulation. Therefore, verification and simulation offer unique, complementary capabilities for designing systems.

Currently, there is no universally accepted definition for multi-resolution as different categorizations of system resolutions exist (Baohong, 2007). Each of these definitions/categorizations may be consistent with a set of systems. However, in this work, we are focusing on a class of systems (i.e., Network-on-Chip) which allows us to be specific and use domain knowledge to define a fitting multi-resolution model for NoC.

Davis and Bigelow recognize 4 dimensions to resolution: object, temporal, process, and spatial. The object dimension relates to the fragmenting components (atomic models to coupled models). By increasing object resolution, the number of components in the model increase and the functionality of each component becomes more detailed. The temporal resolution deals with the granularity of time. The higher the temporal resolution is the more fine grain the time is. The functionality of a component may change without changing object or temporal aspects. This is handled by process resolution, which directly deals with the functionality of each model. Finally, the physical aspects of the model (considering it is modeling a physical entity) are covered by spatial resolution. One important point to note is that no MRM frameworks have been proposed for NoC and System-on-Chips (Berekovic *et al.*, 2002). Without such a framework, it is difficult to classify what could be highest or lowest resolution models (Catania *et al.*, 2016). While one aspect of resolution (such as object, process, time, or space) of a model may be increasing, another aspect may be declining (Davis and Bigelow, 1998). The power of MRM lies in defining levels of model abstractions and more significantly how models that have different levels of resolution can be related based on their differences.

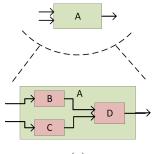

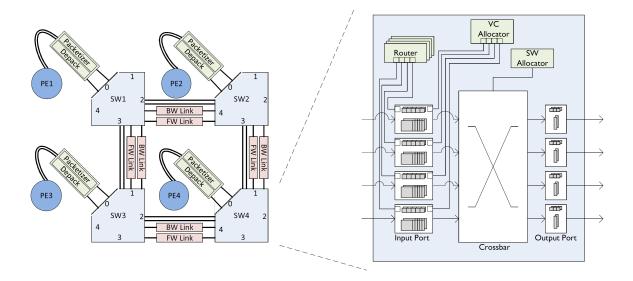

For modeling NoC in this research, we focus on the first three dimensions of resolution: object, temporal, and process. In the context of NoC, object dimension relates to the number of atomic models defining a certain component of the system. For example, the switch element can be modeled as an atomic model or as a coupled model with internal components (buffers, crossbar, routers, etc.). This is shown in Figure 2.4. The switch on the right hand side of this figure is clearly in higher resolution with respect to object dimension. While object resolution is only concerned with the components and couplings, the method/algorithm by which a component completes its task relates to process resolution. An example for this could be the routing algorithm in the switch. A simple algorithm can be X-Y routing in which the flit always takes a deterministic path toward destination. A more complex routing

Figure 2.4: Increasing Object Resolution for the Switch Component

could be an adaptive routing algorithm, which considers the traffic while forwarding flits through the network. The second routing algorithm clearly has higher resolution compared to the first one with respect to process dimension. Finally, the temporal dimension relates to the granularity of the clock signal for the model of NoC.

## 2.5 Homomorphic Mapping

A system can be modeled in number of different ways with respect to modeling method, abstraction level, and methodology. One obvious way of having a number of models for one system is modeling at different levels of abstraction. This can be accomplished with MRM. As explained earlier, a family of models are developed each of which specifying the system at a certain resolution. In these cases, one or more of the object, temporal, process, or spatial aspects of resolution changes which makes one model finer-grained as the other. However, two models may still appear different even if they are modeled at the same level of resolution and have identical functionality. These models may appear different with respect to interface and state space but are still identical. A formal basis for capturing these forms of similarities is very useful. There are three forms of similarity relationships: homomorphism, isomorphism, and copies. These concepts are defined in **Definition 4** to **Definition 6**.

- **Definition 4** Homomorphism: a relationship between two atomic models when one model is a simplification or elaboration of the other one

- **Definition 5** Isomorphism: a relationship between two atomic models when two models are essentially the same (have the same functionality) but may have a different interface or notation

- **Definition 6** Copies: a relationship between two atomic models when two models are identical with respect to interface and functionality

Similarity modeling in the form of homomorphism, isomorphism, and copies are formulated for discrete (-time) systems. A discrete time atomic model is defined as follows (Wymore, 1993):

$$Z = \langle SZ, IZ, OZ, NZ, RZ \rangle$$

In this definition, SZ is the state set, IZ the input set, and OZ is the output set. The set NZ specifies the next state function. NZ is a function from state set and input set to the state set  $(NZ : (SZ \times IZ) \rightarrow SZ)$ . RZ Is the output (readout) function, which is a function from state to output set  $(RZ : SZ \rightarrow OZ)$ . Time is implicit in the definition of discrete systems. After each tick of the clock, the next state and output functions operate based on the current state and the input set.

Figure 2.5: Two Isomorphic Models with Different Structures

Homomorphic mapping establishes similarity relationships between atomic discretetime models by finding a mapping between all these 5 sets. Time is not directly taken into consideration since it is implicitly defined.

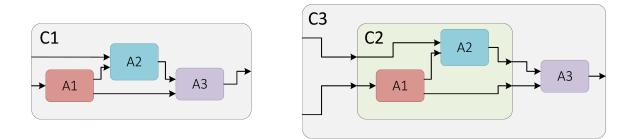

The interesting point here is that two models at different resolutions may be homomorphic, isomorphic, or none of the above. For example, models C1 and C3 in Figure 2.5 are isomorphic although they look very different structurally. C3 has an extra level of hierarchy, which changes the structure of the model though the functionality stays the same. At the heart of both models, are identical atomic models A1, A2, and A3, which result in identical functionalities. Therefore, although these models are different, they are isomorphic. So, if two models are only different with respect to object resolution (and nothing else), we can assume there is an isomorphic relationship between the two. The same thing applies to changes in temporal resolution. In the case of process resolution changes, the other model may end up being homomorphic, isomorphic, or not similar to the original model. Complex cases occur when two or more of resolution dimensions change. For those cases, we require a formal approach toward proving homomorphic or isomorphic relationships.

However, one might ask what the benefits of identifying these similarity relationships are. This could impact the validation and verification activities. If we have two models of a component at two levels of resolution and we prove that the two models are isomorphic, one can apply the same validation experiments to both models with no change. Similarly, if the two models are homomorphic, all validation experiments of the coarser-grain model can be applied to the finer-grain model. These similarity relationships enable us to reuse validation activities across different resolutions.

As mentioned in the definitions above, homomorphism relationship is defined between atomic models (Zeigler *et al.*, 2000). However, there has not been any previous work on modeling homomorphism between coupled/atomic models. One of our challenges is formulating a method for homomorphic mapping among coupled models.

### Chapter 3

# RELATED WORK

Network-on-chip is the central topic of this research. However, NoC design and implementation contains many research fields on structural aspects (such as topology), behavioral aspects (routing or flow control mechanisms), and physical aspects (hardware brand, area information). So many research questions are formulated based on these aspects of NoC (Marculescu *et al.*, 2009). In this research, we focus on multiresolution NoC modeling and V&V of NoC models. Our modeling approach is only limited to discrete event system specification (DEVS). In this section, we first review previous works on NoC verification and validation in Section 3.1. In Section 3.2 we focus on model checking and discuss various modeling methods proposed with support for model checking. Considering the fact that model checking capability should be developed on top of DEVS, we discuss DEVS-based model checking approaches in this section as well. Multiresolution modeling, as the next central subject of this research, is reviewed in Section 3.3.

### 3.1 Network-on-Chip Validation and Verification