# Methodical Design Approaches to Multiple Node Collection Robustness for Flip-Flop

Soft Error Mitigation

by

Sandeep Shambhulingaiah

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved May 2015 by the Graduate Supervisory Committee:

Lawrence Clark, Chair Keith Holbert Jae-sun Seo David Allee

ARIZONA STATE UNIVERSITY

May 2015

### ABSTRACT

The space environment comprises cosmic ray particles, heavy ions and high energy electrons and protons. Microelectronic circuits used in space applications such as satellites and space stations are prone to upsets induced by these particles. With transistor dimensions shrinking due to continued scaling, terrestrial integrated circuits are also increasingly susceptible to radiation upsets. Hence radiation hardening is a requirement for microelectronic circuits used in both space and terrestrial applications.

This work begins by exploring the different radiation hardened flip-flops that have been proposed in the literature and classifies them based on the different hardening techniques.

A reduced power delay element for the temporal hardening of sequential digital circuits is presented. The delay element single event transient tolerance is demonstrated by simulations using it in a radiation hardened by design master slave flip-flop (FF). Using the proposed delay element saves up to 25% total FF power at 50% activity factor. The delay element is used in the implementation of an 8-bit, 8051 designed in the TSMC 130 nm bulk CMOS.

A single impinging ionizing radiation particle is increasingly likely to upset multiple circuit nodes and produce logic transients that contribute to the soft error rate in most modern scaled process technologies. The design of flip-flops is made more difficult with increasing multi-node charge collection, which requires that charge storage and other sensitive nodes be separated so that one impinging radiation particle does not affect redundant nodes simultaneously. We describe a correct-by-construction design methodology to determine a-priori which hardened FF nodes must be separated, as well as a general interleaving scheme to achieve this separation. We apply the methodology to radiation hardened flip-flops and demonstrate optimal circuit physical organization for protection against multi-node charge collection.

Finally, the methodology is utilized to provide critical node separation for a new hardened flip-flop design that reduces the power and area by 31% and 35% respectively compared to a temporal FF with similar hardness. The hardness is verified and compared to other published designs via the proposed systematic simulation approach that comprehends multiple node charge collection and tests resiliency to upsets at all internal and input nodes. Comparison of the hardness, as measured by estimated upset crosssection, is made to other published designs. Additionally, the importance of specific circuit design aspects to achieving hardness is shown.

# DEDICATION

To my parents Shambhulingaiah Madaiah and Sujatha Gubbiyappa and my brother Yogesh Shambhulingaiah, for their love, encouragement and support.

## ACKNOWLEDGMENTS

I would like to thank Prof. Lawrence Clark for giving me an opportunity to work in his lab and for being my advisor. Under his mentorship, my knowledge on digital circuit design got broadened and I was able to improve my problem solving skills which eventually helped me get a job.

I would like to thank Prof. Keith Holbert, Prof. David Allee and Prof. Jae-sun Seo for being on my Ph.D committee.

Finally I would like to thank my previous and current lab mates Nathan Hindman, Jerin Xavier, Vinay Vashishtha, Chandarasekaran Ramamurthy, Srivatsan Chellappa, Sushil Kumar, Christopher Leib and Yitao Chen for their help in my research work.

# TABLE OF CONTENTS

| Page                                            |

|-------------------------------------------------|

| LIST OF TABLES                                  |

| LIST OF FIGURES xi                              |

| CHAPTER                                         |

| 1 INTRODUCTION                                  |

| 1.1 Radiation Environment                       |

| 1.1.1 Trapped Particles1                        |

| 1.1.2 Transient Particles                       |

| 1.1.3 Secondary Particles                       |

| 1.1.4 Radiation Effects in Devices              |

| 1.1.5 Single Event Effects                      |

| 1.1.6 Destructive and Non-Destructive SEEs      |

| 1.2 Radiation hardening                         |

| 1.2.1 Process Mitigation Techniques             |

| 1.2.2 Design Mitigation Techniques16            |

| 1.3 Thesis contribution and organization        |

| 2 RADIATION HARDENED FLIP-FLOPS                 |

| 2.1 Radiation Hardened Flip-Flop Classification |

| 2.2 Redundant Non Self Correcting FFs           |

| CHAPTER | Page                                                             |

|---------|------------------------------------------------------------------|

| 2.2.1   | Built In Soft Error Resilience FF                                |

| 2.2.2   | Bi-stable Cross-Coupled Dual Modular Redundancy FF               |

| 2.2.3   | Bi-stable Cross-Coupled Dual Modular Redundancy FF with Adaptive |

| Coupli  | ng                                                               |

| 2.3 R   | edundant Self Correcting FFs                                     |

| 2.3.1   | Redundant Self Correcting C-Element Based FFs                    |

| 2.3.2   | Redundant Self Correcting DICE Based FFs                         |

| 2.3.3   | Triple Mode Redundant FF                                         |

| 2.4 T   | emporal FFs                                                      |

| 2.4.1   | Four Delay Element FF                                            |

| 2.4.2   | Temporal Latch Incorporating Majority Gate                       |

| 2.4.3   | Temporal FF Incorporating DICE Latch                             |

| 2.4.4   | DF-DICE Latch                                                    |

| 2.5 S   | ummary                                                           |

| 3 TEMP  | ORAL SEQUENTIAL LOGIC HARDENING BY DESIGN WITH A LOW             |

| POWE    | ER DELAY ELEMENT                                                 |

| 3.1 D   | Delay Element Possibilities                                      |

| 3.1.1   | Effect of Transistor Drive Strength on SET Duration              |

| CHAPTER | Pag                                                                    | ze |

|---------|------------------------------------------------------------------------|----|

| 3.1.3   | Stacked Transistors Cascaded Inverter Based Delay Element              | 50 |

| 3.1.4   | Voltage Controlled (Current Starved) Cascaded Inverter Delay Element 5 | 51 |

| 3.1.5   | Delay Elements Comparison                                              | 52 |

| 3.2 Pr  | oposed Delay Element                                                   | 54 |

| 3.2.1   | Circuit Design                                                         | 55 |

| 3.2.2   | Power Reduction                                                        | 55 |

| 3.2.3   | SET Tolerance                                                          | 56 |

| 3.3 De  | elay Element Impact on a temporal Flip-Flop5                           | 58 |

| 3.4 Fl  | ip-flop SET Tolerance5                                                 | 59 |

| 3.5 Fl  | ip-flop layout6                                                        | 50 |

| 3.5.1   | Power Comparison                                                       | 51 |

| 3.6 80  | 051 Implementations                                                    | 52 |

| 3.6.1   | Synthesis                                                              | 52 |

| 3.6.2   | Auto Place and Route (APR)                                             | 52 |

| 3.6.3   | Layout                                                                 | 53 |

| 3.6.4   | Comparison                                                             | 54 |

| 4 METHO | ODOLOGY TO OPTIMIZE CRITICAL NODE SEPARATION IN                        |    |

| HARDI   | ENED FLIP-FLOPS6                                                       | 57 |

| 4.1 M   | ultiple Node Charge Collection6                                        | 57 |

| CHAPTER | Ι                                                        | Page |

|---------|----------------------------------------------------------|------|

| 4.1.1   | Experimental Analysis                                    | 68   |

| 4.1.2   | MNCC Impact on FFs                                       | 69   |

| 4.2 C   | ritical Node Separation Methodology                      | 70   |

| 4.2.1   | Interleaving Circuit Blocks to Avoid MNCC                | 70   |

| 4.2.2   | SET Upset Simulation                                     | 70   |

| 4.2.3   | Simulation Based MNCC Collection Analysis                | 71   |

| 4.2.4   | Node Group Ordering                                      | 78   |

| 4.3 A   | pplication to Radiation Hardened FF Designs              | 78   |

| 4.3.1   | DICE Protected Master Slave FF                           | 79   |

| 4.3.2   | Majority Voter Based Temporal FF                         | 80   |

| 4.3.3   | Area Efficient C-Element Based Temporal FF               | 82   |

| 4.4 In  | nproved Matrix Representation                            | 84   |

| 4.5 N   | on Rectangular Vertical Cell Interleaving                | 85   |

| 4.5.1   | Vertically Interleaved Cell Layout and APR Compatibility | 85   |

| 5 A RED | UCED POWER AND AREA FLIP-FLOP WITH HIGH SOFT ERROR       |      |

| IMMU    | NITY                                                     | 88   |

| 5.1 Pr  | roposed Hardened Flip-Flop                               | 88   |

| 5.1.1   | Hardened FF Circuit Approach                             | 88   |

| 5.1.2   | Design Details                                           | 90   |

| CHAPTER | R                                   | Page |

|---------|-------------------------------------|------|

| 5.2 H   | FF Hardness Verification and Layout |      |

| 5.2.1   | Node Grouping Heuristics            |      |

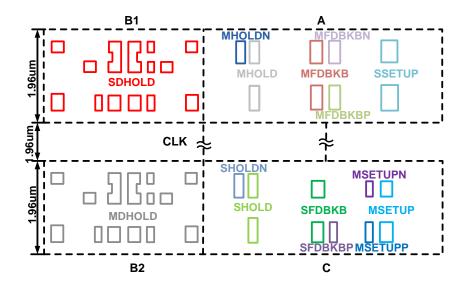

| 5.2.2   | FF Layout and APR Compatibility     | 96   |

| 5.3 I   | Hardness Comparison                 |      |

| 5.3.1   | BISER FF                            |      |

| 5.3.2   | Split Internal Node (SIN) FF        | 101  |

| 5.3.3   | Cross-Section Comparison            | 102  |

| 6 CONC  | CLUSIONS                            | 107  |

| REFEREN | ICES                                | 110  |

# LIST OF TABLES

| Table |                                                           | Page |

|-------|-----------------------------------------------------------|------|

| 1.1   | Various Sub Categories of Single Event Effects            | 13   |

| 2.1   | Delay Elements Area and Energy/Cloock Cycle Comparison    | 54   |

| 3.1   | Standard Cells Areas for both Temporal Designs            | 65   |

| 3.2   | Comparison of Area, Timing and Clock Frequency            | 66   |

| 5.1   | Cross-Section Reductions of FFs in Clocked and Hold Modes | 106  |

# LIST OF FIGURES

| Figure | J                                                                              | Page |

|--------|--------------------------------------------------------------------------------|------|

| 1.1    | Particles in the Space Radiation Environment                                   | 2    |

| 1.2    | Illustration of the Terrestrial Cosmic Ray Shower caused by the Interaction of |      |

|        | Galactic Cosmic Rays With the Earth's Atmosphere                               | 5    |

| 1.3    | A Schematic of a Reverse-Biased n+/p Junction Struck by an Ion                 | 8    |

| 1.4    | Ionizing Radiation Induced Charge Collection at a Combinational Circuit        |      |

|        | Generating SET and on a Latch Circuit Causing a SEU                            | 11   |

| 1.5    | MNCC Effect on SRAMs in 90 nm Process                                          | 13   |

| 1.6    | Cross-Section of an SOI Transistor                                             | 14   |

| 1.7    | Resistively Hardened SRAM Schematic                                            | 16   |

| 1.8    | Triple Modular Redundancy                                                      | 17   |

| 1.9    | Majority Gate Schematic                                                        | 18   |

| 1.10   | DICE Latch Schematic                                                           | 18   |

| 1.11   | Temporally Hardened Circuit                                                    | 19   |

| 1.12   | Combination of C-Element and Inverter Chain Delay Element to Filter Incom      | ning |

|        | SETs                                                                           | 19   |

| 2.1    | BISER FF Schematic                                                             | 24   |

| 2.2    | Bi-Stable Cross-Coupled Dual Modular Redundancy FF Schematic                   | 25   |

| 2.3    | BCDMR-ACFF and AC Flip-Flop Schematics                                         | 27   |

| 2.4    | C-Element Based Latch Schematic                                                | 29   |

| 2.5    | Soft Error Hardened Latch Schematic                                            | 31   |

| 2.6    | Schmitt Trigger Based Latch Schematic                                          | 32   |

| Figure | Page                                                                          |

|--------|-------------------------------------------------------------------------------|

| 2.7    | Split Internal Node Latch Schematic                                           |

| 2.8    | Ten Transistor Hardened Latch Schematic                                       |

| 2.9    | Soft Error Tolerant Static D Latch Schematic                                  |

| 2.10   | Triple Mode Redundant FF Schematic                                            |

| 2.11   | Temporal FF Schematic                                                         |

| 2.12   | Temporal Latch Empoying Majority Gate40                                       |

| 2.13   | Temporal FF Schematic Incorporating DICE Latch                                |

| 2.14   | DF-DICE Latch Schematic                                                       |

| 2.15   | Venn Diagram Representation of FF Classification44                            |

| 3.1    | Measured SETs With Temporal Latches using Current Starved Inverters           |

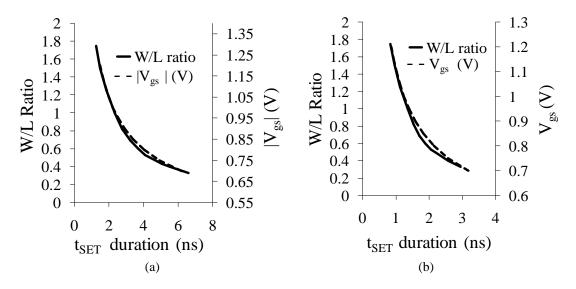

| 3.2    | The Variation of SET Duration as the Function of Drive Strength and Gate Bias |

|        | for a PMOS Transistor and NMOS Transistor                                     |

| 3.3    | Cascaded Inverter Based Delay Element and its Variant which has Additional    |

|        | Capacitance at the Intermittent Nodes                                         |

| 3.4    | Two Transistor Stacked Cascaded Delay Element                                 |

| 3.5    | Voltage Controlled Cascaded Inverter Delay Element                            |

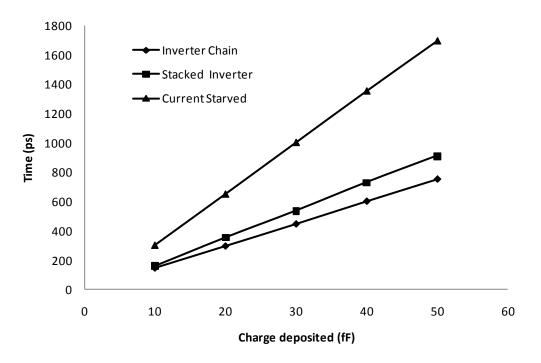

| 3.6    | Comparison of T <sub>SET</sub> durations for the Three Delay Elements         |

| 3.7    | Proposed Delay Elements; its Variant; and Without Dual Redundancy             |

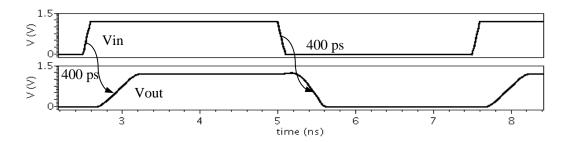

| 3.8    | The Proposed Delay Element Transient Response Producing a Delay of 400 ps 55  |

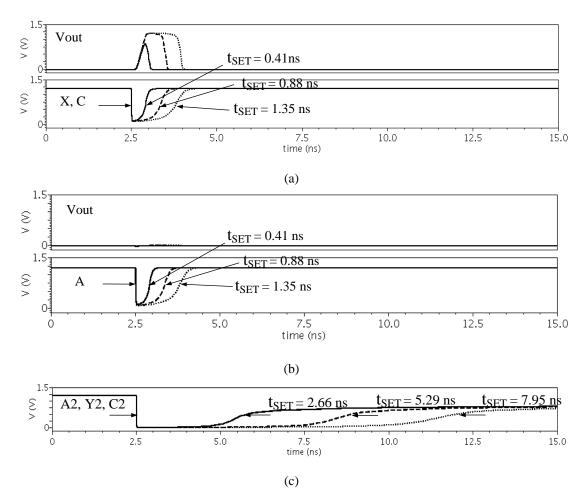

| 3.9    | Effect on Delay Element Output Due to Simulated SETs of Various LET           |

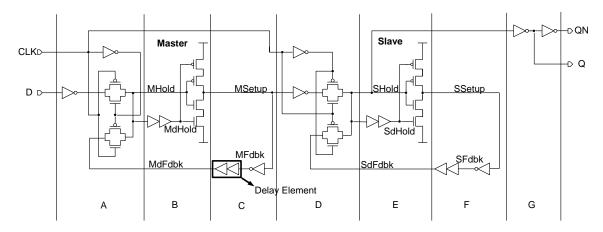

| 3.10   | Temporal FF Schematic Using the Proposed Delay Element                        |

| 3.11 | Waveforms Showing the Effect of Two Radiation Hits on the MSFF Using the     |  |

|------|------------------------------------------------------------------------------|--|

|      | Proposed Delay Element and one Lacking Redundant Paths at the Low-Voltage    |  |

|      | Swing, Current Starved Nodes                                                 |  |

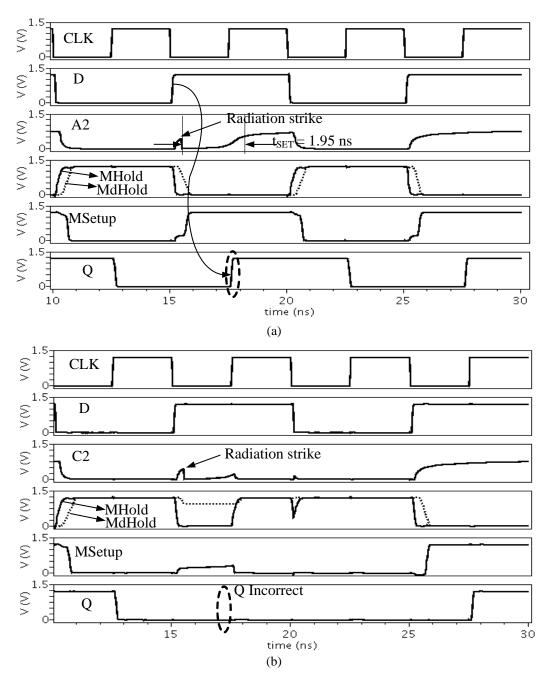

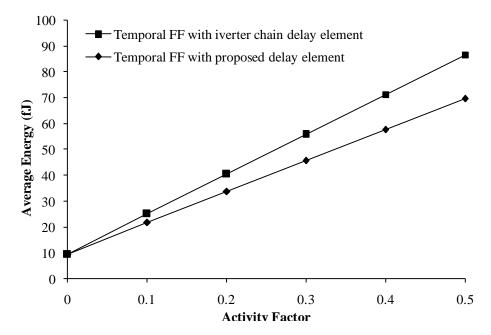

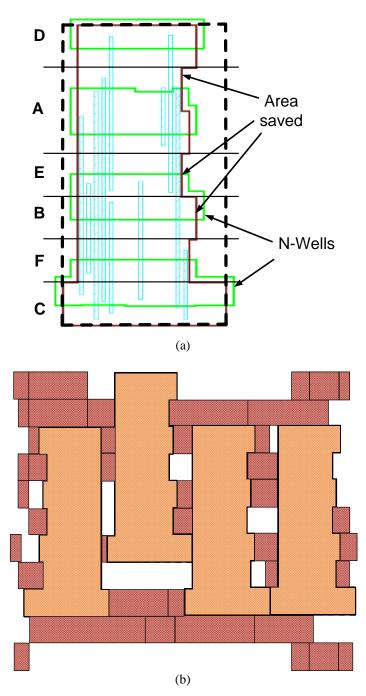

| 3.12 | Layout Arrangement Illustrating the Constituent Cell Interleaving60          |  |

| 3.13 | Comparison of Average Energy Consumption Per Clock Cycle of the MSFF         |  |

|      | Using Both the Inverter Chain and the Proposed Delay Element                 |  |

| 3.14 | 8051 Layouts of the Two Temporal Versions63                                  |  |

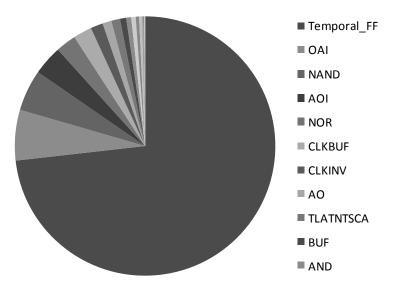

| 3.15 | Standard Cells Areas in Both Temporal Designs64                              |  |

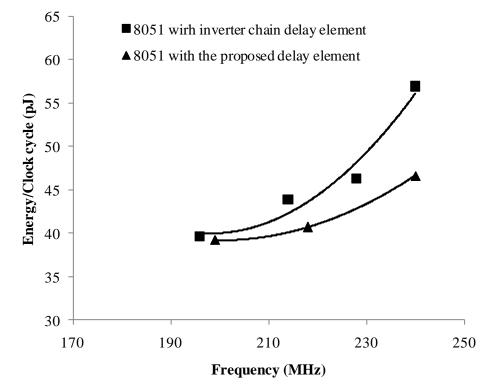

| 3.16 | Average Energy/Clock vs. Maximum Operating Frequency for the Two 8051        |  |

|      | Implementations                                                              |  |

| 4.1  | Experimentally Measured SRAM Multiple Node Upset Extents in the Horizontal   |  |

|      | and Vertical Directions                                                      |  |

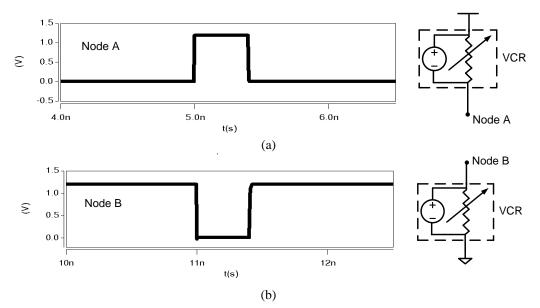

| 4.2  | Voltage Controlled Resistor Induced High and Low SETs on the Circuit Nodes71 |  |

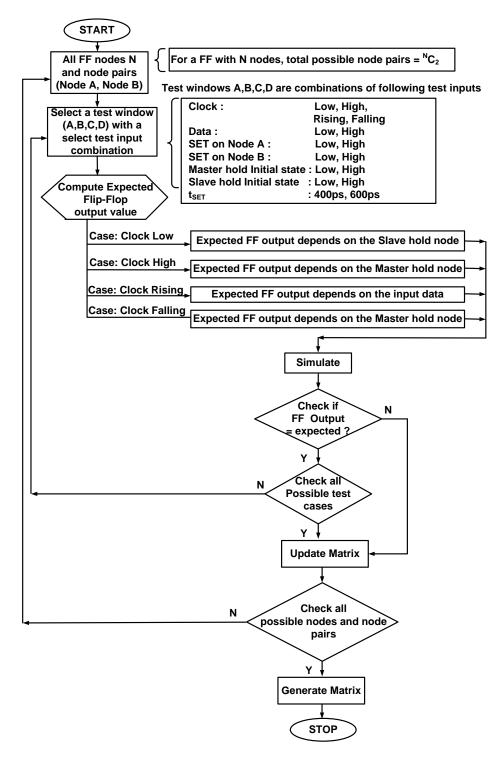

| 4.3  | Flowchart Illustrating the Methodology                                       |  |

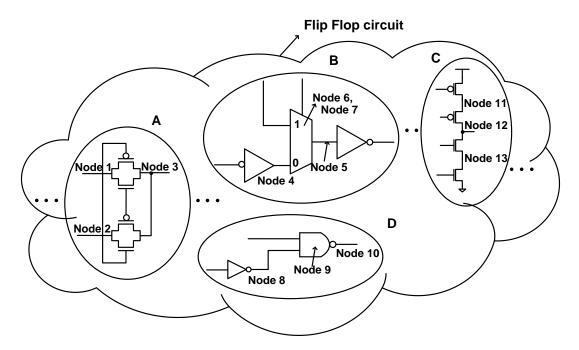

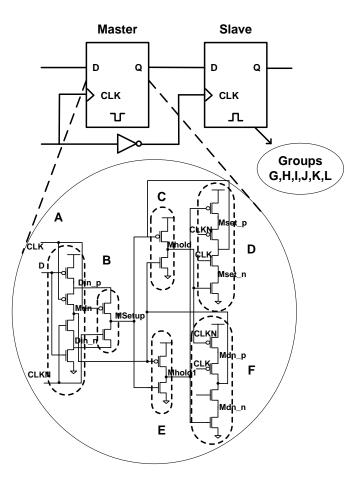

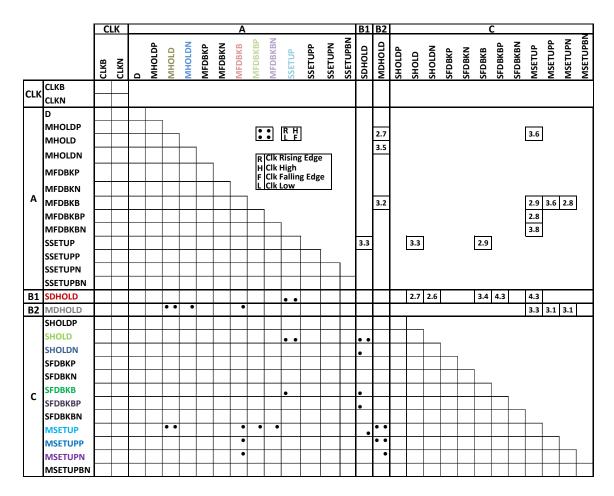

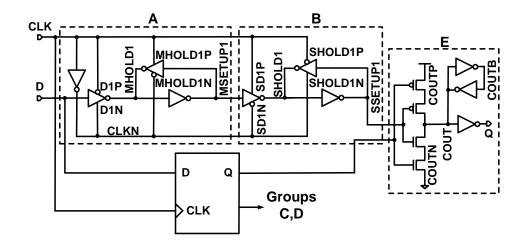

| 4.4  | Circuit Node Grouping in a Hardened FF73                                     |  |

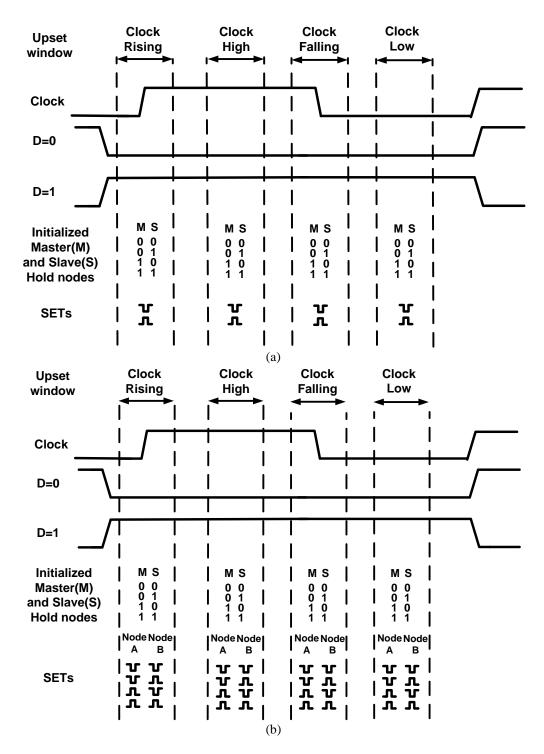

| 4.5  | SET Simulations on all FF Nodes and Node Pairs at Windows A, B, C and D for  |  |

|      | Both Data Inputs75                                                           |  |

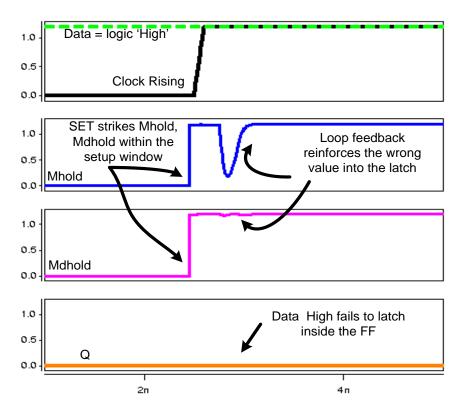

| 4.6  | Waveforms Showing Data Failing to Capture the Correct Value when Two High    |  |

|      | SETs76                                                                       |  |

| 4.7  | Node Matrix Showing Failing Node Pairs Marked in Black and the Passing Node  |  |

|      | Pairs Marked in Grey77                                                       |  |

| 4.8  | DICE FF Schematic and Node Grouping79                                        |  |

| 4.9  | Matrix Showing the Response of the DICE FF after MNCC Simulations With        |  |

|------|-------------------------------------------------------------------------------|--|

|      | SETs Induced Only at Clock High and Low                                       |  |

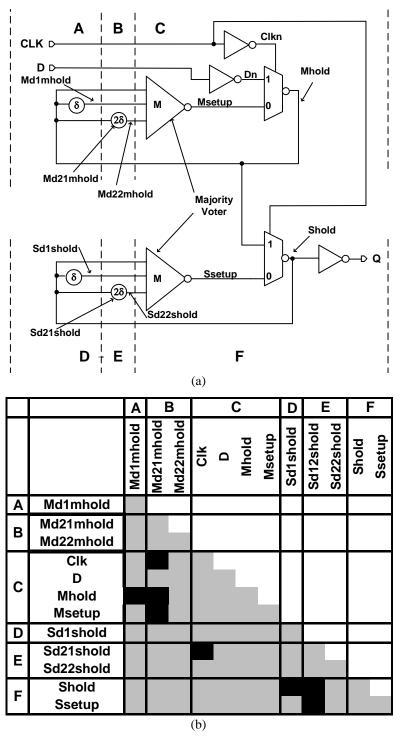

| 4.10 | Temporal FF With Majority Voting Schematic and the Node Matrix Obtained       |  |

|      | after SET Simulations81                                                       |  |

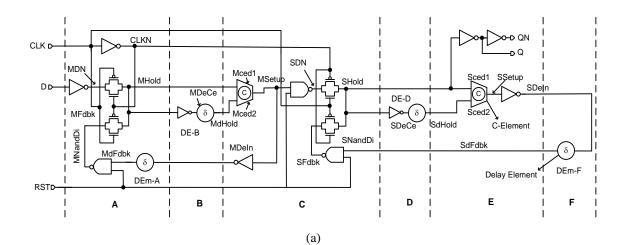

| 4.11 | Temporal FF Schematic Using Muller C-elements and Node Matrix of the          |  |

|      | Response Obtained After SET Simulation Methodology                            |  |

| 4.12 | Node Matrix Showing Failing Node Pairs With Black Dots                        |  |

| 4.13 | Vertically Interleaved Temporal FF Layout, Showing the Area Savings as        |  |

|      | Compared to Rectangular Cell and APR Tool Utilizing the Area Saved to Abut    |  |

|      | Standard Cells                                                                |  |

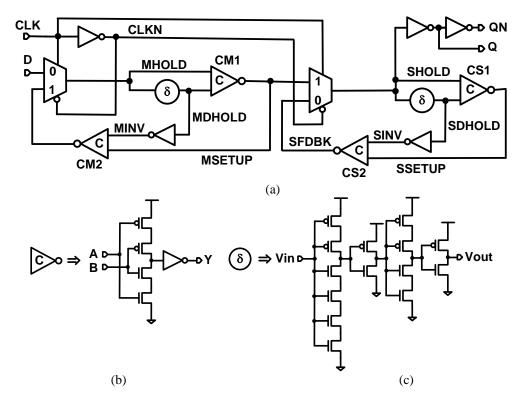

| 5.1  | Initial 4CE FF Design With C-Element and Delay Element Schematics             |  |

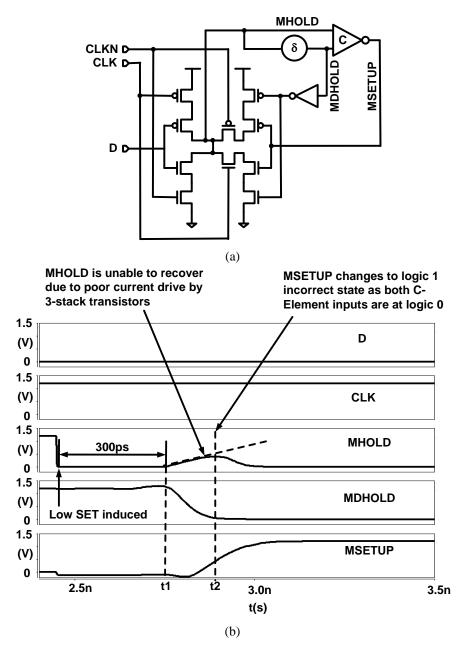

| 5.2  | Initial Proposed FF master Latch Circuit and Waveforms Showing MHOLD          |  |

|      | Node Vulnerable to SET of Duration 300ps91                                    |  |

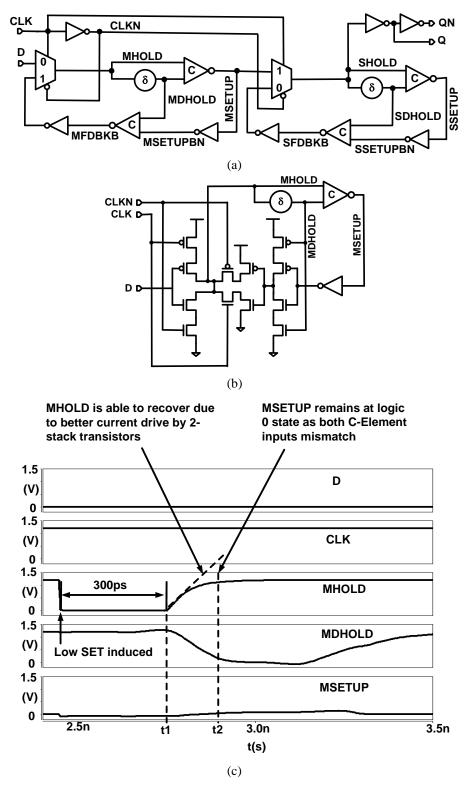

| 5.3  | Modified FF Design That Removes the Previous Three Stack Transistors by       |  |

|      | Adding an Inverter Before and After the C-Element to Master and Slave Latches |  |

|      | and Waveforms Confirming the MHOLD Node Robustness to SET                     |  |

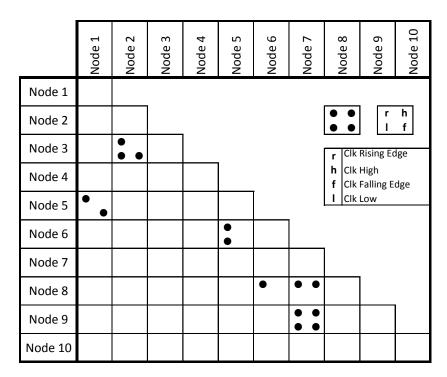

| 5.4  | Matrix Showing the Failing Node Pairs in the Proposed 4CE FF at Different     |  |

|      | Clock Phases When SETs are Simultaneously Induced on Each Node Pair94         |  |

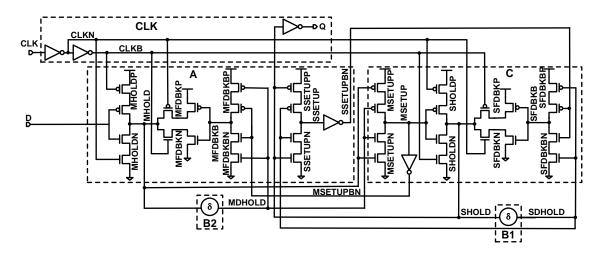

| 5.5  | Proposed FF Schematic Showing Node Grouping to Efficiently Separate Critical  |  |

|      | Nodes Based on the Groupings in the Double Node Upset Matrix                  |  |

| 5.6  | Proposed FF layout Showing the Sensitive Nodes Corresponding to the Color     |  |

|      | Coded Nodes in the Matrix                                                     |  |

| <b>T</b> ' |         |

|------------|---------|

| H1         | auro    |

| 1.1        | eure    |

|            | D *** * |

5.7

5.8

5.9

5.10

5.11

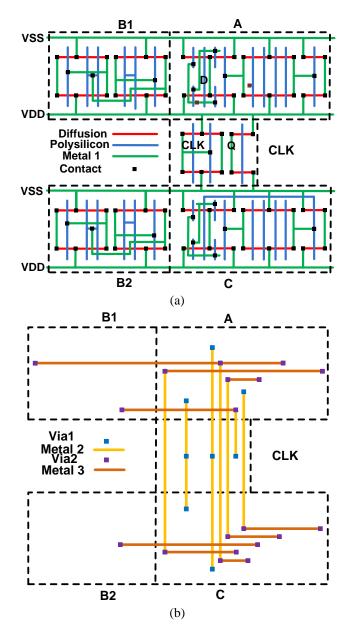

| Stick Diagram Representing the FF Layout.and the Metal Routes Connecting the |

|------------------------------------------------------------------------------|

| Blocks                                                                       |

| FF Placement in a Synthesized Design Abutting Standard Cells                 |

| BISER FF Schematic Showing Sensitive Node Groups                             |

| Matrix Showing Single and Two Node Failures in BISER FF to Induced           |

| Simulated SETs of $\delta$ Duration100                                       |

| SIN FF Schematic Showing Sensitive Node Groups With Groups Interleaved in    |

| the Layout to Avoid Simultaneous Charge Collection From Single Impinging     |

Page

| 5.12 | Matrix Showing Single and Two Node Failures in SIN FF to Induced Simulat     | ed   |

|------|------------------------------------------------------------------------------|------|

|      | SETs of $\delta$ Duration                                                    | 102  |

| 5.13 | The Effective Cross Section Seen by an Ionizing Particle that Simultaneously |      |

|      | Strikes Two Nodes A and B Causing Upset                                      | .104 |

### **CHAPTER 1**

## **INTRODUCTION**

The effect of soft errors in microelectronic devices was first studied in early 1970s [1]. It was predicted that cosmic rays would start upsetting the microcircuits due to heavy ion interactions when the feature sizes became small enough. Through 1970 and early 1980s the physics of these phenomena was examined. May and Woods [2] determined that the errors in the microcircuits were caused by alpha particle emission due to the radioactive decay of uranium and thorium present in the package material. They referred to these errors as "soft errors" and this was the first account of radiation induced upsets on terrestrial micro devices. It was also discovered that the upsets were also caused by nuclear reaction generated neutrons and protons [3].

## **1.1 Radiation Environment**

In 1980s research on single event effects (SEE) increased. Numerous methods were developed to harden the ICs against SEEs. Much of the research work was focused on errors observed in DRAMs, SRAMs, nonvolatile memories, latches and registers. In the 1990's, it was discovered that natural boron and isotope boron-10 present in boro-phospho-silicate-glass (BPSG) used in the manufacturing process reacted with low energy neutrons present in the atmosphere to produce upsets in ICs [4] subsequently, BPSG was removed from most processes.

### **1.1.1 Trapped Particles**

Charged particles that come into contact with the Earth's magnetic field can become trapped in the near-Earth environment. These particles include electrons, protons, and

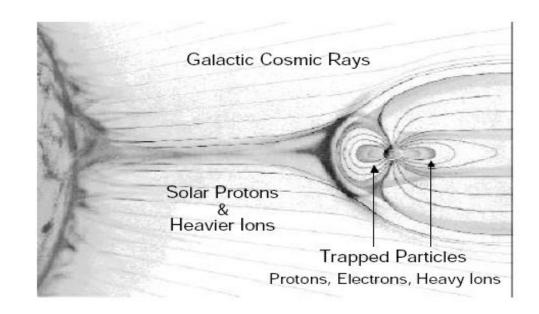

Fig. 1.1. Particles in the space radiation environment [5].

heavy ions. Fig 1.1 shows the space radiation environment. Electrons are very important components of the space environment because they inflict damage on spacecraft through spacecraft charging effects [6][7].

The trapped particle belts (Van Allen belts) consist of two regions of trapped particles, an inner belt centered at about 1.5 Earth radii, and an outer belt of particles at about 5 Earth radii, separated by a region of reduced particle flux.

Sources of radiation include the solar wind and transient solar events, cosmic ray particles from interplanetary space, and reaction products from cosmic ray collisions with the Earth's atmosphere [8].

## **1.1.1.1 Protons**

Energetic protons exist in the near-Earth environment and are one of the most prominent sources of orbital SEE. They range in energy from tens of keV to hundreds of MeV [8]. Protons with these energies are easily able to penetrate shielding and impinge on electronics within spacecraft. The altitude at which proton flux peaks depends on the proton energy, with high energy (>30 MeV) protons being cut off by around 3.5 Earth radii, but lower energy protons existing throughout the slot region.

## 1.1.1.2 Heavy Ions

The heavy ions from space are trapped by the Earth's magnetic field. The origin of these particles are cosmic rays, which are interstellar particles that drift into the solar system, become ionized by the solar wind and accelerated to 10's of MeV/nucleon, and are subsequently trapped by the magnetosphere. Recent studies have shown high heavy ion (e.g. nickel and iodine) fluencies above  $10^6$  particles/cm<sup>2</sup> can damage electronic components through ionization processes [8].

## 1.1.2 Transient Particles

In this section, we classify all particles in the near-Earth space environment that are not trapped in the magnetosphere. This includes particles introduced into the environment by solar events such as flares and coronal mass ejections (CMEs), as well as energetic ions incident from interstellar space.

### **1.1.2.1** Solar Event Protons and Heavy Ions

Solar events can be broadly classified as being either gradual or impulsive. The gradual events produce particle flux that decays slowly over several hours or even days, and have been correlated to CMEs. These events are proton-rich and can produce high-energy (>30 MeV) proton fluences higher than10<sup>9</sup> protons/cm<sup>2</sup> accumulated over a few days. Gradual events are responsible for the majority of large proton fluence events, and occur at a frequency of about 10 per year during solar maximum conditions.

Impulsive events are of much shorter duration (hours at most), and are marked by increased fluences of heavy ions and low energy electrons. Impulsive events produce heavy ion fluences that can be orders of magnitude above the galactic cosmic ray radiation. These heavy ions have energies ranging from tens of MeV/nucleon to hundreds of GeV/nucleon [8][9].

## 1.1.2.2 Galactic Cosmic Rays

Solar event particles are observed only for a short time following an event, although following a large event increased levels of trapped particles are observed and in some cases can produce new trapped particle belts. In contrast, galactic cosmic rays (GCR) form a background component of radiation that shows a slow cyclical variation with solar activity. GCRs are composed of very highly energetic protons and heavy ions that come from outside the solar system.

Protons comprise about 83% of the GCR flux, He nuclei (alpha particles) account for 13%, 3% are electrons, and the remaining 1% are heavier nuclei [10]. Even though they are not very abundant, heavy ions are very important to SEE because they deposit the most energy per unit path length, as discussed in later sections. Beyond Fe, the heavy ion flux drops dramatically. This is important, because the energy deposited by an ion per unit path length depends on its atomic number. Ions heavier than Fe are more ionizing, but are much less abundant.

GCRs that come into contact with the near-Earth environment encounter the Earth's geomagnetic field. Because they are so energetic (tens of MeV/nucleon to hundreds of GeV/nucleon), they do not become trapped and are not significantly attenuated by spacecraft shielding. GCRs that hit the atmosphere form a cascade of

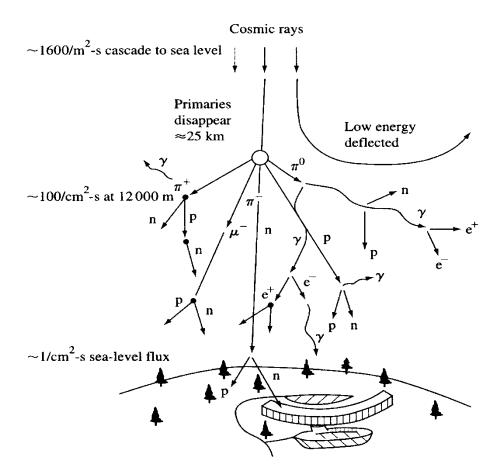

Fig. 1.2. Illustration of the terrestrial cosmic ray shower caused by the interaction of galactic cosmic rays with the Earth's atmosphere [12].

secondary particles.

## 1.1.3 Secondary Particles

Secondary particles are produced when GCRs strike the Earth's atmosphere and produce a shower of particles in the atmospheric environment. A radiation environment also exists in the Earth's atmosphere, and although less harsh than the space environment, it can also produce SEE.

As highly energetic cosmic rays enter the upper atmosphere they interact with oxygen and nitrogen in the atmosphere and produce a shower of daughter products [11][12]. Some of the daughter products can reach all the way through the atmosphere to ground level, equivalent to passing through more than 13 feet of concrete [11]. A diagram of a cosmic ray shower is shown in Fig. 1.2. The daughter products primarily responsible for causing upsets in high-altitude and terrestrial electronics are neutrons and protons [12]. The fluxes of neutrons and protons have similar characteristics with respect to energy and altitude variation, with both populations extending to energies greater than 1 GeV.

## **1.1.4 Radiation Effects in Devices**

When a component is exposed to radiation, the radiation transfers some of its energy to the component materials, changing the localized material properties. This can affect component functionality, with the end result depending on the type of radiation, where the energy deposition occurred, and the type of component.

## 1.1.5 Single Event Effects

SEEs are caused by the impact of either heavy ions or energetic protons and neutrons that occur naturally in space or the atmosphere, on sensitive areas in microcircuits. These particles deposit ionizing energy into the circuit that cause a soft (i.e., a non-permanent) error or in some cases permanent damage to the circuit. In this section we look at the release of mobile carriers along the path of an incident particle and the collection of these carriers.

## **1.1.5.1** Charge Deposition

As ionizing radiation passes through a target material electrons and holes are released along the path of ionizing particles. There are two primary methods by which carriers are released, direct ionization by the incident particle, and ionization by secondary particles created by nuclear reactions between the incident particle and the target material.

When an energetic particle passes through a semiconductor material it frees charged carriers along its path as it loses energy. When all of its energy is lost, the particle comes to rest in the semiconductor, having traveled a total path length referred to as the particle's range. The term linear energy transfer (LET) or dE/dx is used to describe the energy loss per unit path length of a particle as it passes through a material. LET has the units of MeV –  $\text{cm}^2/\text{mg}$ , because the energy loss per unit path length (in MeV/cm) is normalized by the density of the target material (in mg/cm<sup>3</sup>) as given by

$$LET = \frac{1}{\rho} \frac{dE}{dx} \quad (MeV - cm^2/mg), \tag{1}$$

where  $\rho$  is the material density (2.42 g/cm<sup>3</sup> for silicon). The charge deposited through direct ionization sufficient to cause an upset depends on the individual device and circuit that has been struck as well as the strike location and trajectory. Direct ionization is the primary charge deposition mechanism for upsets caused by heavy ions, where we define a heavy ion as any ion with atomic number  $Z \ge 2$  (i.e., He and above, i.e., particles other than protons, electrons, neutrons, or pions).

Direct ionization by light particles usually does not produce a high enough charge density to cause upsets. Protons and neutrons can both produce significant upset rates due to indirect mechanisms. As a high-energy proton or neutron enters the semiconductor lattice it may undergo an inelastic collision with a target nucleus. This may result in the emission of alpha ( $\alpha$ ) or gamma ( $\gamma$ ) particles and a recoiling daughter nucleus (e.g., Si emits  $\alpha$  -particle and a recoiling Mg nucleus) or a reaction, in which the target nucleus is

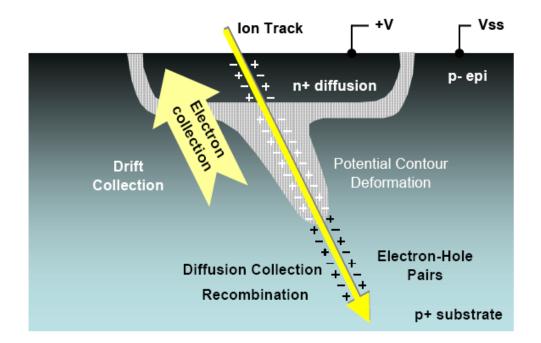

Fig. 1.3. A schematic of a reverse-biased n+/p junction struck by an ion [13].

broken into two fragments (e.g., Si breaks into C and O ions), each of which can recoil. Any of these reaction products can now deposit energy along their paths by direct ionization. Because these particles are much heavier than the original proton or neutron, they can deposit high charge densities as they travel and therefore may cause an SEU.

## 1.1.5.2 Charge Collection

The most sensitive semiconductor device structure is the reverse-biased junction. The collected charge ( $Q_{coll}$ ) depends on the type of ion, its trajectory, and its energy over the path through or near the junction. A reverse biased n+/p junction with a positive voltage on the n+ node is shown in Fig. 1.3. At the onset of an ionizing radiation event, a cylindrical track of electron-hole pairs with very high carrier concentration is formed along the path of the energetic ion's passage. When the resultant ionization track traverses or comes close to the depletion region, carriers are rapidly collected by the electric field creating a large current/voltage transient at that node.

As the ionizing radiation passes through the substrate, the depletion region is extended into a funnel deeper into the substrate [14]. This funnel greatly enhances the efficiency of the drift collection. The depth of the funnel is a function of substrate doping. This "prompt" collection phase is completed within a nanosecond and is followed by a phase where diffusion begins to dominate the collection process. Additional charge is collected as electrons diffuse into the depletion region on a longer time scale (nanoseconds) until all excess carriers have been collected, recombined, or diffused away from the junction area. The diffusion process is much slower and typically the total charge collected from diffusion is significantly less than that collected initially by prompt collection in the case of advanced technologies.

The magnitude of the collected charge ( $Q_{coll}$ ) depends on the size of the device, biasing of the various circuit nodes, substrate structure, device doping, the type of ion, its energy, its trajectory, the initial position of the event within the device, and the state of the device. The device's sensitivity to this excess charge is defined primarily by the node capacitance ( $C_{node}$ ), operating voltage ( $V_{node}$ ), and the strength of feedback transistors, all defining the critical charge ( $Q_{crit}$ ) required to trigger a change in the data state [15].

For simple isolated junctions, a soft error will be induced when a radiation event occurs close enough to a sensitive node such that  $Q_{coll} > Q_{crit}$  and  $Q_{crit}$  has the form

$$Q_{crit} = C_{node} * V_{node}$$

Conversely, if the event results in a  $Q_{coll} < Q_{crit}$  then the circuit will survive the event and no soft error will occur.

## 1.1.6 Destructive and Non-Destructive SEEs

Single-event effects are broadly characterized as either non-destructive or

#### TABLE I

| Acronym | Result          | Effect Name                        | Description                                     |

|---------|-----------------|------------------------------------|-------------------------------------------------|

| SEU     | Non-Destructive | Single Event Upset                 | Switching of a digital logic state              |

| SET     | Non-Destructive | Single Event Transient             | Voltage transient at circuit node               |

| SEMBU   | Non-Destructive | Single Event Multiple Bit<br>Upset | Switching logic states of adjacent cells        |

| SEB     | Destructive     | Single Event Burnout               | High current condition in BJTs or Power MOSFETs |

| SEGR    | Destructive     | Single Event Gate Rupture          | Destruction of Insulated Gate in power MOSFET   |

| SEL     | Destructive     | Single Event Latchup               | High current destruction of a n-p-n-p structure |

### VARIOUS SUB CATEGORIES OF SINGLE EVENT EFFECTS (SEE) [20]

destructive SEE. SEEs that cause no observable physical effect or a temporary disruption of circuit operation (known as soft errors) are Non-Destructive. SEEs which cause permanent damage to the device or integrated circuit (known as hard errors) are Destructive. Table I lists the various sub categories of SEEs. Any of these effects can cause soft errors in space applications. A brief description of each kind of SEE is given below

## 1) Single Event Transients (SET)

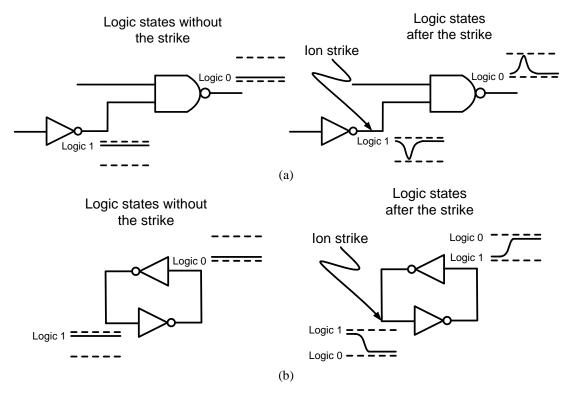

The situation in which a single event charge collection happens at a combinational circuit node generating a temporary voltage glitch is called a single event transient as shown in Fig. 1.4(a). The SET generated depends on the circuit node logic state and diffusion type. The SET can propagate through combinatorial logic and if captured by a sequential circuit, can upset the IC architectural state.

Fig. 1.4. Ionizing radiation induced charge collection at (a) a combinational circuit generating SET and (b) on a latch circuit causing a SEU. Either or both may upset IC architectural state in flip-flops.

2) Single Event Upsets (SEU)

A single event upset is charge collection at a sequential circuit storage node upsetting the logic state directly as shown in Fig 1.4(b). This can be caused either by the direct ionization from a traversing particle or by the ionization produced by charged particles and recoiling nuclei emitted from a nuclear reaction induced near the microcircuit element.

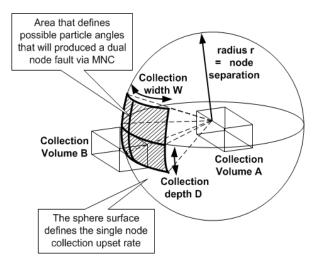

3) Single Event Multiple Bit Upsets (SEMBU)

SEMBUs occur when there is multiple node charge collection (MNCC) across multiple circuit nodes which simultaneously collect charge deposited by the same ionizing radiation particle track. MNCC can span multiple microns, greatly complicating the design and layout of hardened sequential circuit elements [21][22]. MBU probability is strongly dependent on node spacing, feature size, and supply voltage. As feature sizes shrink, MBUs are becoming more of an issue. The LET, range, track radius, and angle of incidence of the particle inducing upset are also important. In general, particles that deposit more energy, have a longer range, and have a larger radius are more likely to induce MBU. Since a single event induces an MBU, the MBU fail pattern is typically contiguous and follows a trajectory. In accelerated experiments, care must be taken when taking data to ensure that adjacent bit errors caused by separate events are not to be considered MBUs. Statistical methods can be applied to sort out adjacent upsets that appear to be MBU as well as fast bitmapping, i.e., time stamping and rapid SRAM readout.

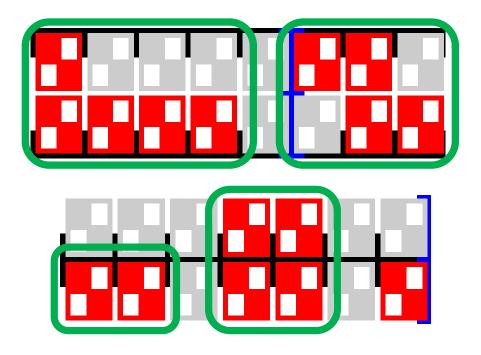

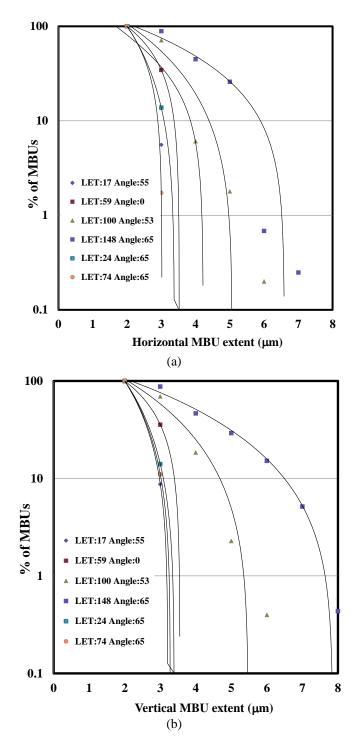

Fig. 1.5 shows MNCC effect on SRAMs designed at Arizona State University in a 90 nm process. Red cells indicate upset cells due to charge collection and MNCC regions are indicated in green. MNCC producing a multi-bit upset in a single EDAC word is trivially avoided in SRAMs by column interleaving, which has been standard practice for decades.

4) Single Event Burnout (SEB) and Single Event Gate Rupture (SEGR)

The charge track from an ion traversing a power MOSFET structure causes an avalanche breakdown between the n-epi and n+ substrate regions and produces a burnout and permanent damage at this interface [23].

SEGR is permanent damage causing rupture in dielectric gate materials due to avalanche breakdown caused by the traversal of a heavy ion [24].

Fig. 1.5. MNCC effect on SRAMs in 90 nm process. Red cells indicate upset cells due to charge collection and MNCC regions are indicated in green

5) Single Event Latchup (SEL)

Single event latchup is a CMOS Latchup caused by the collected charge. A SEL triggers a large supply currents that results when a parasitic silicon controlled rectifier pn-p-n structure is triggered into a regenerative forward bias [25]. Generally SER requires the device be powered down to turn off the SCR. If the current levels are high enough, permanent damage can result.

## 1.2 Radiation hardening

Hardness against radiation can be achieved through a variety of methods. One method is by employing special processes in the fabrication of microelectronic circuits. This can involve variation in the substrate structures or doping profiles. All methods use specialized circuit design techniques. Through specific design techniques, it is possible to

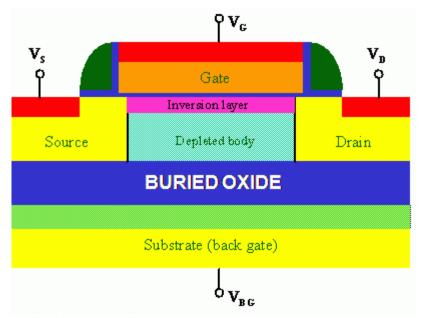

Fig. 1.6. Cross-section of an SOI transistor [26].

fabricate radiation hardened components using standard CMOS process flow known as radiation hardening by design (RHBD).

## **1.2.1** Process Mitigation Techniques

Substrate structures or doping profiles can have a large impact on reducing the critical charge, thus reducing SER. CMOS with buried implants can improve SER by reducing the size of the funnel formed, thereby reducing the amount collected by sensitive nodes. Following sections discusses some of these techniques.

## **1.2.1.1 SOI substrate**

Substrates incorporating a thin silicon layer on a thicker layer of buried oxide (Fig. 1.6) have been shown to reduce SER sensitivity as compared with bulk silicon [27][28]. In SOI, the isolation provided by the isolation oxide improves the SER robustness since less charge is collected than the bulk counterpart, i.e., the track length is attenuated.

### General Advantages of SOI

- Eliminates latch-up.

- Si volume reduction leads to large reduction in critical charge collection compared to bulk.

- No funneling can occur

### **1.2.1.2** Increasing the critical charge

SEE is a balance between charge collection and critical charge required for upset. If we increase the storage charge of a device its sensitivity to radiation can be reduced. Using either parasitic capacitance with back-end (metallization and inter-level dielectric) process tweaks or dedicated capacitor structures, critical charge can be increased. However, adding capacitance can have some negative effects on dynamic circuit response and dynamic leakage. The capacitors also require space, increasing the circuit area.

## 1.2.1.3 RC - Hardening

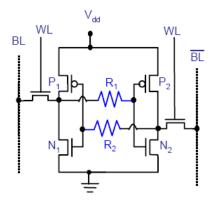

Any change which increases the critical charge while maintaining or reducing the collected charge will improve the SER performance of a device. A typical high-density SRAM cell consists of six transistors; two allowing data to be read and written to-and-from the cell and four transistors making up the two cross-coupled inverters responsible for maintaining the data state.

As shown in Fig. 1.7, resistance can be added between the two inverters so that the time to flip the cell is increased [29], thus effectively allowing the pull-up/pull-down transistors more time to restore the data state. However, this approach affects the write time of the cell. The latch or SRAM response is thus slowed so that it cannot respond to

Fig. 1.7. Resistively hardened SRAM schematic [29].

the voltage pulse induced by a radiation event before the charge is removed. As the node capacitance scales down, the resistance must scale up. These approaches seem to be "running out of steam" at about the  $0.25\mu$ m node.

## **1.2.2** Design Mitigation Techniques

Soft errors caused by ionizing particles can be overcome by solely using circuit techniques i.e., RHBD [32][35]. Sequential circuit elements like latches, flip flops and registers are hardened to radiation by one of the two well known design techniques, namely hardening by redundancy and via temporal techniques. The principles involved in these two techniques are discussed in the following sections.

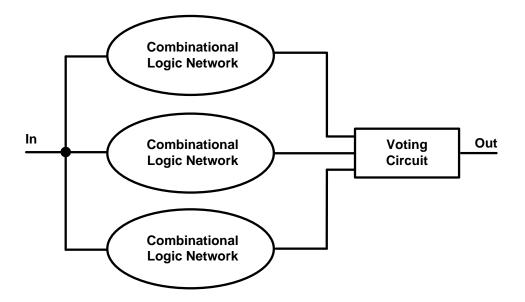

### **1.2.2.1 Hardening by Redundancy**

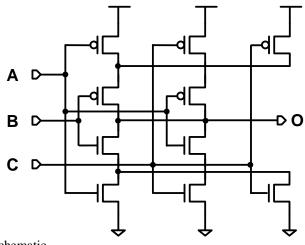

Redundancy hardens by duplication or triplication of the circuit elements and voting out the upset state. Redundancy operates in a way that error propagation is blocked unless two or more circuit elements are simultaneously in error. The most common spatial redundancy technique for combinational logic is the triple modular redundancy (TMR) shown in Fig. 1.8 [31]. Logic is replicated three times and then connected to a majority gate. The majority voter schematic is shown in Fig. 1.9. The

Fig. 1.8. Triple Modular Redundancy [30].

incorrect logic state resulting from the radiation strike at its input is voted out by the other two correct states.

The clear penalty in this technique is the 3X increase in area. This is an expensive technique but it does reduce soft failure rates to near zero levels, providing the necessary reliability for long term mission critical applications. It is also straightforward to implement and validate.

The DICE latch [32] shown in Fig. 1.10 is the most commonly used redundant structure, doubling the storage nodes in a configuration that requires two nodes be upset to change the state. However DICE latch based flip-flops have been shown to be susceptible to SET induced upsets [33], since input or clock errors are not mitigated. Moreover, they are increasingly susceptible to upset by MNCC, particularly on bulk technologies. The high DICE circuit density also makes it very difficult to provide adequate critical node spacing to avoid MNCC induced upsets.

Fig. 1.9. Majority gate schematic.

Fig. 1.10. DICE latch schematic [32].

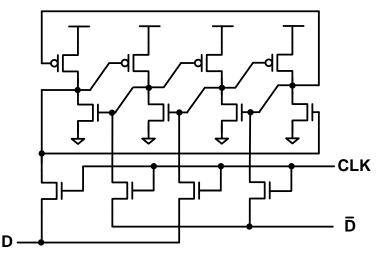

## **1.2.2.2** Temporal Hardening

Temporal hardening operates by essentially placing various types of low pass filters in the logic string. Various possible designs are described in [34]. One of the ways to achieve temporal filtering is to split the output of each combinational logic string into three branches, delay two of those branches by one and two delays, respectively, and then perform a majority vote on all three. Fig. 1.11 is a block diagram illustration for this technique. To be effective, the delay of each successive element must exceed the

Fig. 1.11. Temporally hardened circuit [30].

Fig. 1.12. Combination of C-element and inverter chain delay element to filter incoming SETs.

maximum pulse width of the transient.

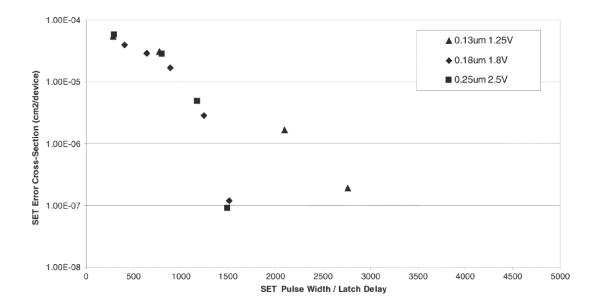

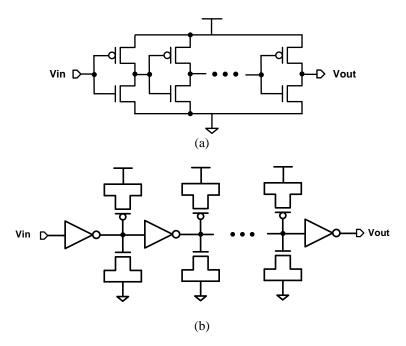

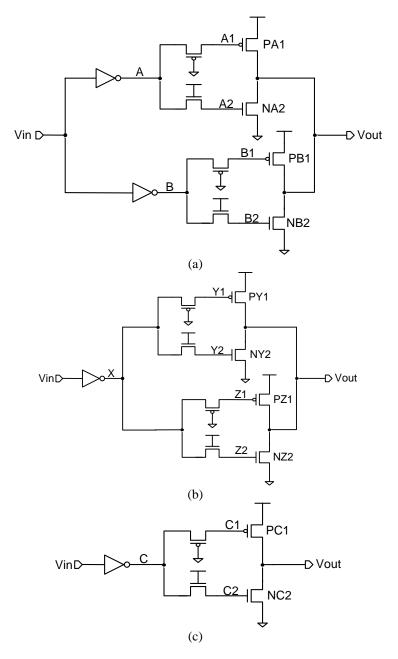

Temporal hardening uses delay elements to filter upsets into time windows. A delay element is a circuit which delays the input signal by a particular duration. These approaches have been shown effective at mitigating SETs on the sequential circuit clock and control inputs as well as SEUs [34][35]. Delay based filters combine a C-element and a delay element to filter SETs of durations less than the delay element delay as shown in Fig 1.12. Since circuit delay reduces with scaling, a key difficulty in temporal hardening is generating a low power and area delay circuit, that itself does not produce limiting SET durations. For instance, when using current starved delay elements to measure SET durations, up to 3 ns SET durations ( $t_{SET}$ ) were experimentally measured [36]. Thus, reducing the delay element usage, size, and SET duration due to the delay elements

themselves are key issues in temporal hardening. Temporal filtering the flip-flop (FF) inputs has demonstrated effectiveness when combined with a DICE latch at mitigating both SET and SEU [37].

## 1.3 Thesis contribution and organization

The causes and IC effects of radiation on silicon were discussed in the previous sections. Radiation hardening is a requirement for microelectronic circuits, especially in aerospace applications, as they are prone to radiation induced upsets from high altitude or orbital neutrons and ions. The most common method to SEE harden VLSI circuits is to use hardened FFs. Chapter 2 classifies different hardened FFs that have been proposed and providing a brief description of the operating principle, advantages and drawbacks for each FF. It is shown that ad-hoc design approaches frequently leave "holes" in the hardness.

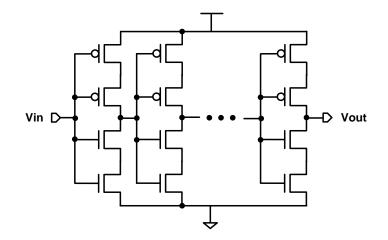

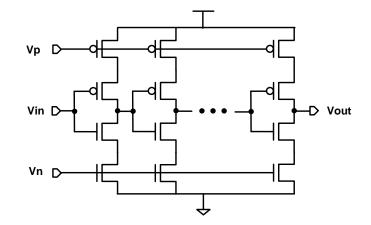

Modern CMOS processes are designed to minimize gate delay, which is a key metric. In RHBD, temporal delay circuits must maximize delay. However, current starving or longer than minimum channel length devices in a delay element may also produce the limiting t<sub>SET</sub>, against which the delay element is used to protect the circuit. Chapter 3 addresses this issue by proposing a dual redundant delay element which does not adversely affect the worst-case SET duration on the IC. Each redundant element is slowed by reduced gate overdrive, and the lower swing of the drain nodes provides power savings. The delay element SET tolerance is demonstrated by simulations using it in a RHBD master slave FF. Using the proposed delay element saves up to 25% total FF power at 50% activity factor. The delay element incorporates redundancy to mask long transients, which would otherwise limit the circuit hardness. A FF layout using the

proposed delay element is used in synthesis and auto-place and route experiments to confirm overall power, performance, and density. It uses a multi-bit cell interleaving the constituent circuits of four FFs to be robust to MNCC.

The design of FFs is made more difficult with increasing MNCC in advanced scaled fabrication processes, which requires that charge storage and other sensitive nodes be separated so that one impinging radiation particle does not affect redundant nodes simultaneously. In chapter 4, a correct by construction design methodology to determine a-priori which hardened FF nodes must be separated, as well as a general interleaving scheme to achieve this separation is described. Graph clustering approaches to determine effective node separation to protect against upset due to MNCC are demonstrated. The methodology is circuit simulation based, making it efficient and usable by circuit designers. The methodology is applied to radiation hardened flip-flops and optimal circuit physical organization for protection against MNCC is demonstrated. Example designs are presented to demonstrate the analysis and clustering for real flip-flop designs.

In chapter 5, a new low power and area efficient radiation hardened flip-flop design is presented. The hardness is verified and compared to other published designs through the proposed methodology that comprehends MNCC and tests resiliency to upsets at all internal and input nodes. Comparison of the hardness, as measured by estimated upset cross-section, is made to two published designs. Additionally, the importance of specific circuit design aspects to achieving hardness is shown. The FF achieves a 31% power and 35% area reduction compared to a previous design with similar hardness.

Finally, the summary of this work and conclusions are presented in chapter 6.

#### **CHAPTER 2**

## **RADIATION HARDENED FLIP-FLOPS**

This chapter explores the different radiation hardened FFs that have been proposed in the literature and tries to classify them based on different hardening techniques and the hardness afforded, e.g., to SEU only or to SET and SEU. Radiation strikes affect the sensitive nodes in the combinational logic, by generating voltage transients that propagate through the circuit. These SETs may sometimes be masked by the feed forward logic circuitry. However, if they are captured by a sequential element, the circuit logic state may change affecting its overall functionality. Sequential logic circuits are also vulnerable to radiation strikes that directly upset the storage node logic state (i.e., SEU)

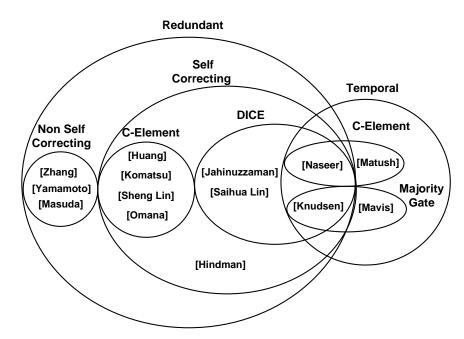

## 2.1 Radiation Hardened Flip-Flop Classification

By analyzing the working principles of various designs available in the literature, radiation hardened FFs can be classified into two broad categories. One is temporal hardening and the other is hardening by redundancy, both of which were explained in chapter 1. Further, most FFs in each of these categories have similar hardening principles which are mostly improvements or combinations of certain hardening techniques. For instance many FFs utilize the four node redundant storage structure seen in DICE to achieve SEU hardness on storage nodes. This enables us to further classify FFs in each of these two broad categories based on common working principles. Some FFs incorporate hardening principles from both of the two broad categories, for instance the DF-DICE [37] latch utilizes temporal hardening to filter SETs on clock and D inputs and redundant storage structure of DICE for protection against SEUs. The original authors' names are used throughout.

## 2.2 Redundant Non Self Correcting FFs

FFs hardened by redundancy can be further classified into self-correcting and nonself-correcting. Non-self-correcting FFs, as the name suggests, will not have mechanism to restore upsets on storage node states. Instead the incorrect storage node state is merely prevented from propagating. These circuits typically have redundant latches whose outputs are connected to a C-element or majority gate. If the storage node in one of the latches upsets due to particle strike, the C-element or majority gate inputs mismatch. In the former case, the C-element output tri-states, blocking the upset state from reaching the next stages. Three such FFs belong to this category, the prominent one being BISER proposed by Zhang [44]. The designs proposed by Yamamoto [45] and Masuda [46] are improved versions of BISER FF.

#### 2.2.1 Built In Soft Error Resilience FF

#### Working principle:

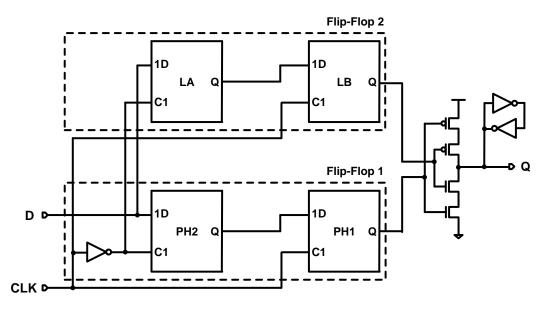

The first FF in this category is the Built-In Soft Error Resilience (BISER) [44]. It consists of two D-flip-flops joined with a C-element as shown in Fig. 2.1. A particle strike can happen either in the clock low or clock high phase and can upset one of the four latches. In the clock low phase latches LB and PH1 hold the stored logic value and hence are prone to SEUs, while LA and PH2 are not error-prone as they are transparent and driven by the preceding logic stages. If a particle strike flips the logic value stored in LB or PH1, the two inputs to the C-element will differ and the error will not propagate to the C-element's output. Similarly in the clock high phase, latches LA and PH2 are holding the data and hence are prone to upsets while latches LB and PH1 are transparent.

Fig. 2.1. BISER FF schematic [44].

Now upsets on LA or PH2 will be directly fed to C-element inputs, which again tri-states if they mismatch preventing the error from propagating further.

The purpose of the keeper is to fight the leakage current in the C-element when both its pull-up and the pull-down paths are shut off, which occurs only when the content of one bi-stable circuits gets flipped by a particle strike.

## Advantages:

Its layout area is slightly more than twice the standard D-FF layout which is relatively small as compared to other hardened FF designs, especially temporal FFs. *Disadvantages:*

It is not hard to SETs on its D and clock inputs. A major flaw in this design is the exposed storage node at the output Q which may cause data from the next stage to write back and change the current FF state. Finally, it is not self-correcting.

Fig. 2.2. Bi-stable cross-coupled dual modular redundancy (BCDMR) FF schematic [45].

## 2.2.2 Bi-stable Cross-Coupled Dual Modular Redundancy FF

## *Working principle:*

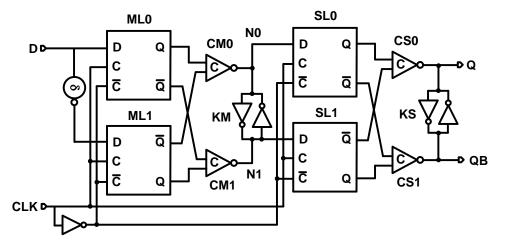

The bi-stable cross-coupled dual modular redundancy flip flop (BCDMR) [45] shown in Fig. 2.2 is an "improved" version of BISER. It has two C-elements connecting the master to the slave latches. There is an inverting delay element between the two master latches ML0 and ML1; hence their inputs will have opposite logic states, resulting in the C-elements CM0 and CM1 to have identical logic states at their inputs. Thus this design adds temporal protection to the D input.

Similar to the BISER FF case, a particle strike can happen either in the clock low or clock high phase and can strike one of the four latches. In the clock low phase, the protection provided to upsets in latches SL0 and SL1 by C-elements CS0 and CS1 is similar to that in BISER. However, in the clock high phase, unlike BISER, the C-elements CM0 and CM1 prevent upsets in ML0 and ML1, both in hold mode, from propagating further. The C-elements must have sufficient drive strength to flip the weak keeper. The keepers need not be strong as the two C-elements will rewrite the keeper if it flips.

### Advantages:

It is hard to SETs on D-input. In the clock low phase, a delay filter circuit will be formed at the D-input, as latches ML0 and ML1 become transparent, connecting the delay element to one of inputs of C-elements CM0 and CM1.

#### Disadvantages:

It is not hard to SETs on clock inputs. This design also has the same flaw as the BISER design where it has exposed storage node at the output which may cause data from the next stage to write back and change the current FF state. This is a common error in academic papers but absolutely never occurs in real commercially shipping industry designs. Of course it makes the timing and power look better, but is prone to coupling noise induced failure. The area advantage of the BISER FF no longer holds for this FF, as it has a delay element, three additional C-elements, and three additional keepers.

# 2.2.3 Bi-stable Cross-Coupled Dual Modular Redundancy FF with Adaptive Coupling

## Working principle:

The FF [46] shown in Fig. 2.3 (top) is essentially BCDMR FF with the standard D latches replaced with master and slave latches of adaptive coupled flip-flop (ACFF) shown in Fig. 2.3 (bottom). Hence it is called BCDMR-ACFF. Its working principle is same as BCDMR except for the functioning of ACFF. The master latch has adaptive-coupling (AC) element, comprised of PMOS and NMOS transistors connected in parallel with both their gates connected together. The reason for having the AC element in the master latch is as follows.

Fig. 2.3. BCDMR-ACFF (top) [46] and AC flip flop (below) [47] schematics.

Let us assume that there is no AC element. Node F will be connected to node G and node FN will be connected to node GN. Now assume node G (or node F) to be at logic 1 and node GN (or node FN) to be logic 0. Due to the weak current drive of PMOS pass gate, logic 0 (D=0) cannot be written on node G (or node F). Now consider the case when the AC element is added to the master latch as shown in Fig. 2.3. Now if logic 0 has to be written to node G, node BN should be at logic 1 and node B should be at logic 0. This causes the NMOS transistor in the bottom AC element to turn on, resulting in the state of node F to be lowered to Vdd-V<sub>t</sub>, when the current discharges through the F-B path. Due to the lowered potential on node F, the PMOS pass gate can now pull node F and hence node G towards logic 0. However, node F will not be completely discharged. When node G goes to logic 0 by charging node FN, node F will be completely discharged.

to 0V through the G-F path, as the NMOS in the AC element allows a strong discharge current.

#### Advantages:

This FF saves power as the ACFF operates with the single-phase clocking scheme. Power reduction is achieved by not using the local clock buffers and using pass transistors instead of transmission gates, which results in four fewer transistors than the standard transmission-gate FF.

#### Disadvantages:

As PMOS pass transistors have weak current drive and are used to write data into latch storage nodes, the SEU recovery time will be longer. Again since disruption of the output jam latch is independent from a soft error, the lack of output buffering is unacceptable. The use of slave jam latches makes this design problematic on modern processes with high process variation. Moreover, using NMOS pull-ups and PMOS pulldown transistors is generally banned for the same reasons.

## 2.3 Redundant Self Correcting FFs

In the self-correcting designs, upsets on storage node states are restored to original state by built-in circuit mechanisms. The restoration is due to positive feedback between storage nodes. Most FFs in this category base their design either on the four node storage structure seen in DICE or utilize C-elements. Hence, the self-correcting designs are further classified as the ones that utilize a DICE latch storage structure and the ones that utilize C-elements. The FFs proposed by Huang [48], Komatsu [49], Sheng Lin [51] and Omana [52] are self-correcting designs that utilize C-elements. The designs proposed by Hazucha [53], Jahinuzzaman [54], Blum [55] and Saihua Lin [56] are self-correcting

Fig. 2.4. C-Element based latch schematic [48].

designs that incorporate DICE latch storage structure. The TMR FF proposed by Hindman [43] does data correction in the clock low phase and hence can also be categorized as self-correcting.

## 2.3.1 Redundant Self Correcting C-Element Based FFs

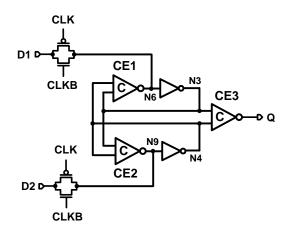

#### **2.3.1.1** Three C-Elements Based Latch

#### *Working principle:*

Fig. 2.4 shows a hardened latch design using three C-elements [48]. There are three C-elements in the latch: CE1, CE2 and CE3. CE1 and CE2 constitute a "dual interlocked" keeper for two purposes. Firstly, they can be used as keepers when the latch is not transparent to keep the correct value. Secondly, they are used to mask the radiation-induced SEU on the internal storage nodes N3 and N6. C-element CE3 is used to block soft errors from propagating through the latch. Consider an upset on node N3, when the latch is in hold mode. The C-element CE1 tri-states, and holds node N6 in its original state, eventually driving the node N3 to recover to its original state. Until that time, the C-element CE3 also tri-states and blocks the data from propagating further.

## Advantages:

Its layout area is almost twice the standard D latch area, which is relatively small as compared to other hardened FF designs, especially temporal FFs.

## Disadvantages:

This latch is not hard to SETs on data and clock inputs. With delay element between D1 and D2, the latch can mitigate SETs on D input. When the latch is in the hold mode, if node N6 (or N9) is upset due to particle strike, node N3 flips that causes CE1 (or CE3) to tri-state. There is no mechanism to restore node N6 to its original state and eventually, due to charge leakage nodes N6 and Q may switch to wrong state. Also, since the C-elements occupy only two polygon tracks, storage nodes will be in close vicinity making them vulnerable to multi-node charge collection. Consequently this latch is not really hard to all SEU or SET possibilities. Thus while small, it is also ineffective.

## 2.3.1.2 Soft Error Hardened Latch

#### Working principle:

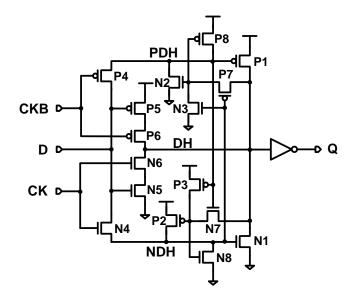

Fig. 2.5 shows the schematic for the soft error hardened (SEH) latch proposed in [49]. The latch operates by complementary clocks, CK and CKB. The circuit has two bistable elements formed by transistors P1-N1 & P8-N2 and P1-N1 & P2-N8. DH, PDH and NDH are the three storage nodes in the circuit. When the latch opens, input data drives the DH, PDH and NDH. PDH and NDH have the same polarity as the input data while DH has inverted polarity.

Consider the latch to be in the hold mode and the node DH to be at logic 1 state. As nodes PDH and NDH are complimentary to node DH, both will be in the logic 0 states, turning on transistor P1 and holding node DH at logic 1. Now, if an upset on node

Fig. 2.5. Soft error hardened latch schematic [49].

DH pulls it to logic 0, it will be pulled back to the logic 1 state through P1. Now consider the case when there is an upset on node PDH and pulls it to logic 1 state. The logic 0 state on node NDH will turn on P7, which then turns on N2 due to logic 1 state on node DH. Eventually transistor N2 pulls the node PDH back to logic 0. Similar analysis holds good for logic 1 to 0 upset on node PDH, where P8 would restore the logic 1 state as N3 would turn on due to logic 1 state on NDH.

#### Advantages:

As the circuit has 18 transistors, the layout area is small as compared to other hardened designs.

## Disadvantages:

This latch is not hard to SETs on data and clock inputs. Also, as the circuit is small, the storage nodes will be in close vicinity making them vulnerable to multi-node charge collection. The extensive use of NMOS pull up and PMOS pull down transistors is problematic for robustness to process variation, which is more commonly encountered than soft errors.

Fig. 2.6. Schmitt trigger based latch schematic [51].

## 2.3.1.3 Schmitt Trigger Based Latch

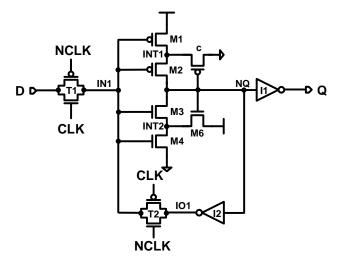

#### *Working principle:*

A hardened latch design based on Schmitt trigger [51] is shown in Fig. 2.6. In this latch, node IN1 is connected to a Schmitt trigger that consists of six transistors. The Schmitt trigger provides tolerance to soft errors by obviously resisting a voltage change (since this is what Schmitt triggers are designed to do), i.e., hysteresis. When node IN1 is at logic 0 state, node NQ will be in logic 1 state, M6 is on, and node INT2 is charged. Consider the latch to be in the hold mode. Now, if there is a strike on node IN1 that changes its state from logic 0 to logic 1, to affect NQ, the charge at node INT2 has to be discharged. Thus the logic state on storage node NQ will be retained until the additional charge due to parasitic capacitance on node INT2 is fully discharged. During this time the inverter I2 driving node IN1 would restore it to the original state. Similarly if the strike on node IN1 changes its state from logic 1 to logic 0, to affect NQ, the charge at node INT1 has to be discharged.

Fig. 2.7. Split internal node latch schematic [52].

## Disadvantages:

This latch is not hard to SETs on D and clock inputs.

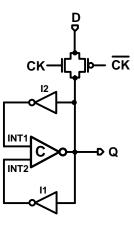

## 2.3.1.4 Split Internal Node Latch

## Working principle:

Fig. 2.7 shows a latch [52] design based on duplicating the nodes within the latch feedback loop. When CK = 1, D propagates to the output Q and is fed back to nodes INT1 and INT2 through inverters I1 and I2, respectively. Since both of these internal nodes assume the same logic value, only one of the series of two transistors, MN1-MN2 or MP1-MP2, will be conducting. When CK = 0, the transmission gate is turned off and, consequently, the previous output value is maintained. In case of a strike affecting one of the latch feedback internal nodes INT1 or INT2, the C-element inputs mismatch and its output Q temporarily moves to a high impedance state, without changing its logical value.

### Disadvantages:

This latch is not hard to SETs on D and clock inputs. The storage node is directly connected to the output (but this is easily fixed). When the latch is in the hold mode, an

Fig. 2.8. Ten transistor hardened latch schematic [54].

upset on node Q causes it to flip to a wrong logic state and there is no mechanism to restore it to the original state. Basically it splits the feedback node into two and the design is hard to upsets on them, but the hold node is unhardened.

#### Advantages:

No advantages are seen in this latch as it has the above mentioned design flaw.

## 2.3.2 Redundant Self Correcting DICE Based FFs

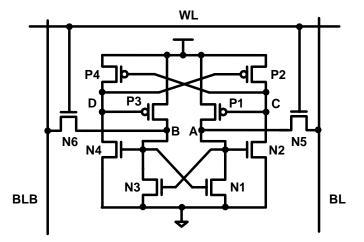

#### 2.3.2.1 Quatro Latch

## Working principle:

Fig. 2.8 shows a hardened SRAM design [54] consisting of ten transistors called the Quatro latch. Two access transistors, N5 and N6, connect the bit lines (BL and BLB) to the storage nodes A and B. If the stored bit is'0', the logic states at nodes A, B, C, and D will be '0', '1', '1', and'0', respectively. Each of these nodes is driven by an NMOS and a PMOS transistor, their gates being connected to two different nodes. If an SET pulls down (up) a node voltage, the node voltage is restored by the 'ON' PMOS (NMOS) transistor connected to the node and driven by an unaffected node.

Fig. 2.9. Soft error tolerant static D latch schematic [56].

Advantages:

It is DICE latch with modifications.

## Disadvantages:

The modifications from the DICE make the latch suffer than DICE. The latch is vulnerable to multiple node charge collection from a single particle strike, the worst case being two nodes at same potential (nodes A and D or nodes B and C) getting affected. Therefore, in order to reduce the possibility of upsets due to MNCC, the cell should be laid out by keeping the same potential nodes as physically apart as possible.

## 2.3.2.2 Static DICE Based D Latch

## Working principle:

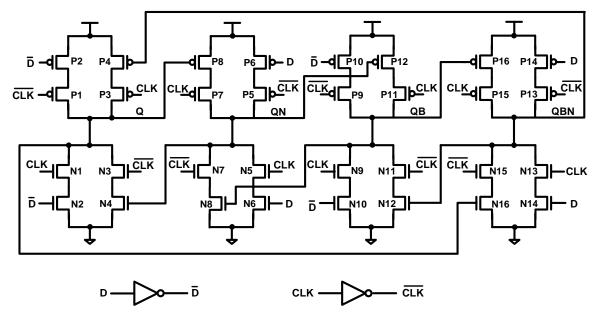

Fig. 2.9 shows another latch design based on DICE latch [56]. It essentially integrates tri-state inverters to a DICE latch which has Q, QN, QB and QBN as its storage nodes. In the clock high phase transistors P1-N1, P5-N5, P9-N9 and P13-N13 are on and

P3-N3, P7-N7, P11-N11 and P15-N15 are off, enabling the data to be written to the latch storage nodes. In the clock low phase, the latch is in the hold mode and P3-N3, P7-N7, P11-N11 and P15-N15 are on, turning the circuit to a DICE latch structure. In this phase, transistors P16-P15-N15-N16, P12-P11-N11-N12, P8-P7-N7-N8 and P4-P3-N3-N4 form the DICE structure.

In the hold mode, consider the logic states on storage nodes Q, QN, QB, and QBN to be LHLH and due to particle strike assume the pattern changes to LLLH. Now, P12 turns on trying to charge node QB to H and N4 turns off, leaving the node Q floating. The L state on node Q keeps transistor P8 on that eventually charges node QN to H, bringing the logic states on storage nodes back to LHLH.

#### Advantages:

This latch is similar in design to the latch described in section 2.3.2.1. It has relatively small area as compared to other hardened designs

#### Disadvantages:

It is not hard to SETs on D and clock inputs. As the storage nodes are in close vicinity, they are vulnerable to multi-node charge collection.

## 2.3.3 Triple Mode Redundant FF

#### *Working principle:*

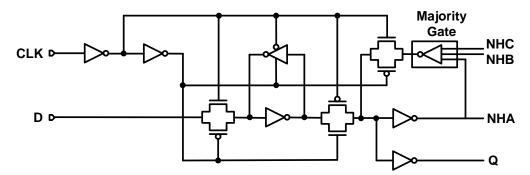

The last design [43] in the self-correcting category is shown in Fig. 2.10. It is the most robust of all the FFs seen so far but by far the largest. It has the normal D-FF replicated three times with a modified slave latch. The slave latch feedback path uses a majority gate driven by the other redundant copies. When the clock rises, the slave latch holds the data and the master latch is transparent. In this clock high phase, the state of the

Fig. 2.10. Triple Mode Redundant FF schematic [43].

slave latch is voted to be the same as the majority of the triple redundant copies. This provides the self-correcting feature, which allows clock gating, in the FF. Node NHA in the slave latch and nodes NHB and NHC from other two copies are fed to the majority gate. Similarly, nodes NHA NHB and NHC are fed to the majority gates in the other two latches. The added capacitive loading on the NHA node does not affect the circuit timing as the slave latch has the entire clock high phase to propagate the slave latch feedback signals.

## Advantages:

It is hard to SETs on D and clock inputs. The circuits using this FF will have full commercial speed performance, except for slightly longer local routing. A variation of these FFs that have correcting master latches has been used extensively in FPGA based designs [63].

## Disadvantages:

Since the circuits using this FF are replicated three times there is a threefold increase in area and power as compared to the same unhardened circuits.

Fig. 2.11. Temporal FF schematic [35].

#### 2.4 Temporal FFs

Temporal designs' working principle was explained in chapter 1. All temporal FFs utilize delay filters to filter SETs in time domain. As was shown in chapter 1, the delay filter combines a delay element with either a C-element or a majority gate and can filter SETs on clock, data and other control signals. For the delay filter to be effective the delay element delay should be more than the expected SET duration.

The delay filter in Matush's [35] design incorporates C-elements while that in Mavis's [34] design incorporates majority voter. The designs proposed by Knudsen [39] and Naseer [37] although classified as temporal designs, utilize DICE redundant storage structure in their master and/or slave latches. The delay elements occupy most of the FF area and dissipate most of its power. Hence designing a low power area efficient delay element is essential to these designs - that is covered in chapter 3.

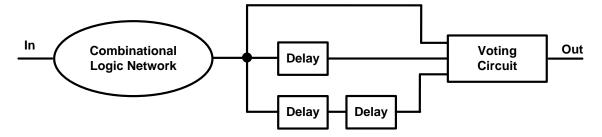

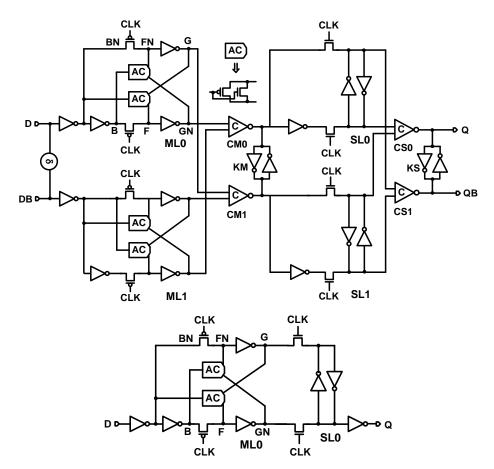

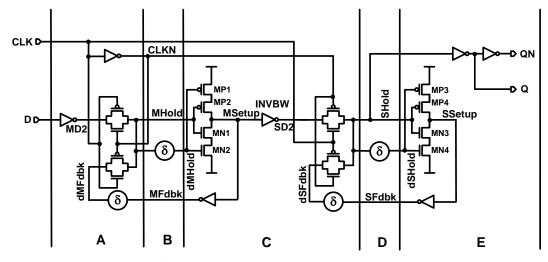

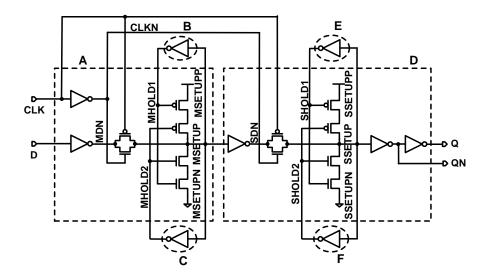

#### 2.4.1 Four Delay Element FF

#### Working principle:

Fig. 2.11 shows a temporal FF [35] schematic comprised of two temporal latches acting as the master and slave. In this design, there are four delay elements, two for each latch. The latch uses dual redundancy, in the form of one delayed and one non-delayed node, driving the C-element storing the latch value. The delay assures that the effect of an SET on the hold nodes, or preceding nodes, does not flip the latch. The first delay element, combined with the C-element, mitigates SETs at the pins D, CLK, and CLKN that are less than the delay element delay. The second delay element in the feedback loop protects the latch nodes, MSetup and SSetup, from SEUs. Without this delay, a hit on a logically high setup node would cause a low value to be fed back to the C-element, causing the C-element to tri-state. When tri-stated, the C-element cannot restore the setup node to the correct value. The second delay element allows the C-element to remove any charge collected on the setup nodes before it tri-states. The inverter INVBW between node MSetup and the slave latch input node SD2 prevents charge sharing failures. *Advantages:*

This FF is very robust as it is hard to SETs on D and clock inputs and to SEUs on the storage nodes.

#### Disadvantages:

The drawback of this FF (and all temporal FFs) is the increased circuit size and power dissipation due to the delay elements. It has four delay elements. Delay elements are composed mostly of inverters driving two large capacitances with a buffer at the end.

Fig. 2.12. Temporal latch employing majority gate [34].

The FF setup time increases by an additional delay element delay to account for an SET during the setup time.

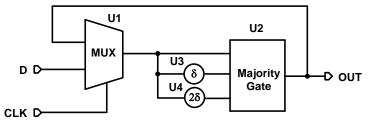

#### 2.4.2 Temporal Latch Incorporating Majority Gate

#### Working principle:

Fig. 2.12 shows the temporal design [34] incorporating majority gate. It has a two-input MUX (multiplexer) with its output fed back to one of its input, the data fed to its other input, and the select line controlled by the clock signal. The MUX (UI) output is sampled using a majority gate (U2) along with sampling delays (U3 and U4) and then the majority of the sampled data is fed back to the input. An SET at the D-input passing through the MUX reaches the majority gate at three separate times t,  $t+\delta$  and  $t+2\delta$ . Hence at any given time, the majority gate sees the transient at only one of its inputs. The other two inputs will not have transients and hence the SET is voted out. By using the MUX at three separate times, the temporal latch is effectively replicated not in space, but in time. This temporal latch is also immune to transients occurring on the input clock node. Any clock transient momentarily switches the selected MUX input producing a possible transient at the MUX output. Since this is just the data input to the temporal sampling circuitry, it is eventually rejected by the voting circuitry.

Fig. 2.13. Temporal FF schematic incorporating DICE latch [39].

Advantages:

This latch is hard to SETs on D and clock inputs and to SEUs on the storage nodes.

#### Disadvantages:

This latch has three delay elements and has greater circuit size and power dissipation than a conventional DFF, as well as a much larger the effective setup time.

## 2.4.3 Temporal FF Incorporating DICE Latch

Working principle:

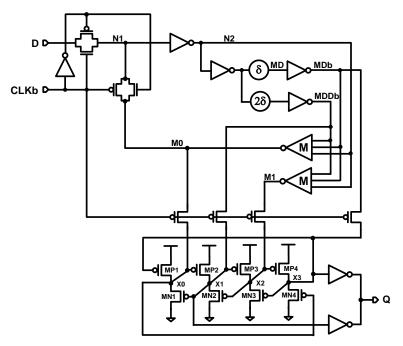

The temporal FF [39] shown in Fig. 2.13 comprises a temporal master latch discussed in section 2.4.2 and a DICE slave latch. As explained in previous section, the temporal latch is not susceptible to SEU or SET induced upsets on the D and CLK inputs. The temporal master latch generates three signals M0, MDb, and MDDb, which are combined by the feedback majority gate and connected to DICE slave latch. The fourth

DICE input M1 is generated through a second majority gate. M0 and M1 have the same signal polarity while MDb and MDDb have opposite signal polarity. The PMOS pass transistors connect the master latch to the DICE slave latch. The DICE latch PMOS to NMOS ratio is sized to allow the PMOS to overcome the NMOS feedback. Two separate output inverters connected in parallel to drive a common output, splits the capacitive loading of the output inverter transistors across two of the DICE storage nodes, improving the clock to Q delay.

## Advantages:

This latch is hard to SETs on D and clock inputs. The DICE slave latch replacement for a temporal slave latch results in reduced circuit area and power dissipation compared to other temporal designs.

#### Disadvantages:

It utilizes three delay elements in the master latch resulting in increased circuit size as compared to conventional FF designs. Since the clock closes the slave latch before the inputs are able to recover, the incorrect logic state is captured.

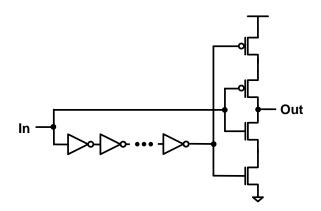

## 2.4.4 **DF-DICE Latch**

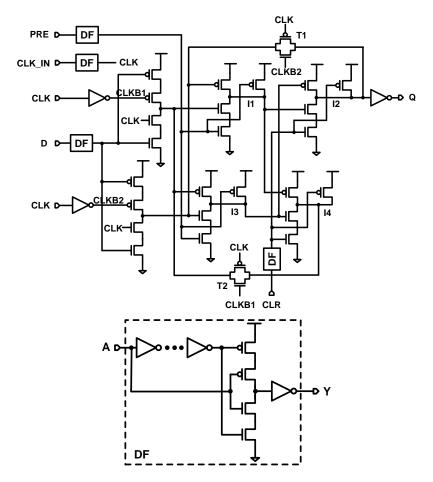

#### Working principle

Fig. 2.14 shows a temporal latch [37] hard to SETs on input, clock and control signals as the incoming clock, data, preset and clear signals pass through the delay filter. This latch essentially has the DICE structure with preset and clear control signals integrated to the four standard PMOS-NMOS structures seen in DICE. CLKB1 and CLKB2 are the inverted version of the CLK signal. Nodes I1, I2, I3 and I4 are the DICE latch storage nodes. In the clock high phase, the latch is transparent, transmission gates

Fig. 2.14. DF-DICE latch schematic [37].

T1 and T2 are turned off and data is written on nodes I1 and I3. In the clock low phase, the latch holds the data as the transmission gates T1 and T2 are turned on completing the four node feedback structure of DICE latch. Now upsets due to particle strikes on any of the four storage node are restored by the self-correcting feature of the DICE latch. *Advantages:*

This latch is hard to SETs on clock, data and control signals. Due to the DICE latch storage structure it is hard to SEUs on storage nodes.

## Disadvantages:

This design uses four delay elements leading to increased area and power penalty. Also as the output of the C-element is a dynamic node, it can lose its state if left floating

Fig. 2.15. Venn diagram representation of FF classification.

for longer times. To overcome this problem, a weak inverter which provides feedback and maintains the output state should be used at the output node.