## New Model for Simulating Impact of

Negative Bias Temperature Instability (NBTI)

in CMOS Circuits

by

Sudheer Padala

A Thesis Presented in Partial Fulfillment of the Requirements for the Degree Master of Science

Approved November 2014 by the Graduate Supervisory Committee:

Hugh Barnaby, Chair Bertan Bakkaloglu Jennifer Kitchen

ARIZONA STATE UNIVERSITY

December 2014

#### **ABSTRACT**

Negative Bias Temperature Instability (NBTI) is commonly seen in p-channel transistors under negative gate voltages at an elevated temperature. The interface traps, oxide traps and NBTI mechanisms are discussed and their effect on circuit degradation and results are discussed. This thesis focuses on developing a model for simulating impact of NBTI effects at circuit level. The model mimics the effects of degradation caused by the defects.

The NBTI model developed in this work is validated and sanity checked by using the simulation data from silvaco and gives excellent results. Furthermore the susceptibility of CMOS circuits such as the CMOS inverter, and a ring oscillator to NBTI is investigated. The results show that the oscillation frequency of a ring oscillator decreases and the SET pulse broadens with the NBTI.

# Dedicated to my parents

Murali Padala and Rajeswari Padala

#### **ACKNOWLEDGMENTS**

I would like to thank my advisor Dr. Hugh Barnaby for giving me an opportunity to be part of his research group. His wide knowledge on the topic and his extensive research has been of great value for me. His understanding, encouraging and personal guidance have provided a good basis for the present thesis. I want to express my deepest gratitude to the Ridgetop Group for giving me the opportunity to work with them as an Intern. It was one of the best learning experiences one could expect to get as a student.

I am deeply grateful to my thesis committee members, Bertan Bakkaloglu and Jennifer Kitchen for their comments and valuable time.

I am thankful to Mehdi Saremi with whom I had very good technical discussions. I also want to thank some of my friends - Raviraj, Harsha, Raghuvir, Yashwanth, Sravan, Akhilesh, Abhishek, my roommates and many others who helped me and constantly supported me during my hard times at ASU.

Finally I am indebted to my family for their constant encouragement and belief in me. I am very proud of them and I constantly work hard to achieve my dreams and to make them proud.

## TABLE OF CONTENTS

|                 | Page                                |

|-----------------|-------------------------------------|

| LIST OF TABLES  | vii                                 |

| LIST OF FIGURES | Sviii                               |

| LIST OF ABBREV  | TATIONSx                            |

|                 |                                     |

| CHAPTER         |                                     |

| 1 INTRODUCTI    | ON 1                                |

| 2 OVERVIEW C    | OF THE DEFECTS                      |

| 2.1 MC          | OSFET Analysis2                     |

| 2.1.1           | The Basic MOSFET Equations          |

| 2.1.2           | MOSFET Region of Operations         |

| 2.1.3           | Interface and Oxide Charges5        |

| 2.1.4           | NBTI Related Models                 |

| 2.2 The         | e Silicon/Silicon Dioxide Interface |

| 2.2.1           | The Silicon Dangling Bonds7         |

| 2.2.2           | Oxide Traps8                        |

| 2.2.3           | Oxide Charges/Interface Traps9      |

| 3 NEGATIVE BI   | AS TEMPERATURE INSTABILITY 10       |

| 3.1 Phy         | vsical Mecahanism of NBTI10         |

| 3.1.1           | Reaction Diffusion Model            |

| 312             | Hydrogen Model                      |

| CF | HAPTER     |                                            | Page |

|----|------------|--------------------------------------------|------|

|    | 3.1.3      | 8 Experimental Setup for NBTI              | 12   |

|    | 3.2 How p- | -MOSFET are different from n-MOSFET        | 13   |

|    | 3.2.1      | Occupancy of Interface Traps               | 13   |

|    | 3.2.2      | 2 Breaking of Si-H Bonds                   | 15   |

|    | 3.2.3      | Surface potential-gate voltage behavior    | 16   |

| 4  | MODELING   | OF NBTI                                    | 18   |

|    | 4.1 N      | Modelling the defects in a PMOS transistor | 18   |

|    | 4.2 N      | Modelling of defects in NMOS transistor    | 23   |

|    | 4.3 V      | alidation and Results                      | 23   |

|    | 4.3.1      | IV characteristics                         | 25   |

|    | 4.3.2      | 2 Threshold Voltage Shift                  | 27   |

|    | 4.4 N      | Modeling Defect Generators                 | 27   |

|    | 4.4.1      | Interface Traps (Dit) Generator            | 28   |

|    | 4.4.2      | 2 Oxide Traps (Not) Generator              | 30   |

|    | 4.5 S      | tatic NBTI                                 | 32   |

|    | 4.6 D      | Oynamic NBTI                               | 33   |

| 5  | NBTI EFFEC | TS IN A CMOS CIRCUITS                      | 34   |

|    | 5.1 C      | CMOS Inverter                              | 34   |

|    | 5.1.       | 1 NBTI Effects in CMOS Inverter            | 36   |

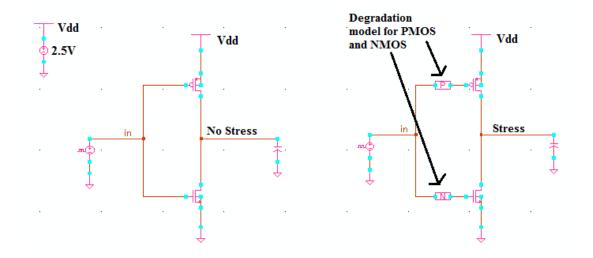

|    | 5.1.       | 2 Inverter with the degradation model      | 37   |

|    | 5.2 R      | ing Oscillator                             | 39   |

| CH  | APTER       | Page |

|-----|-------------|------|

| 6   | CONCLUSION  | 44   |

|     |             |      |

| REF | FRENCES     | 45   |

| API | PENDIX      |      |

|     | A TCAD CODE | 53   |

## LIST OF TABLES

| Tabl | Γable                               |    |

|------|-------------------------------------|----|

| 1.   | Oxide Charges/Interface Traps       | 9  |

| 2.   | Bias Stress Temperature in Inverter | 36 |

| 3.   | Component parameters of Inverter    | 38 |

## LIST OF FIGURES

| Fig | gure |                                                                                                                  | Page |

|-----|------|------------------------------------------------------------------------------------------------------------------|------|

|     | 1.   | Basic n-MOSFET Structure                                                                                         | .2   |

|     | 2.   | Channel Formation in p-Substrate                                                                                 | .3   |

|     | 3.   | Si-SiO2 Interface and Oxide Defect Structure                                                                     | .6   |

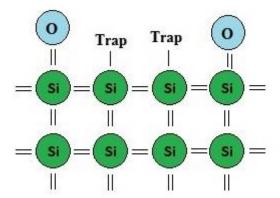

|     | 4.   | The Valence Electrons Forms Active Interface Traps at the Surface                                                | 7    |

|     | 5.   | The Interface Traps Are Reduced after Oxidation                                                                  | .7   |

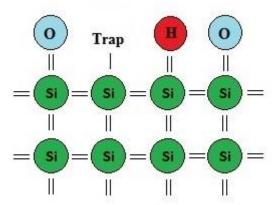

|     | 6.   | The Interface Traps Are More Suppressed after Hydrogen Passivation                                               | .8   |

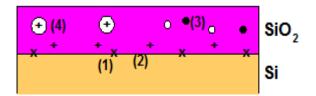

|     | 7.   | Oxide Charges and the Interface Traps                                                                            | .9   |

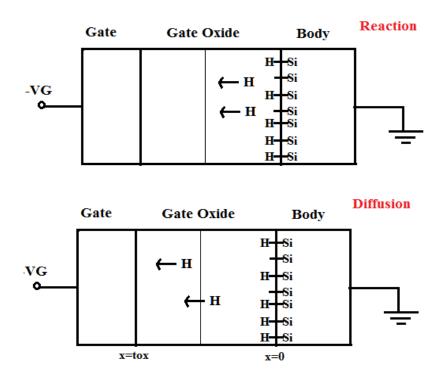

|     | 8.   | Reaction-Diffusion Model                                                                                         | 11   |

|     | 9.   | Hydrogen Model                                                                                                   | 12   |

|     | 10.  | The Setup for NBTI Experiment                                                                                    | 12   |

|     | 11.  | BTI in PMOS and NMOS Transistors                                                                                 | 13   |

|     | 12.  | Band Diagram Showing the Polarities of Interface States                                                          | 14   |

|     | 13.  | Interface Trap Creation Due to Hydrogen [10]                                                                     | 16   |

|     | 14.  | Simulation Setup for PMOS with the Degradation Model                                                             | 19   |

|     | 15.  | Degradation Model Schematic for a PMOS Transistor                                                                | 22   |

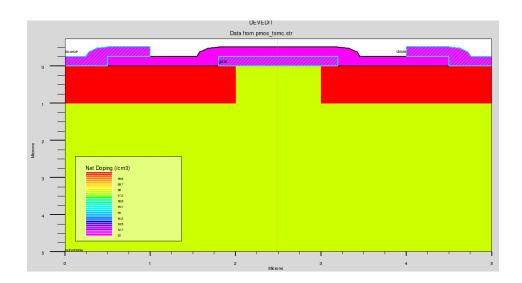

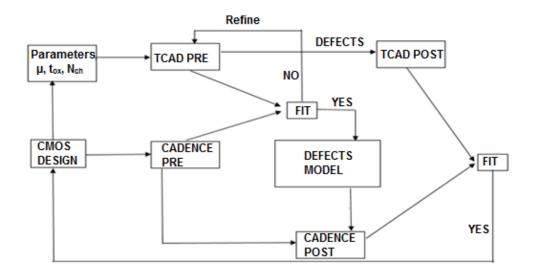

|     | 16.  | p- Channel MOSFET Silvaco Structure                                                                              | 24   |

|     | 17.  | Validation Model Block Diagram                                                                                   | 24   |

|     | 18.  | I-V Curves of PMOS for Not = 0 and Dit = 0.                                                                      | 25   |

|     | 19.  | I-V Curves of PMOS with Not=1.2 x10 <sup>12</sup> cm <sup>-2</sup> and Dit=1x10 <sup>12</sup> cm <sup>-2</sup> 2 | 25   |

|     | 20.  | I-V Curves of PMOS with Not = 0 and Dit = $1 \times 10^{12} \text{ cm}^{-2}$                                     | 26   |

|     | 21.  | I-V Curves of PMOS with Not = $1.2 \times 10^{12}$ cm <sup>-2</sup> and Dit = 0                                  | 26   |

| Figure |                                                                      | Page |

|--------|----------------------------------------------------------------------|------|

| 22.    | Threshold Voltage Before and After the Degradation Model             | 27   |

| 23.    | Threshold Voltage Shift- Defect Model and Vt only                    | 27   |

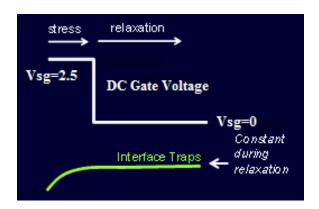

| 24.    | Ideal Response of Interface Traps During Stress and Relax            | 28   |

| 25.    | Nit Defect Generator Schematic                                       | 29   |

| 26.    | Interface Trap Voltage with Time and Gate Bias                       | 30   |

| 27.    | Ideal Response of Oxide Traps During Stress and Relax                | 30   |

| 28.    | Not Defect Generator Schematic                                       | 31   |

| 29.    | Oxide Trap Voltage with Time and Gate Bias                           | 32   |

| 30.    | Static NBTI                                                          | 33   |

| 31.    | Dynamic NBTI                                                         | 33   |

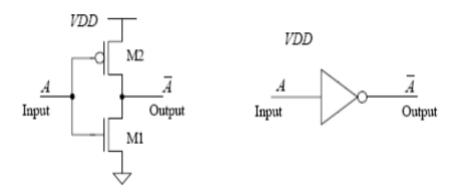

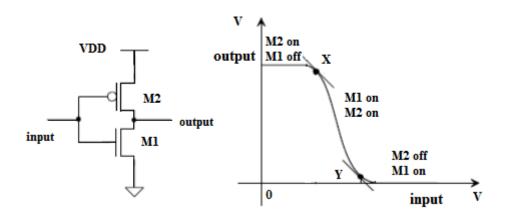

| 32.    | CMOS Inverter                                                        | 34   |

| 33.    | The CMOS Inverter Voltage Transfer Characteristics                   | 35   |

| 34.    | Inverter Propagation Delay                                           | 35   |

| 35.    | CMOS Inverter Degradation                                            | 37   |

| 36.    | CMOS Inverter with and Without Degradation Models                    | 38   |

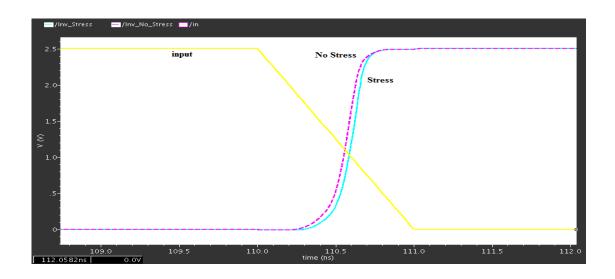

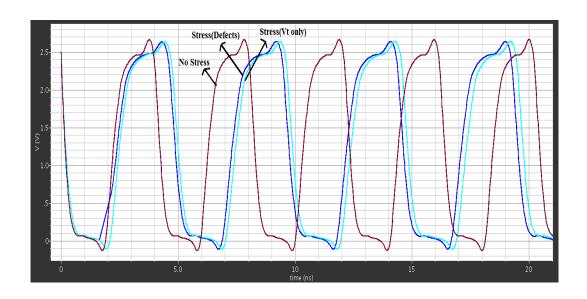

| 37.    | CMOS Inverter Output with and Without Stress                         | 39   |

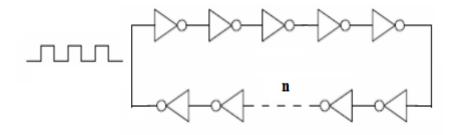

| 38.    | An n-Stage Ring Oscillator                                           | 39   |

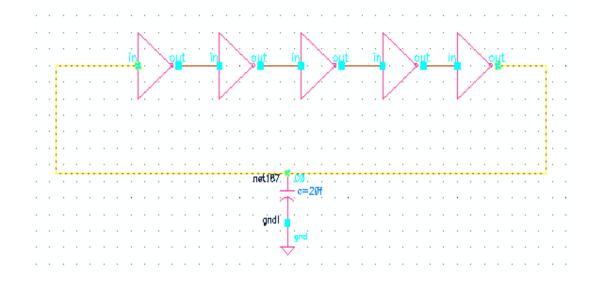

| 39.    | Ring Oscillator Schematic with 25 Inverters                          | 41   |

| 40.    | Ring Oscillator Output Waveform with and Without Stress              | 41   |

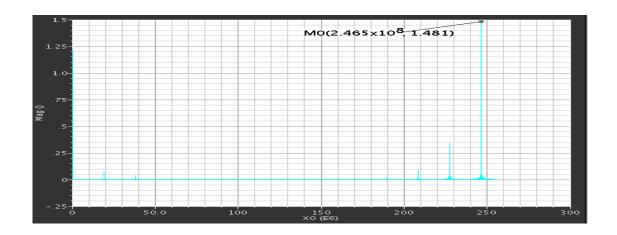

| 41.    | Frequency Response Without Stress                                    | 42   |

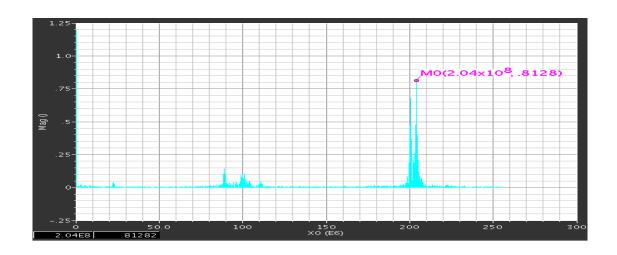

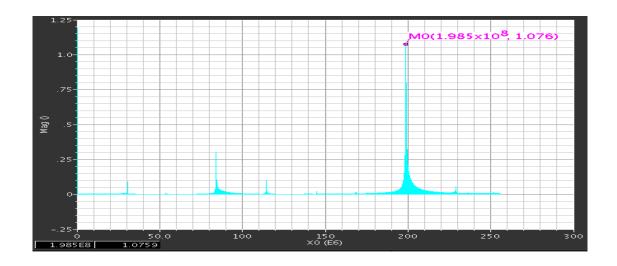

| 42.    | Frequency Response with Stress(Defects Model & V <sub>t</sub> Model) | 42   |

| 43.    | Modeling SET Pulse Broadening                                        | 43   |

| 44.    | SET Pulse Broadening Without and with Stress                         | 43   |

#### LIST OF ABBREVIATIONS

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

nMOSFET n-channel MOSFET

pMOSFET p-channel MOSFET

NBTI Negative Bias Temperature Instability

PBTI Positive Bias Temperature Instability

BTI Bias Temperature Instability

CMOS Complementary Metal—Oxide—Semiconductor

PMOS p-Channel Metal-Oxide-Semiconductor

NMOS n-Channel Metal-Oxide-Semiconductor

D<sub>it</sub> Density of Interface Traps

N<sub>ot</sub> Density of Oxide Traps

DOS Density of States

BTS Bias Temperature Stress

TCAD Technology Computer Aided Design

SET Single Event Transient

#### CHAPTER 1

#### INTRODUCTION

Negative-bias temperature instability (NBTI) is a main reliability issue in MOSFETs. The NBTI effect is more seen in a p-channel MOSFET when stressed with negative gate voltages at elevated temperatures. The NBTI causes the absolute value of threshold voltage to increase and consequent decrease in drain current and decrease of other important parameters like trans-conductance, channel mobility of a MOSFET. The same effects can be seen in n-channel MOSFET's too but the degradation is very less compared to that of a p-channel MOSFET. Therefore it is of immediate concern in p-channel MOS devices, since they almost always operate with negative gate-to-source voltage like in an inverter and ring oscillator.

There are two main types of traps which contribute to NBTI:

- Interface traps: These traps cannot be recovered over a reasonable time of operation. In the case of NBTI, it is believed that the Si–H bonds located at the silicon-silicon dioxide interface are broken when interacted with the protons coming from substrate [42]. The dangling bonds contribute to the threshold voltage degradation.

- Oxide traps: When gate stress is applied, some holes are pulled into the oxide from channel of PMOS. These traps can be emptied when the stress voltage is removed. The threshold voltage degradation can be recovered over time.

A new model to simulate the circuit level degradation subjected to negative bias temperature instability (NBTI) has been developed in this thesis work. A very basic

fundamental ring oscillator circuit is studied to evaluate the impact of NBTI on CMOS digital circuit performances.

The change in threshold voltage is modeled as a defect potential and is applied at gate.

The defects dependence on time and gate voltage is modeled in the defect potential.

#### CHAPTER 2

#### **OVERVIEW OF THE DEFECTS**

Before even discussing about the defects, let us discuss about the basic MOSFET operation like the channel formation, regions of operation and the threshold voltage.

#### 2.1 MOSFET ANALYSIS

### 2.1.1 The Basic MOSFET Operation

A metal—oxide—semiconductor field-effect transistor (MOSFET) is basically a device which controls and modulates the charge by a capacitance between a body terminal and a gate terminal. The gate of the MOSFET is located on the top of the body substrate and it is insulated from other regions by a field oxide, such as silicon dioxide. The body of the MOSFET is generally doped by silicon. The p-channel MOSFET substrate is doped by n-silicon, whereas the n-channel MOSFET substrate is doped by p-silicon. The silicon surface and gate terminal acts like two terminals of the capacitance and the dielectric is silicon dioxide [12].

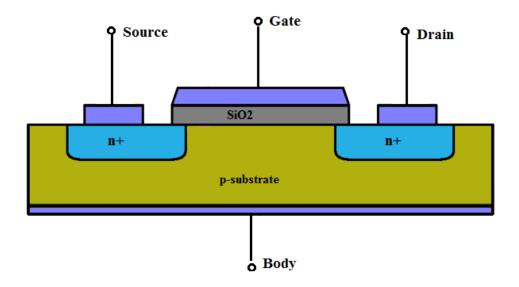

In nMOSFET, the source and drain regions are "n+" type and the body substrate is "p" type silicon as shown in Figure 1. In the case of a pMOSFET, the source and drain are "p+" regions and the body is an "n" region. In pMOSFET, the source and drain regions are "p" type and body substrate is "n" type silicon.

Figure 1: Basic p-MOSFET Structure

Let us see how a channel is formed in an nMOSFET. The same theory applies to pMOSFETs.

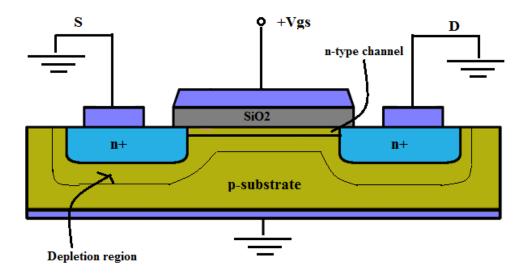

In nMOSFET, the substrate is "p" type where holes are the majority carriers. When a positive voltage is applied to the gate, it repels the positively charged holes away from the substrate. A depletion region is formed when the holes move further deep into the substrate. When the positive voltage is applied at the gate, it attracts electrons from the source and drain which are "n+" regions and have excess of electrons, into the channel region. As the number of electrons accumulate near the surface of the Si-SiO<sub>2</sub>, an n region is in created, connecting the source and drain regions as shown in Figure 2. If a voltage is now applied at the drain of the MOSFET, current starts flowing through this channel. Thus a channel is formed between drain and source and current flows in a MOSFET [13].

Figure 2: Channel Formation in p-Substrate

## 2.1.2 MOSFET Region of Operations

The MOSFET operates in different regions depending on the gate voltage.

Cutoff, Sub threshold, or weak inversion mode:

When  $V_{GS} < V_{th}$ ,

In this region, the transistor is turned off, and there is no current flowing between drain and source. But there is a weak sub threshold current which is exponentially dependent on the gate source voltage [12].

$$I_{D} = I_{D0} e^{\frac{(V_{GS} - V_{th})}{nV_{T}}} \tag{1}$$

Where  $I_{D0}=$  current at  $V_{GS}=V_{th}$ , the thermal voltage  $V_T=kT/q$  and the slope factor n is given by

$$n=1+\frac{c_D}{c_{ox}} \tag{2}$$

Where  $C_D$  = capacitance of the depletion layer and  $C_{ox}$  = capacitance of the oxide layer. This equation is generally used, but is only an adequate approximation for the source is connected to the body.

Triode mode or linear region:

When

$$V_{GS} > V_{th}$$

,  $V_{DS} < V_{GS} - V_{th}$

In this region the transistor is turned on, and a channel has been formed allowing the current to flow from drain to source. The MOSFET operates like a resistor, controlled by the gate voltage relative to both the source and drain voltages.

The drain current is,

$$I_{ds} = \mu C_{ox} \frac{W}{L_{eff}} (V_{gs} - V_{th} - \frac{V_{ds}}{2}) (1 + \lambda V_{ds})$$

(3)

Where  $\mu$  is the effective mobility, W is the width of the device,  $L_{eff}$  is the effective gate length and  $\lambda$  is the channel length modulation parameter.

In Saturation region, where

$$V_{gs} > V_{th}$$

and  $V_{ds} > V_{gs} - V_{th}$

The transistor is turned on, and a channel has been created, which allows current to flow between the drain and source [12].

The drain current is,

$$I_{ds} = \frac{1}{2} \mu C_{ox} \frac{W}{L_{eff}} (V_{gs} - V_{th})^2 (1 + \lambda V_{ds})$$

(4)

The threshold voltage of a MOSFET is given by the equation (5)

$$V_{th} = V_{To} + \gamma (\sqrt{2\phi_B - V_{BS}} - \sqrt{2\phi_B}) + \frac{Q_{it} + Q_{ox}}{C_{ox}}$$

(5)

Where  $V_{To}$  is the threshold voltage when  $V_{BS}=0$ ,  $C_{ox}$  is the capacitance per unit area of the oxide,  $Q_{it}$  is the interface charge,  $Q_{ox}$  is the oxide charge and  $\gamma$  is the body-effect parameter, defined as

$$\gamma = \frac{\sqrt{2\varepsilon_{S}q_{o}N_{A}}}{C_{ox}} \tag{6}$$

Here,  $\epsilon_s$  is the permittivity of the silicon substrate and  $N_A$  the acceptor doping concentration. The potential in the neutral p-type region  $\phi_B$  is evaluated as

$$\phi_{\rm B} = \frac{KT}{q} \ln \frac{N_A}{n_i} \tag{7}$$

During NBTI, the interface defects and oxide traps will be formed which degrades the performance of the transistor and the threshold voltage is shifted by  $\Delta V_{th}$  obtained from (5)

#### 2.1.3 Interface and Oxide Charges

The threshold voltage shift ( $\Delta V_{th}$ ) is contributed mainly because of the changes in interface and oxide charges ( $\Delta Q_{it}$  and  $\Delta Q_{ox}$ ) and is given by,

$$\Delta V_{th} = \frac{\Delta Q_{it} + \Delta Q_{ox}}{C_{ox}} \tag{8}$$

In the context of NBTI interface charges are usually the result of charged interface defects  $D_{it}$ . The interface charge depends on the Fermi-level  $E_F$  and the trap occupancy f and can be calculated as [43]

$$Q_{it} = q \int_{E_o}^{E_c} D_{it}(E) f(E_f, E) dE.$$

(9)

Charged oxide traps  $D_{ox}$  contribute to the threshold voltage shift depending on their position in the dielectric. The resulting, effective,  $Q_{ox}$  can be evaluated as

$$Q_{ot} = q \int_0^{t_{ox}} \rho(x) \frac{x}{t_{ox}} dx, \qquad (9)$$

where  $t_{ox}$  is the oxide thickness.

#### 2.1.4 NBTI Related Models

The important parameter which changes because of NBTI is the trans-conductance  $(g_m)$ . As the drain current changes with the trapped charges, so does the trans-conductance.

$$g_{\rm m} = \frac{\Delta I_d}{\Delta V_g} \tag{11}$$

Devine et al. proposed a trans-conductance shift versus interface trap  $(N_{it})$ , relation as [45]

$$\Delta g_{\rm m} = g_{\rm mo} \frac{\alpha N_{it}}{1 + \alpha N_{it}} \tag{12}$$

Where  $\alpha$  is a processing related parameter.

The mobility model proposed by Devine et al. [45] is

$$\mu = \frac{\mu_0}{1 + \alpha N_{it}} \tag{13}$$

Therefore the mobility and trans-conductance decreases with increase in the interface traps. The NBTI also increase the threshold voltage. Decrease in carrier mobility and

trans-conductance and increase in absolute value threshold voltage leads to the reduction of drain current and the performance of the transistor is degraded [20].

#### 2.2 The Silicon/Silicon Dioxide Interface

One of the most important things that led to the enormous success and continuous improvement of the CMOS technology are the excellent properties of the thermally grown  $Si/SiO_2$  interface.

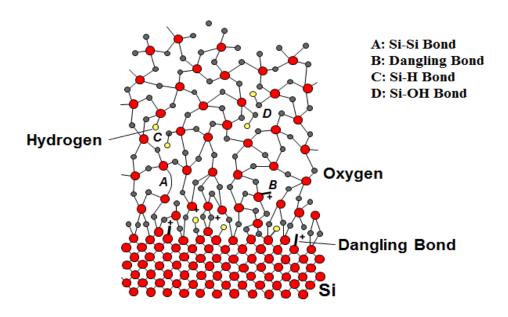

Figure 3: Si-SiO2 Interface and Oxide Defect Structure [53]

Silicon dioxide (SiO<sub>2</sub>) is formed when the silicon surface is exposed to oxygen. This process is called oxidation. Silicon dioxide is a very good electrical insulator and hence we use it for the electrical isolation of the devices, and also as a component in MOS transistors. It acts like a dielectric in the MOS capacitance, the two plates being

the gate and body electrodes. Figure 3 shows the Si/SiO<sub>2</sub> interface and various types of bonds that exist at the interface and in the oxide.

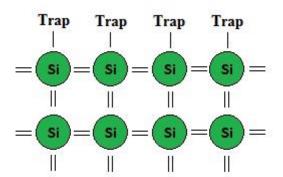

### 2.2.1 Silicon Dangling Bonds

The silicon atom has four valence electrons and hence it wants to bond with four atoms to be stable. In the silicon crystal each silicon atom bonds with four other silicon atoms but at the surface there are no silicon atoms to bond with and hence traps are formed as shown in Figure 4. The density of these interface states,  $D_{it}$  is approximately  $10^{14}$  cm<sup>-2</sup> eV<sup>-1</sup>. When the silicon surface is oxidized, some of the silicon atoms at the surface are bonded with the oxygen atoms as shown in Figure 5. The density of interface traps then reduces a bit and is approximately  $D_{it} = 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> [46].

Figure 4: The Valence Electrons Forms Active Interface Traps at the Surface.

Figure 5: The Interface Traps are Reduced After Oxidation.

Figure 6: The Interface Traps are More Suppressed After Hydrogen Passivation.

There can still be a lot of defects present which causes the circuit degradation. So it is very important that the defects need to be reduces and passivated at the interface in a transistor. The interface traps causes degradation of transistor parameters like the threshold voltage, the trans-conductance, the on-current, and the carrier mobility at device level and increases the delay time at circuit level. These interface traps can be reduced more by annealing the surface with hydrogen gas. The remaining silicon dangling bonds react with hydrogen forming Si-H bonds and thus the defects are reduced to more extent. After the hydrogen passivation the density of interface defects

can be reduced to around  $D_{it}=10^{10}\,\text{cm}^{-2}\text{eV}^{-1}$  [46]. These Si-H bonds can break at high temperatures or with the negative gate stress, forming interface traps [22] as discussed in the further sections.

### 2.2.2 Oxide Traps

Oxygen vacancies are the major hole trapping mechanisms. Because of the manufacturing defects, oxygen vacancies are formed in the oxide which traps the positively charged holes. When the Si-H bonds break with the gate stress or at high temperatures, the hydrogen atoms diffuse into the oxide and holes can be trapped [22]. When the gate stress is applied, there will be an electric field in vertical direction which causes the holes to be trapped. The threshold voltage is degraded because of the charge accumulated by these holes in the oxide. When the stress is removed, the oxide traps will be annealed and the threshold voltage can be annealed up to some extent.

The mechanisms for the formation of interface traps and oxide traps are discussed in the further sections.

## 2.2.3 Oxide Charges/Interface Traps

Figure 7: Oxide Charges and the Interface Traps [53]

Table 1 gives more details like the causes and effects of the oxide charges and interface traps which were shown in Figure 7.

Table 1: Oxide Charges/Interface Traps [53]

| Charge                               | Type      | Location             | Cause           | Effect on Devices    |

|--------------------------------------|-----------|----------------------|-----------------|----------------------|

|                                      |           |                      |                 |                      |

| (1)                                  | Interface | SiO <sub>2</sub> /Si | Dangling        | Junction Leakage     |

| $D_{it}(cm^{-}2eV^{-1}),$            | Trap      | Interface            | Bonds           | Current Noise,       |

| $N_{it}, Q_{it}$                     | Charge    |                      |                 | Threshold Voltage    |

|                                      |           |                      |                 | Shift, Sub Threshold |

|                                      |           |                      |                 | Slope                |

| (2)                                  | Fixed     | Close to             | Si <sup>+</sup> | Threshold Voltage    |

| $N_f$ , $Q_f$                        | Charge    | SiO <sub>2</sub> /Si |                 | Shift                |

| cm <sup>-2</sup> , C/cm <sup>2</sup> |           | Interface            |                 |                      |

| (3)                                  | Oxide     | In SiO <sub>2</sub>  | Trapped         | Threshold Voltage    |

| $N_{ot}$ , $Q_{ot}$                  | Trapped   |                      | Electrons       | Shift                |

|                                      | Charge    |                      | and             |                      |

|                                      |           |                      | Holes           |                      |

| N <sub>m</sub> , Q <sub>m</sub>      | Mobile    | In SiO <sub>2</sub>  | Na, K, Li       | Threshold Voltage    |

|                                      | Charge    |                      |                 | Shift                |

|                                      |           |                      |                 |                      |

In this work, only interface trap charges and oxide trap charges are considered and their time dependence and gate voltage dependence are modeled to simulate the impact of NBTI at circuit level.

#### CHAPTER 3

## NEGATIVE BIAS TEMPERATURE INSTABILITY (NBTI)

Bias temperature instability (BTI) is a degradation phenomenon affecting mainly MOS field effect transistors. The highest impact is observed in p-MOSFETs. Either Negative voltages or high temperatures can cause NBTI, but a faster and stronger effect is produced with negative stress and high temperature together. The stress conditions for this negative bias temperature instability (NBTI) typically lie below 6MV/cm for the gate oxide electric field and temperatures ranging 100-250 °C. A very interesting thing about NBTI is its capability to anneal to a certain extent when the stress is removed [18].

The important transistor parameters which degrade because of NBTI are:

- Trans-conductance (g<sub>m</sub>) decreases

- $\bullet \quad \mbox{Linear drain current and saturation current } (I_{dsat}) \mbox{ decreases}$

- Channel mobility ( $\mu_{eff}$ ) decreases

- Sub-threshold slope (S) decreases

- Absolute value of the threshold voltage (V<sub>th</sub>) increases

At the circuit level the switching speeds are reduced and the delay times are increased as the charging time for load capacitances or the parasitic capacitances are increased.

The NBTI is first reported many years ago [49], but gained much attention in recent years [3, 11, 18, 48] due to modern semiconductor technologies.

The following aspects are the main factors that lead to the increasing NBTI [20]:

- higher oxide electric fields due to oxide scaling

- higher temperatures due to higher power dissipation

- high performance IC's during routine operation

## 3.1 Physical Mechanisms of NBTI

The negative bias temperature instability (NBTI) effect has been reported many years ago by several groups [49, 50, 51], there is still a lot to understand the exact mechanisms behind the NBTI degradation. The general theory says that when MOSFETs are stressed with a gate voltage at an elevated temperature, charge builds up because of the interface traps and the oxide traps at the interface and oxide respectively. This charge leads to degradation of the transistor performance [20]. PMOS transistors are more susceptible to the degradation as they always operate with negative gate source voltage.

#### 3.1.1 Reaction Diffusion Model

The reaction-diffusion (R-D) model is been proposed by several groups [7, 8, 9] states that when a p-MOSFET is in strong inversion, the holes in the inversion layer reacts with Si-H bonds at the Si-SiO<sub>2</sub> interface and weakens the bonds. At high temperatures, these Hydrogen bonds dissociate forming active interface traps (N<sub>it</sub>). Initially the generation rate of interface traps depends on the dissociation of the Si-H bonds. This process is reaction. Later the generation of interface traps depends on the

diffusion of hydrogen atoms. This is the diffusion step [22]. Figure 8 shows the reaction diffusion model for NBTI.

Figure 8: Reaction-Diffusion Model

$$\frac{dN_{it}}{dt} = K_f(N_{Si-H} - N_{it}) - K_r N_{it} N_H(x=0)$$

(14)

Where  $K_f$ ,  $K_r$ ,  $N_{Si-H}$  and  $N_H(x=0)$  are bond-breaking rate, hydrogen annealing rate, Si-H density before stress and hydrogen density at the interface respectively [22].

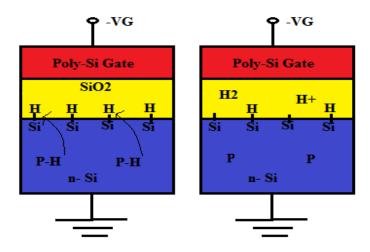

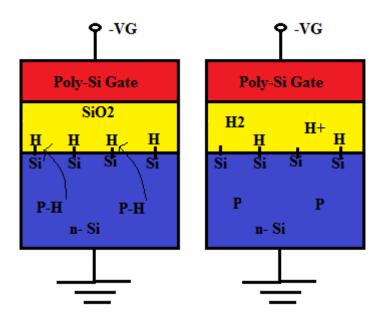

## 3.1.2 Hydrogen Model

The hydrogen atoms from the Si substrate migrate to the  $Si/SiO_2$  interface. These hydrogen atoms are produced when the Phosphorous-Hydrogen bonds (n-

substrate) or the Boron-Hydrogen bonds (p-substrate) break. The hydrogen atoms when migrating towards are the interface traps a hole and becomes  $H^+$ . The positive hydrogen atoms depassivate the Si-H bonds at the Si/SiO<sub>2</sub> interface forming  $H_2$  and an interface trap [42] as shown in Figure 9. In the process, some  $H^+$  can go into the oxide, hence forming oxide traps ( $N_{ot}$ ).

$$Si_3 \equiv Si - H + H^{\dagger} = Si_3 \equiv Si \cdot + H_2$$

(15)

Si• is a dangling bond.

Figure 9: Hydrogen Model [18]

When the stress is removed the  $H_2$  can passivate the dangling bonds and the degradation is reduced.

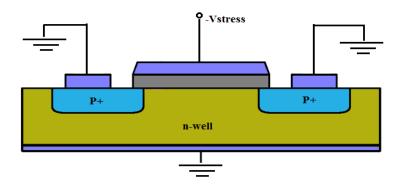

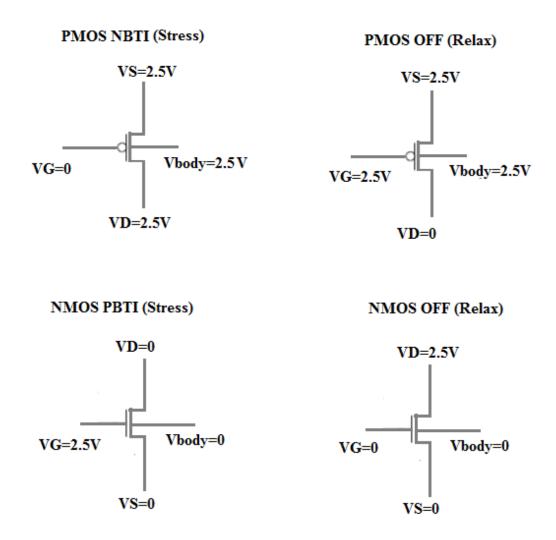

## 3.1.3 Experimental Setup for NBTI

The gate is biased with a negative voltage, while the drain, source, and bulk are grounded.

Figure 10: The Setup for NBTI Experiment.

The set-up for the negative bias temperature instability (NBTI) at a device level is shown in Figure 10. The bulk of the transistor is grounded. The source and drain contacts are also grounded. A negative gate voltage stress is applied to the gate at elevated temperatures, typically ranging between 100 and 250 °C, for a certain period of time. To measure the degradation, the threshold voltage can be measured by plotting the drain current with respect to source gate voltage.

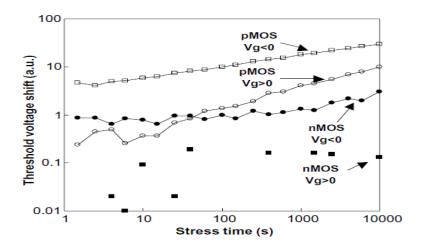

## 3.2 How p-MOSFET are different from n-MOSFET

NBTI is observed both in PMOS and NMOS transistors; however PMOS shows more degradation in their performance compared to the NMOS. Figure 11, presenting data from Huard et al. [3], shows that the threshold voltage degradation is more in PMOS transistors with negative gate voltage stress. When a positive gate voltage is applied to PMOS, the degradation is very less compared to that of negative voltage stress and also the effects in NMOS transistors for both positive and negative voltage are less too.

Figure 11: BTI in PMOS and NMOS Transistors [3].

In the next sections we will discuss the other possible reasons for the different degradation performance in PMOS and NMOS transistors.

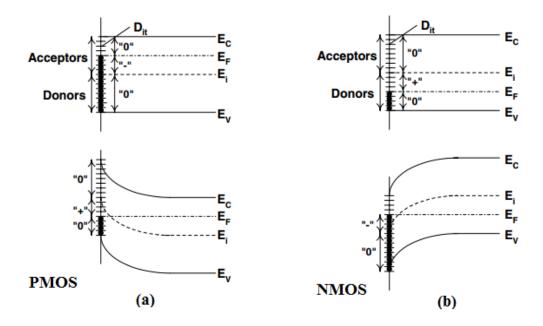

### 3.2.1 Occupancy of Interface Traps

A donor trap can be either positive or neutral. A donor trap is positively charged when empty and neutral when filled. An acceptor trap can be either negative or neutral. An acceptor trap is neutral when empty and negatively charged when filled. The donor traps usually lie near the valence band and the acceptor traps usually lie near the conduction band. Figure 12 shows the polarities of the interface trap charge in both PMOS and NMOS transistors. The lines are the energy states of interface traps and the solid ones are filled energy states. The charge state of the interface traps depends on the Fermi level. All the energy states below the Fermi level are filled. The charge polarity of the interface traps at the Si/SiO<sub>2</sub> interface in inversion is important as the threshold voltage depends on this charge [10].

Figure 12: Band Diagram Showing the Polarities of Interface States. (a) n- Substrate at Flat Band and in Inversion. (b) p-Substrate at Flat Band and in Inversion. [10]

In the case of a PMOS, it's an n substrate. At flat band the acceptor traps are filled and hence it's negatively charged. In inversion, the Fermi level is below the intrinsic energy level and hence the donor traps are empty which means it is positively charged as shown in Figure 12(a). Hence for an n-substrate in inversion, the charge because of interface traps is positive [10].

$$Q_{Dit} = + Q_{it} \tag{16}$$

In the case of an NMOS the situation is different. Figure 12(b) shows the energy diagram of an NMOS in flat band and in inversion. At the flat band, the donor traps are empty and hence it is positively charged but in inversion, the Fermi level is above the intrinsic energy level. So the acceptor traps are filled and hence negatively charged. Hence in inversion the net charge because of interface traps for p-substrate is negative [10].

$$Q_{Dit} = -Q_{it} \tag{17}$$

The Oxide traps are mainly because of the holes getting trapped in the oxide. In both NMOS and PMOS the mechanism is the same that is the hole gets trapped in oxide and hence it is positively charged in both cases. Therefore the charge contribution because of oxide traps is almost same in both PMOS and NMOS and it is positive.

$$Q_{\text{Not}} = + Q_{\text{ot}} \tag{18}$$

So when we add the net charge contributions caused by interface traps and oxide traps for PMOS and NMOS, we get

$$Q_{total} = Q_{Dit} + Q_{Not}$$

(19)

For PMOS,

$$Q_{\text{total}} = Q_{\text{it}} + Q_{\text{ot}} \tag{20}$$

For NMOS,

$$Q_{\text{total}} = -Q_{\text{it}} + Q_{\text{ot}} \tag{21}$$

In PMOS, the interface traps and the oxide traps contribute to the threshold voltage shift whereas in NMOS the interface traps reduces the shift caused by the oxide traps and the effect of NBTI is therefore less seen in NMOS compared to PMOS devices.

## 3.2.2 Breaking of Si-H Bonds

Tsetseris et al. [42] proposed a model explaining the different degradation behavior in p-MOSFETs and n-MOSFETs. The positively charged hydrogen or

proton,  $H^+$  is responsible for the breaking of Si-H bonds at the interface. The hydrogen is originated from the phosphorous-hydrogen bonds in the n-substrate in the case of a p-MOSFET. The hydrogen atom then picks up a hole to form  $H^+$  and then reacts with the Si-H bond at the interface to form  $H_2$  and leaved behind a silicon dangling bond which is an interface trap and the  $H_2$  diffuses into the oxide as shown in Figure 13.

Figure 13: Interface Trap Creation Due to Hydrogen [10]

When the stress is removed, the  $H_2$  can diffuse back to the interface and hence passivate the silicon dangling bond.

The activation energy for dissociation of P-H bonds is usually high. The bonds can be broken only in the depletion region. During negative bias stress a p-MOSFET is in strong inversion and a depletion region is formed in the substrate. Hydrogen atoms can break and cause degradation at the interface. But when there is a positive stress depletion region is not formed. Therefore the protons are not available from the P-H bonds, and the interface traps are not formed.

In the n-MOSFET the substrate is doped with boron and it is more difficult to break the boron-hydrogen bonds as their binding energy is much higher.

### 3.2.3 Surface potential-gate voltage behavior

The different degradation behavior of p- and n-channel MOSFETs can be because the gate voltages can be different for a given oxide electric field [18].

The Fermi-level of a p-type poly gate lies approximately at the valence band edge  $E_F$  =  $E_V$  while the Fermi-level of an n-type poly gate is located at the conduction band edge energy  $E_F$  =  $E_C$ . For NBT stress the p-type poly gate of the p-channel device is depleted while the n-type poly gate of the n-channel device is driven into accumulation.

Oxide and interface charges generated by NBTI degradation further shift the relevant gate voltages.

This asymmetry in n-type and p-type gate contacts, the oxide electric fields are not the same for a given gate voltage and at a given oxide electric field the gate voltages are different. This effect has to be accounted while comparing between p-channel MOSFET's and n-channel MOSFET's [20].

#### **CHAPTER 4**

#### MODELING OF NBTI

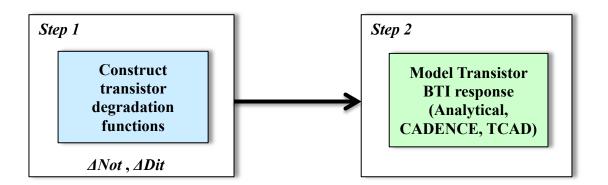

As we have discussed in previous sections, charge build up with the defects and which degrades the threshold voltage of the transistor. A model has been developed for simulating impact of Negative Bias Temperature Instability (NBTI) at circuit level.

## 4.1 Modelling the defects in a PMOS transistor

If  $\Delta N_{ot}$  and  $\Delta D_{it}$  are able to be measured experimentally as a function of bias stress and time, their effects be simulated in Cadence at the circuit level

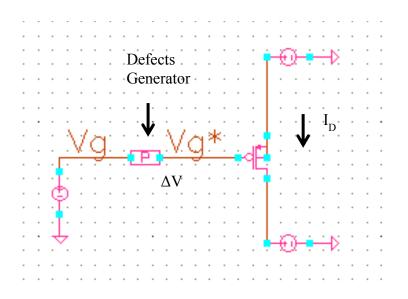

The approach is to utilize external voltages ( $\Delta V$ ) in series with the transistor gate stimulus that mimic effects of time and bias dependent defects.

The degradation model is developed using the drain current equation in the sub threshold region. The sub threshold model works for strong inversion too with slight modifications.

$$I_{D,pre} \propto \exp\left(\frac{V_{SG} - V_{t,pre}}{m\phi_t}\right)$$

(22)

$$I_{D,pst} \propto \exp\left(\frac{V_{SG} - V_{t,pst}}{m\phi_t}\right)$$

(23)

where

$$V_{t,pst} = -\Delta V + V_{t,pre}$$

(24)

$$I_{D,pst} \propto \exp\left(\frac{V_{SG} + \Delta V - V_{t,pre}}{m\phi_t}\right)$$

(25)

$$I_{D,pst} \propto \exp\left(\frac{V_{SG} * - V_{t,pre}}{m\phi_t}\right)$$

(26)

where

$$V_G^* = V_G - \Delta V$$

(27)

Figure 14: Simulation Setup for PMOS with the Degradation Model

Figure 14 shows the simulation setup for PMOS transistor.  $\Delta V$  is the defect potential.

From (19), we know that for a PMOS transistor the total charge accumulated because of the interface traps and oxide charge is

$$Q_{total} = Q_{ot} + Q_{it} \tag{28}$$

Therefore

$$\Delta V = -\frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}(\psi_S - \phi_B)}{C_{ox}}$$

(29)

$$\Delta V = -\frac{qN_{ot}}{C_{ox}} + \frac{qD_{it}\phi_B}{C_{ox}} - \frac{qD_{it}\psi_S}{C_{ox}}$$

(30)

From (43)

$$\psi_{\rm S} \approx \frac{C_{ox}}{C_{dm} + \xi C_{ox}} \left( V_{t,pst} - V_G \right) + 2\phi_B$$

where

$$\xi = 1 + \frac{qD_{it}}{C_{or}} \tag{31}$$

and  $\psi_{\rm S} - 2\phi_{\rm B}$  is small

$$\therefore \Delta V \approx -\frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}\phi_B}{C_{ox}} - \frac{qD_{it}}{C_{dm} + \xi C_{ox}} \left(V_{t,pst} - V_G\right)$$

(32)

Now

$$V_{t,pst} \approx -\frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}\phi_B}{C_{ox}} + V_{t,pre}$$

(33)

So

$$\Delta V \approx -\frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}\phi_B}{C_{ox}} - \frac{qD_{it}}{C_{dm} + \xi C_{ox}} \left( -\frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}\phi_B}{C_{ox}} + V_{t,pre} - V_G \right)$$

(34)

The derivation for surface potential ( $\psi_s$ )

$$V_G = V_{FB} - \xi \psi_S - \gamma \sqrt{\psi_S} \tag{35}$$

if

$$\psi_S = 2\phi_B - \Delta\psi$$

and  $\Delta\psi << 2\phi_B$

$$V_G = V_{FB} - \xi (2\phi_B - \Delta\psi) - \gamma \sqrt{2\phi_B - \Delta\psi}$$

(36)

$$V_G = V_{FB} - \xi (2\phi_B - \Delta \psi) - \gamma \sqrt{2\phi_B} \sqrt{1 - \frac{\Delta \psi}{2\phi_B}}$$

(37)

$$V_G \approx V_{FB} - \xi \left(2\phi_B - \Delta\psi\right) - \gamma \sqrt{2\phi_B} \left(1 - \frac{1}{2} \frac{\Delta\psi}{2\phi_B}\right)$$

(38)

$$V_G \approx V_{FB} - \xi (2\phi_B) + \xi \Delta \psi - \gamma \sqrt{2\phi_B} + \gamma \frac{1}{2} \frac{\Delta \psi}{\sqrt{2\phi_B}}$$

(39)

$$V_G \approx V_{th} + \xi \Delta \psi + \gamma \frac{1}{2} \frac{\Delta \psi}{\sqrt{2\phi_B}} \tag{40}$$

$$V_G \approx V_{th} + \xi \left(2\phi_B - \psi_S\right) + \frac{C_{dm}}{C_{ox}} \left(2\phi_B - \psi_S\right) \tag{41}$$

where,

$$C_{dm} = \sqrt{\frac{\varepsilon_{\rm s} q N_{\rm a}}{4\phi_{\rm B}}} \tag{42}$$

$$\therefore \psi_S \approx \frac{\left(V_{th} - V_G\right)}{\xi + \frac{C_{dm}}{C_{dm}}} + 2\phi_B = \frac{C_{ox}}{C_{dm} + \xi C_{ox}} \left(V_{th} - V_G\right) + 2\phi_B \tag{43}$$

We know that

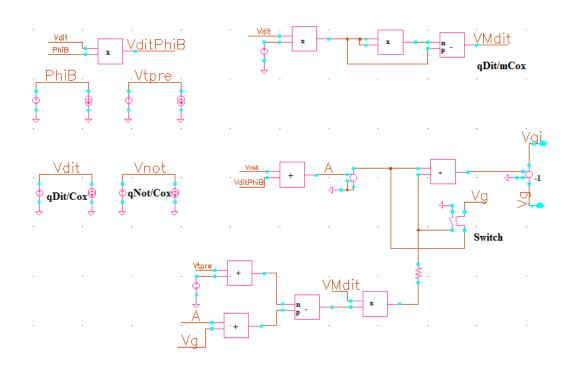

$$\frac{qD_{it}}{C_{dm} + \xi C_{ox}} = \frac{qD_{it}}{C_{dm} + C_{ox} + qD_{it}} = \frac{qD_{it}/(C_{dm} + C_{ox})}{1 + qD_{it}/(C_{dm} + C_{ox})} = \frac{qD_{it}}{mC_{ox}}$$

(44)

If,  $qD_{it} \ll C_{dm} + C_{ox}$ , so using Tylor series

$$\frac{qD_{it}}{mC_{ox}} \approx qD_{it} / (C_{dm} + C_{ox}) - [qD_{it} / (C_{dm} + C_{ox})]^2$$

(45)

The function  $\frac{qD_{it}}{mC_{ox}}$  is a rational function, so it is approximated.

$$\Delta V \approx -\frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}\phi_B}{C_{ox}} + \frac{qD_{it}}{mC_{ox}} \left( V_{GB} - V_{t,pre} + \frac{qN_{ot}}{C_{ox}} + \frac{qD_{it}\phi_B}{C_{ox}} \right)$$

(46)

In Strong Inversion,

For  $V_{SG} \ge V_{t,post}$

$$\Delta V(V_G) \approx -\frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}\phi_B}{C_{ox}} + \frac{qD_{it}}{mC_{ox}} \left( V_{GB} - V_{t,pre} + \frac{qN_{ot}}{C_{ox}} + \frac{qD_{it}\phi_B}{C_{ox}} \right)$$

The terms crossed out should be shorted out with a switch.

The shift  $\Delta V$  in threshold voltage should be fixed to

$$\Delta V \approx -\frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}\phi_B}{C_{ox}} \tag{47}$$

This captures the fact that in strong inversion the surface potential is "pinned" at  $\phi_{B.}$ Thus the threshold voltage shift shows no more dependence on  $V_{G.}$

For the 0.25u tsmc technology,

Oxide Thickness  $t_{ox} = 5.8$ nm.

Threshold Voltage  $V_{THo} = 0.4308V$ .

Substrate Doping  $N_{CH} = 2.35 \times 10^{17} \text{ cm}^{-3}$ .

Therefore Bulk potential  $\phi_B = \frac{kT}{q} \ln \left( \frac{N_{CH}}{n_i} \right) = 0.456 \text{V}.$

$$C_{dm} = \sqrt{\frac{\epsilon_s q N_a}{4 \varphi_B}} = 4.8 x 10^{-7} \ F/cm^2.$$

Figure 15 shows the degradation model developed in cadence.

Figure 15: Degradation Model Schematic for a PMOS Transistor

#### 4.2 Modelling of defects in NMOS transistor

The same approach used for PMOS applies for NMOS transistor too with slight changes as shown below.

The total charge accumulated because of defects in NMOS from (21) is

$$Q_{total} = Q_{ot} - Q_{it}$$

Therefore the threshold voltage shift is

$$\Delta V = -\frac{qN_{ot}}{C_{ox}} + \frac{qD_{it}(\psi_s - \phi_B)}{C_{ox}}$$

(48)

After substituting for surface potential and solving for  $\Delta V$ , we get the defect potential as

$$\Delta V \approx -\frac{qN_{ot}}{C_{ox}} + \frac{qD_{it}\phi_B}{C_{ox}} + \frac{qD_{it}}{mC_{ox}} \left( V_G - V_{t,pre} + \frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}\phi_B}{C_{ox}} \right)$$

(49)

In Strong Inversion,

For  $V_{GS} \ge V_{t,post}$

$$\Delta V(V_G) \approx -\frac{qN_{ot}}{C_{ox}} + \frac{qD_{it}\phi_B}{C_{ox}} + \frac{qD_{it}}{mC_{ox}} \left( V_G - V_{t,pre} + \frac{qN_{ot}}{C_{ox}} - \frac{qD_{it}\phi_B}{C_{ox}} \right)$$

The crossed out terms are shorted out with a switch in strong inversion.

The shift  $\Delta V$  in threshold voltage should be fixed to

$$\Delta V \approx -\frac{qN_{ot}}{C_{ox}} + \frac{qD_{it}\phi_B}{C_{ox}}$$

(50)

#### 4.3 Validation and Results

The PMOS transistor is modelled in Silvaco (Atlas) as shown in Figure 4.3. The model parameters are taken from the compact models of 0.25u CMOS technology and then the I-V characteristics of a transistor are compared both in Cadence  $(0.25\mu)$  and TCAD. Once both the curves fit each other, the degradation model is developed in cadence according to the equation (46). The degradation block is then inserted before the gate of the transistor and the post stress simulations are done. Similarly in TCAD the post stress simulations are done with the interface and oxide traps and the I-V characteristics are compared till both fit each other. The block diagram for validating the degradation model with TCAD is shown in Figure 16. We validate the model by fitting the IV curves in cadence model and in TCAD simulations. The comparison is done for four different values of interface and oxide traps. The same process is repeated for NMOS transistor.

Figure 16: p- Channel MOSFET Silvaco Structure

Figure 17: Validation Model Block Diagram

The model parameters for the TCAD structure are taken from the compact model of tsmc 0.25u technology. Figure 17 shows the block diagram of validating the model.

### 4.3.1 IV characteristics

The current voltage characteristics are plotted when the gate voltage is swept from 2.5V to 0.

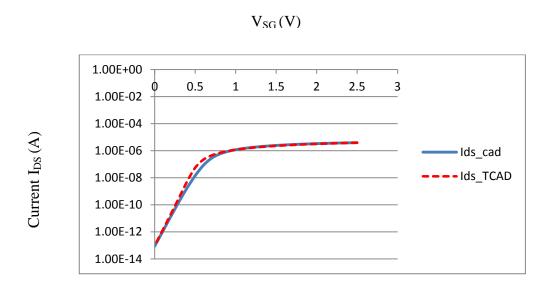

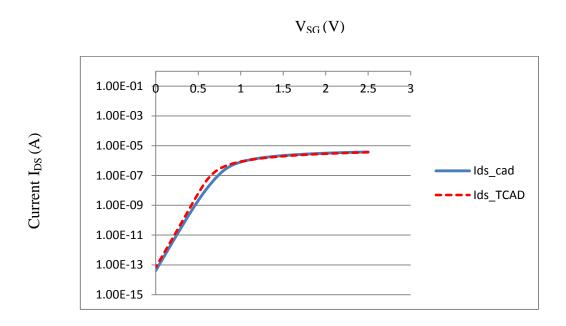

# (a) For $N_{ot} = 0$ and $D_{it} = 0$

Figure 18: I-V Curves of PMOS for  $N_{\text{ot}} = 0$  and  $D_{\text{it}} = 0$ .

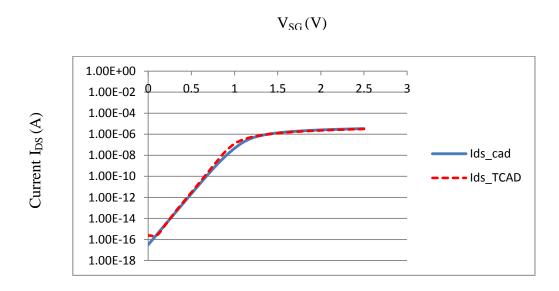

(b) For  $N_{ot} = 1.2 \ x \ 10^{12} \ cm^{\text{--}2}$  and  $D_{it} = 1 \ x \ 10^{12} \ cm^{\text{--}2}$

Figure 19: I-V Curves of PMOS with  $N_{ot} = 1.2 \ x \ 10^{12} \ cm^{-2}$  and  $D_{it} = 1 \ x \ 10^{12} \ cm^{-2}$ .

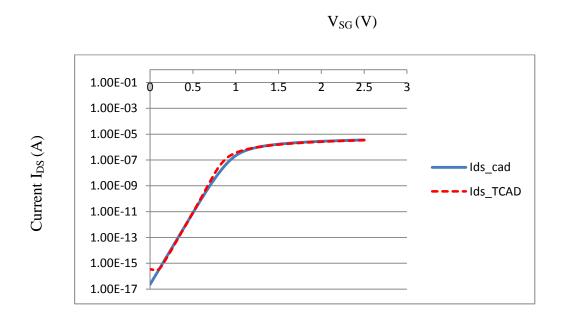

(c) For  $N_{ot}=0$  and  $D_{it}=1\ x\ 10^{12}\ cm^{\text{-}2}$

Figure 20: I-V Curves of PMOS with  $N_{ot} = 0$  and  $D_{it} = 1 \ x \ 10^{12} \ cm^{-2}$ .

(d) For  $N_{\text{ot}}=1.2~\text{x}~10^{12}~\text{cm}^{\text{--}2}$  and  $D_{\text{it}}=0$

Figure 21: I-V Curves of PMOS with  $N_{\text{ot}} = 1.2 \ x \ 10^{12} \ \text{cm}^{\text{--}2}$  and  $D_{\text{it}} = 0.$  34

As we see from the above curves, the I-V characteristics of the PMOS closely fit each other in cadence and TCAD. The comparison is made first without any defects and then with defects for four different cases. In all the cases the degradation model mimics the defects very well.

### 4.3.2 Threshold Voltage Shift

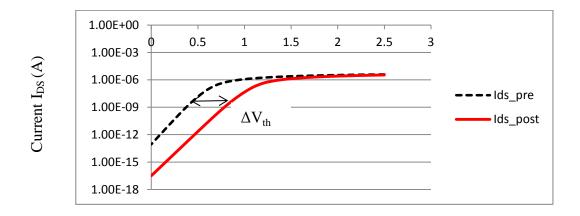

$V_{SG}(V)$

Figure 22: Threshold Voltage Before and After the Degradation Model

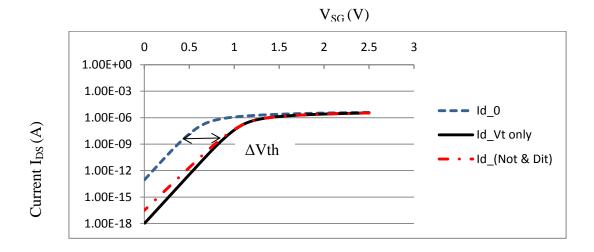

Figure 23: Threshold Voltage Shift- Defect Model and Vt Only

The Current-Voltage curves are generated for a PMOS with and without the degradation model. We see a threshold voltage shift in the Figure 22, which is caused by the defects.

Figure 23 shows the current-voltage plots with and without gate bias dependence of the defects. In the Vt only plot, the change in threshold voltage is given by the equation (47). Whereas in the other current plot the defects are dependent on gate voltage in the sub threshold region and the threshold voltage difference is given by the equation (46).

### **4.4 Modeling Defect Generators**

### **4.4.1** Interface Traps (D<sub>it</sub>) Generator

For interface traps the response profile increases with stress, but remains virtually constant once the stress is removed. Figure 24 shows the ideal response of interface traps during stress and when the stress is removed.

Figure 24: Ideal Response of Interface Traps during Stress and Relax

This may also be captured by the transient equation but instead with a very large delay time constant.

$$V_{Dit}(t) = V_{pb}[(1-\exp(-\frac{t}{\tau_1}))u(t) - (1-\exp(-\frac{t-T}{\tau_2}))u(t-T)]$$

(51)

where

$$V_{Dit}(t) = \frac{qD_{it}(t)}{C_{ox}}$$

(52)

The equation (51) can be implemented in cadence as shown in Figure 25.

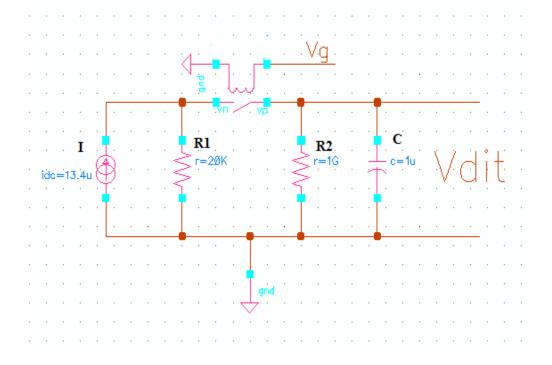

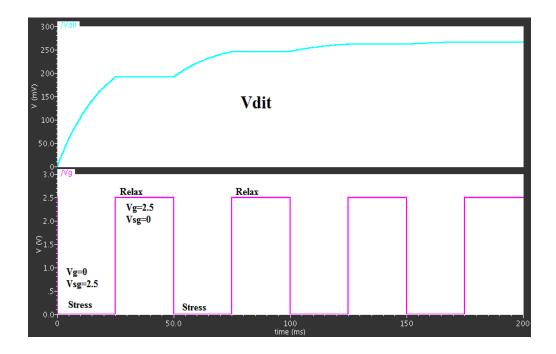

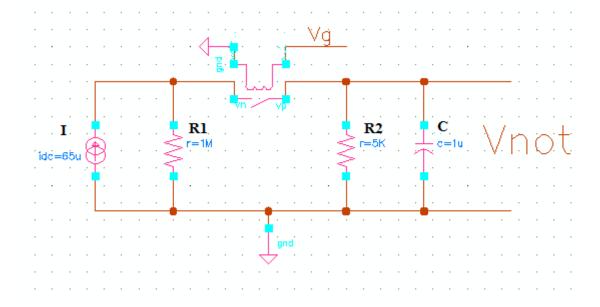

Figure 25: Nit Defect Generator Schematic

The maximum value of  $D_{it}$  is taken to be  $1x10^{12}$ .

Therefore

$$V_{Dit} = \frac{qD_{it}}{C_{ox}} = 268 \text{mV}.$$

During Stress, the switch is closed and the time constant  $\tau_1 = (R1||R2)C$ .

During Relax, the switch is open and the time constant  $\tau_2 = (R2)C$ .

We want the delay time constant to be very large, so R2 is a big value.

So one can select values  $R2 = 1G\Omega$  and C = 1uF.

Since  $V_{max} = 268mV = I(R1||R2)$ .

So accordingly one can select values  $R1 = 20k\Omega$  and I = 13.4u.

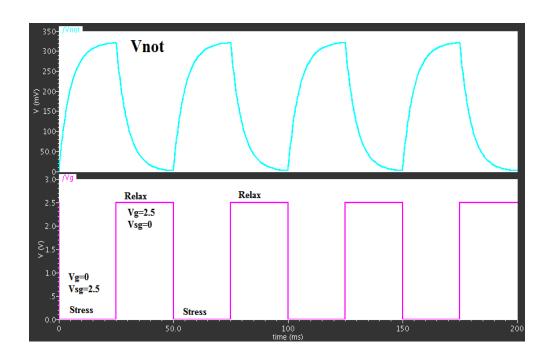

When Vg = 0 i.e. Vsg=2.5 and hence it is a stress and the Interface Trap voltage increases with time and when Vg=2.5 i.e. Vsg=0, it is relax and hence the voltage remains constant as shown is Figure 26. The interface traps don't anneal during relax.

Figure 26: Interface Trap Voltage with Time and Gate Bias

## 4.4.2 Oxide Traps (Not) Generator

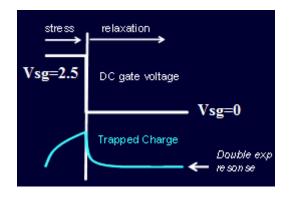

In response to gate voltage stress, the fixed trapped charge density may be assumed to follow a double exponential response profile. Figure 27 shows the ideal response of the oxide traps during stress and when the stress is removed.

Figure 27: Ideal Response of Oxide Traps During Stress and Relax

The above response can be captured by the transient equation

$$V_{\text{Not}}(t) = V_{\text{pb}}[(1 - \exp(-\frac{t}{\tau_1}))u(t) - (1 - \exp(-\frac{t - T}{\tau_2}))u(t - T)]$$

(53)

Where

$$V_{\text{Not}}(t) = \frac{qN_{ot}(t)}{c_{ox}}$$

(54)

The above equation can be generated in a circuit by a gate voltage-controlled switch and an RC network shown in Figure 28.

Figure 28: Not Defect Generator Schematic

The maximum value of  $N_{\text{ot}}$  is taken to be  $1.2x10^{12}$ .

Therefore

$$V_{\text{Not}} = \frac{qN_{ot}}{c_{ox}} = 322\text{mV}.$$

During Stress, the switch is closed and the time constant  $\tau_1 = (R1||R2)C$ .

During Relax, the switch is open and the time constant  $\tau_2 = (R2)C$ .

Since

$$V_{max} = 322mV = I(R1||R2)$$

.

So accordingly one can select values R1 =  $1M\Omega$ , R2 =  $5k\Omega$ , C=1uF and I = 65u.

When Vg = 0 i.e. Vsg=2.5 and hence it is a stress and the Oxide Trap voltage increases with time and when Vg=2.5 i.e. Vsg=0, it is relax period and hence the voltage decreases as shown is Figure 29. The Oxide traps anneal when the stress is removed.

Figure 29: Oxide Trap Voltage with Time and Gate Bias

#### 4.5 Static NBTI

In static NBTI, the gate of the PMOS transistor is stressed for a long time and the change in threshold voltage is observed with respect to time. The threshold voltage increases monotonically with time as the defects keeps on increasing. The threshold voltage shift shows two asymptotes: the slow response and the fast response [32]. The inrerface traps ( $D_{it}$ ) voltage is very slow and takes a lot of time to reach its maximum value, whereas the oxide traps ( $N_{ot}$ ) voltage reaches its saturation value way before the Interface trap voltage. Using the model developed in this work, a similar pattern is observed for the threshold voltage shift. Figure 30 shows the threshold voltage shift generated using our model. The time constants used in the equations (51) and (53) are chosen in such a way that the final value of oxide trap voltage saturates much before the final value of the interface trap voltage.

The change in threshold voltage varies with time as a power-law [32].

$$\Delta V_{th} \propto t^n$$

The value of n varies depending of what type of defects dominates.

Figure 30: Static NBTI

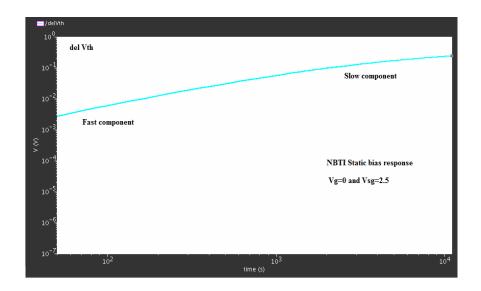

## 4.6 Dynamic NBTI

In Dynamic NBTI, the gate of the PMOS transistor is allowed to switch from 0 to  $V_{DD}$ . When the source gate voltage is 0, the transistor is in strong inversion and because of the gate stress oxide traps and interface traps are formed. When the stress is removed i.e. if the source gate voltage is  $V_{DD}$ , then the defects are annealed up to certain extent because the trapped holes will be de-trapped as discussed in the earlier sections. The interface traps are fixed but the oxide traps anneal when the stress is removed. Therefore the threshold voltage degradation is annealed up to some extent.

Figure 31 shows the threshold voltage with time using the degradation model. The fast component is because of the oxide traps whereas the slow component is due to the interface traps [32].

Figure 31: Dynamic NBTI

#### CHAPTER 5

#### **NBTI EFECTS IN CMOS CIRCUITS**

#### 5.1 CMOS Inverter

The CMOS inverter is a basic building block for digital circuit design. The input to the inverter is connected to both a PMOS transistor and an NMOS transistor. When the voltage of input A is low, the NMOS transistor is turned off and its channel is in a high resistance state. The PMOS transistor is strongly on and its channel is in a low resistance state and it allows the current to flow from the  $V_{DD}$  to the output. It charges the load capacitance. As the resistance between the supply voltage and output is low, the voltage drop between the supply voltage and output due to a current drawn from output is small resulting in a high voltage at the output [27].

Figure 32: CMOS Inverter

On the other hand, when the voltage of input A is high, the PMOS transistor is turned off so it would not allow the current to flow from the  $V_{DD}$  to the output, while the NMOS transistor is completely turned on and, allowing the current to flow from output to ground. The low resistance between output and ground keeps the voltage

drop due to a current drawn into output very small. This low drop results in a low output voltage [27].

In short, inverter is a circuit where the output is inverted, such that when the input is high  $(V_{DD})$ , the output is low (0), and when the input is low, the output is high. The NMOS and PMOS transistor goes through different regions as the input swings from 0 to  $V_{DD}$ . The threshold voltage of both the transistors is important as the propagating signal depends on the threshold voltage.

This CMOS inverter transfer characteristics is shown in Figure 33.

Figure 33: The CMOS Inverter Voltage Transfer Characteristics

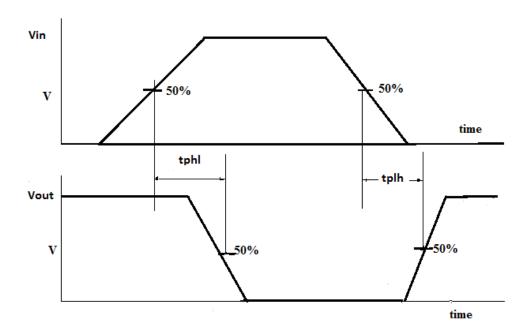

There are various regions of operation when the input goes from 0 to  $V_{DD}$ . When the input is low, the M2 transistor is turned on while the M1 transistor is off. In the mid values of input, both the transistors are turned on. When the input is high, the M2 transistor is off and M1 transistor is turned on. X and Y are the transition points. The total intrinsic propagation delay of an inverter is given by  $t_d = (t_{pHL} + t_{pLH})/2$ , where  $t_{pHL}$  and  $t_{pLH}$  are explained in Figure 34.

Figure 34: Inverter Propagation Delay

The propagation delay depends on almost all the parameters like supply voltage, threshold voltage, width, effective length, channel mobility etc.

#### **5.1.1** NBTI Effects in CMOS Inverter

NBTI primarily occurs in p-channel MOSFET's when a negative gate voltage is applied and it is almost negligible when a positive voltage is applied. When the source gate voltage is high, the transistor is in stress and when source gate voltage is zero, the transistor is off. Although the defects increase with stress, but when the stress is removed then interface traps are going to be annealed which recovers the threshold voltage. This leads to an increase in the propagation delay. The NBTI can also cause a spread in signals. The increase in spread of signals can cause serious malfunction of the logic circuits and hence they will be failed [18].

The delay time  $t_d$  [53] is

$$t_{d} = \frac{cV_{DD}}{I} = \frac{c}{\frac{1W}{2L}\mu_{eff}C_{ox}V_{DD}\left(1 - \frac{V_{th}}{V_{DD}}\right)^{2}}$$

(55)

Therefore current decreases and delay time increases when threshold voltage increases and mobility decreases.

In an inverter the NBTI causes a propagation delay and when a chain of inverters are connected like in a ring oscillator circuit, the total propagation delay increases and which causes the frequency of the ring oscillator to change.

Table 2 shows the phases of bias temperature instability in a CMOS inverter.

Table 2: Bias Stress Temperature in Inverter [53]

| V <sub>in</sub> | $V_{out}$ | NMOS         | PMOS         |

|-----------------|-----------|--------------|--------------|

| 0               | $V_{DD}$  | Relax(off)   | NBTI(stress) |

| $V_{ m DD}$     | 0         | PBTI(stress) | Relax(off)   |

Figure 35 illustrates the various phases of NBTI in a CMOS inverter when the gate voltage is swinging from 0 to  $V_{\rm DD}$ .

Figure 35: CMOS Inverter Degradation [53]

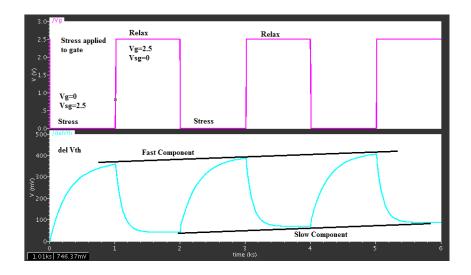

## **5.1.2** Inverter with the degradation model

The defect model developed in this model is connected to the gate terminals of both PMOS and NMOS in the inverter. Although the PBTI effect in NMOS is very less compared to that of NBTI in PMOS, the defect model for NMOS is also connected.

When the gate voltage is 0V, the source gate voltage for PMOS is  $V_{DD}$  hence it is stress condition. When gate voltage is  $V_{DD}$ , the PMOS is in off condition. Similarly when the gate voltage is 0, the NMOS is off and when the gate voltage is  $V_{DD}$  then the NMOS is under stress. Although the PBTI effects are very minimum compared to NBTI, both the effects are considered in this inverter simulation.

Figure 36: CMOS Inverter with and Without Degradation Models

Table 3: Component parameters of Inverter

| W <sub>p</sub> (nm) | 12000 |

|---------------------|-------|

| W <sub>n</sub> (nm) | 4000  |

| L(nm)               | 1000  |

Inverter with and without the degradation model are shown in Figure 36. The degradation model mimics the effects of NBTI in PMOS. The width and lengths of PMOS and NMOS used in the inverter design are shown in table 3. When the stress is applied, interface traps and oxide traps are formed which degrades the performance of

the PMOS by reducing its mobility and increasing absolute value of threshold voltage. This causes a propagation delay in the inverter as shown in Figure 37. Although the defects models are modeled for both PMOS and NMOS, the only major factor contributing for propagation delay is the NBTI effect of PMOS transistors as the PBTI in NMOS contributes very less effect. As the simulation results shows that the defects cause an asymmetry in the rise and fall times and the propagation time for the signal increases causing a delay. So when the inverters are connected in a chained fashion like in a ring oscillator, the total propagation delay increases and frequency of the ring oscillator decreases.

Figure 37: CMOS Inverter Output with and Without Stress

### 5.2 Ring Oscillator

A ring oscillator is a device composed of an odd number of Inverters connected in a positive feedback loop, whose output oscillates between two voltage levels 0 and  $V_{DD}$ . A block diagram of an n-stage inverter ring oscillator is shown in Figure 38.

Figure 38: An n-Stage Ring Oscillator

The inverters are connected in a chain fashion in stages; the inverters are basically connected in cyclic order, so that the output of the last inverter is fed back as an input to the first inverter of the chain. As there will be an inversion for every stage of inverters, the output will also be inverted if the number of stages is an odd number. There is a certain time delay for every inverter for the signal to pass from input to output. It is also the same time to charge and discharge the capacitance at the output node. Thus every inverter in the chain has a time delay for its output to show up. As the number of inverters increase, the gate delay increases which decreases the frequency of the ring oscillator. The main reason for the oscillation is the odd number of inverters and output of last inverter feeding back into the input. A real ring oscillator is almost a self-start circuit which only requires power to operate; above a certain threshold voltage, oscillations begin spontaneously. To increase the frequency of oscillation, ring oscillator should be made from a smaller number of inverters.

The frequency of oscillation at each stage is inversely proportional to the number of stages in the ring oscillator circuit and the gate delay of each individual gate. As the number of stages increase, the frequency of oscillation decreases.

$$f_{osc} = \frac{1}{2nt_d} \tag{56}$$

Where "n" denotes the number of inverters used, t<sub>d</sub> is the time delay of each inverter.

The frequency of the ring oscillator depends on process parameters like the width, length, threshold voltage etc. The propagation delay of an inverter circuit can be obtained by measuring the time period of the oscillator.

With the gate stress and at elevated temperatures, the interface traps and oxide traps are formed which degrades the performance of the transistor by increases the threshold voltage and degrading other important parameters. As the threshold voltage increases, the value of  $(V_{DD}-V_{th})$  decreases and hence it increases the delay according to the equation (55).

In this work, a ring oscillator circuit of 5 inverters chain is designed as shown in Figure 39 and is simulated with and without the stress. In spectre simulations, an initial condition is given to the output node and then the output oscillates automatically. The results are also compared with the results of only  $V_t$  mode. The frequency of the ring oscillator without stress is 246.5MHz and we observed that the frequency with stress as decreased. The frequency of the ring oscillator with stress i.e., when the defects model is applied is 204MHz. The frequency when just the  $V_t$  model is applied is 198.5MHz.

Figure 39: Ring Oscillator Schematic with 5 Inverters

Figure 40: Ring Oscillator Output Waveform with and Without Stress

The transient response with and without stress are shown in Figure 40. In the  $V_t$  model, the gate bias dependency in the subtreshold region is not considered. The frequency response is compared in Figure 41 and Figure 42 respectively.

Figure 41: Frequency Response without Stress

Figure 42(a): Frequency Response with Stress (Defects Model)

Figure 42(b): Frequency Response with Stress ( $V_t$  Model)

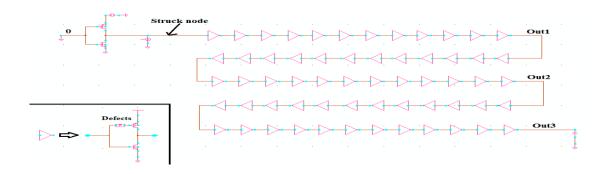

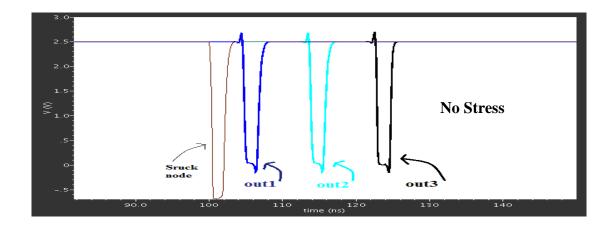

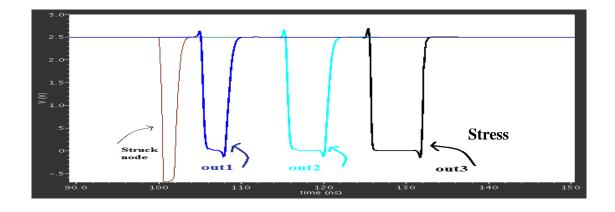

The model is also applied to test the single event transient (SET) pulse broadening and we see the pulse broadening with stress as shown in Figure 45.

Figure 43: Modeling SET Pulse Broadening

Figure 45(a): SET Pulse Broadening Without Stress

Figure 45(b): SET Pulse Broadening with Stress

#### **CHAPTER 6**

#### **CONCLUSION**

Negative bias temperature instability (NBTI) is a serious problem in PMOS transistors. The defects caused by the gate stress and elevated temperatures should be considered in the circuit simulations. But the defects change with time and they are not constant, so it is very hard for the designer to include the defects every time. So in this work a model is developed to which the inputs are the maximum value of the density of interface traps and oxide traps. The model generates a defect potential which is exactly the change is threshold voltage caused by the defects. The defects are gate voltage and time dependent.

The MOSFET Sub-threshold current method is used to evaluate the interface traps and oxide traps in PMOS transistor. The degradation model in modeled in cadence and validated the same with the simulations in Silvaco. The current-voltage curves in both cadence and Silvaco are compared and both the results fit each other. A shift is observed in the threshold voltage when the degradation model is introduced which is obvious as the shift is caused by the interface traps and the oxide traps. The simulation results produced by the model discussed in this work are compared to various other results by other authors. The same methodology is replicated for NMOS transistor and a degradation model is developed for NMOS transistor. After the device level simulations, the degradation models were introduced at the gate terminal of PMOS and NMOS in an inverter. The threshold voltage degradation is very less for a NMOS transistor. A ring oscillator circuit of 5 inverters chain is designed and the frequency of the ring oscillator is observed with and without stress. The frequency of

ring oscillator is decreased by applying stress which is because of the increase in threshold voltage and hence increase in gate delay. The  $V_t$  only model result is also compared with that of the defects model. There is a change is frequency in both the models. The  $V_t$  only model doesn't include the gate voltage dependency in the subtreshold region. The model is also used to see the single event transient pulse broadening and it gave a satisfactory result as observed by some authors.

This model captures transistor response using fixed trapped charge ( $N_{ot}$ ) and interface traps densities ( $D_{it}$ ) as the input parameters. The model is external to the transistor, thus easily implemented with time and bias dependence but without modifications to compact model. This is very advantageous to the designers.

#### REFERENCES

- [1] H.J. Barnaby, "Total-Ionizing-Dose Effects in Modern CMOS Technologies" IEEE Trans. Nucl. Sci. Vol. 53, No. 6, December 2006.

- [2] Boualem Djezzar, Hakim Tahi, and Arezki Mokrani, "Why Is Oxide-Trap Charge-Pumping Method Appropriate for Radiation-Induced Trap Depiction in MOSFET?" IEEE Trans. on Device and Materials Reliability, Vol. 9, No. 2, June 2009

- [3] V. Huard, M. Denais, and C. Parthasarathy, "NBTI Degradation: From Physical Mechanisms to Modelling," *Microelectron.Reliab.*, vol. 46, no. 1, pp. 1-23, 2006.

- [4] P. M. Lenahan and P. V. Dressendorfer, "Hole traps and trivalent silicon centers in metal/oxide/silicon devices," J. Appl. Phys., vol. 55, pp. 3495, 1984.

- [5] Y. F. Chen, M. H. Lin, C. H. Chou, W. C. Chang, S. C. Huang, Y. J. Chang, K. Y. Fu, M. T. Lee, C. H. Liu, and S. K. Fan, "Negative bias temperature instability (NBTI) in deep sub-micron P+-gate pMOSFETs," in Proc. IRW, Lake Tahoe, CA, pp. 98–101, Oct. 2000.

- [6] C. H. Liu, M. T. Lee, C. Y. Lin, J. Chen, Y. T. Loh, F. T. Liou, etc, "Mechanism of threshold voltage shift ( $\Delta V$ th) caused by negative bias temperature instability (NBTI) in deep submicrometer pMOSFETs," Jpn. J. Appl. Phys., vol. 41, pp. 2423-2425, April 2002.

- [7] M. A. Alam, H. Kufluoglu, D. Varghese, and S. Mahapatra, "A comprehensive model for PMOS NBTI degradation: Recent progress," Microelectron. Reliab., vol. 47, no. 6, pp. 853–862, Jun. 2007.

- [8] K. O. Jeppson and C. M. Svensson, "Negative bias stress of MOS devices at high electric fields and degradation of MOS devices," J. Appl. Phys., vol. 48, pp. 2004–2016, 1977.

- [9] S. Mahapatra, P. B. Kumar, and M. A. Alam, "A new observation of enhanced bias temperature instability in thin gate oxide p-MOSFETs," in IEDM Tech. Dig. pp. 196–202, 2003.

- [10] Dieter K. Schroder, "Negative bias temperature instability: What do we understand?" Microelectronics Reliability, vol. 47, pp. 841-852, 2007.

- [11] M. A. Alam, S. Mahapatra, "A comprehensive model of PMOS NBTI degradation," Microelectronics Reliability, vol. 45, pp. 71-81, 2005.

- [12] "MOSFET." Wikipedia. Retrieved October 15, 2014, from http://en.wikipedia.org/wiki/MOSFET.

- [13] A. S. Sedra, K. C. Smith, "Microelectronics circuits", Oxford University Press, 2004.

- [14] A. Narr, and A. Lill, "Lifetime Prediction for PMOS and NMOS Devices Biased on A Degradation Model for Gate-Bias-Stress," Microelectronics Reliability, vol. 37, pp. 1433-1436, 1997.

- [15] Y. H. Lee, S. Jacobs, S. Stadler, N. Mielke, and R. Nachman, "The impact of PMOST bias-temperature degradation on logic circuit reliability for performance," Microelectronics Reliability, vol. 45, pp. 107-114, 2005.

- [16] A. T. Krishnan, V. Reddy, and S. Krishnan, "Impact of charging damage on negative bias temperature instability," in IEDM Tech. Dig., pp. 39.3.1–39.3.4., 2001.

- [17] Harris, H.R.; Choi, R.; Lee, B.H.; Young, C.D.; Sim, J.H.; Mathews, K.; Zeitzoff, P.; Majhi, P.; Bersuker, G.; "Recovery of NBTI degradation in HfSiON/metal gate transistors, Integrated Reliability Workshop Final Report," 2004 IEEE International, pp. 132 135, Oct. 2004.

- [18] Dieter K. Schroder, "Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing," J. Appl. Phys., vol. 94, 1 July 2003.

- [19] S. Zafar, "Statistical mechanics based model for negative bias temperature instability induced degradation," Journal of Applied Physics, vol. 97, pp. 1-9, 2005.

- [20] Robert Entner, "Modeling and Simulation of Negative Bias Temperature Instability," PhD Dissertation, Institute of Microelectronics, 2007.

- [21] Chen G., Li M.F., Ang C.H., Zheng J.Z., Kwong D.L., "Dynamic NBTI of p-MOS transistors and its impact on MOSFET scaling," IEEE Electron Dev Lett, vol. 23, pp. 734–6, 2002.

- [22] Alam M.A., "A critical examination of the mechanics of dynamic NBTI for pMOSFETs," IEDM Tech Dig, pp. 346–9, 2003.

- [24] Yang, T. Shen, C. Li, M.F. Ang, C.H. Zhu, C.X. Yeo, Y.-C. Samudra, G. Kwong, D.-L., "Interface trap passivation effect in NBTI measurement for p-MOSFET with SiON gate dielectric, Electron Device Letters," IEEE, Vol. 26, pp. 758-760, Oct.2005.

- [26] Xiaojun Li, Jin Qin, Bing Huang, Xiaohu Zhang, and Joseph B. Bernstein, "A New SPICE Reliability Simulation Method for Deep Submicrometer CMOS VLSI Circuits," IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, vol. 6, No. 2, pp. 247-257, June. 2006.

- [27] "CMOS." Wikipedia. Retrieved September 30, 2014, from http://en.wikipedia.org/wiki/CMOS.

- [32] A. Neugroschel, G. Bersuker, R. Choi, C. Cochrane, P. Lenahan, D. Heh, C. Young, C.Y. Kang, B.H. Lee, and R. Jammy, "An Accurate Lifetime Analysis Methodology Incorporating Governing NBTI Mechanisms in High-k/SiO2 Gate Stacks" in Proc. Int. Electron Devices Meeting, San Francisco, CA, Dec. 2006, pp. 317-320.

- [33] C. Leroux, J. Mitard, G. Ghibaudo, X. Garros, G. Reimbold, B. Guillaumor, F. Martin, "Characterization and modeling of hysteresis phenomena in high-k dielectrics," IEEE Intl Electron Devices Meeting Tech Digest. pp. 737-740, 13-15 Dec. 2004.

- [34] S. Zafar, A. Callegari, E. Gusev, M.V. Fischetti, "Charge trapping in high-k gate dielectric stacks," IEEE IEDM, pp. 517-520, 2002.

- [35] G. RibePb, M.Miillerd, S. Bruykre, D. Roy ,M. Denaisa, V. Huardd, TSkotnicki, G. Ghibaudob, "Characterization of Vt instability in hafnium based dielectrics by pulse gate voltage techniques," IEEE, vol. 5, pp. 89-92, 2004.

- [36] Gurfinkel, M.; Suehle, J.; Bernstein, J.B.; Shapira, Y.; Lelis, A.J.; Habersat, D.; Goldsman, N.; "Ultra-Fast Characterization of Transient Gate Oxide Trapping in SiC Mosfets," IEEE International pp. 462 466, April 2007.

- [38] C.D. Young, Y. Zhao, M. Pendley, B.H. Lee, K. Matthews, J.H. Sim, R. Choi, G.A. Brown, R.W. Murto and G. Bersuker, "Ultra-Short Pulse Current-Voltage Characterization of the Intrinsic Characteristics of High k Devices", Jpn. J. of Appl. Phys., vol. 44, No. 4B, 2437, 2005.

- [39] KERBER A.; CARTIER E.; PANTISANO L.; DEGRAEVE R.; GROESENEKEN G.; MAES H. E., SCHWALKE U., "Charge trapping in SiO2/HfO2 gate dielectrics: Comparison between charge-pumping and pulsed ID–VG," Microelectronic Engineering, vol.72, pp. 267-272, April 2004.

- [40] C. D. Young, R. Choi, J. H. Sim, B. H. Lee, P. Zeitzoff, Y. Zhao, K. Matthews, G. A. Brown, and G. Bersuker, "Interfacial layer dependence of HFSI/sub x/O/sub y/ gate stacks on V/sub T/ instability and charge trapping using ultra-short pulse in characterization," presented at the 43rd Annual IEEE Intl. Reliability Physics Symp. Proc, pp.75-79, 2005.

- [41] Kang, Kunhyuk Kim, Keejong Islam, Ahmad E. Alam, Muhammad A. Roy, Kaushik, "Characterization and Estimation of Circuit Reliability Degradation under NBTI using On-Line IDDQ Measurement," Design Automation Conference, 2007. DAC '07. 44th ACM/IEEE, Publication, pp. 358 363, June 2007.

- [42] L. Tsetseris, X. Zhou, D. Fleetwood, R. Schrimpf, and S. Pantelides, "Physical Mechanisms of Negative-Bias Temperature Instability," Appl.Phys.Lett., vol. 86, no. 14, pp. 1-3, 2005.

- [43] T. Grasser, W. Gös, V. Sverdlov, and B. Kaczer, "The Universality of NBTI Relaxation and its Implications for Modeling and Characterization," in Proc. Intl.Rel.Phys.Symp., pp. 1-13, 2007.

- [44] D. K. Schroder, Semiconductor Material and Device Characterization, 3rd Edition. Wiley Interscience, 2006.

- [45] R. A. B. Devine, J.-L. Autran, W. L. Warren, K. L. Vanheusdan, and J.-C. Rostaing, "Interfacial Hardness Enhancement in Deuterium Annealed 0.25 mu m Channel Metal Oxide Semiconductor Transistors," Appl.Phys.Lett., vol. 70, no. 22, pp. 2999-3001, 1997.

- [46] A. H. Edwards, "Interaction of H and H<sub>2</sub> with the Silicon Dangling Orbital at the <111> Si/SiO<sub>2</sub> Interface," Phys.Rev.B, vol. 44, no. 4, pp. 1832-1838, 1991.

- [47] V. Reddy, A. T. Krishnan, A. Marshall, J. Rodriguez, J., S. Natarajan, T. Rost, S. Krishnan, "Impact of Negative Bias Temperature Instability on Digital Circuit Reliability," IEEE Reliability Physics Symposium Proceedings, 2002. 40th Annual, pp. 248-254, 2002.

- [48] J. Stathis and S. Zafar, "The Negative Bias Temperature Instability in MOS Devices: A Review," *Microelectron.Reliab.*, vol. 46, no. 2-4, pp. 270-286, 2006.

- [49] Y. Miura and Y. Matukura, "Investigation of Silicon-Silicon Dioxide Interface Using MOS Structure," *Jpn.J.Appl.Phys.*, vol. 5, p. 180, 1966.

- [50] A. Goetzberger and H. Nigh, "Surface Charge After Annealing of Al-SiO<sub>2</sub> Si Structures Under Bias," Proc.IEEE, vol. 54, no. 10, p. 1454, 1966.

- [51] E. Deal, M. Sklar, A. S. Grove, and E. H. Snow, "Characteristics of the Surface-State Charge (Qss) of Thermally Oxidized Silicon," J.Electrochem.Soc., vol. 114, no. 3, p. 266, 1967.

- [52] Y. Mitani, M. Nagamine, H. Satake, and A. Toriumi, "NBTI Mechanism in Ultra-Thin Gate Dielectric Nitrogen-Originated Mechanism in SiON," in Proc. Intl. Electron Devices Meeting, pp. 509-512, 2002.

- [53] D. K. Schroder, "Advanced MOS Devices", class notes, Arizona State University, Tempe, 2011.

- [54] C. R. Helms and E. H. Poindexter, "The Silicon-Silicon Dioxide System: Its Microstructure and Imperfections," Reports on Progress in Physics, vol. 57, no. 8, pp. 791-852, 1994.

- [55] J. P. Campbell, P. M. Lenahan, A. T. Krishnan, and S. Krishnan, "Observations of NBTI-Induced Atomic Scale Defects," IEEE Trans.Dev.Mat.Rel., vol. 6, no. 2, pp. 117-122, 2006.

- [56] J. Campbell, P. Lenahan, A. Krishnan, and S. Krishnan, "Direct Observation of the Structure of Defect Centers Involved in the Negative Bias Temperature Instability," Appl.Phys.Lett., vol. 87, no. 20, pp. 1-3, 2005.

- [57] P. Lenahan, T. Mishima, J. Jumper, T. Fogarty, and R. Wilkins, "Direct Experimental Evidence for Atomic Scale Structural Changes Involved in the Interface-Trap Transformation Process," IEEE Trans. Nuclear Science, vol. 48, no. 6, pp. 2131-2135, 2001.

- [58] L. A. Ragnarsson and P. Lundgren, "Electrical Characterization of P<sub>b</sub> Centers in (100) Si/SiO<sub>2</sub> Structures: The Influence of Surface Potential on Passivation During Post Metallization Anneal," J.Appl.Phys. vol. 88, no. 2, pp. 938-942, 2000.

- [59] V. Reddy, J. Carulli, A. Krishnan, W. Bosch, and B. Burgess, "Impact of Negative Bias Temperature Instability on Production Parameter Drift," IEEE ITC International Test Conference, pp. 148-155, 2004.

# APPENDIX A

## TCAD CODE

```

go atlas

#set Niti=2.3e10

\# D is Niti/.023 where .023 eV = phiB/20 and PhiB=.46 for the nmos2 str

set Not=1.2e12

mesh inf=pmos_tsmc.str

model print SURFMOB

material region=1 eg300=1.12 nc300=3.2e19 nv300=2e19 mun=455.3

mup=158.7 permittivity=11.7 affinity=4.05 taun0=1 taup0=1

contact name=source neutral

contact name=drain neutral

contact name=gate workfun=5.17

interface qf=$Not

method 2nd tol.time=1e-6

output con.band val.band band.params charge

solve init

save outf=pmos_0V_$"Not"_$"Niti".str

# save structure for off state Vds=50mV

solve vdrain=-0.05 name=drain

save outf=pmos_sd_p05V_$"Not"_$"Niti".str

solve vgate=0

# save IV for dc Id-Vgs linear response

log outf=T_PMOS_1pe12_1e12.log

solve vgate=0 vstep=-0.1 vfinal=-2.5 name=gate

```

# save structure for strong-inv, linear Vds=50mV

save outf=pmos\_tsmc\_2p5.str

quit