## Monocrystalline ZnTe/CdTe/MgCdTe Double Heterostructure Solar Cells

Grown on InSb Substrates by Molecular Beam Epitaxy

by

Michael John DiNezza

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved October 2014 by the Graduate Supervisory Committee:

Yong-Hang Zhang, Chair Shane Johnson Meng Tao Zachary Holman

ARIZONA STATE UNIVERSITY

December 2014

## ABSTRACT

There has been recent interest in demonstrating solar cells which approach the detailed-balance or thermodynamic efficiency limit in order to establish a model system for which mass-produced solar cells can be designed. Polycrystalline CdS/CdTe heterostructures are currently one of many competing solar cell material systems. Despite being polycrystalline, efficiencies up to 21 % have been demonstrated by the company First Solar. However, this efficiency is still far from the detailed-balance limit of 32.1 % for CdTe. This work explores the use of monocrystalline CdTe/MgCdTe and ZnTe/CdTe/MgCdTe double heterostructures (DHs) grown on (001) InSb substrates by molecular beam epitaxy (MBE) for photovoltaic applications.

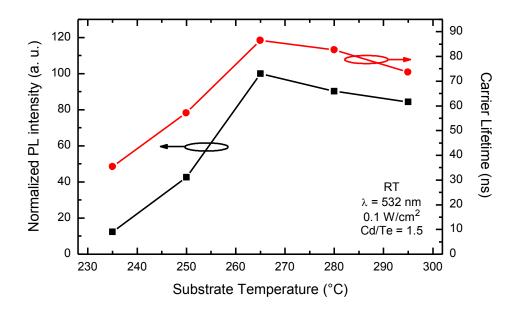

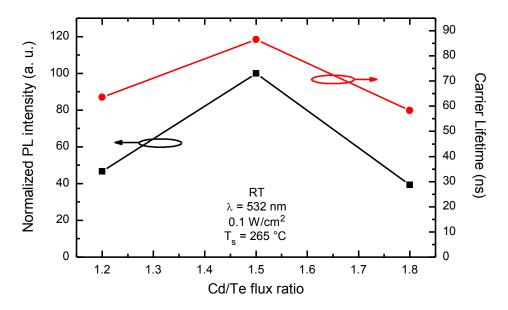

Undoped CdTe/MgCdTe DHs are first grown in order to determine the material quality of the CdTe epilayer and to optimize the growth conditions. DH samples show strong photoluminescence with over double the intensity as that of a GaAs/AlGaAs DH with an identical layer structure. Time-resolved photoluminescence of the CdTe/MgCdTe DH gives a carrier lifetime of up to 179 ns for a 2 µm thick CdTe layer, which is more than one order of magnitude longer than that of polycrystalline CdTe films. MgCdTe barrier layers are found to be effective at confining photogenerated carriers and have a relatively low interface recombination velocity of 461 cm/s. The optimal growth temperature and Cd/Te flux ratio is determined to be 265 °C and 1.5, respectively.

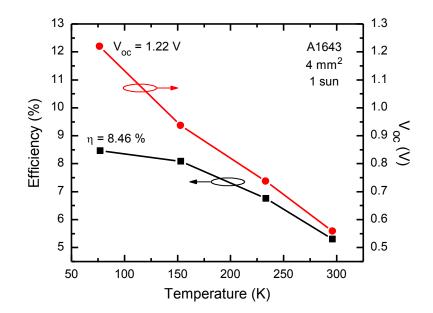

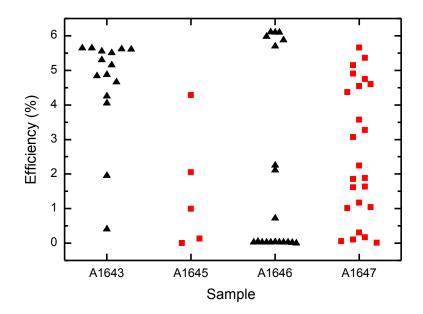

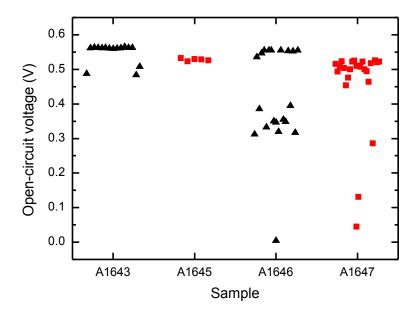

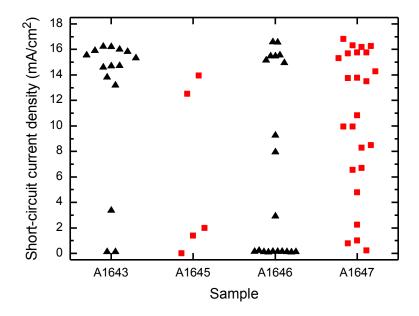

Monocrystalline ZnTe/CdTe/MgCdTe P-n-N DH solar cells are designed, grown, processed into solar cell devices, and characterized. A maximum efficiency of 6.11 % is demonstrated for samples without an anti-reflection coating. The low efficiency is mainly due to the low open-circuit voltage ( $V_{oc}$ ), which is attributed to high dark current caused by interface recombination at the ZnTe/CdTe interface. Low-temperature measurements show a linear increase in  $V_{oc}$  with decreasing temperature down to 77 K, which suggests that the room-temperature operation is limited by non-radiative recombination. An opencircuit voltage of 1.22 V and an efficiency of 8.46 % is demonstrated at 77 K. It is expected that a coherently strained MgCdTe/CdTe/MgCdTe DH solar cell design will produce higher efficiency and  $V_{oc}$  compared to the ZnTe/CdTe/MgCdTe design with relaxed ZnTe layer. This work is dedicated to my wife, Nikki DiNezza, whose love and support have made it possible to pursue my dreams.

### ACKNOWLEDGMENTS

First and foremost, I would like to think my research advisor Dr. Yong-Hang Zhang. He has always challenged and inspired me to think at a much deeper level, both with my technical work and within my personal life. His guidance and intuition has led me to study CdTe solar cells, and I am truly grateful for that. I would also like to thank Dr. Shane Johnson who has also been a mentor to me, particularly relating to the operation of the MBE system. I'm also thankful for my committee members Dr. Meng Tao and Dr. Zachary Holman for their important feedback on this work.

Over the past 6 years there have been many people in our group who have mentored me or contributed to my education and training. I am thankful to have worked with (in roughly chronological order): Dr. Ding Ding, Dr. Shumin Wang, Dr. Songnan Wu, Dr. Robin Scott, Dr. Jin Fan, Dr. Ben Green, Dr. Elizabeth Steenbergen, Dr. Jingjing Li, Dr. Kevin O'Brien, Dr. Swee Hoe Lim, Dr. Charles Allen, Dr. Oray Orkun Cellek, Dr. Qiang Zhang, and Dr. Stuart Farrell. I'm also thankful to have worked with the Master's graduates Junliang Chen and W. H. G. (Hank) Dettlaff.

Special recognition should be given to the many people in our group who worked directly on this project. First to be recognized is Xin-Hao Zhao, who performed photoluminescence measurements, X-ray diffraction measurements, and preliminary modeling. Ying-Shen Kuo and Jacob Becker carried out the processing and testing of solar cell samples. Dr. Alex Kirk and Yuan Zhao provided solar cell modeling. Shi Liu carried out III-V growths, a few of the II-VI growths, and developed the InSb buffer layer growth procedure. Calli Campbell carried out some of the growths as well. Xiao-Meng Shen assisted with XRD. Preston Webster has contributed to my understanding of MBE

growth and characterization through many discussions. From Dr. David Smith's group, I would like to acknowledge Jing Liu who provided TEM cross section measurements. Lastly, I'd like to acknowledge Dr. Xinyu Liu and Dr. Jacek K. Furdyna at Notre Dame University who carried out the ZnTe emitter layer growth. It would not have been possible to demonstrate a working solar cell in such a short period of time without them.

Several ASU and external organizations also contributed to this work. These include the Center for Solid State Electronics Research (CSSER) and the Leroy Eyring Center for Solid State Science (CSSS). Both of these organizations provided the fabrication tools and characterization equipment that have made this work possible. External collaborations include General Electric, First Solar, the National Renewable Energy Laboratory (NREL), and Dr. Tom Myers at Texas State University, all of which have provided important feedback about our samples.

Funding from numerous sources has made this work possible, and I am grateful for their support. These include Fellowships from the Science Foundation Arizona and National Science Foundation (grant number DGE-0802261) which supported me for a total of 5 years. I am also grateful for the fellowship provided by Mr. and Mrs. Kucera through the Achievement Rewards for College Scientists Foundation, the Ford Fellowship, and the Ira. A. Fulton Fellowship. Additional research grants were provided by the Bay Area Photovoltaic Consortium, Department of Energy, First Solar, Science Foundation Arizona, Air Force Office of Scientific Research, Arizona State University, and the National Science Foundation.

## TABLE OF CONTENTS

|            | Pa                                                                | age  |

|------------|-------------------------------------------------------------------|------|

| LIST OF TA | ABLES                                                             | viii |

| LIST OF FI | GURES                                                             | ix   |

| CHAPTER    |                                                                   |      |

| 1 INTR     | ODUCTION                                                          | 1    |

| 1.1        | CdTe-Based Heterostructures Grown on InSb Substrates              | 4    |

| 1.2        | Organization of the Dissertation                                  | 7    |

| 2 PHO      | TOLUMINESCENCE STRUCTURE DESIGN                                   | 10   |

| 2.1        | Critical Thickness of CdTe and MgCdTe on InSb                     | 10   |

| 2.2        | Design of the MgCdTe Barrier Layer                                | 12   |

| 2.3        | Basics of PL Measurements and PL Sample Structure Designs         | 15   |

| 3 MOL      | ECULAR BEAM EPITAXIAL GROWTH OF CdTe/MgCdTe ON InSb               | 20   |

| 3.1        | Fundamentals of MBE and Overview of Growth                        | 20   |

| 3.2        | Review of CdTe/MgCdTe Growth Conditions                           | 25   |

| 3.3        | Growth Calibration and Optimization                               | 27   |

| 4 STRU     | JCTURAL CHARACTERIZATION OF CdTe/MgCdTe STRUCTURES                | 30   |

| 4.1        | Investigation of Surface Roughness using Atomic Force Microscopy  | 30   |

| 4.2        | Transmission Electron Microscopy of CdTe/MgCdTe DHs               | 32   |

| 4.3        | X-ray Diffraction Measurements of CdTe/MgCdTe DHs on InSb         | 33   |

| 5 OPTI     | CAL CHARACTERIZATION OF CdTe/MgCdTe STRUCTURES                    | 39   |

| 5.1        | Comparison of Steady-State Photoluminescence of Various Structure |      |

|            | Designs                                                           | 39   |

| CHA  | PTER  |                                                           | Page |

|------|-------|-----------------------------------------------------------|------|

|      | 5.2   | Time-Resolved Photoluminescence of CdTe/MgCdTe DHs        | 42   |

|      | 5.3   | Optimization of Growth Conditions using Photoluminescence | 45   |

| 6    | DESI  | GN OF ZnTe/CdTe/MgCdTe DOUBLE HETEROSTRUCTURE SOL         | AR   |

|      | CELL  | S                                                         | 48   |

|      | 6.1   | Solar Cell Operation and Design Principles                | 48   |

|      |       | 6.1.1 Abrupt PN Homojunction Characteristics              | 49   |

|      |       | 6.1.2 Abrupt PN Heterojunction with Asymmetric Doping     | 56   |

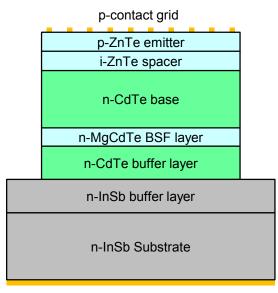

|      | 6.2   | Design of the ZnTe/CdTe/MgCdTe Layer Structure            | 59   |

|      |       | 6.2.1 Initial Structure Design                            | 60   |

|      |       | 6.2.2 Numerical Simulation and Junction Analysis          | 67   |

| 7    | GROV  | WTH, PROCESSING, AND DEVICE CHARACTERIZATION OF           |      |

|      | ZnTe/ | CdTe/MgCdTe DH SOLAR CELLS                                | 74   |

|      | 7.1   | MBE Growth of ZnTe/CdTe/MgCdTe DH Solar Cells             | 74   |

|      | 7.2   | Processing of ZnTe/CdTe/MgCdTe DH Solar Cells             | 78   |

|      | 7.3   | Characterization of ZnTe/CdTe/MgCdTe DH Solar Cells       | 81   |

| 8    | CONC  | CLUSIONS                                                  | 97   |

| REFE | ERENC | ES                                                        | 99   |

| APPI | ENDIX |                                                           |      |

| А    | MATI  | ERIAL PARAMETERS USED FOR PHOTOLUMINESCENCE               |      |

|      | STRU  | CTURE DESIGN                                              | 105  |

| В    | MATI  | ERIAL PARAMETERS USED IN PC1D SIMULATIONS                 | 107  |

# LIST OF TABLES

| Table |                                                                        | Page |

|-------|------------------------------------------------------------------------|------|

| 1.1.  | Demonstrated Cell Efficiencies and Theoretical Limits                  | 3    |

| 2.1.  | Absorbed Pump Light in Various Layers                                  | 17   |

| 3.1.  | Equilibrium Vapor Pressures                                            | 26   |

| 3.2.  | Growth Conditions and Sample Numbers for Seven Samples used in the     |      |

|       | Optimization of the Material Quality                                   | 29   |

| 5.1.  | Measured Carrier Lifetime as a Function of CdTe Middle Layer Thickness | 45   |

| 7.1.  | Measured and Simulated Solar Cell Performance                          | 84   |

| 7.2.  | Measured and Simulated Solar Cell Performance with Non-Zero Surface    |      |

|       | Reflectance and Interface Recombination                                | 91   |

# LIST OF FIGURES

| Figure | Page                                                                                              |

|--------|---------------------------------------------------------------------------------------------------|

| 1.1.   | A Diagram of Experimentally Measured Band gaps vs. Lattice Constants of                           |

|        | Common Semiconductors. Solid and Dashed Lines Represent Direct and Indirect                       |

|        | Band gap Alloys, Respectively. *Figure Provided by Dr. Ding Ding at ASU 6                         |

| 2.1.   | Calculated Critical Thickness of Mg <sub>x</sub> Cd <sub>1-x</sub> Te on InSb Using Two Different |

|        | Models                                                                                            |

| 2.2.   | Band Offsets for CdTe/Mg <sub>x</sub> Cd <sub>1-x</sub> Te, Assuming that MgTe has a Bandgap of   |

|        | 3.0 eV, Bandgap Bowing is Negligible, and $\Delta E_v$ is 30 % of the Difference in the           |

|        | Bandgaps. The Critical Thickness is Calculated using the Matthews-Blakeslee                       |

|        | Model as a Conservative Estimate                                                                  |

| 2.3.   | Basic Setup for Steady-State PL Measurements                                                      |

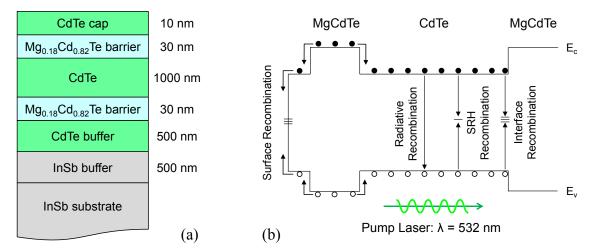

| 2.4.   | (a) Layer Structure Diagram and (b) Schematic Band Edge Diagram for the                           |

|        | CdTe/MgCdTe DH PL Structure                                                                       |

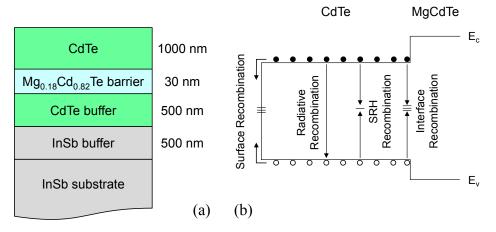

| 2.5.   | (a) Layer Structure Diagram and (b) Schematic Band Edge Diagram for the                           |

|        | CdTe/MgCdTe Single Barrier Structure (Bottom Only) 19                                             |

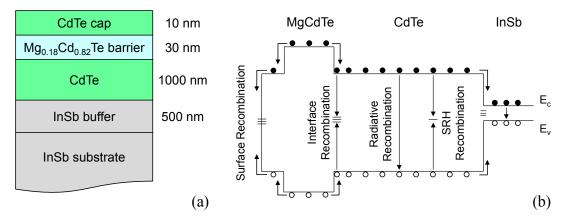

| 2.6.   | (a) Layer Structure Diagram and (b) Schematic Band Edge Diagram for the                           |

|        | CdTe/MgCdTe Single Barrier Structure (Top Only) 19                                                |

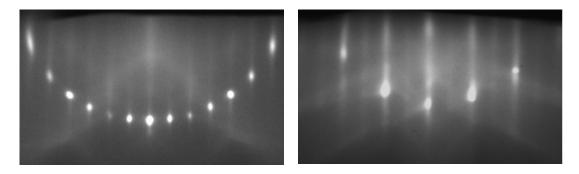

| 3.1.   | RHEED Patterns Along the (001) Direction for InSb at 200 °C (Left) and along                      |

|        | the (011) Direction for CdTe at 265 °C (Right)                                                    |

| 3.2.   | CdTe Growth Rate as a Function of Cd Flux with the Te Flux Kept Constant. The                     |

|        | Intersection of the Linear Region (Cd-Limited) and Saturation Growth Rate (Cd-                    |

|        | rich) Gives the Growth Conditions where the Cd/Te Flux Ratio is Unity                             |

| 4.1. | Atomic Force Micrographs of (a) an InSb Buffer Layer (B2034) and (b) a            |    |

|------|-----------------------------------------------------------------------------------|----|

|      | CdTe/MgCdTe DH Grown on InSb with $T_s = 265$ C and a Cd/Te Flux Ratio of         |    |

|      | 1.5 (A1579). The z-range for both figures is $\pm 6 \text{ nm}$                   | 31 |

| 4.2. | RMS Surface Roughness of CdTe/MgCdTe DHs as a Function of (a) Substrate           |    |

|      | Temperature $T_s$ and (b) Cd/Te Flux Ratio                                        | 32 |

| 4.3. | TEM Image Showing the Lower Portion of the CdTe/MgCdTe DH. *Image                 |    |

|      | Acquired by Jing Lu and Dr. David Smith at ASU                                    | 33 |

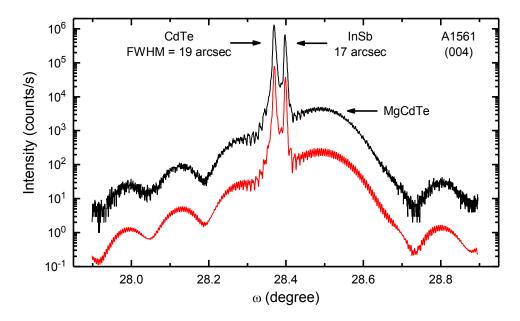

| 4.4. | X-ray Diffraction (XRD) $\omega$ -2 $\theta$ Scan of the CdTe/MgCdTe Double-      |    |

|      | Heterostructure Sample Taken in the Vicinity of the (004) Diffraction Peak. The   | ;  |

|      | black curve is the measured diffraction pattern, while the red curve is simulated |    |

|      | using the software program X'Pert Epitaxy                                         | 36 |

| 4.5. | Reciprocal Space Map (RSM) of the CdTe/MgCdTe DH (A1561) in the Vicinity          | у  |

|      | of the (115) Diffraction Peak with Contours Plotted on a Logarithmic Scale        | 38 |

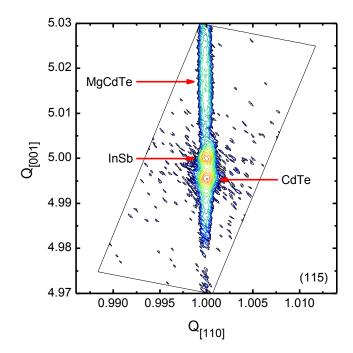

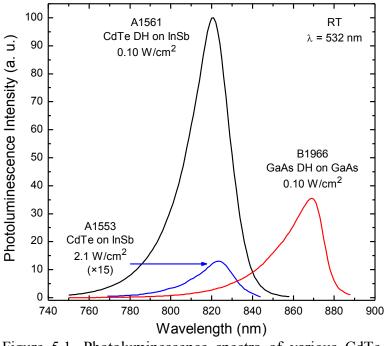

| 5.1. | Photoluminescence Spectra of Various CdTe-Based Structures and a GaAs             |    |

|      | Structure for Comparison                                                          | 41 |

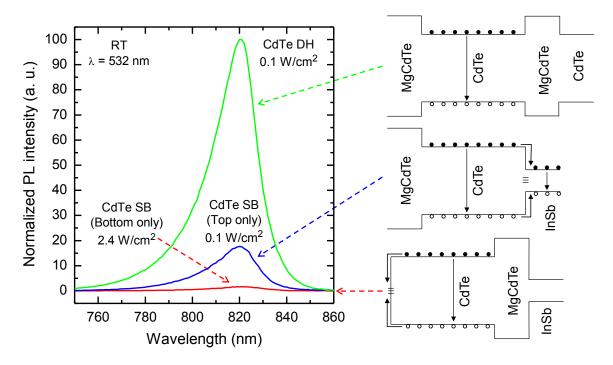

| 5.2. | Comparison of Photoluminescence Spectra for the CdTe/MgCdTe Double and            |    |

|      | Single Heterostructure Samples, along with Their Schematic Band Edge              |    |

|      | Diagrams Showing the Various Recombination Mechanisms                             | 42 |

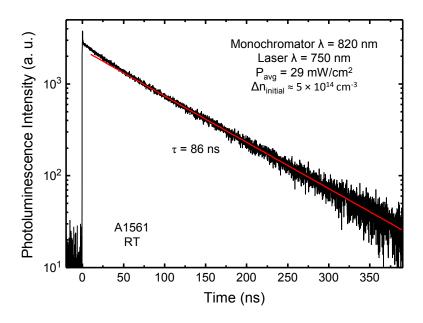

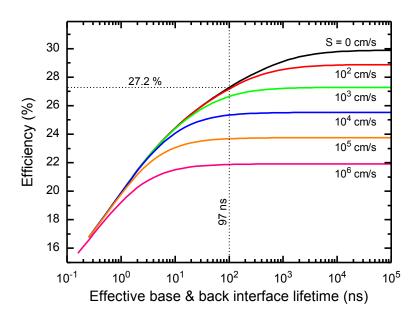

| 5.3. | Room Temperature Time-Resolved Photoluminescence Decay of the                     |    |

|      | CdTe/MgCdTe Double Heterostructure Grown on InSb. A Carrier Lifetime of           |    |

|      | 86 ns is Extracted Using a Single Exponential Decay Model                         | 44 |

| 5.4. | Comparison of PL Intensity and Carrier Lifetime as a Function of Substrate                          |

|------|-----------------------------------------------------------------------------------------------------|

|      | Growth Temperature                                                                                  |

| 5.5. | Comparison of PL Intensity and Carrier Lifetime as a Function of Cd/Te flux                         |

|      | Ratio                                                                                               |

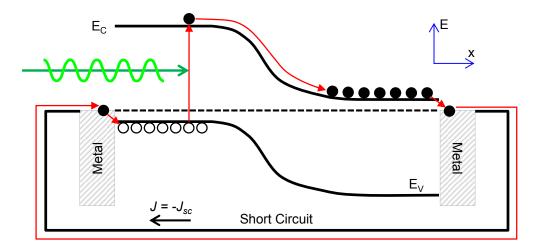

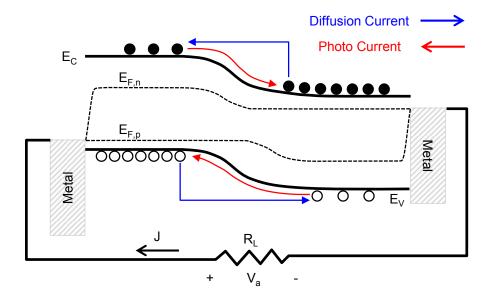

| 6.1. | Schematic Band Edge Diagram of a PN Junction Under Short Circuit Conditions                         |

|      | and with Illumination. Quasi-Fermi Levels are Omitted for Clarity 50                                |

| 6.2. | Schematic Band Edge Diagram of a PN Junction Under Illumination and with                            |

|      | Non-Zero Load Resistance                                                                            |

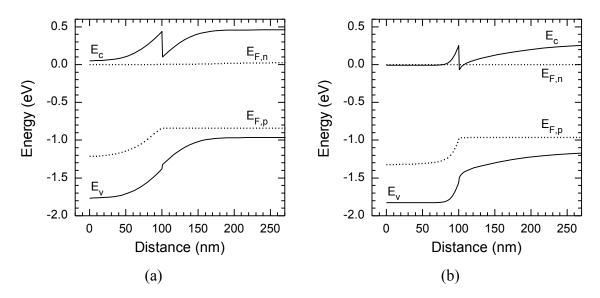

| 6.3. | Simulated Band Edge Diagrams of Symmetric (a, Left) and Asymmetric (b,                              |

|      | Right) PN Heterojunction at the Maximum Power Operating Point 58                                    |

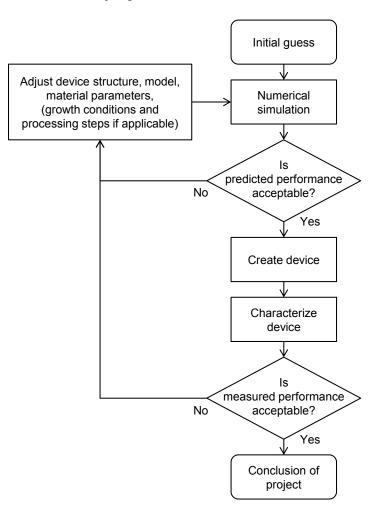

| 6.4. | Flow Chart Illustrating the Methodology to Study and Improve the Performance                        |

|      | of Monocrystalline CdTe Solar Cells                                                                 |

| 6.5. | Layer Structure of a ZnTe/CdTe/MgCdTe Double Heterostructure Mesa-Defined                           |

|      | Solar Cell                                                                                          |

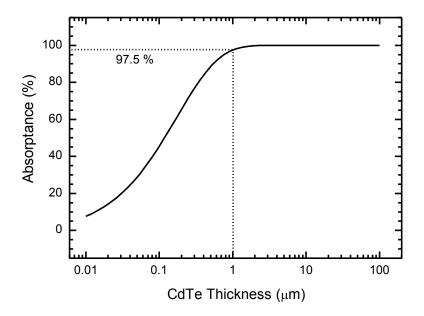

| 6.6. | Absorptance as a Function of CdTe Layer Thickness for the AM1.5G                                    |

|      | Spectrum                                                                                            |

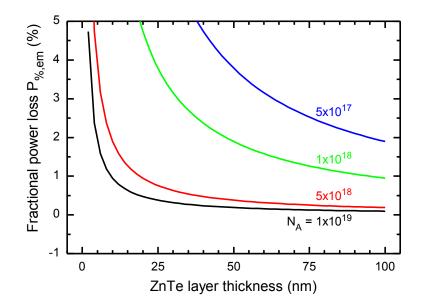

| 6.7. | Fractional Power Loss Due to Emitter Current Spreading Resistance as a                              |

|      | Function of ZnTe Thickness and Emitter Doping Concentration. A Mobility of                          |

|      | $50 \text{ cm}^2 \text{v}^{-1} \text{s}^{-1}$ and a Finger Spacing of 200 $\mu \text{m}$ is Assumed |

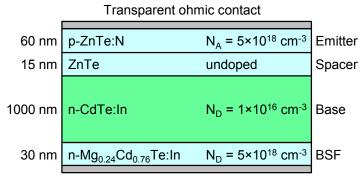

| 6.8. | Layer Structure Diagram Used as the Default Structure for the Numerical Device                      |

|      | Simulation                                                                                          |

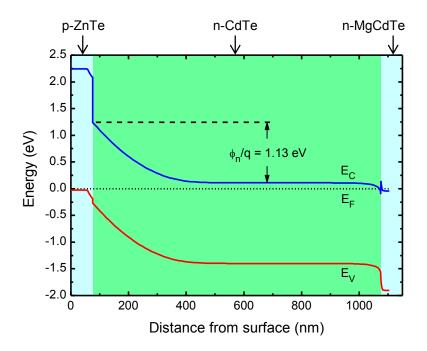

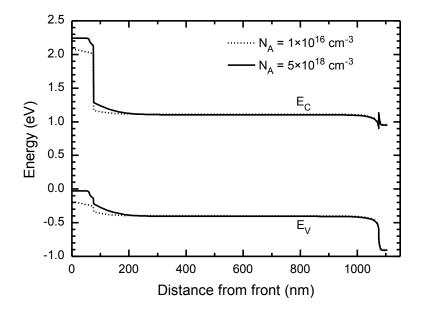

| 6.9. | Equilibrium Band Edge Diagram of the Default Structure in Fig. 6.8                                  |

| 6.10. | Band Edge Diagrams of Two Devices with Different Emitter Doping                  |

|-------|----------------------------------------------------------------------------------|

|       | Concentration under 1-Sun Concentration and at the Maximum Power Operating       |

|       | Point                                                                            |

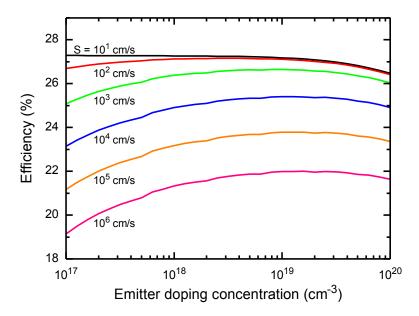

| 6.11. | Solar Cell Efficiency as a Function of Emitter Doping Concentration and          |

|       | Interface Recombination Velocity at the ZnTe/CdTe Interface                      |

| 6.12. | Solar Cell Efficiency as a Function of Emitter Doping Concentration and          |

|       | Interface Recombination Velocity at the ZnTe/CdTe Interface                      |

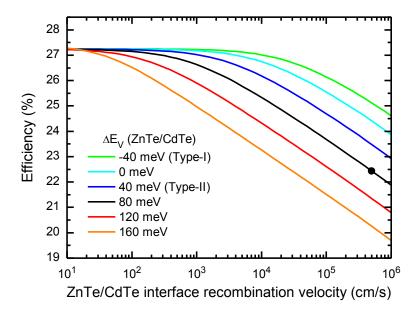

| 6.13. | Solar Cell Efficiency as a Function of ZnTe/CdTe Interface Recombination         |

|       | Velocity for Several Band Offsets. The black dot represents the efficiency based |

|       | on the reported values of interface recombination and band offset at the         |

|       | ZnTe/CdTe interface                                                              |

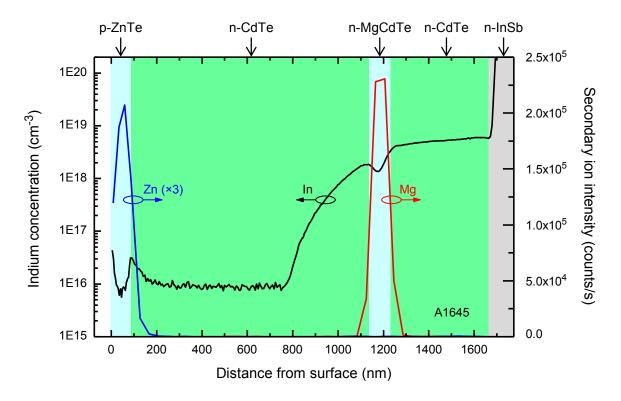

| 7.1.  | SIMS Depth Profile of the Completed Solar Cell Structure with a Calibrated In    |

|       | Trace                                                                            |

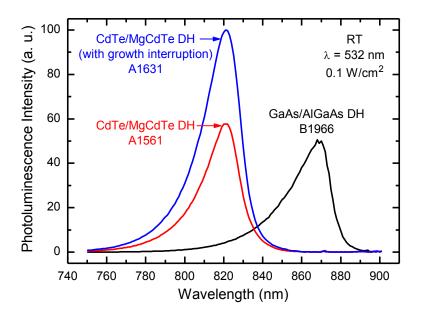

| 7.2.  | Room Temperature PL Spectra of a CdTe/MgCdTe DH with Growth Interruption         |

|       | in the Buffer Layer, the Uninterrupted DH Sample with 86 ns Lifetime, and the    |

|       | GaAs Reference Sample                                                            |

| 7.3.  | Solar Cell Layer Structure Design Matrix Showing Four Samples. All Values        |

|       | Listed Are Inferred from Calibrations                                            |

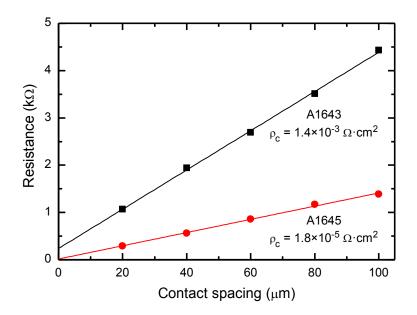

| 7.4.  | Contact Resistivity Determined by Resistance Vs. Contact Spacing for a TLM       |

|       | Pattern                                                                          |

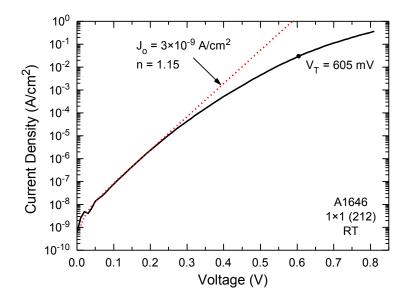

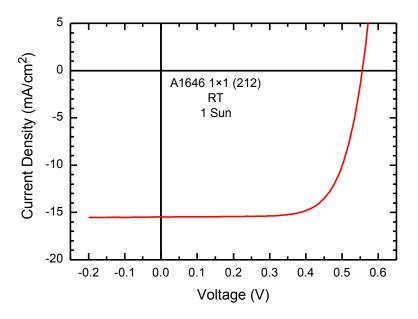

| 7.5.  | . Dark <i>J-V</i> Curve of the ZnTe/CdTe/MgCdTe DH Solar Cell at Room Temperat    |  |  |

|-------|-----------------------------------------------------------------------------------|--|--|

|       | (Solid) Plotted with the Ideal Diode Equation (Dotted). The Turn-On Voltage $V_T$ |  |  |

|       | is Defined at 30 mA/cm <sup>2</sup>                                               |  |  |

| 7.6.  | Photo J-V Curve of the ZnTe/CdTe/MgCdTe DH Solar Cell at Room                     |  |  |

|       | Temperature Under One Sun Concentration                                           |  |  |

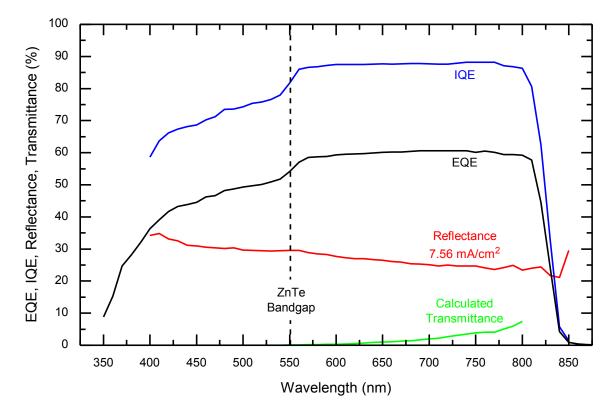

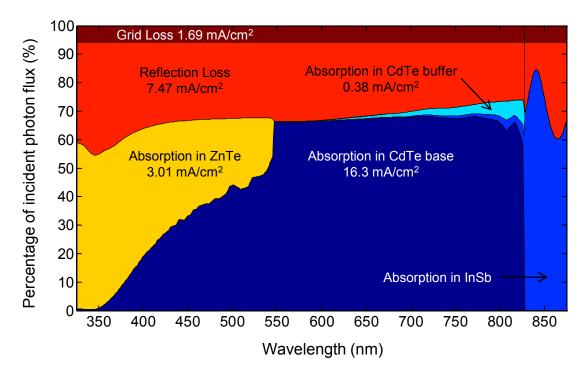

| 7.7.  | Internal and External Quantum Efficiency, Measured Reflectance, and Calculated    |  |  |

|       | Transmittance as a Function of Wavelength for the ZnTe/CdTe/MgCdTe DH             |  |  |

|       | Solar Cell Sample. The Current Loss Due to Reflectance is Calculated for the      |  |  |

|       | AM1.5G Spectrum                                                                   |  |  |

| 7.8.  | Calculated Reflectance and Absorptance as a Function of Wavelength for the        |  |  |

|       | ZnTe/CdTe/MgCdTe DH with the Structure of A1646. *Figure Provided by Yuan         |  |  |

|       | Zhao at ASU                                                                       |  |  |

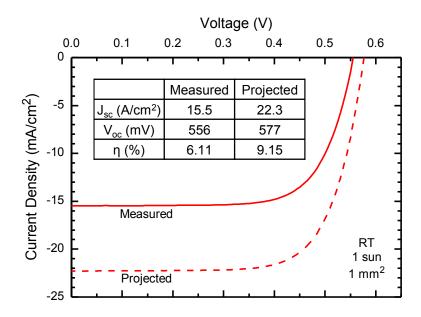

| 7.9.  | Measured J-V Curve of the ZnTe/CdTe/MgCdTe Solar Cell with Record High            |  |  |

|       | Efficiency and Projected Performance for the Same Cell with an AR Coating 88      |  |  |

| 7.10. | Efficiency and $V_{oc}$ as a Function of Temperature for Sample A1643 2×2 (211)   |  |  |

|       | Under One Sun Concentration                                                       |  |  |

| 7.11. | Scatter Plot of Efficiency Vs. Sample Number for Samples with i-ZnTe Spacer       |  |  |

|       | Layer (Black Triangles) and Without Spacer Layer (Red Squares) at Room            |  |  |

|       | Temperature and under One Sun Concentration                                       |  |  |

| 7.12. | Scatter Plot of $V_{oc}$ Vs. Sample Number for Samples with i-ZnTe Spacer Layer   |  |  |

|       | (Black Triangles) and Without Spacer Layer (Red Squares) at Room Temperature      |  |  |

|       | and under One Sun Concentration                                                   |  |  |

| 7.13. | Scatter Plot of $J_{sc}$ Vs. Sample Number for Samples with i-ZnTe Spacer Layer |  |  |

|-------|---------------------------------------------------------------------------------|--|--|

|       | (Black Triangles) and Without Spacer Layer (Red Squares) at Room Temperature    |  |  |

|       | and under One Sun Concentration                                                 |  |  |

Page

#### CHAPTER 1

## INTRODUCTION

In the quest for low-cost renewable energy, photovoltaic solar cells have emerged as a promising alternative to fossil fuels and other renewable energy sources. What is unique about solar cells is that they *directly* convert photons from the sun into electricity by utilizing the unique properties of semiconductors. Other technologies also derive their energy from the sun, but in indirect and less-efficient ways. For example, bio fuels are derived from plant matter that obtains energy from the sun using photosynthesis, which has a maximum light-to-biomass efficiency of only 8-9 % [1]. In contrast, the maximum theoretical efficiency of a single-junction solar cell is 33.7 % under AM1.5G illumination, as determined by the detailed-balance model and assuming the material has a band gap of 1.34 eV [2]. The relatively high efficiency and the high energy density of sunlight make photovoltaics (PVs) the most promising alternative electricity source.

Polycrystalline CdTe is one of several semiconductor materials that are currently being used in commercially-developed terrestrial PV installations. As a material, CdTe has a nearly ideal direct band gap of 1.51 eV and a large absorption coefficient, which makes it suitable for thin-film solar cells. Other competing technologies include silicon (mono-crystalline, poly-crystalline and amorphous), CIGS (copper indium gallium selenide), and concentrated photovoltaics using multi-junction III-V based junctions on Ge or GaAs substrates [2]. Their efficiencies vary, and all of them have unique device structures, advantages, and disadvantages. One important metric for terrestrial photovoltaics is the price-per-peak-watt output (measured at 1 sun concentration), noted as  $\$/W_p$ . In 2009, the US-based PV manufacturer First Solar was the first company to

surpass the \$1/ $W_p$  threshold using a CdTe/CdS heterojunction device deposited on glass panels [3]. Since then, the company has achieved an impressive \$0.40/ $W_p$  for productionquality CdTe modules that operate at 14.2 % efficiency [4], and the record module efficiency is 17.5 % [5]. On the other hand, the record monocrystalline Si module efficiency is 22.9 % [5], and the company Jinko Solar has achieved production-quality modules that operate at 16.5 % efficiency [6] and at a cost of \$0.47/ $W_p$  [7]. Clearly, CdTe-based panels have a lot of catching up to do in terms of panel efficiency, which is an important factor for rooftop and space-constrained applications. For these applications, gains in efficiency relate to larger balance-of-system savings compared to utility-scale applications [8]. Also, customers may value the total power output of a rooftop installation over the cost-per-watt metric. For these reasons, it is worthwhile to explore new ways of improving the CdTe cell efficiency and to determine the fundamental limits of this technology.

There has been considerable interest recently in demonstrating solar cells that reach their detailed-balance limit [9]. The motivation for this initiative is to demonstrate very high efficiency cells (albeit at higher cost) which represent the ideal structure for manufacturers to achieve through lower-cost manufacturing processes. Table 1.1 shows a comparison of the efficiencies for CdTe and GaAs solar cells in both polycrystalline and monocrystalline form. Also listed is the detailed balance limit for those materials, which is calculated assuming no non-radiative recombination, one sun concentration (AM1.5G spectrum), 25 °C operation, and a perfect rear reflector [10]. Monocrystalline GaAs shows the highest efficiency at 28.8 %, which is just 4.4 % (absolute) away from its detailed balance limit. Polycrystalline GaAs trails far behind at 18.4 %, which is expected

for materials with a high concentration of crystalline defects. On the other hand, the opposite is observed for CdTe. Most research on CdTe focuses on polycrystalline material due to the relatively low cost deposition and manufacturing process [2]. A record efficiency of 21 % has been achieved by First Solar which is far beyond that of polycrystalline GaAs [11]. Monocrystalline CdTe has not been studied significantly, presumably because the high cost of CdTe substrates are prohibitive for research and commercial applications. The highest efficiency for monocrystalline CdTe is only 13.4 %, which utilizes a CdTe/In<sub>2</sub>O<sub>3</sub> PN heterojunction [12]. Given the high efficiency achieved for polycrystalline CdTe, it would be reasonable to expect monocrystalline CdTe cells to achieve efficiencies approaching GaAs or even greater. Advances in materials and growth technology may open up an opportunity to demonstrate high-efficiency monocrystalline CdTe solar cells.

| Table 1.1. Demonstrated cell efficiencies and theoretical limits [5], [10]. |                   |                   |                  |

|-----------------------------------------------------------------------------|-------------------|-------------------|------------------|

| Matarial                                                                    | Polycrystalline   | Monocrystalline   | Detailed Balance |

| Material                                                                    | Record Efficiency | Record Efficiency | Limit            |

| CdTe                                                                        | 21.0 %            | 13.4 %            | 32.1 %           |

| GaAs                                                                        | 18.4 %            | 28.8 %            | 33.2 %           |

The relatively poor efficiency of polycrystalline CdTe cells comes from defect recombination losses, which is evidenced by the typically short carrier lifetimes of less than 6 ns [13]. It should be no surprise that defect recombination dominates in these devices considering the small grain size of 1  $\mu$ m, which provides a large surface area for grain boundary recombination [14]. Recently, our group has grown monocrystalline CdTe/MgCdTe double heterostructures (DHs) on InSb substrates using molecular beam epitaxy (MBE) which have a carrier lifetime of 86 ns for a 1  $\mu$ m thick CdTe layer [15]. Longer SRH lifetimes of 179 ns have also been demonstrated using a 2  $\mu$ m thick CdTe

layer, and up to 97 ns has been observed for the 1 µm thick CdTe layer by probing different areas on the wafer [16]. Based on this carrier lifetime and practical assumptions for material parameters (surface recombination, mobility, etc...), our modeling results show that monocrystalline CdS/CdTe solar cells can achieve efficiencies greater than 25 % [10]. Additional improvements are expected by replacing the relaxed CdS emitter layer with a coherently strained MgCdTe emitter. Although such a cell grown by MBE would be too expensive for the PV industry to commercialize, it can be used to investigate the fundamental limits of the material and develop an ideal CdTe structure, which may lead to improvements in commercially-produced polycrystalline CdTe solar cells.

## 1.1 CdTe-based heterostructures grown on InSb substrates

In order to understand the fundamental physics that limits the record efficiencies of polycrystalline and monocrystalline CdTe solar cells, it is highly desirable to have a model system in which various defect recombination mechanisms can be studied in a controlled manner. A double heterostructure (DH) with type-I band edge alignment provides a model system where the middle CdTe layer can be isolated and studied. Using steady-state photoluminescence (PL) and time-resolved photoluminescence (TRPL) measurements, the recombination mechanisms of bulk CdTe epilayers can be studied without the influence of surface recombination and carrier diffusion to the buffer layers and substrate. These DHs have been used in devices such as LEDs and lasers for many years by the MBE community [17]. It is also the standard structure for MBE calibration samples, of which the PL intensity and peak position give information about the optimal growth conditions and alloy compositions, respectively. However, these structures are not currently used by the CdTe community. For example, researchers use TRPL to study the properties of poly-CdTe solar cell structures [13]. The measured PL lifetime is related to the material quality but is complicated by the carrier dynamics of the PN junction. It is then necessary to perform simulations in order to analyze the multiple exponential decay characteristics observed in the TRPL. Another example is in the growth quality optimization of MBE-grown CdTe. Previous studies have used plain CdTe epilayers grown on InSb substrates without any carrier confinement [18, 19]. Surface recombination is likely to dominate in those samples, and the density and nature of surface states may be affected by the growth conditions. Therefore, the PL intensity may not be indicative of the bulk material quality but rather the impact of the surface. The aforementioned DH design is ideal for material quality investigation and optimization because of the relative simplicity of the PL analysis. Alternatively, surfaces and interfaces can be studied by growing samples with appropriate layer structures that separate the photogenerated carriers from the surface or interface, respectively. It is then clear that intelligent structure design coupled with PL measurements allows one to gain significant insight into material properties.

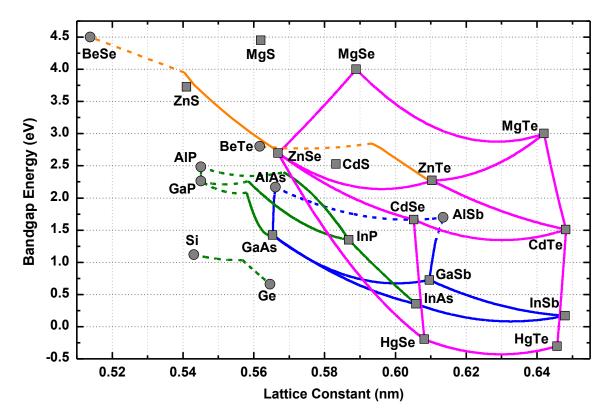

MgCdTe is the most practical alloy to form a barrier with CdTe. Figure 1.1 shows the band gap vs. lattice constant of many common semiconductors, where the lines connecting the binary materials represent random alloys containing the common cation or anion. The first consideration in choosing a barrier layer is the lattice constant and band gap. It is generally desirable for a device structure to be made of materials which are all lattice matched so that thick dislocation-free layers can be grown. MgCdTe, although not lattice-matched, provides the largest increase in band gap for the same corresponding change in lattice constant. Alloys with Zn, Be, and S also increase the band gap but correspond to a large decrease in the lattice constant, making them undesirable for CdTebased barrier layers. The second consideration is the band alignment and offsets. MgCdTe has a type-I band alignment with CdTe, and the valance band offset is 30 % of the difference between the two band gaps [20]. In a DH used for PL and TRPL measurements, it is desirable to have both electron and hole confinement in the conduction band and valance bands, respectively. MgCdTe can therefore provide the necessary confinement for both electrons and holes, and the dislocation density can be minimized by using thin layers with a moderately small Mg composition.

Figure 1.1. A diagram of experimentally measured band gaps vs. lattice constants of common semiconductors. Solid and dashed lines represent direct and indirect band gap alloys, respectively. *\*Figure provided by Dr. Ding Ding at ASU*.

CdTe can be grown on several commercially available substrates, but InSb is the most practical based on lattice mismatch, cost, and pre-existing knowledge of buffer layer growth procedures. The lattice mismatch between CdTe and InSb is incredibly small, only 0.03 %. This is even better than the famous GaAs/AlAs system which has a mismatch of 0.136 %. InSb wafers are commonly used for IR photodetectors and are available in diameters from 2" to 5" with impressive etch pit densities (EPD) of less than 50 cm<sup>-2</sup> [21]. The cost of an InSb substrate is roughly  $22 \text{ cm}^{-2}$ , which is considerably less than that of CdTe which is about \$500 cm<sup>-2</sup> and is only commonly available in  $1 \text{ cm} \times 1 \text{ cm}$  square pieces. Furthermore, the EPD of a CdTe wafer is around 3 orders of magnitude larger than that of InSb [22]. Since the etch pits are indicative of dislocations in the wafer, higher quality CdTe epilayers should be possible using InSb as long as an abrupt interface can be formed and the CdTe critical thickness is not exceeded. CdTe can be grown on GaAs using a ZnTe intermediate layer, but the severe lattice mismatch will result in lower material quality [23]. This structure may be useful for studying the effect of dislocations on CdTe, rather than for demonstrating the highest quality CdTe material or solar cell. Finally, it should also be noted that the growth of CdTe/MgCdTe structures has been previously demonstrated [24], and the growth of CdTe on InSb has also been demonstrated [25]. The novel aspect of this research is the combination of those two ideas for the applications of growth quality optimization, recombination physics investigation, and the exploration of the limits of CdTe solar cell efficiency.

## 1.2 Organization of the dissertation

Chapter 2 discusses the designs of the CdTe/MgCdTe PL structures used in this study, along with the basics of PL measurements. The choice of composition and

thickness of each layer is determined based on several considerations: critical thickness, barrier heights, and absorption of the PL pump laser. Several different structures are presented in order to determine various physical characteristics of CdTe. These characteristics are the bulk SRH recombination lifetime of CdTe, interface recombination velocity of the CdTe/MgCdTe interface, effect of surface recombination and diffusion of carriers to the buffer layers and substrate, and the effect of the growth temperature and Cd/Te flux ratio on the SRH lifetime of CdTe. An identical GaAs/AlGaAs DH is also grown as a comparison sample, and its sample structure is briefly discussed.

Chapter 3 discusses the MBE growth of the previously mentioned structures. This includes the fundamentals of MBE, *in-situ* characterization techniques, growth rate and Cd/Te flux ratio calibration, and specific details and procedures necessary for obtaining high quality materials. A growth condition optimization experiment is designed based on previous reports in literature. The goal is to increase the carrier lifetime in CdTe by finding the optimal substrate temperature and Cd/Te flux ratio.

Chapter 4 discusses the structural characterization of CdTe/MgCdTe DHs. Atomic force microscopy (AFM) is used to measure the surface roughness as a function of the growth conditions. Transmission electron microscopy (TEM) is used to show the crystalline quality of the InSb/CdTe interface. Finally, X-ray diffraction (XRD) and reciprocal-space maps (RSMs) are used to measure relaxation in the films, the composition of the MgCdTe barrier layers, and the overall crystalline quality of the structure.

Chapter 5 discusses the optical characterization of the samples, which includes PL and TRPL. The PL intensity is correlated with the carrier lifetime, as measured by TRPL.

It is shown through TRPL that the PL measurement conditions are performed under low injection, which is necessary to correlate the PL lifetime with the carrier lifetime. The lifetime is the most important metric used for gauging the material quality because it directly impacts solar cell performance and it is sensitive to both dislocations and point defects.

Chapter 6 discusses PN junction theory and how it relates to solar cells, along with the design of a ZnTe/CdTe/MgCdTe DH solar cell. This structure design is chosen over a MgCdTe/CdTe/MgCdTe DH because of the doping limitations of the II-VI chamber at ASU. This is explained in more detail within the chapter. Numerical simulations using the software PC1D [26] are used to optimize the structure design and to determine which design parameters have the greatest effect on the efficiency.

Lastly, chapter 7 discusses the growth, processing, and testing of the ZnTe/CdTe/MgCdTe DH solar cells. Testing of the solar cells includes current density vs. voltage (*J-V*) measurements both in the dark and under 1 sun concentration, as well as external quantum efficiency (EQE) measurements. These measurements coupled with additional modeling are used to explain the low efficiency measured for these devices. Future recommendations are presented, and the dissertation ends with a conclusion.

#### CHAPTER 2

## PHOTOLUMINESCENCE STRUCTURE DESIGN

CdTe photoluminescence (PL) layer structures are designed for the purpose of material characterization. The choice of barrier material, thickness, and alloy composition is based on the critical thickness and band offsets for that material with respect to CdTe. The basics of PL measurements are discussed, and several structures are presented which are useful for probing various material properties.

## 2.1 Critical thickness of CdTe and MgCdTe on InSb

One of the first considerations when designing a device structure is the critical thickness of lattice-mismatched epilayers. The critical thickness, denoted as  $h_c$ , is defined as the maximum thickness of an elastically strained epilayer in which the substrate and epilayer have the same in-plane lattice constant. Above the critical thickness, strain in the epilayer is relaxed by the formation of misfit dislocations. As more dislocations are generated, the lattice constant of the epilayer approaches its natural bulk value, and the layer becomes fully relaxed. Below the critical thickness, the epilayer is under compressive or tensile strain as it tries to match the in-plane lattice constant of the substrate. When there is no relaxation, the layer is referred to as coherently strained. For the materials considered here, CdTe grown on InSb is under a small compressive strain, while MgCdTe is under moderate tensile strain. It is generally known that dislocations act as non-radiative deep-level recombination centers, so the design must not allow for relaxation.

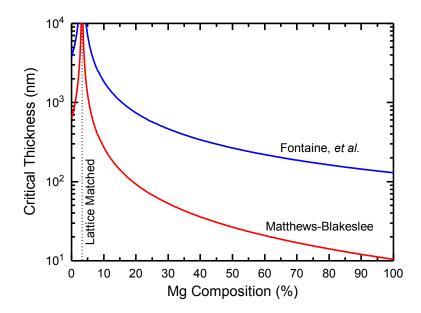

The critical thickness of CdTe and  $Mg_xCd_{1-x}Te$  on InSb is calculated using two different models, as shown in Fig. 2.1. The first model is one proposed by Matthews and

Blakeslee which involves balancing the line tension of a dislocation and the stress caused by the lattice mismatch [27]. It was originally proposed for the GaAs/GaAsP system. The critical thickness is given by:

$$h_{c} = \frac{a_{s} \left(1 - \frac{v}{4}\right) \left[ \ln\left(\frac{h_{c} \sqrt{2}}{a_{s}}\right) + 1 \right]}{k \sqrt{2}\pi |f|(1 + v)} , \qquad (2.1)$$

$$v = \frac{C_{12}}{C_{11} + C_{12}} \quad , \tag{2.2}$$

$$f = \frac{a_s - a_l}{a_l} \quad , \tag{2.3}$$

where  $a_s$  and  $a_l$  are the substrate and epilayer lattice constants, respectively, *v* is Possion's ratio,  $C_{11}$  and  $C_{12}$  are the elastic stiffness parameters of the epilayer, and *k* is a constant equal to 4 for single epilayers (as opposed to quantum wells and superlattices). The material parameters are given in Appendix A. This model gives a critical thickness for CdTe on InSb of only 620 nm. The second model, proposed by Fontaine, *et al.*, is based on empirical XRD measurements of CdTe grown on Zn<sub>0.04</sub>Cd<sub>0.96</sub>Te substrates [28]. XRD is used to measure the in-plane lattice constant, which is then used to calculate the stress of the epilayer. They found that above a critical thickness, the product of stress and the thickness remains constant, which indicates that the 2D density of misfit dislocations is increasing as the epilayer thickness increases. The critical thickness product and is given by:

$$h_c = \frac{\sum_{001}}{H_{001}|f|} \quad , \tag{2.4}$$

$$H_{001} = C_{11} + C_{12} - \frac{2C_{12}^2}{C_{11}} , \qquad (2.5)$$

where  $H_{001}$  is the biaxial modulus, and  $\Sigma_{001}$  is the product of stress and the critical thickness which is equal to 46 J·m<sup>-2</sup> for CdTe according to XRD measurements [28]. Equations (2.4) and (2.5) give a critical thickness of 3.8 µm for CdTe on InSb, which is nearly an order of magnitude larger than the Matthews-Blakeslee model. The discrepancy could be explained by the differing nature of dislocations in the GaAs/GaAsP and CdTe/InSb systems, which is beyond the scope of this dissertation. For the purpose of designing a PL structure, it appears that the model proposed by Fontaine, *et al.* may be the most relevant to the CdTe/MgCdTe/InSb system.

Figure 2.1. Calculated critical thickness of  $Mg_xCd_{1-x}Te$  on InSb using two different models.

## 2.2 Design of the MgCdTe barrier layer

The MgCdTe barrier layer must meet several criteria in order to be both practical and effective. The composition and thickness must be carefully chosen based on

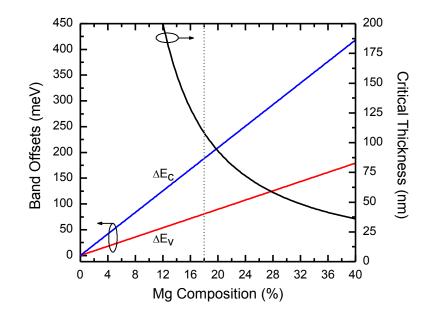

electronic, optical, and growth (materials) perspectives. From an electronic perspective, the potential energy height of the barrier (known as barrier height) must be large enough to block thermally-excited high-energy carriers. One can set an arbitrary minimum barrier height of  $3k_BT$ , where  $k_B$  is the Boltzmann constant and T is the temperature in kelvin. At room temperature,  $3k_BT$  is roughly equal to 76 meV. The barrier height is determined by the Mg composition of the alloy, as shown in Fig. 2.2. The upper limit of the Mg composition is determined by the reactivity of Mg in air (specifically water). Alloys up to 65 % have been shown to be stable [24], while pure MgTe reacts with air. As for the thickness of the barrier, it must be thick enough to prevent quantum tunneling. A minimum barrier thickness of a few tens of nanometers is generally considered to be sufficient to prevent tunneling. The maximum barrier thickness is determined by the critical thickness and absorption losses of the PL pump light. As shown in Fig. 2.2, a Mg composition of 18 % gives a valance band offset of  $\Delta E_v = 80$  meV and a conduction band offset of  $\Delta E_c = 188$  meV. 30 nm is chosen as the thickness since it is sufficient enough to prevent tunneling and is well below the critical thickness as determined by the Matthews-Blakeslee model. 18 % Mg composition therefore is the lower limit for this structure. It will be shown later through experiments that the barrier is sufficient to block the diffusion of photogenerated carriers.

Figure 2.2. Band offsets for CdTe/Mg<sub>x</sub>Cd<sub>1-x</sub>Te, assuming that MgTe has a band gap of 3.0 eV, band gap bowing is negligible, and  $\Delta E_{\nu}$  is 30 % of the difference in the band gaps. The critical thickness is calculated using the Matthews-Blakeslee model as a conservative estimate.

The effect of strain on the MgCdTe barrier layer must also be considered. Tensile strain causes the band gap to be reduced, while the heavy- and light-hole bands split. The magnitude of this effect is determined by the amount of strain, the elastic stiffness parameters, and the deformation potentials [17, pp. 136-138]. Some of the deformation potentials are not known accurately for CdTe [29], so the largest value is assumed as a conservative estimate. Based on the equations provided by Chuang [17, pp. 136-138], the maximum band shifting that can be expected is only 9 meV each for the valance and conduction bands. The splitting of the heavy and light hole bands is less than 1 meV. It can therefore be concluded that the effect of strain on the band edges is negligible, since the band offsets are still close to  $3k_BT$ .

## 2.3 Basics of PL measurements and PL sample structure designs

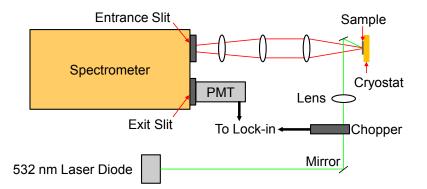

A typical PL measurement setup is shown in Fig. 2.3. The sample is mounted on the cold finger of a cryostat in a position perpendicular to the optical input axis of the spectrometer. A 532 nm laser diode is used as the pump source because that wavelength is readily absorbed by CdTe, and the absorption coefficients of CdTe and GaAs are similar at that wavelength [30]. The laser passes through a chopper wheel to modulate the excitation source, which allows for the lock-in technique to be used. The laser is then focused onto the sample with a spot size around 50 µm. Photoluminescence from the sample is collected by a series of lenses and an image of the PL spot is focused onto the entrance slit of the spectrometer. The light then reflects off of two diffraction gratings placed in series, which disperses the PL light across the exit slit. By rotating the gratings, the spectrometer acts as a tunable bandpass filter. The resolution of the spectrometer is determined by the entrance and exit slit widths, which are typically around 1 mm. A photomultiplier tube (PMT) is used to detect the PL light that passes through the exit slit. Lastly, a lock-in amplifier is used to selectively measure the PL signal which is modulated at a frequency around 100 Hz by the chopper wheel. A similar setup is used for TRPL measurements, with some modifications. The laser diode and chopper is replaced with a 530 nm high speed pulsed laser operating at 2 MHz with a peak width of 6 ps. A high speed PMT is used, and the lock-in amplifier is replaced with a timecorrelated single-photon counting system. Also, a single grating spectrometer is used for higher throughput and wider spectral bandwidth.

Figure 2.3. Basic setup for steady-state PL measurements.

The layer structure and schematic band edge diagrams for the CdTe/MgCdTe DH are shown in Fig. 2.4. An identical GaAs/AlGaAs DH sample is also grown using the same layer thicknesses and Al<sub>0.3</sub>Ga<sub>0.7</sub>As barrier layers. The main objective of the design is to generate carriers in the 1 µm thick middle layer using the pump laser, and then capture the luminescence from that layer. The two barriers prevent the carriers from diffusing to the surface and buffer layers. The cap layer is used as a precaution to prevent oxidation of the MgCdTe and AlGaAs barriers, while the buffer layers are used to smooth the surface of the wafer, which improves the material quality of the subsequent layers. The thickness of the middle layer is designed so that very few photons reach the buffer layers. This is done so that PL is not generated in those layers, which would make analysis more difficult. Table 2.1 shows the various loss mechanisms for the pump laser, which is calculated using the Beer-Lambert law for absorption and assuming the laser is at normal incidence to the sample. Since only a small fraction of the pump light reaches the back barrier, it can be assumed that the buffer layer doesn't contribute significant PL.

Figure 2.4. (a) Layer structure diagram and (b) schematic band edge diagram for the CdTe/MgCdTe DH PL structure.

| ruble 2.1. Roboroed pump inght in various layers. |                                                                                       |  |

|---------------------------------------------------|---------------------------------------------------------------------------------------|--|

| CdTe/Mg <sub>0.18</sub> Cd <sub>0.82</sub> Te     | GaAs/Al <sub>0.30</sub> Ga <sub>0.70</sub> As                                         |  |

| 27.1 %                                            | 37.4 %                                                                                |  |

| 5.30 %                                            | 4.25 %                                                                                |  |

| 9.90 %                                            | 6.25 %                                                                                |  |

| 0.03 %                                            | 0.05 %                                                                                |  |

|                                                   |                                                                                       |  |

| 57.7 %                                            | 52.1 %                                                                                |  |

|                                                   |                                                                                       |  |

|                                                   | CdTe/Mg <sub>0.18</sub> Cd <sub>0.82</sub> Te<br>27.1 %<br>5.30 %<br>9.90 %<br>0.03 % |  |

Table 2.1. Absorbed pump light in various layers.

The schematic band edge diagram in Fig. 2.4b shows the various recombination mechanisms and carrier diffusion, which are expected for the DH. First, electron-hole pairs (EHPs) are generated with a total energy of 2.33 eV, which is equal to the energy of the pump photons. EHPs are mostly generated in the cap, top barrier, and middle layers, as outlined in Table 2.1. The carriers relax to the band edge by emitting phonons, and the carriers can diffuse for a short period of time before recombining. The four significant recombination mechanisms expected for this structure are radiative, Shockley-Read-Hall (SRH), CdTe/MgCdTe interface, and surface recombination. In the cap layer, it is assumed that surface recombination dominates over the other three recombination mechanisms, since the surface is not passivated and there is a high density of surface

states. Carriers generated in the cap layer will be trapped by the MgCdTe barrier and will mostly recombine through surface recombination. Carriers in the barrier layer will quickly diffuse to the lower band gap CdTe layers, and so very little recombination should take place there. Within the middle CdTe layer, only SRH, interface recombination, and radiative recombination are likely to take place. This is because the pump laser is not powerful enough to create the high carrier concentrations which are necessary for Auger recombination. Therefore, the vast majority of PL photons detected should come only from the middle CdTe layer, and the intensity and carrier lifetime observed should be indicative of the bulk and interface properties of the middle CdTe layer.

Two additional layer structures are shown in Figs. 2.5 and 2.6 which are designed to measure the effect of surface and buffer layer recombination, respectively. Both structures are similar to the DH discussed previously, except one of the barriers is omitted from the design. For the structure shown in Fig. 2.5, EHPs are mostly generated in the first few hundred nanometers of the top CdTe layer. Those carriers can diffuse and recombine via surface recombination, in addition to radiative, SRH, and interface recombination. Likewise, for the structure shown in Fig. 2.6, a majority of EHPs are generated in the 1 µm thick CdTe layer. Those carriers can then diffuse to the CdTe/InSb interface and recombine via interface recombination or within the InSb buffer layer. The relative effect of these recombination mechanisms can be determined by comparing the PL intensity of these structures to the DH sample. Furthermore, the comparison also qualitatively indicates the effectiveness of the MgCdTe barrier layers. If the barriers have relatively low interface recombination velocity, then the PL intensity of the DH sample should be much larger than that of the single barrier samples.

Figure 2.5. (a) Layer structure diagram and (b) schematic band edge diagram for the CdTe/MgCdTe single barrier structure (bottom only).

Figure 2.6. (a) Layer structure diagram and (b) schematic band edge diagram for the CdTe/MgCdTe single barrier structure (top only).

In summary, various structures can be used to selectively test the effect of different recombination mechanisms. The double heterostructure (or double barrier) design is used for probing the bulk properties of CdTe, while single heterostructure (or single barrier) designs are used for probing the surface and buffer layers. The following chapter discusses how the material quality of CdTe/MgCdTe DHs are optimized. The single barrier structures are then grown using the optimized growth conditions.

## CHAPTER 3

## MOLECULAR BEAM EPITAXIAL GROWTH OF CdTe/MgCdTe ON InSb

The fundamentals of MBE are discussed, with emphasis on the concepts that are important for the high-quality growth of monocrystalline layers. A brief literature review of CdTe growth is presented in order to lay the foundation for designing a growth optimization experiment. *In-situ* characterization techniques and basic calibration results are also discussed.

#### 3.1 Fundamentals of MBE and overview of growth

Molecular beam epitaxy (MBE) is a semiconductor deposition technique which offers several unique advantages compared to other techniques. Generally speaking, deposition (henceforth referred to as growth) using MBE involves exposing a heated wafer to atomic or molecular fluxes, which takes place inside an ultra-high vacuum (UHV) chamber. Wafer heating is necessary to improve the surface migration of adsorbed atoms and to sublimate excess flux from the surface, both of which ensure that stoichiometric films can be grown with high structural quality. For example, high-quality stoichiometric GaAs is routinely grown with As/Ga flux ratios of 1.5 when the substrate is heated to around 550 °C. Without substrate heating, which is typical in thermal and electron-beam evaporation, the flux will condense on the wafer without preference for forming a stoichiometric single crystal. Having the ability to heat the substrate also allows for thermal oxide removal and decontamination of the wafer surface prior to deposition. This is essential for forming a good interface and a film with low dislocation density. The UHV condition is also necessary to remove wafer contamination and to reduce the bulk impurity density in the epilayer. Wafers and their holders are typically decontaminated (outgassed) using a substrate heater in a separate UHV chamber attached to the growth chamber. Without UHV, residual gases such as H<sub>2</sub>O, O<sub>2</sub>, and CO<sub>2</sub> will condense back on the wafer and re-contaminate the surface. Wafers are outgassed in a separate chamber to prevent contamination of the growth chamber, since the epilayer impurity density is a function of the background pressure in the growth chamber. For example, to obtain a C impurity concentration less than  $10^{14}$  cm<sup>-3</sup> at a growth rate of 1 µm/h, the CO partial pressure in the chamber must be less than  $2 \times 10^{-12}$  Torr [31, pp. 1-38]. This is easily possible using available pump and chamber technologies, as well as maintaining cleanliness during maintenance periods when the chamber is opened.

MBE also allows for several *in-situ* characterization and process monitoring techniques. Flux monitoring, substrate temperature measurement, and reflection highenergy electron diffraction (RHEED) are the most used in this study. Flux monitoring is used prior to growth to measure the relative flux vs. temperature characteristic of the cell. This is performed by placing an ion gauge in front of the substrate and measuring the resulting ion gauge current from the cell as the temperature is adjusted. This is important for calibrating the flux ratio, as will be discussed later. Substrate temperature measurements are performed during every growth using a pyrometer. The pyrometer is a calibrated InGaAs photodetector which senses the blackbody radiation from the wafer. Based on the intensity of thermal radiation and emissivity of the wafer at the detection wavelength, the temperature is calculated using Planck's law. Detection wavelengths of 950 nm and 1150 nm are used for GaAs and InSb wafers, respectively. It's important to note that the wafers are opaque at those wavelengths (due to optical absorption above the band gap), which is necessary for detecting blackbody radiation from the semiconductor. The pyrometer used for the InSb wafer allows for temperature measurements down to 250 °C, which is useful for CdTe growth at low temperatures.

RHEED is the most important *in-situ* characterization technique used in this study, simply because of the vast amount of information it provides about the growth. In this technique, a collimated electron beam with a diameter of a few mm strikes the wafer at a glancing angle of only a few degrees from the surface. The electron kinetic energy is 15 keV, and so the electron wavelength is much less than the lattice spacing. Electrons diffract off of the wafer surface and form an image on a phosphor screen, creating what is called a RHEED pattern or image. Because of the glancing angle of the electron beam, only the top few monolayers (MLs) will contribute to the RHEED image, which makes this technique highly sensitive to the atomic configuration of the surface. Several characteristics can be observed. First, surfaces that are oxidized will give hazy RHEED patterns because of the random arrangement of atoms on the surface. This is important for monitoring the oxide removal process. In contrast, smooth surfaces of a monocrystalline wafer will give a pattern of parallel streaks. The brightness and spacing of the streaks is indicative of the atomic periodicity of the surface. Atoms on the surface of a crystal will re-arrange themselves to form the lowest energy state, which is referred to as a surface reconstruction. It is widely known that the reconstruction (and therefore RHEED pattern) is sensitive to the material being deposited, the lattice spacing near the surface, and the growth conditions including substrate temperature  $(T_s)$  and flux ratio. RHEED is most useful during growth for monitoring the surface condition, which can drastically change if there's a system problem or error. For example, if a shutter fails to open, the surface can become rough and the RHEED pattern will become spotty. This

technique is also useful for measuring the growth rate. It's commonly observed that the intensity of the zero order diffraction streak oscillates during growth, with each oscillation corresponding to the growth of 1 ML [31, pp. 1-38]. This oscillation is observed for the 2D growth mode, which starts with the formation of 1 ML thick islands followed by a coalescence of those islands. The growth rate can then be used to determine the 1:1 flux ratio, as described in section 3.3.

The MBE system used in this study is a dual-chamber "solid-source" MBE system which was recently upgraded to grow II-VI materials. Two separate chambers are used to grow III-V and II-VI materials in order to prevent cross contamination. Specifically, As is known to be highly mobile in a vacuum chamber, while Cd and Se have similar vapor pressures to As [32]. The chambers are connected by a UHV transfer chamber, which has a heating stage for outgassing wafers. The system is considered to be "solid source" because there are no gas sources (AsH<sub>3</sub>, PH<sub>3</sub>, etc..), although some of the sources are operated above the melting point (notably Ga and Al). For MgCdTe growth, three separate cells are used which consist of graphite crucibles loaded with pieces of Mg, Cd, and Te. The crucibles are heated using tantalum filaments and the temperature is monitored using a thermocouple.

The growth procedure for CdTe samples is briefly outlined in the following. First, a 2" InSb wafer is diced into quarters, and one piece is mounted onto the center of a 3" Si wafer using indium. The Si carrier wafer is mounted on a molybdenum holder and loaded into the system. Note that for the solar cell growths described in chapter 7, whole 2" InSb wafers are loaded in place of the Si carrier wafer, and no indium is used. The wafer and holder is outgassed at 200 °C for 1 hour and then transferred to the III-V chamber for

oxide removal and buffer layer growth. The conditions for oxide removal and InSb growth has been reported elsewhere [33]. After the InSb buffer layer growth, the wafer is transferred to the II-VI chamber and the temperature is raised to the desired growth temperature. At this time, the cells have already been brought up to the operating temperature and stabilized for 30 minutes. At  $T_s = 240$  °C, the Cd shutter is opened in order to saturate the surface with Cd. It is known that group VI elements react with group III [34], so a half monolayer of Cd is deposited on the surface before the Te shutter is opened. The Cd shutter can be left open for several minutes, since the substrate temperature is high enough to prevent multiple layers from depositing. When the substrate temperature is stabilized, a computer program is initiated which starts the growth and controls the Mg, Cd, and Te shutters and cell temperatures. An initial Cd/Te flux ratio of 3.5 is used for the first two minutes of growth in order to further prevent the reaction of Te with the substrate [34]. The flux ratio is then ramped down to the desired value within 5 minutes. Figure 3.1 shows typical RHEED patterns for InSb directly after transfer into the II-VI chamber and CdTe after 10 minutes of growth. The streaky patterns indicate that relatively smooth, monocrystalline layers have been grown. When the growth is complete, the shutters are automatically closed and the wafer temperature is ramped down. The wafer holder is then unloaded and the InSb piece is removed from the Si carrier wafer.

Figure 3.1. RHEED patterns along the (001) direction for InSb at 200 °C (left) and along the (011) direction for CdTe at 265 °C (right).

# 3.2 Review of CdTe/MgCdTe growth conditions

Several studies have been published on the growth of CdTe and MgCdTe, although none of the studies give a comprehensive overview of the entire parameter space. In order to be considered "comprehensive," the growth quality must be studied as a function of substrate temperature, flux ratio, growth rate, and preparation procedures. The metric for growth quality will depend on the desired outcome; in this case an improvement in the carrier lifetime is desired. Several factors likely contribute to the relative lack of data in the literature, such as the cost of substrates and source material (particularly CdTe wafers and Mg source material), insufficient "critical mass" of researchers in the II-VI area, and the use of polycrystalline material for low-cost photovoltaics instead of high-quality monocrystalline material. However, there have been some basic studies, particularly in the '80's and early '90's. These studies act as a guide for further exploration of the growth parameter space.

Several material properties must be simultaneously considered when defining the practical limits of the growth window. Table 3.1 shows the equilibrium vapor pressures for various elements at 300 °C, which is a common growth temperature for CdTe. In general, a non-unity flux ratio is typically used, where the material with the larger vapor

pressure has the larger flux. For GaAs, excess As is provided and the growth rate is determined only by the Ga flux. On the other hand, Cd has a higher vapor pressure than Te, so conventional wisdom would say that the material should be grown in Cd-rich conditions.

| Table 3.1. Equilibrium vapor pressures [32]. |                                          |  |  |  |

|----------------------------------------------|------------------------------------------|--|--|--|

| Element                                      | Vapor pressure at 300 °C                 |  |  |  |

|                                              | (Torr)                                   |  |  |  |

| Mg                                           | 2×10 <sup>-5</sup>                       |  |  |  |

| Cd                                           | 4×10 <sup>-2</sup>                       |  |  |  |

| Te                                           | 1×10 <sup>-4</sup>                       |  |  |  |

| Ga                                           | << 1×10 <sup>-8</sup>                    |  |  |  |

| As                                           | $4 \times 10^{-2}$<br>$5 \times 10^{-8}$ |  |  |  |

| Sb                                           | 5×10 <sup>-8</sup>                       |  |  |  |

An experimental study which measured the lower growth temperature limit concluded that Cd-rich growth conditions lead to higher quality CdTe [35]. It is shown that there is a minimum threshold temperature for which monocrystalline CdTe can be formed, below that temperature polycrystalline material is obtained. This threshold is 205 °C for Te-rich growth and only 85 °C for Cd-rich growth. Polycrystalline material is usually formed when the surface migration is too low to form an ordered crystal, so this finding suggests that Cd-rich surfaces have higher migration of adsorbed atoms (adatoms). It is desirable to maximize the adatom migration using flux ratio rather than using a higher growth temperature, since the formation of point defects such as vacancies and interstitials increases with temperature [31, pp. 1-38]. Therefore, the flux ratio is just as important as the growth temperature when optimizing the growth conditions.

The maximum growth temperature is determined by the desorption rate and the tolerance for point defects. RHEED oscillations have been used to measure the desorption rate of CdTe as a function of temperature [24]. A maximum growth

temperature of 340 °C corresponds to a desorption rate of 0.16 Å/s, which is 10 % of the growth rate used in this study (1.6 Å/s). The effect of point defects is more difficult to determine. One study reported the low temperature (2 K) PL spectra of samples grown at different temperatures and concluded that 185 °C is the optimal growth temperature [18]. This optimization is based on maximizing the ratio of free-excitation emission intensity to deep level photoluminescence. Unfortunately, the analysis of the result is complicated by the fact that a compound CdTe source was used for growth, so the surface condition (Cd or Te rich) could not be controlled. Also, this temperature seems unusually low in comparison to the commonly used substrate temperature of 300 °C [31, pp. 311-341].

For the growth of MgCdTe, there are no publications on the optimization of the growth conditions, however MgCdTe/CdTe structures have been demonstrated [36]. The only information available is that MgCdTe can be grown at the same substrate temperature as CdTe, and that the sticking coefficient of Mg is larger than Cd [37]. Since the growths in this study take place in the Cd-rich regime, there is competition between Mg and Cd for the group II lattice positions. Mg will displace Cd due to its larger sticking coefficient, however it is difficult to predict the Mg composition since the sticking coefficients are not accurately known. X-ray diffraction experiments can be performed to determine the composition, as described in the next chapter.

# **3.3** Growth calibration and optimization

The calibration of the CdTe growth conditions is performed using RHEED oscillations to measure the growth rate. CdTe is grown on an InSb wafer using the procedures outlined previously. After 30 minutes of growth, the CdTe layer is smooth enough to begin calibrations. A camera and computer software is used to select the zero

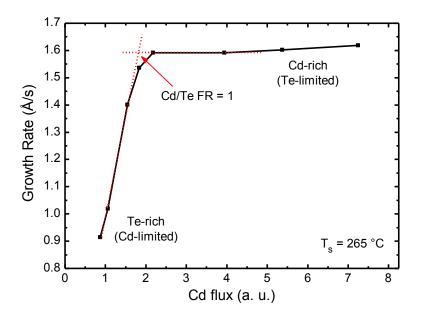

order (011) diffraction streak, and the average intensity is monitored over time. The oscillations are initiated by shutting the Te shutter for several seconds, then opening it again to resume the growth. Approximately 10 oscillations occur before the intensity dampens. The software is then used to fit the intensity curve to a decaying sinusoidal curve and obtain the growth rate. Figure 3.2 shows the growth rate as a function of Cd flux with fixed Te flux and a substrate temperature of 265 °C. An almost linear increase in the growth rate is observed with increasing Cd flux, followed by a saturation of the growth rate. The saturation indicates that the growth rate is limited by the Te flux. A growth rate of approximately 1.6 Å/s (576 nm/h) is achieved, which is typical for MBE. The linear and constant portions are extrapolated to find the Cd flux which gives a Cd/Te flux ratio of unity. Non-unity values are then determined using the measured flux vs. cell temperature profile for Cd.

Figure 3.2. CdTe growth rate as a function of Cd flux with the Te flux kept constant. The intersection of the linear region (Cd-limited) and saturation growth rate (Cd-rich) gives the growth conditions where the Cd/Te flux ratio is unity.

A growth optimization experiment is designed to determine the effect of flux ratio and  $T_s$  on the carrier lifetime. Table 3.2 shows the "one-factor-at-a-time" design used in this study. The flux ratio is first set to 1.5 and  $T_s$  is varied. When the optimal  $T_s$  is found, the flux ratio is varied while keeping  $T_s$  constant. A flux ratio of 1.5 was chosen as a first guess because that is the flux ratio used for GaAs by our group. Throughout this study, the Mg and Te cell temperatures are fixed at 500 °C and 425 °C, respectively. It should be noted that this design assumes that the growth rate doesn't change significantly as a function of  $T_s$ . Previous studies have shown that the growth rate only varies by 7 % when  $T_s$  varies from 235 °C to 295 °C [24].

Table 3.2. Growth conditions and sample numbers for seven samples used in the optimization of the material quality

| Cd/Te<br>flux ratio | Substrate temperature (°C) |       |       |       |       |  |

|---------------------|----------------------------|-------|-------|-------|-------|--|

|                     | 235                        | 250   | 265   | 280   | 295   |  |

| 1.8                 |                            |       | A1568 |       |       |  |

| 1.5                 | A1565                      | A1564 | A1561 | A1571 | A1566 |  |

| 1.2                 |                            |       | A1567 |       |       |  |

Lastly, the effectiveness of the MgCdTe barriers are evaluated by growing samples with one of the barriers removed. The growth conditions are similar to that of sample A1561, which is  $T_s = 265$  °C and a flux ratio of 1.5. As will be shown in the following chapters, those growth conditions are optimal for CdTe/MgCdTe structures grown on InSb substrates using our MBE system. The sample numbers are A1572 and A1573, which have only the bottom barrier and top barrier, respectively.

## **CHAPTER 4**

#### STRUCTURAL CHARACTERIZATION OF CdTe/MgCdTe STRUCTURES

Several structural characterization techniques are carried out in order to determine the overall crystalline quality and provide feedback to the grower for calibrating the growth conditions. These measurements are typically carried out when new structures are grown for the first time, or when layer compositions and thicknesses need to be verified. Roughness measurements are carried out on samples used in the growth optimization experiment, the crystalline quality is verified by transmission electron microscopy images, and the Mg composition in the MgCdTe layer is verified by X-ray diffraction measurements.

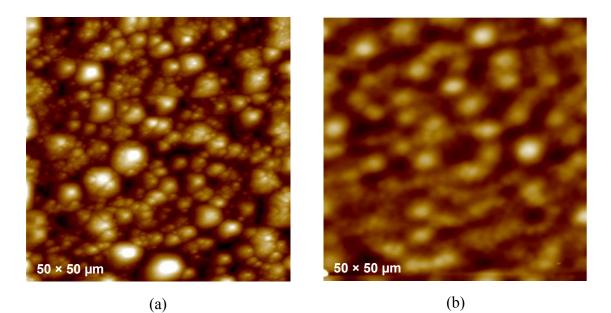

## 4.1 Investigation of surface roughness using atomic force microscopy

Surface roughness is one of several metrics which represents the material quality of an epilayer. For ultra-smooth surfaces formed using the 2D growth mode, single step edges with a height of 1 monolayer will be observed. Therefore the surface roughness will be on the order of the monolayer thickness or less. Figure 4.1 shows atomic force microscopy (AFM) images of an InSb buffer layer surface and a CdTe surface after the growth of a CdTe/MgCdTe DH on InSb. The InSb surface has an RMS roughness of 1.86 nm, which is considerably larger than the monolayer thickness. When a smaller region is imaged, each hill is seen to be made of multiple step edges, which indicates a step-flow growth mode for InSb. The CdTe surface shows similar sized features, but the image is blurred and individual step-edges cannot be observed. The reason for the blurred image is not evident, but is repeatable on all CdTe samples.

Figure 4.1. Atomic force micrographs of (a) an InSb buffer layer (B2034) and (b) a CdTe/MgCdTe DH grown on InSb with  $T_s = 265$  C and a Cd/Te flux ratio of 1.5 (A1579). The z-range for both figures is  $\pm 6$  nm.

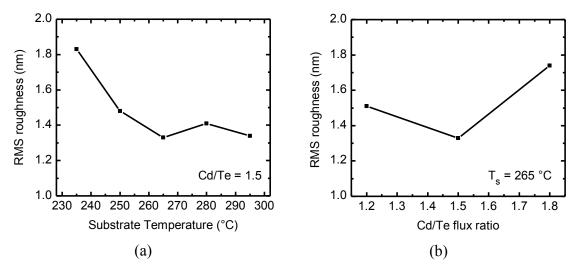

Figure 4.2 shows the effect of growth conditions on the surface roughness of CdTe/MgCdTe DHs. A clear trend is observed for the effect of growth temperature. Increasing growth temperature leads to smoother CdTe surfaces, which is expected because higher temperature leads to higher adatom migration on the surface during growth. The effect of flux ratio is not obvious since there are not enough data points. However, the lowest surface roughness occurs at the optimal flux ratio (as will be shown in chapter 5). It is important to note that all CdTe surfaces have a smaller RMS roughness compared to the InSb surface, which indicates that smoothing occurs during CdTe growth. Optimization of the InSb growth conditions may lead to smoother surfaces below 1 nm RMS.

Figure 4.2. RMS surface roughness of CdTe/MgCdTe DHs as a function of (a) substrate temperature  $T_s$  and (b) Cd/Te flux ratio.

# 4.2 Transmission electron microscopy of CdTe/MgCdTe DHs

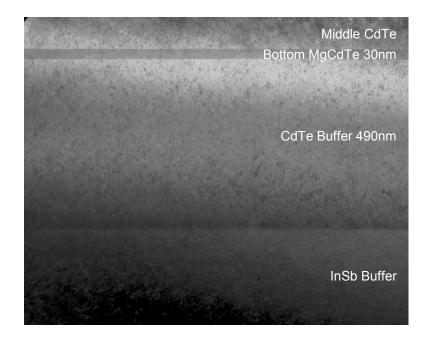

Transmission electron microscope (TEM) images of the CdTe/MgCdTe DH are taken in order to determine the crystalline quality and thicknesses of all the layers. Figure 4.3 shows a cross sectional TEM image of the lower region of the structure which indicates that all the interfaces are relatively free of defects. Furthermore, the measured thicknesses closely match the design thicknesses for the structure. It should be noted that the speckling of the image is likely due to TEM sample preparation, which is difficult because of the relative softness of both CdTe and InSb.

Figure 4.3. TEM image showing the lower portion of the CdTe/MgCdTe DH. \**Image acquired by Jing Lu and Dr. David Smith at ASU*.

## 4.3 X-ray diffraction measurements of CdTe/MgCdTe DHs on InSb

X-ray diffraction (XRD) is a versatile characterization method which is useful for measuring several properties of a structure, including layer composition, thicknesses, relaxation, and relative dislocation density. The setup consists of a monochromatic, collimated x-ray beam which is directed towards the sample at an angle  $\omega$  with respect to the wafer surface. X-rays penetrate into the surface up to several microns and diffract off of the atoms back towards the wafer surface, giving rise to intensity variations that can be detected as a function of  $\omega$ . The measurements used in this study are high resolution  $\omega$ -2 $\theta$ scans, where 2 $\theta$  is the angle between the x-ray beam and the detector within the plane of incidence. The measurement is high resolution because an x-ray analyzer is used, which limits the acceptance angle of the detector. The angles  $\omega$  and 2 $\theta$  are set equal to each other and scanned within a certain range where diffraction peaks occur. The diffraction is described by Bragg's law:

$$n\lambda = 2d\sin(\omega) \quad , \tag{4.1}$$