Asymmetric Multiprocessing Real Time Operating System on Multicore Platforms

by

Girish Rao Bulusu

# A Thesis Presented in Partial Fulfillment of the Requirement for the Degree Master of Science

Approved September 2014 by the Graduate Supervisory Committee:

Yann-Hang Lee, Chair Georgios Fainekos Carole-Jean Wu

ARIZONA STATE UNIVERSITY

December 2014

#### ABSTRACT

The need for multi-core architectural trends was realized in the desktop computing domain fairly long back. This trend is also beginning to be seen in the deeply embedded systems such as automotive and avionics industry owing to ever increasing demands in terms of sheer computational bandwidth, responsiveness, reliability and power consumption constraints. The adoption of such multi-core architectures in safety critical systems is often met with resistance owing to the overhead in migration of the existing stable code base to the new system setup, typically requiring extensive re-design. This also brings about the need for exhaustive testing and validation that goes hand in hand with such a migration, especially in safety critical real-time systems.

This project highlights the steps to develop an asymmetric multiprocessing variant of Micrium  $\mu$ C/OS-II real-time operating system suited for a multi-core system. This RTOS variant also supports multi-core synchronization, shared memory management and multi-core messaging queues.

Since such specialized embedded systems are usually developed by system designers focused more so on the functionality than on the coding standards, the adoption of automatic production code generation tools, such as SIMULINK's Embedded Coder, is increasingly becoming the industry norm. Such tools are capable of producing robust, industry compliant code with very little roll out time. This project documents the process of extending SIMULINK's automatic code generation tool for the AMP variant of  $\mu$ C/OS-II on Freescale's MPC5675K, dual-core Microcontroller Unit. This includes code generation from task based models and multi-rate models. Apart from this, it also describes the development of additional software tools to allow semantically consistent communication between task on the same kernel and those across the kernels. To all who supported me

# ACKNOWLEDGEMENTS

I am extremely grateful to my supervisors, Prof. Yann-Hang Lee, Prof. Fainekos and Prof. Wu for their continuing support and invaluable advice throughout. Also to my teammate Dhiraj Shetty.

|      |      |        | I                                                     | Page |

|------|------|--------|-------------------------------------------------------|------|

| LIST | OF T | ABLES  |                                                       | ix   |

| LIST | OF F | IGURE  | S                                                     | X    |

| CHA  | PTER | Ł      |                                                       |      |

| 1    | INT  | RODU   | ICTION                                                | 1    |

|      | 1.1  | Motiv  | ation                                                 | 1    |

|      |      | 1.1.1  | Need for Multicore in Embedded Systems                | 1    |

|      |      | 1.1.2  | Problems With Multi-Core Adoption in Embedded Systems | 2    |

|      |      | 1.1.3  | AMP-RTOS and SMP-RTOS on Multi-Core                   | 4    |

|      |      | 1.1.4  | Need for Automatic Code Generation                    | 8    |

|      | 1.2  | Contr  | ibution and Method                                    | 9    |

|      | 1.3  | Docur  | nent Outline                                          | 10   |

| 2    | BAC  | CKGRO  | UND                                                   | 11   |

|      | 2.1  | Multic | core Microcontroller Units                            | 11   |

|      |      | 2.1.1  | True Parallelism with Multicore                       | 12   |

|      | 2.2  | Power  | PC and E200Z7 Processor                               | 13   |

|      |      | 2.2.1  | Atomic Instructions                                   | 15   |

|      | 2.3  | Freesc | ale MPC5675K                                          | 18   |

|      |      | 2.3.1  | Lock Step Mode and Decoupled Parallel Mode            | 18   |

|      |      | 2.3.2  | Hardware Semaphore Peripheral                         | 19   |

|      | 2.4  | Real-T | Time Operating Systems and $\mu C/OS$ -II             | 20   |

|      |      | 2.4.1  | Real-Time Kernels and RTOS                            | 20   |

|      |      | 2.4.2  | Scheduler and Rate Monotonic Scheduling               | 22   |

|      |      | 2.4.3  | Lifetime of a $\mu$ C/OS-II Task                      | 23   |

|      |      | 2.4.4  | Priorities and Ready List                             | 24   |

# TABLE OF CONTENTS

|   |     | 2.4.5   | Time Management                                         | 25 |

|---|-----|---------|---------------------------------------------------------|----|

|   |     | 2.4.6   | Mutual Exclusion and Synchronization                    | 26 |

|   |     | 2.4.7   | Message Queues                                          | 28 |

|   |     | 2.4.8   | Memory Management                                       | 31 |

|   | 2.5 | Auton   | natic Code Generation and $\mu C/OS$ -II                | 33 |

|   |     | 2.5.1   | Model Based Design and Rapid Prototyping                | 33 |

|   |     | 2.5.2   | Code Generation Architecture and TLC Process            | 34 |

|   |     | 2.5.3   | Program Execution of Generated Code                     | 39 |

| 3 | LIT | ERATU   | JRE REVIEW AND RELATED WORKS                            | 45 |

|   | 3.1 | FreeR   | TOS and Multicore                                       | 45 |

|   | 3.2 | Multip  | processors Synchronization protocol                     | 47 |

|   | 3.3 | Seman   | tics Preserving Multi-Task Implementation               | 49 |

|   | 3.4 | Three-  | Slot Asynchronous Reader-Writer Mechanism for Multicore | 50 |

| 4 | PRC | OBLEM   | ANALYSIS AND REQUIREMENTS                               | 52 |

|   | 4.1 | Overv   | iew of Objectives                                       | 52 |

|   | 4.2 | Functi  | onal Requirements                                       | 53 |

|   |     | 4.2.1   | μC/OS-II System Level Requirements                      | 53 |

|   |     | 4.2.2   | µC/OS-II Additional Services Requirements               | 53 |

|   |     | 4.2.3   | Requirements of $\mu C/OS$ -II Support on SIMULINK      | 53 |

| 5 | DES | SIGN    |                                                         | 55 |

|   | 5.1 | μC/O    | S-II for MPC5675k in AMP mode                           | 56 |

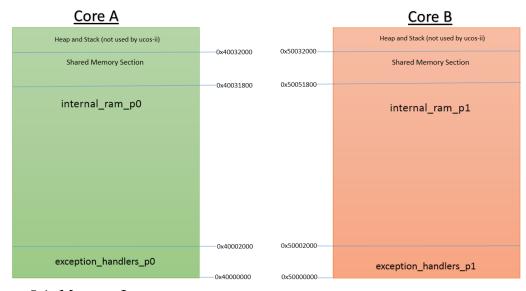

|   |     | 5.1.1   | Memory Layout                                           | 56 |

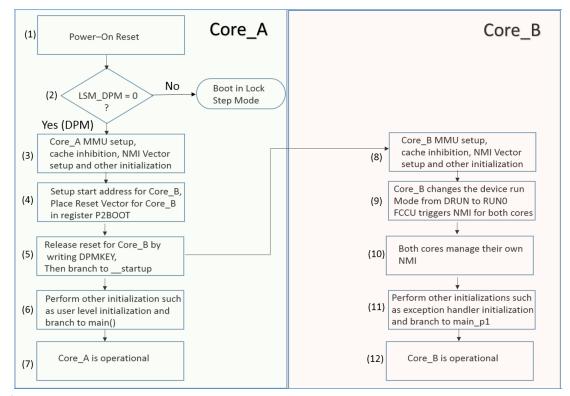

|   |     | 5.1.2   | Initialization and Bootstrapping                        | 59 |

|   | 5.2 | Inter-C | Core Communication                                      | 62 |

Page

| 5.3  | Mutua   | l Exclusion - Spinlocks                                    | 63  |

|------|---------|------------------------------------------------------------|-----|

|      | 5.3.1   | Mutual Exclusion using Semaphore Peripheral                | 63  |

|      | 5.3.2   | Mutual Exclusion using Atomic CAS                          | 64  |

| 5.4  | Inter-C | Core Barriers                                              | 65  |

|      | 5.4.1   | Barriers using Semaphore Peripheral                        | 65  |

| 5.5  | μC/O    | S-II Global Counting Semaphores                            | 66  |

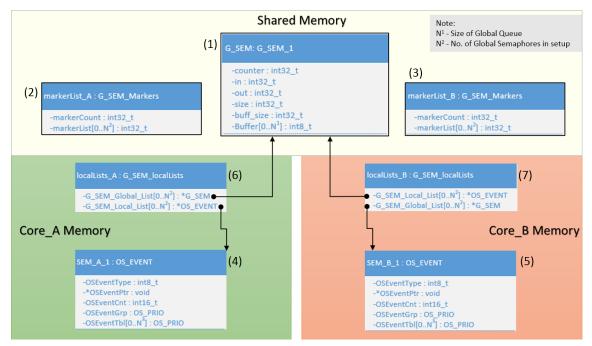

|      | 5.5.1   | Global Semaphore Data Structure Setup                      | 67  |

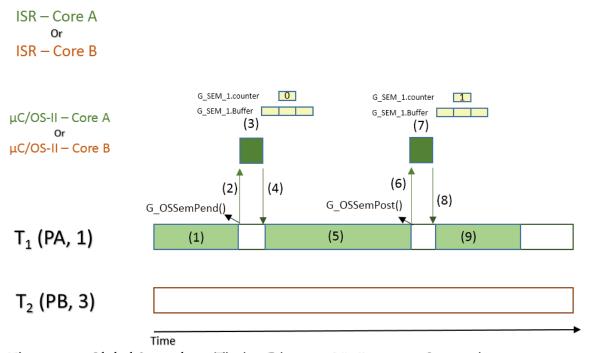

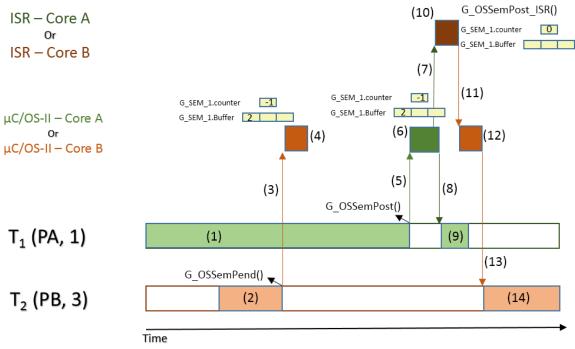

|      | 5.5.2   | Global Semaphore Algorithm                                 | 69  |

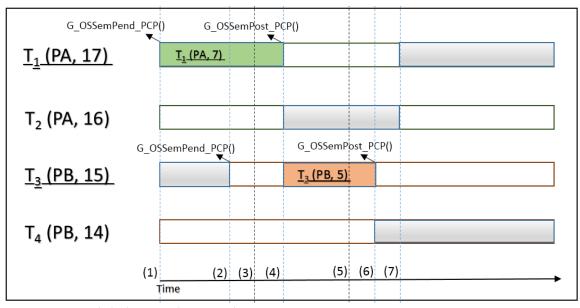

|      | 5.5.3   | Global Semaphore with PCP Algorithm                        | 76  |

| 5.6  | μC/O    | S-II Shared Memory Management                              | 78  |

|      | 5.6.1   | Shared Memory Management Data Structure and Initial Setup. | 79  |

|      | 5.6.2   | Shared Memory Management Algorithm                         | 80  |

| 5.7  | μC/O    | S-II Shared Memory Queues                                  | 82  |

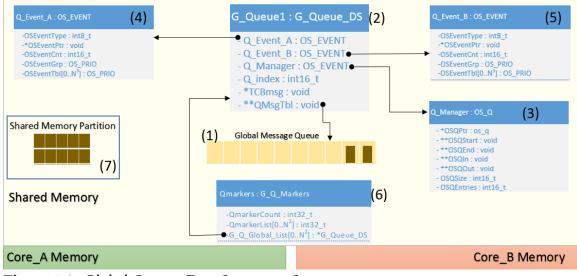

|      | 5.7.1   | Shared Memory Queues Data Structure Setup                  | 84  |

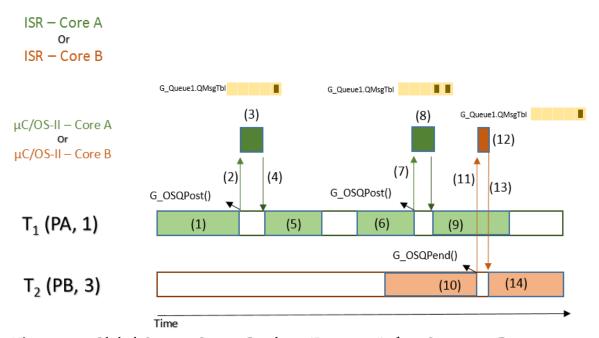

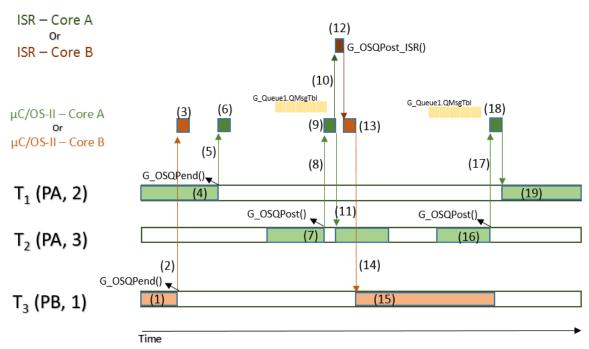

|      | 5.7.2   | Shared Memory Queues Algorithm                             | 87  |

| 5.8  | Task N  | Aodel for $\mu C/OS$ -II on Simulink embedded coder        | 96  |

| 5.9  | Multir  | rate Model for $\mu$ C/OS-II on Simulink Embedded Coder    | 98  |

|      | 5.9.1   | Initial Setup for Multi-rate Code Generation               | 99  |

|      | 5.9.2   | Multi-rate Process Execution Algorithm                     | 100 |

| 5.10 | Dynar   | nic Buffering Protocol-Single Core RT SIMULINK Block       | 102 |

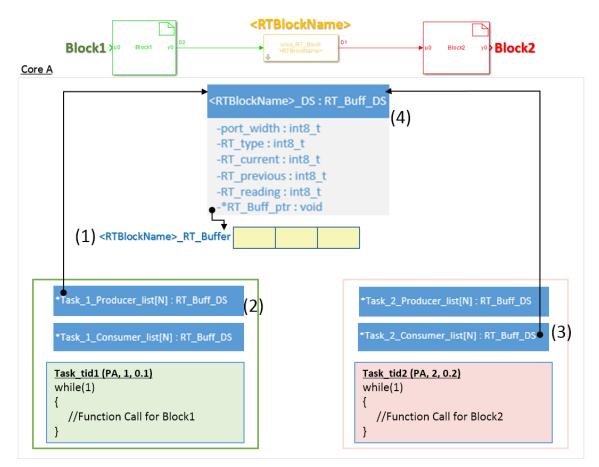

|      | 5.10.1  | Data Structures Required                                   | 104 |

|      | 5.10.2  | Intra-core Communication Protocol Algorithm                | 106 |

| 5.11 | Multic  | core Rate Transition SIMULINK Block                        | 111 |

|      | 5.11.1  | Initial Setup and Data Structures Required                 | 113 |

Page

|   |     | 5.11.2  | Inter-Core Communication Protocol Algorithm 115                 |

|---|-----|---------|-----------------------------------------------------------------|

| 6 | IMP | LEME    | NTATION 119                                                     |

|   | 6.1 | Portin  | g µC/OS-II for MPC5675K in AMP Mode 119                         |

|   |     | 6.1.1   | Project Directory Structure                                     |

|   |     | 6.1.2   | Porting steps in µC/OS-II/BSP 126                               |

|   |     | 6.1.3   | Porting Steps for Hardware Specific and Startup Code 130        |

|   | 6.2 | Codew   | varrior Setup and Debugging Tools                               |

|   |     | 6.2.1   | Codewarrior Setup for AMP Variant Of $\mu$ C/OS-II 132          |

|   |     | 6.2.2   | Importing and Compiling the Code 133                            |

|   |     | 6.2.3   | Setting Core B Entry Point 134                                  |

|   |     | 6.2.4   | Debugging the Code 135                                          |

| 7 | EVA | LUATI   | ON                                                              |

|   | 7.1 | High I  | Level Testing Strategy                                          |

|   | 7.2 | Testing | g the $\mu C/OS\text{-II}$ porting for Core_A and Core_B 137    |

|   |     | 7.2.1   | Verify $\mu$ C/OS-II Porting: OSTaskStkInit() and OSStartHigh-  |

|   |     |         | Rdy() 137                                                       |

|   |     | 7.2.2   | Verify µC/OS-II Porting: OSCtxSw()                              |

|   |     | 7.2.3   | Verify $\mu$ C/OS-II Porting: OSIntCtxSw() and OSTickISR() 141  |

|   |     | 7.2.4   | Performance Improvement with Respect To Single Core 143         |

|   | 7.3 | Testing | g Mutual Exclusion Primitives 146                               |

|   |     | 7.3.1   | Testing Mutual Exclusion Functionality Based on Atomic CAS 147  |

|   |     | 7.3.2   | Testing Mutual Exclusion Functionality - Hardware Semaphore 149 |

|   |     | 7.3.3   | Comparison of Spin Locks-Atomic CAS and HWSEMA4 150             |

| 8 | CO  | NCLUS   | ION and FUTURE WORK 152                                         |

# LIST OF TABLES

| Table | Page                                                          |

|-------|---------------------------------------------------------------|

| 6.1   | Folder Structure: Application Specific Code 120               |

| 6.2   | Folder Structure: $\mu$ C/OS-II and $\mu$ C/CPU Configuration |

| 6.3   | Folder Structure:µC/OS-II Source Code                         |

| 6.4   | Folder Structure:µC/LIB Libraries 123                         |

| 6.5   | Folder Structure:Processor Specific Code 124                  |

| 6.6   | Folder Structure:Board Support Package 124                    |

| 6.7   | Folder Structure:Hardware Specific and Startup Code 125       |

| 6.8   | Folder Structure:Global Functions 125                         |

| 7.1   | Performance Measurement of Test Case(a)                       |

| 7.2   | Performance Measurement of Test Case(b) and Test Case(d) 146  |

| 7.3   | Performance Measurement of Test Case(d) 146                   |

| 7.4   | Performance Comparison of Spin-locks 150                      |

# LIST OF FIGURES

| Figure |                                                                       | Page |

|--------|-----------------------------------------------------------------------|------|

| 2.1    | Atomic Compare and Swap Function                                      | 17   |

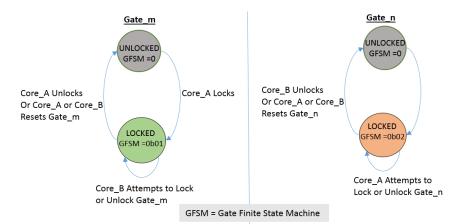

| 2.2    | Hardware Semaphore Gate Finite State Machine                          | 20   |

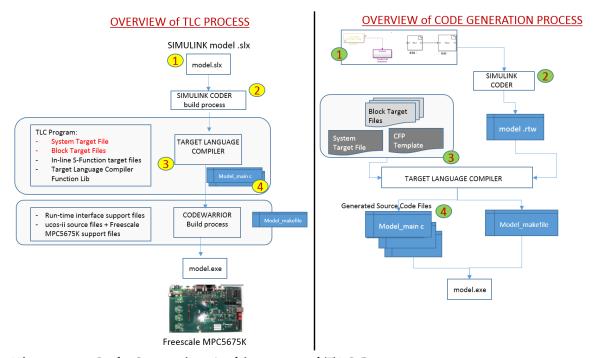

| 2.3    | Code Generation Architecture and TLC Process                          | 35   |

| 2.4    | Single Rate Program Execution                                         | 40   |

| 2.5    | Multi-Rate Program Execution                                          | 42   |

| 2.6    | Tornado- rtwdemo_mrmtos_main Task                                     | 43   |

| 2.7    | Tornado tBaseRate- Base Rate Function                                 | 44   |

| 5.1    | Memory Layout                                                         | 57   |

| 5.2    | Boot Sequence                                                         | 60   |

| 5.3    | Spinlocks using Hardware Semaphore Peripherals                        | 64   |

| 5.4    | Global Semaphore Data Structures Setup                                | 67   |

| 5.5    | Global Semaphore Timing Diagram: No Resource Contention               | 71   |

| 5.6    | Global Semaphore Timing Diagram: With Resource Contention             | 73   |

| 5.7    | Global Semaphore with PCP Timing Diagram                              | 77   |

| 5.8    | Global Queues Data Structures Setup                                   | 84   |

| 5.9    | Global Queues Case 1: Producer Enqueues Before Consumer Dequeues      | 89   |

| 5.10   | Global Queues Case 2: Consumer Tasks Pend Before Producer Enqueues .  | 91   |

| 5.11   | μC/OS-II Task - SIMULINK Block                                        | 98   |

| 5.12   | $\mu C/OS$ -II Multi-Rate Model Initialization $\ldots$               | 102  |

| 5.13   | DBP based SIMULINK RT Block- Data Structures Required                 | 104  |

| 5.14   | DBP Based Rate Transition Block: Model Initilzation                   | 108  |

| 5.15   | DBP Based Rate Transition Block: Timer Callback Function              | 109  |

| 5.16   | DBP Based Rate Transition_Block: Reader Writer Functions              | 110  |

| 5.17   | 3-ACM Global Rate Transition_Block: Model Setup and Data Structures . | 114  |

# Figure

| 5.18 | 3-ACM Global Rate Transition_Block: Writer side algorithm | 117 |

|------|-----------------------------------------------------------|-----|

| 5.19 | 3-SAM Global Rate Transition_Block: Reader side algorithm | 118 |

| 7.1  | Initialization of Task Stack: CPU Registers               | 139 |

| 7.2  | AMP vs Single Core Performance: Test Setup (a) and (b)    | 144 |

| 7.3  | AMP vs Single Core Performance: Test Setup (c) and (d)    | 145 |

| 7.4  | Test Setup: Spin-lock using Atomic CAS                    | 147 |

# Chapter 1

#### INTRODUCTION

The central idea behind this project revolves around the use of  $\mu$ C/OS-II, a real-time operating systems (RTOS), in an Asymmetric Multiprocessing (AMP) mode of operation on a multi-core system. The hardware used in this project is the Freescale Qorivva MPC5675K, Power Architecture 32-bit Micro-controller Units (MCU). The choice of hardware and the operating system is representative of a typical industry setup seen especially in the automotive domain. However, the concepts explored within the scope of this project can be easily extended to any other configuration. This project serves to document the process of porting an existing uni-processor real-time operating system to an AMP mode of operation along with support for multi-core synchronization and message passing capabilities. The project also describes the process of extending SIMULINK's Embedded Coder to support this above mentioned configuration. Such an automatic code generation framework would serve as the starting point for a more customized code generation frameworks based on the applications intended to be designed and developed.

# 1.1 Motivation

### 1.1.1 Need for Multicore in Embedded Systems

Traditionally, the prevalent trend within the semiconductor industry in the design of processors revolved around the shrinking of the die size and increasing the operating frequency. However in the earlier years of computing, particularly in the 1970s, the physical limitation that uni-processor systems inherently possessed was realized. This notion became more concrete in the 1980s because of which a number of parallel computing machines were built for commercial purposes. Many prominent researcher such as Stone and Cocke proposed that 250 MHz would be the highest operating frequency attainable on a uni-processor system [44] and any further increase would be constrained by physical factors. However, this upper-limit on the CPU clock rate was soon disproved and the market focus again shifted back to the ramp up of the uni-processor system's clock rates. As the demand for high performance computing began to emerge in the embedded systems domain, such as sophisticated signal processing, the need for higher MIPS performance was seen. This increase in complexity of systems drove the operating frequency of micro-processors till it began to peak at several billion operations per second, well within the giga-hertz operating range.

The sheer increase in operating frequency led to increased computational bandwidth in terms of instruction executed per second, however the negative effects of pushing the limits could no longer be ignored. The most critical problem being that of heat dissipation. Also, there was an inherent upper limit to this approach as most chip designers had hit an architectural wall in terms of designing sophisticated pipelining techniques. These techniques had reached a point where any further optimization in terms of pipelining for the best case scenario would only result in much greater degradation in performance during worst case execution [23]. Keeping in mind the above mentioned thermal, architectural, physical and systemic software issues, the need to transition to multi-processor systems seemed as the next logical step.

#### 1.1.2 Problems With Multi-Core Adoption in Embedded Systems

On narrowing the discussion to deeply embedded systems such as Automotive Embedded Systems, there are many more factors which influence the move from single core to multi-core systems. According to a study performed by VDC [19] the adoption of multiprocessor in the communications processors market was almost 3 times more likely than in the automotive domain. The study highlighted that the main cause for this slow adoption was the software rework required to migrate the legacy code from the uni-processor to multi-processor systems. This migration, especially in safety critical systems, is met with great resistance owing to the need for extensive and thorough re-testing and validation. Another cause to this slow adoption was the nature of the applications and the inherent sequential nature of C/C++ programs, which is the most prevalent language for such domains. Parallel programming considerations proved to be major paradigm shift for most experienced developers who were accustomed to sequential programming.

Despite the issues mentioned above, the 2 main reasons tipping the scales in the favor of adoption of mulit-processor systems in the deeply embedded domain are the economic and technical reasons [47]. Taking the example of the automotive industry, on an average, today's vehicles incorporate up to 70 ECUs with a sum total of about 20 million lines of code running across these ECUs. This steady increase in the number of ECUs and the effort spent in the software development for these ECUs in a car is estimated to account for almost 40% of the automobile's production cost [18]. Such an approach is at a watershed owing to limited composability, increased communication delays and decreasing probability of fault isolation and error containment [24].

The move to multi-core SoCs that communicate via some form message passing or shared memory schemes eliminates the need for multiple ECUs. Such a consolidation helps in minimizing communication delays between the ECUs, driving down production costs and facilitates precise fault and error detection. Also, such a multi-core setup can be used to provide more robust fault tolerance mechanisms by utilizing multi-core SoCs for error detection and to maintain high availability in the event of a failure of one of the processors. However, the issue of increasing complexity of software design and development in such a multi-processor setup still needs to be addressed. The study of some of these software issues was an area of focus during the course of this project.

#### 1.1.3 AMP-RTOS and SMP-RTOS on Multi-Core

A real-time system, in its most general form, can be defined as a computer systems that is required to adhere to some bounded response time constraints in a deterministic manner. On failing to do so, it can run the risk of causing some catastrophic system failures [27]. This definition of real-time systems brings into focus three key aspects, namely, temporal correctness, deterministic behavior and the severity of system failure associated if these criteria are not met. The ability of a system to cope with certain temporal and behavioral failures enables one to categorize these systems as "hard", "firm" and "soft" real time systems. These terms are defined in detail in the following sections.

The common underlying thread to all these categories of real-time systems is the adherence to some form of temporal behavioral in a deterministic manner. Having said that, an over-simplified argument would be that greater the computational capacity of the system, less likely would be the occurrence of missed deadlines and an increase in responsiveness.

However, with multi-core real time system, designers would have a major challenge in terms of determining the worst case execution times in such an environment. The system could essentially lose its determinism and reliability. Hence the most important thing that can be made available to such systems designers is an easy to use application development environment. A Real Time Operating System (RTOS) can provide some degree of abstraction to the designers hence reducing the development effort of a realtime system.

A Real Time Operating System (RTOS) acts like the management system between the application and the hardware resources. Most of the hardware related design time considerations can be abstracted from the application designers in this manner. The RTOS would also provide the capability to schedule the real-time tasks hence allowing the resource requests by tasks to be serviced in a timely manner. The APIs exposed by the RTOS would allow application designers to focus on the functionality and their use in designing more complex system, rather than being concerned about the underlying implementation details of these services.

The two broad classification amongst RTOS are Uni-Processor RTOS (UP-RTOS), and Multi-Processor RTOS (MP-RTOS). MP-RTOS can further be classified as Symmetric Multi-Processor RTOS (SMP-RTOS) and Asymmetric Multi-Processor RTOS (AMP-RTOS).

#### SMP RTOS and Global Scheduling

In a SMP-RTOS setup all the underlying processors share a common memory and one instance of the thread safe operating system code. An SMP-RTOS typically has a global queue containing all tasks and at any one point of time 'm' highest priority tasks would be dynamically scheduled on the 'm' available processors. Following is a listing of some of the advantages and disadvantages to global scheduling schemes typically seen in SMP-RTOS. Based on the inherent disadvantages of an SMP-RTOS setup with global scheduling, the decision to adopt an AMP-RTOS setup with partitioned scheduling was seemed obvious.

## Advantages:

- 1. SMP-RTOS with global scheduling are best suited in a memory constrained systems since only one instance of the RTOS is needed in memory [8].

- Programming software for an SMP-RTOS with synchronization routines, such as spin-locks, mutexes and semaphores, becomes easier since only one set of these synchronization routines would be used to manage the tasks on the multicore system [8].

- 3. Extensive study done in the area of queuing theory [22] has shown that tasks scheduled using a single global FIFO queue of tasks on a multi-processor setup exhibit better average response times. Since there exists a single ready queue maintained by one kernel, all ready to run tasks would be scheduled to execute on the available processors and if needed tasks can be migrated from one core to another. This allows for better CPU utilization and load balancing between the processors [7].

- 4. In a multi-core setup with m processors, if more than m tasks have individual task utilization greater than 0.5, it is empirically seen that global scheduling policies offer better overall utilization as compared to portioned scheduling schemes [2].

- 5. Other scheduling schemes such as the PFAIR scheduling proposed by Baruah, Cohen, Plaxton and Varvel [3] have been proven to be optimal for scheduling periodic tasks on a multiprocessor setup. These scheduling protocols have has a linear-time complexity to perform the necessary and sufficient schedulability test. However since the PFAIR scheduling algorithm relies upon the breaking up of tasks into subtasks of smaller time slices it consequently leads to high implementation overhead [2].

#### Disadvantages

Since there is a single FIFO queue to schedule the tasks, synchronization overheads are considerably higher when scheduling tasks concurrently for multiple processors. Repeated kernel level locks to make the shared operating system code reentrant can hit the execution time bounds of the tasks adversely, leading to high worst case latencies [2].

- 2. Since task migration is essential in a dynamic scheduling scheme, inter-processor interrupts and cache reloading that is required for such a task migration can prove to be expensive when resuming a task on different processor [2].

- 3. There are no known necessary and sufficient schedulability tests available for global fixed priority scheduling which can be performed in less than exponential time [2]. Some test sets, which even though have only close to 1 total utilization demand, cannot be scheduled using the global EDF or global RM policies on an multi-core system (here utilization demand is lower than the number of processors). Such tasks sets typically contain a mix of both high and low utilization tasks present together. This phenomena is called the Dhall's effect [?, p. 281sha2006embedded]

# AMP RTOS and Partitioned Scheduling

In way of comparison, each processor executes a distinct instance of the RTOS on an AMP-RTOS setup. In an AMP setup typically a partitioned scheduling scheme is followed where each task may only execute on a fixed processor and separate dispatch queues for each processor.

#### Advantages:

- 1. Most techniques for single-processor scheduling are also applicable here especially if the task sets are completely independent [2].

- 2. There is wide body of work which proves that partitioning-based scheduling algorithms on multi-core systems offers better real-time performance, especially with respect to hard real-time systems, as compared to global scheduling algorithms [48].

- 3. Facilitates integration of legacy code written for 2 or more independent UP-RTOSs into an AMP-RTOS without considerable re-design.

#### Disadvantages:

- 1. Such a duplication of the RTOS code leads to a greater memory footprint [7].

- 2. Synchronization routines becomes difficult to implement due independent RTOS code and partitioned queues

- 3. Such an analysis to split up tasks for each of the dispatch queues, translates to a greater design time over-head [45]. This analysis required to find an optimal distribution of tasks across the cores falls in the class of bin-packaging problems is known to be a NP-hard problem and cannot be performed in polynomial time [38]. However some heuristics based algorithms such as the Rate Monotonic First Fit (RMFF) proposed by Dhall and Liu offer close to optimal solutions [21].

Despite the above mentioned disadvantages, the inherent advantages to AMP-RTOS and the disadvantages of SMP-RTOS have made AMP-RTOS the choice of setup for this project.

# 1.1.4 Need for Automatic Code Generation

Taking the case of embedded systems design and development, where often crossfunctional designers from the mechanical, electrical and software domains work in collaboration, the ability to understand the details of each of these domains can prove to be challenging.

With this in mind it has become the need of the day to increase the abstraction level of the projects and provide faster code production techniques which is also compliant with industry standards. With the help of tools allowing Model Based Design and Automatic Production Code Generation, consistent co-design of components is possible starting all the way from the design phase to the code production phase [35]. Also, model-based designs can facilitate code-reuse and allow greater testing coverage. These factors are vital in driving down the cost of such complex embedded systems.

With the help of tools like SIMULINK's Embedded Coder the process of system design and production code generation can become a seamless process allowing easy integration of components at any phase - from requirements gathering to the final product integration phase. This thesis project includes the setup, and some of the additional functionalities, added to the Embedded Coder framework to allow easy development of applications on the Freescale MPC5675K running  $\mu$ C/OS-II in AMP mode.

# 1.2 Contribution and Method

This thesis document presents the study done in taking some of the design decisions over the course of the project. Some of these decisions were driven owing to the advantages and optimality they offered and some chosen owing to their ease of implementation which might not be the most optimal solutions. However with this framework in place, it would not require considerable change to implement other more optimal solutions, as suited by the need of the application.

Unlike the commonly followed scheme of requirement gathering, wherein within the first few iterations of the development cycle all of the requirements are identified, in this project the requirements were captured in an evolutionary and adaptive fashion. Starting with the core requirements, which was the need to support a real-time operating system on the provided multi-core hardware and to support code generation for  $\mu$ C/OS-II, other requirements were added to the pool over every development iteration. Further requirements were mostly identified keeping in mind the typical issues a system designer or application developer, using such a framework, would face over the course of a similar project. The finalized set of requirements presented within this body of work should be

the base functional requirements upon which more specific functional and non-functional requirements can be added.

# 1.3 Document Outline

The rest of the document is organized as follows. Chapter 2 provides Background information about  $\mu$ C/OS-II, its architecture.It also explains the code generation process for single rate and multi-rate system using SIMULINK.

Chapter 3 mentions the related work done in the area of AMP RTOS setups, dynamic buffering protocol and the three-slot asynchronous data sharing semantics.

Chapter 4 provides a list of the formalized requirements of this thesis project.

Chapter 5 talks about the design of the additional  $\mu$ C/OS-II related capabilities that have been added in this project. It also provides details of the multi-rate code generation support for  $\mu$ C/OS-II from SIMULINK models and the semantic preserving data sharing protocols implemented as blocks within SIMULINK.

Chapter 6 describes the implementation details of the porting process of  $\mu$ C/OS-II on the MPC5675K MCU.

Chapter 7 gives the summary of the test cases that have been employed in the testing of various aspects of the project.

Chapter 8 gives as a concluding note, some of the advantages of this setup and also future work that would be done in continuation to this project.

### Chapter 2

#### BACKGROUND

This section of the document provides some definitions and brief description about some of the concepts upon which further work has been done over the course of the project. For a reader familiar with concepts based on  $\mu$ C/OS-II, the configuration of the MPC5675K automotive dual-core MCU, atomic instructions provided by PowerPC architecture, SIMULINK automatic code generation for multi-rate models and its existing buffering techniques, this section can be skipped.

### 2.1 Multicore Microcontroller Units

A processor core is the computing unit within the integrated circuit, also known as the central processing unit, responsible for fetching and executing instructions to perform a specific function. These instructions are a part of the instruction set architecture of the processor which allows the programmer or compiler designers to interact with the processor to implement a functionality to be performed by the processor.

Before any further discussion is undertaken it is important to make a critical distinction between microprocessors and microcontrollers. A microcontroller or a Microcontroller Unit (MCU) is a complete computing system which consists of a processor, memory and other peripherals. Microcontrollers are used for embedded systems applications. Since embedded system typically have a defined fixed relationship between the outputs to given inputs to the system and they do not serve a general purpose computing role the need for extensive resources is eliminated. Owing to these factors the micro-controllers often operate in a much lower frequency domain, of the order of a couple of hundred megahertz (like 0-180 MHZ for the e200z7d processors on the MPC5675K). Microprocessors on the other hand consists of only the CPU or the core, and the other components such as RAM, ROM have to be incorporated by the designers externally as a part of SoC to make it a functional unit. Microprocessors usually are used in general purpose computing domain which demands higher RAM, ROM and I/O resources. The clock speeds seen on the microprocessors often run in the gigahertz range. The choice of using microcontrollers in embedded systems is driven primarily by cost considerations and low-power constraints. However these days with the increase in complexity of embedded systems, microprocessors SoCs are often being used in embedded systems. This is particularly seen in the mobile computing domain.

The next distinction to be considered is that of a multi-processors and multi-core processors. Though often used interchangeably, a multi-core processors is a setup where two or more cores are integrated onto a single integrated circuit die instead of having two or more independent processors on the motherboard interfaced using multiple sockets. There are several advantages of a multi-core setup, which has made this architecture design the de-facto standard within the industry. The proximity of the cores greatly decreases the cache coherency latency allowing them to run at a much higher rate. Also the die area required on the printed circuit board is also greatly reduced as opposed to that taken up by a multi-chip design. The proximity of the cores also ensures that the power required to drive the off-chip signals are reduced, leading to greater to power saving [5].

# 2.1.1 True Parallelism with Multicore

In a dual-core processor or MCU, like the one present within the MPC5675K board used in the project, there are two independent cores present. With this true parallelism can be achieved rather than just an illusion of parallelism which is provided by multithreaded programs on a single core system. To explain this further consider single core setup running 2 tasks of dual priority. In a single core system the execution of these tasks would be interleaved, wherein a context switch between the tasks could be triggered every fixed quanta of time. Thus it is easy to conclude that each task gets at the most 50 per-cent of the processor time. Here we can for the time being ignore the context switch overhead which would also eat up on the CPU utilization. Now on scaling up the number of task to say 100, each task gets only about 1per-cent of the CPU time. On a fast enough processor it would still seem as though tasks are executing parallel however there would be clear reduction in the responsiveness of the system. On the other hand going back to the 2 task setup but this time on a dual core system. It is possible to schedule each of the tasks on each of the cores wherein almost 100 % of each of the cores utilization is towards the execution of each of the tasks. Here parallelism in its true sense is seen. With the help of a scheduling policy, such as EDF scheduling, it is possible to run 100 tasks on the 2 cores, where a simplistic division of tasks would be to allocate 50 tasks to each of the cores. In such a scenario, each task gets 2 % of the CPU time as compared to 1 %, thereby increasing the responsiveness of the system by almost a factor of 2.

However, multi-core systems bring about the need of synchronization and other such design considerations owing to true simultaneity. This can make the design of application more complicated and also such synchronization requirements to protect shared resources often prove to be computationally expensive.

# 2.2 PowerPC and E200Z7 Processor

A collaboration between Apple, IBM and Motorola on a common RISC architecture to create a new architecture aimed at the high performance, low cost computers led to the creation of the PowerPC architecture [11]. It was based on IBM's existing Power architecture, which underwent a number of significant changes to improve performance such as increase in clock rates, a simplified instruction set, and a higher degree of superscalar execution, 64-bit support and multiprocessor support. This improved form of the POWER architecture was branded as PowerPC (POWER Performance Computing) [11].

There are a number of distinguishing factors between PowerPC and other popular architectures because of which it has become one of the most pervasive architecture in the embedded systems domain such as avionics, automobile, telecommunication etc. Before we discuss the key features of PowerPC and in specific the e200 series of micro-processors it is important to loosely define the terms architecture and micro-architecture. An architecture or Instruction Set Architecture (ISA) is a specification of the functionality that a microprocessor has to provide. From a purely architecture point of view the implementation of these functionalities in hardware hold very little importance to the programmer or the compiler designer. However with varying demands the hardware implementation of the micro-architectures would also vary. These hardware variations such as the depth of the pipeline, superscalar design, branch prediction are a part of the micro-architecture.

Some of the key distinguishing features that makes PowerPC still a favorite within the industry is the broad range of microprocessor families it has to offer and the use of a common instruction set architecture (Power ISA) which covers this gamut of microprocessor families [4].

PowerPC architecture also allows great flexibility in terms of the number of I/O peripherals that can be interfaced, this makes these implementations highly scalable. PowerPC also does not rigidly define the implementation of the standard peripherals, such as the debug controller or the interrupt controller units, which provides the vendor a great deal of flexibility in their implementation. Compared to this the ARM architecture imposes a strong integration in the design of such units. This would no doubt improve performance owing to the strongly coupled design but at the expense of versatility and diversity in hardware solutions. Finally and probably one of key advantages are that PowerPC based microprocessors and MCUs owing to their simplicity and compact design make it more reliable. This allows them to operate under a greater range of temperatures. For example the operating temperatures for the e200 series microprocessor within the MPC5675K board ranges from -40 to 120 degrees Celsius making it ideal for automotive and high temperature industrial applications [16].

The e200 family of processor and more specifically the e200z7 variant of this processor used within the MPC5675K was designed to be simpler compared to the other higher performance PowerPC processors and suited for a real-time environments [12]. An example of this simple design is the in-order execution and retirement of instructions. The core proves to be highly cost effective as it is highly customizable.

Some of the features worth mentioning as they are relevant in this project. Each core is a dual issue 32-bit processor with an independent instruction and data buses. The 64bit path to cache supports fetching of two 32-bit instruction per clock. It also has dedicated program counter incrementers supporting pre-fetching of instructions. The load and store units support both unit and multiple word with a latency of 3 cycles for a load latency. Each core individually supports interrupts and exception handling with extensive vectored interrupt and nested interrupt capability [17, p. 136].

# 2.2.1 Atomic Instructions

From this projects point of view the need for atomic instruction is vital for the synchronization of the two cores when running in AMP mode. Based on these basic instructions a shared memory access (both read and write) can be made atomic. With this it is possible to implement busy-waiting mutual exclusion routines. With these mutual exclusion routines across cores, more sophisticated synchronization solutions between the two kernels such as the blocking counting semaphore and shared memory blocking queues, can be implemented.

Spin-lock implementations of locks across cores described in the upcoming section relies on shared memory. A pre-determined location in shared memory is used to hold a flag value indicating that the critical section has been entered or is free for access to the requesting process.

lwarx (Load Word and Reserved Instruction) and stwcx (Store Word Conditional Indexed) instructions work in conjunction. lwarx instruction loads the word held at the effective address (shared memory) location into the required register and places a reservation on this memory location [14, p. 80]. During the execution of stwcx instruction, it is checked if the reservation held by lwarx on the memory location has not been corrupted by another access [14, p. 137]. If it has not been corrupted, then the stwcx instruction stores the value held in a register into the effective address pointing to the shared memory, sets bit 0-2 of the cr0 (conditional register 0) to 0b001 and clears the reservation set by the lwarx instruction. However, if the reservation was corrupted by another access then the store to the effective address does not occur and the sets bit 0-2 of the cr0 to 0b000. Based on the value set into this conditional register it can be checked if the flag value set in the shared memory location was atomically accessed or not.

The isync instruction is also essential along with the use of the above mentioned instructions. This instruction prevents the execution of the instructions following the isync instruction till all the instruction issued prior to the isync instruction have completed execution and have taken effect. Following the isync instruction the instruction queue is flushed and the instructions are fetched again [13].

## Atomic Compare and Swap:

```

int Atomic_CAS(volatile int * p, int oldval, int newval)

1

2

{

3

__asm___volatile__ (

"0: lwarx %0, 0, %1

\n\t"

4

xor. %0, %3, %0

5

\n\t"

...

6

bne 1f

\n\t"

stwcx. %2, 0, %1 \n\t"

7

bne- Ob

8

\n\t"

\n\t"

9

isync

"1:

10

11

: "=&r"(fail)

: "r"(p), "r"(newval), "r"(oldval)

12

13

: "cr0");

14

return fail;

15 }

```

Figure 2.1: Atomic Compare and Swap Function

Atomic Compare and Swap (CAS) function with the help of atomic instructions have been used widely over the years and for the purpose of this project the following code snippet has been taken from [46]. Based on this function, a spin-lock implementation has been incorporated into the project.

Here in this code-snippet first at (Fig 2.1, 4), the contents of the memory address calculated by adding address offset 0 to %1 (parameter 1 i.e. \*p) into %0 (here 0% represents "fail"). Apart from doing this, a reservation is also done for the memory location now currently held by 0% (0 + %1).

Next, the contents of the 0% are compared to "ldval" (Fig 2.1, 5). If the contents are equal, then the code continues to run without any branch. But if the values are not equal then it branches forward to the label "1:" at line (Fig 2.1, 10) and continues to return back from the function with the fail value set as 1.

At (Fig 2.1, 7), it then checks that the reservation made for the memory location still holds or not. If it is successful then no other access to the memory have been done and continues to write the newval back to the memory address (0 + %1) and releases the

reservation and finally returns back from the function with "fail" set as 0. However if the reservation fails then it branches back to the label "0:" and retries the entire operation.

As explained above the isync instruction at (Fig 2.1, 9) ensure that all instruction such as the memory reservation, the checks performed and the release of the reservation is completed before the function return back.

#### 2.3 Freescale MPC5675K

The MPC5675K microcontroller is ideal for application that adhere to the Safety Integrity Level 3 with the help of providing a great level of on-chip redundancy [17, p. 33]. Some of these critical systems include redundant CPU cores, Interrupt Controllers, DMA controller, crossbar bus systems, memory protection unit, peripheral bus bridge, system timers and the watchdog timers. Apart from this peripherals such as FLEXCAN and LIN-CAN are also redundant. This redundancy can greatly reduce the software complexity, especially in an AMP setup, by statically allocating peripheral usage to each kernel.

#### 2.3.1 Lock Step Mode and Decoupled Parallel Mode

The MPC5675K MCU can be booted up by in two modes of operations, namely Lock Step Mode (LSM) and Decoupled Parallel Mode (DPM). This selection needs to be done statically at system startup.

In the LSM mode of operation is well suited for applications requiring high levels of fault tolerance through redundancy. When the MCU runs in LSM, both cores run synchronously also known as in lock-step and execute the same commands. Here each pair of the memory mapped peripherals share the same address. As mentioned before this MCU offers a great deal of redundancy, and in the LSM mode each redundant subsystem executes the same operations as the other. Following the execution of the same commands, a set of dedicated Redundancy Control Checker Units (RCCU) detect failures by making sure the outputs to the SRAM, flash or external buses are consistent.

Decoupled Parallel Mode (DPM) of operation is meant for additional performance. In this mode, each CPU core and each connected channel run independently [40]. While in this mode, the RCCU is disabled and all of the peripherals are mapped to different address allowing individual control. Also, SRAM is relocated and split into half, and the single 512KB SRAM array is also split into two 256KB arrays. Along the same lines, the redundant Interrupt Controllers are mapped to different memory location, where each is dedicated to one of the cores. Another peripheral of significant use within this project, namely the Hardware Semaphore Module (SEMA4), also becomes available in DPM.

# 2.3.2 Hardware Semaphore Peripheral

As discussed earlier, the need for atomic instructions is crucial for providing any kind of mutual exclusion and synchronization between the cores and the use of the peripherals. Since the MPC5675K MCU has a dual core setup and also has the DPM more of operation, for the sake of making application development easier and providing atomicity a dedicated SEMA4 peripheral has been added to provide such atomicity. With such an implementation, the need for an architecture specific read-modify-write instructions is eliminated and the solution becomes architecture-neutral. [17, p. 1601] Each of the 16 gates provided within the SEMA4 unit are capable of holding 3 states representative of unlocked (0), locked by Core\_A (0b01) and locked by Core\_B (0b10). To illustrate the states of the gates, say Core\_A ( 2.2) sets the state of a Gate\_n as locked, then only when Core\_A writes zero or when either cores initiate and complete the entire reset sequence can this gate be unlocked [17, p. 1602].

When the gate is locked by a core, and then attempts to lock or unlock the gate by the other care take no effect as the buses are monitored to track source of access.

Figure 2.2: Hardware Semaphore Gate Finite State Machine

## 2.4 Real-Time Operating Systems and µC/OS-II

This section talks about some general real-time concepts and provides various features available on a typical RTOS and specific details of some of these concepts with respect to  $\mu$ C/OS-II.

# 2.4.1 Real-Time Kernels and RTOS

A real time kernel is software that manages the time and resources of a microprocessor, micro-controller or Digital Signal Processor [26, p. 17]. The management of resources can also be defined in terms of the management of the application tasks, and by adhering to some degree of the temporal reliability. The way to achieve this kind of temporal reliability is to ensure deterministic execution of the RTOS code and by minimizing the jitters or fluctuations in the execution of these tasks. Here a task is an application typically implemented as an infinite loop, which assumes that the CPU is completely available for its execution and is designed to achieve a per-determined functionality. Here such tasks and task level applications comprise of the background part of the real-time systems. On the other hand Interrupt Service Routines make up the interrupt level part of the real-time system also known as the foreground system. Another important characteristic of real-time systems is the deterministic functional behavior. This essentially means, the system should ensure that given the same inputs the response of the system should always be the same unless the system is designed to behave differently. It is important to note that different behavior owing to system design at different instances of time is still deterministic behavior. To make this clearer let us take an example of the Airbags deployment system in an automobile. In the detection of a crash by the sensors present on the chassis, these sensor values are provided to the system eventually leading to the deployment of the airbags. However at another instances of time such identical sensor inputs are again given to the system but the system does not deploy the airbags. This would make the system unpredictable and certainly make this system unsuited for hard real time systems.

Based on the degrees to which an RTOS can provide guarantees in their real-time characteristics categorizes them into the 3 categories. These categories are Hard, Soft and Firm Real-time systems.

A "hard" real time system shows the least degree of tolerance to failures and any failure to conform to the requirements leads to catastrophic system failure [27, p. 6]. "Soft" real time systems are ones where on missing some temporal constraints the system does not fail completely, but continues to run in a compromised or degraded state with respect to the ideal case where no such deadline misses were encountered [27, p. 6].

The middle grounds between the hard and soft real time system are classified as "Firm" real time systems. This is where the distinctions between the three tends to become blurry. The definition of a firm real time system would be a system where few missed deadlines can be tolerated by the system and would not lead to complete catastrophic failure. However missing more than a few deadlines can in-fact lead to a catastrophic failure. Here the problem arises in defining the value of few deadlines. It can be assumed to be a parameter defined by the nature of the application under consideration.

Real-time kernels is the software responsible for managing the tasks within a realtime system. The presence of more than one task, which typically is the case, makes this a multi-tasking environment. With the help of multi-tasking parallelism can be achieved making the system more responsive and maximizes CPU utilization. It also makes the system design modular instead of being monolithic making it easier for application programming.

Apart from managing the tasks and their scheduling it also responsible for managing inter-task communication and management of system resources. The services provided by the kernel come at the cost of overhead in execution time but are an indispensable part of any RTOS. This kernel, such as the one in Micrium's  $\mu$ C/OS-II, uses between 2% to 4% of the CPU time [26, p. 18].

### 2.4.2 Scheduler and Rate Monotonic Scheduling

The scheduler or also known as the Dispatcher is the component of the RTOS responsible for deciding which task, of all the available tasks, will run next. Like most real-time kernels even the  $\mu$ C/OS-II kernel is preemptive and priority based. Here each task is assigned a priority based solely on the criticality of the task or could be decided by other schemes such as Rate Monotonic Scheduling.

Rate Monotonic Scheduling (RMS) has been adopted within the scope of this project, more specifically in the work involving code generation for  $\mu$ C/OS-II using SIMULINK Automatic Code Generation. There are certain assumptions that need to be made with RMS which are:

- All tasks within the system have to be periodic.

- Tasks should synchronize with one another and data transfers should only occur with lock-free, semantics preserving techniques.

• The kernel should be preemptive and allocate the CPU for execution to the highest priority task available within the ready list.

With RMS scheduling as long as the CPU utilization is bounded by 0.693, for a task set containing numerous tasks, schedulablity can be achieved. Other non-critical tasks, presumably with lower priority, can also be executed to make the CPU utilization closer to 100%.

# 2.4.3 Lifetime of a µC/OS-II Task

Tasks as define earlier serve the purpose of performing some sort of functionality such as monitoring inputs, updating outputs, reading sensor data, react to external events, react in a time-define manner, interface with peripherals and communicate with other systems

For a Task to be set up in in  $\mu$ C/OS-II it requires a Task Control Block (TCB), a stack and a priority should be assigned [25]. Apart from this there other parameter that are required to be defined when calling the OSTaskCreate() function [25]. Once the task is created successfully it is placed onto the ready-list, which would be described in the upcoming sections.

Task stacks in  $\mu$ C/OS-II are defined in a static manner and it is preferred not to allocate stack memory to the task using C compilers malloc. The main reason for this being the problem of fragmentation of heap memory that arises with the use of malloc() [25].

Tasks in  $\mu$ C/OS-II can be in any one of the 5 following states: Dormant, Ready, Running, Waiting for Event, Interrupted [25].

Dormant state corresponds to the state when the task has been created and resides in memory but has not been made available to the kernel yet. Dormant state also applies to task which have been deleted. The task still remains in memory but it is just that the scheduler is unaware of its existence any more. Ready state corresponds to the state when it is ready to execute however owing to its priority being less it cannot preempt the low priority task.

Running State is held by only one task within a kernel and this task has control over the CPU. At this moment no other higher priority task would not be in the ready state giving the task the opportunity to run.

Waiting state or also called the blocked state is when the task is waiting for an Event to occur after which its state would be changed to ready. Events could be based on inter-task synchronization and communication services provided by the kernel, timer expiry etc. More about events would be discussed in the upcoming sections.

Finally the Interrupted state corresponds to when a task is interrupted and the CPU is currently processing the interrupt.

### 2.4.4 Priorities and Ready List

Each task within the  $\mu$ C/OS-II kernel is allocated a unique priority [25]. Ranging from 0 to OS\_LOWEST\_PRIO value set within the OS\_CFG.H. However the upper limit to priorities is 64. In this setup priority 0 is equivalent to the highest priority and 64 represents the lowest possible priority that can be set. An important point to note here is that, since only task can exist at each priority level, the priority values in themselves can be used as unique identifiers to the task.

In an effort to reduce the amount of RAM used to maintain the Ready-list a table like data structures is maintained to preserve the state of the tasks. Also to increase the speed of access of these data structure every time a scheduling point occurs an additional data structure is maintained called the OSRdyGrp.

Each row within the ready table represents groups of tasks. To place a task within the ready list first the group of the task is is set. This is done using the following:

OSRdyGrp |= OSMapTbl[prio >> 3];

This indicated that a task within the corresponding group is in the ready state. Next it is required that the specific bit within the OSRdyTbl is set, thus specifying the exact task that is ready. This is done using the following:

OSRdyTbl[prio >> 3] = OSMapTbl[prio & 0x07];

# 2.4.5 Time Management

Like for any Operating system, even in the case of a RTOS, the need for periodic timer interrupts is essential to provide services such as time delays and timer timeouts [25]. Especially in this implementation where we follow a RMS scheme in the SIMULINK related aspects of the project. The low level setup of the decrementer timer provided by the e200z7 processor would be discussed in the porting section, however once this setup is complete periodic timer interrupt is triggered by the hardware. But through the operating system we have greater control over the resolution of this timer. The resolution can be set to 10 to 1000 timer per second as typically seen in most RTOS. This value can be set by assigning the appropriate value to the OS\_CFG\_TICK\_RATE within os\_cfg\_app.h. It is not always advisable to keep the timer resolution to 1000 timer per second as it can lead to considerable overheads in the handling of these recurring interrupts.

Apart from the usual services such as delay OSTimeDly we need the periodic timer service for the implementation of a RMS scheme . Once these timers are enabled (by setting OS\_CFG\_TMR\_EN to 1) and the timers are created (using OSTmrCreate()), by providing the required periodicity and the call back function and initial offset the timers can be started (using OSTmrStart()). Once such a timer is created the operating parameters cannot be changed on the fly and requires that the timer be deleted and a new timer be created [26, p. 201].

The timers are maintained with the help of an internal timer task- OS\_TmrTask() which is spawned only when the timer are enabled [25]. The source for this timer task is

also the same interrupts used for he OS timer ticks. As shown in the figure below, every time a timer interrupt is fired, the Tick ISR is called which in turn signals the release of the Timer Task with the help of a dedicated semaphore. This timer task is responsible for updating the timer values, which were created, and to invoke the required call back functions of the timers have expired.

Here the timer call back functions are run within the context of the timer task, and if there are multiple timers then it is essential that sufficient stack space is allocated.

## 2.4.6 Mutual Exclusion and Synchronization

There are a number a number of way through which mutual exlcusion (critical section access) in  $\mu$ C/OS-II can be achieved between the tasks [25, p. 134].

• Disabling Interrupts: To access critical sections shared between tasks interrupts can be disabled (using

OS\_ENTER\_CRITICAL) before entering the critical section and then enabled again (using OS\_EXIT\_CRITICAL) after exiting the critical section. By disabling interrupts since the scheduler can no longer be invoked unless done so explicitly. This ensure that the critical section is protected from other tasks and interrupt service routines. However if the length of the critical sections is large this can severely downgrade the responsiveness of the system as it would not be able to service any interrupts during this period. Such an approach is suited for very small critical sections of code.

• Scheduler locking: A more moderate form of protecting critical sections is with the use of Scheduler locking (OSSchedLock()) before entering and Scheduler unlock after exiting (OSSchedUnLock()). By doing so task rescheduling is no longer possible while in the critical section giving complete CPU control to the currently running task. However interrupts are still enabled and would be serviced if triggered while in the critical section. This helps improve the responsiveness of the system.

• Semaphores, message queues and mailboxes: By protecting critical sections with semaphores it is possible that tasks can wait in the blocked or waiting state till the task which is currently holding the lock decides to leave it. Here it is possible for even ISR to be able to release locks. With the use of semaphores not only critical sections be protected but also complex synchronization between the tasks can be achieved. More details regarding Semaphores and Message Queues would be given in the coming sections as their understanding is important to better understand the work done in the project.

The concept of semaphores in the context of computing was invented by Dijkstra in 1965. Semaphores can be thought of conceptually as keys with which a resource access can be restricted. A semaphore could be configured to work as a binary or counting semaphores. The counter within the binary semaphores can either hold 0 or 1. In the counting semaphore with 32-bit counters, as is implemented in the  $\mu$ C/OS-II setup of the project [25], the counter can hold values up to 65535. Every time a task intends to acquire the semaphore it decrements the counter and continues on with its normal execution. However if the counter reaches a value 0, the task can no longer continue and goes into waiting state.

When the task releases a semaphore it increments the counter. If there are tasks currently waiting on the semaphore then the highest priority task of all the waiting tasks are put into the ready-list with the help of Event Control Block (ECB). This being a preemptive kernel, if this recently released task is of a higher priority than the task currently running an immediate context switch occurs. The signals that allow tasks and ISRs to synchronize with each other are called events within the context of  $\mu$ C/OS-II. Task can wait for other tasks or ISRs to send an event signal with the help of kernel data structures called as Event Control Blocks (ECB) [25, p. 134]. It is important to note that only tasks can be in the waiting state and ISRs are not allowed to wait on the ECB.

$\mu$ C/OS-II maintains the task dependent on an event and other crucial data structures such as semaphore counters, pointer arrays for message queues etc with the help of an ECB. Each semaphore, mailbox and queue is assigned an ECB with which inter-task synchronization can be made possible.

Using the OSEventTbl[] and OSEventGrp data structures, which are very similar to the OSRdyGrp and OSRdyTbl of the ready list, it maintains the list of waiting tasks. The same operations as mentioned earlier to place or remove task from the ready list can be used to place or remove tasks from the event wait list.

OSEventTaskWait() function is called when it is needed to remove a task from the ready list and instead be placed on the wait list while it waits for an event to occur. When the event, such as the release of a semaphore, occurs task can be removed from the wait list and put on the ready list by calling OSEventTaskWait().

Semaphores in  $\mu$ C/OS-II can be access with the help of 5 services namely OSSemCreate(), OSSemPend(), OSSemPost(), OSSemAccept and OSSemQuery.

# 2.4.7 Message Queues

To be able to send one or more messages between tasks  $\mu$ C/OS-II provides the messaging queue service [25]. The use of global variables to exchange data between tasks and ISRs has certain restrictions. It is possible for tasks to share data between each other by protecting global variables with semaphores. However for a task and an ISR to exchange data, semaphores cannot be used to protect the global variables since ISR cannot block on a semaphore. The way to overcome this problem is with the help of message queues.

A message in the context of  $\mu$ C/OS-II consists of a pointer to data and as is the case with semaphores there is a wait list associated with each message queue. The message queue is essentially an array of void type capable of storing address of the memory blocks which have the required data within them. This avoids the overhead of copying the data and allows pointers to be passed around making the implementation faster.

A task that expects to read a message from the queue but if the message is not available the task will be suspended and is placed on the wait list. This wait period can also be specified in the form of a timeout period. If the message is not received within this timeout period the waiting task is put into the ready-list and returns back with an error code indicating no message. Here again ECB would be required for the wait list.

When the message is delivered into the queue by the producer task then two things can occur. If there are no tasks waiting for the message then this message gets buffered within the queue and corresponding data structures to maintain the circular queue are updated. However, if there is a task on the wait list, then this task is put on the ready-list and the message is directly given to the task by passing the pointer to the tasks TCB.

Apart from the ECB we also need another kernel data structure called the Queue Control Block (QCB) [25]. This holds the required data to manage the queue.

.OSQStart – Holds the pointer to the start of the message queue.

.OSQEnd — Holds the pointer to one position beyond the end of the message queue, allowing circular buffer semantics to be followed.

.OSQIn — Holds the pointer to the location within the queue where the next message will be inserted. Since this is a circular queue once OSQIn value equals the OSQEnd positions is it reset to OSQStart value.

.OSQOut — Holds the pointer to the location within the queue where the next message can be retrieved from. Since this is a circular queue once OSQOut value equals the OSQEnd positions is it reset to OSQStart value.

.OSQSize — This value is set at the time of creation of the message queues and indicated the maximum number of message entries possible within the queue.  $\mu$ C/OS-II allows up to 65535 entries within each queue.

**.OSQEntries** – Holds the number of message currently in the message queue.

The functions that would be required to be understood for the scope of this project are the following:

**OSQCreate()** — This function creates the queue. In the process of creation of a queue an ECB and a Q\_OS is acquired from the kernel. It then links the ECB and the OS\_Q data structures by passing the pointer of the QCB into ECBs OSEventPtr field. Then it initializes the QCB data structures such as the size of the queue to OSQSize, start and end positions and sets the in and out values to 0 indicating that the queue is empty.

**OSQPost()** — This function is used to deposit a messgae to a waiting task or the queue. When a message is generated by the producer this function first checks the ECB to see if there are any tasks currently waiting on the message. If there are then it puts the message onto the task's TCB and removes the task from the wait list and puts it onto the ready list.

If there are no task waiting in the wait list. It then places the data ontot the circular buffer, makes changes to the OSQIn and OSQEntries values.

**OSQPend()** — This function is used to wait for a message. When the message becomes available and no task is on the wait list it decrements the value of OSQEntries and moves the OSQOut value. If the message is not available then the task puts itself on the wait list and calls the OSSched() function to schedule the next highest priority task to run. After the timeout has occurred the task wakes up to see if there is a message on its TCB.

If there is no message it returns with an error message to be appropriately handled by the application.

**OSQAccept()** — This function is similar to OSQPend() except that if there is no message available it does not put the task to sleep and return back with a null pointer indicating that no message was available. This makes it ideal to be used from within an ISR since blocking is not permitted.

#### 2.4.8 Memory Management

Dynamic memory allocation is generally done with the use of ANSI C compilers malloc() and free() functions. However these schemes have a problem of fragmentation. In a case where a large contiguous memory is demanded by the task and because of fragmentation no such contiguous memory is not available then the application execution can break down. Another reason for having a special dynamic memory allocation scheme apart from the use of malloc() and free() is the non-determinism in the execution time of these functions [26, p. 299]. The memory management scheme followed in  $\mu$ C/OS-II for allocation and de-allocation is done in constant time and is deterministic.

$\mu$ C/OS-II manages memory in the form of partitions. Here partition is the contiguous block of memory that is global to the tasks. This block of memory is known as a partition in the context of  $\mu$ C/OS-II. This partition is initialized and managed with the help of the various memory management services about which further discussion would be taken up. However like in the case of semaphores or message queues, there is kernel data structure which is needed to manage these partitions. This data structure is called the Memory Control Block (MCB). Now, based on the size of each of the memory block required by the application, this partition is further divided into memory blocks. Say, if we allocate a 1024Bytes of memory to a partition and each block is of size 32bits (4Bytes) then there would be 256 (1024/4) such memory blocks available to the application tasks. To better understand the memory management techniques employed within  $\mu$ C/OS-II the fields of the MCB need to be analyzed.

**OSMemAddr** – Holds the beginning address of the memory partition. During the OSMemCreate() function call this entire partition is initialized by stetting the value to 0.

**OSMemFreeList** — Holds the pointer of the next available free memory block from the linked list of free memory blocks.

**OSMemBlkSize** — Is set only at time when OSMemeCreate() is called and holds the size of each memory block.

**OSMemNBlks** — This value is also set during the call to OSMemCreate() and holds the number of memory blocks within the partition.

**OSMemNFree** – Holds the number of free memory blocks available in the partition.

Now that the function of each of the data members has been discussed, a complete picture of how memory management is done in  $\mu$ C/OS-II can be gathered with a discussion on the memory management services provided.

**OSMemeCreate()** — It is assumed that the memory partitions are created before this function is called. As a part of the initialization done during this function call, the memory blocks are cleared and set with zero. More importantly a linked list of the memory blocks is created. This linked list represents the free blocks available within the partition.

As a part of the function call the starting address of the partition is passed within the function call along with the number of memory blocks required and size of each block. On the successful initialization, of this partition and the creation of the memory blocks each of these values are assigned to OSMemAddr, OSMemNBlks and OSMemBlkSize member of the MCB respectively.

**OSMemGet()** — This function call is equivalent of the malloc() system call. Based on the partition MCB passed into the function call as a parameter, a memory block from the partition is returned. If a memory block is available within the partition then the OSMemNFree value is decremented and a pointer to the memory block is returned. If no memory block is available then a well-known error value is returned indicating that there are no longer any free memory block available.

**OSMemPut()** — This function call is equivalent of the free() system call. As a part of the parameters the pointer to the partition's MCB as well as the memory blocks address is passed. As a part of this call it also checked if the memory partition is already full. If it is not full then OSMemNFree value is incremented and success value is returned back. However, if the partition is already full then this indicates an error condition and return the error OS\_MEM\_FULL. An important point to note here is that it is possible that, owing to an error in programming, a block belonging to another memory partition can be returned through OSMemPut to another partition. Such a situation should be avoided.

### 2.5 Automatic Code Generation and $\mu$ C/OS-II

# 2.5.1 Model Based Design and Rapid Prototyping

Model based design (MBD) is increasingly being adopted as a methodology for designing complex embedded systems since it allows advanced verification and validation [1]. MBD can be defined in simple terms as the use of diagrams, mathematical or other visual methods to represent the components of a complex control system [41].

Another key approach that is used in the development and validation, especially for embedded control systems, is the use of rapid prototyping. In an multi-domain environment where all the of required sub-systems and components might not be available during the early stages of the project, the use of prototyping allows the design teams to work with customers and continuously refine the designs and validate them as well.

In a typical industry setup, say for the development of a new controller module, during the early stages of the development process an initial prototype is often required. Designer usually incorporate the functional algorithms and early iterations of the software on an FPGA or a generic microprocessor with similar specifications to demonstrate the feasibility and performance of the controller [20]. This process repeats over many iteration till the software and hardware is finally ready for deployment in the production environment.

Within each iteration of this rapid prototyping approach an idealized form of the model is created, containing the most refined versions of the algorithm and the functional logic. This model can then be tested and validated in either a simulation environment also called as model-in-loop testing or with the help of automatic code generation tools the code can be deployed on the controller hardware for validation. This hardware could be the production hardware, if available, or an FPGA. With this approach, during every iteration the model parameters can be fine-tuned, optimized and tested for functionality, compliance to standards and robustness.

SIMULINK can be used for the purpose of automatic code generation if the requirements include the fixed point and timing behaviors. The following sections would discuss more in details regarding this code generation process from models.

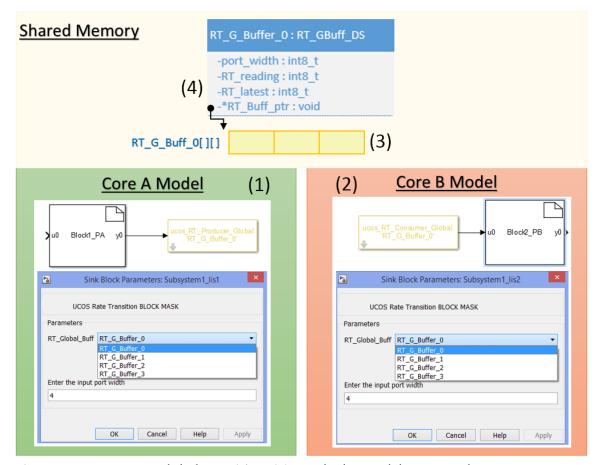

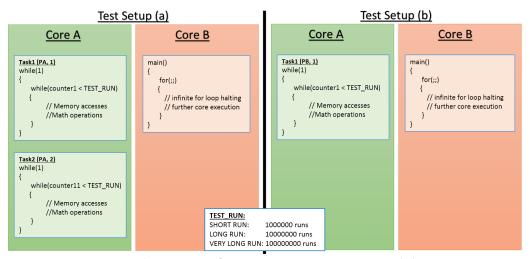

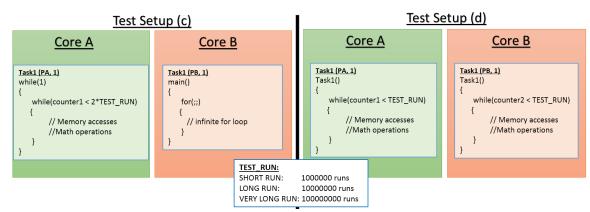

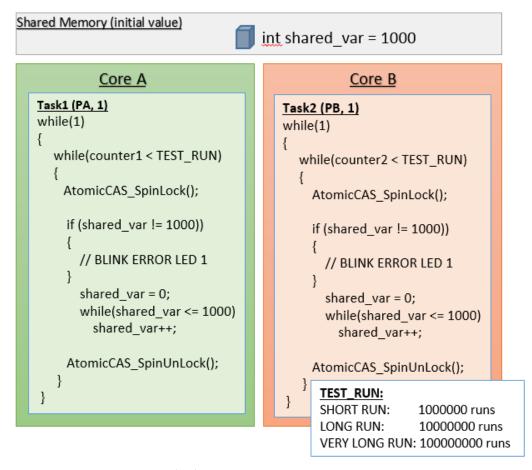

## 2.5.2 Code Generation Architecture and TLC Process