Digital Calibration and Effective Number of Bit Prediction for Pipeline ADC

by

## Kibeom Kim

## A Thesis Presented in Partial Fulfillment of the Requirements for the Degree Master of Science

Approved November 2013 by the Graduate Supervisory Committee:

Sule Ozev, Chair Jennifer Kitchen Hugh Barnaby

## ARIZONA STATE UNIVERSITY

December 2013

## ABSTRACT

In thesis, a test time reduction (a low cost test) methodology for digitally-calibrated pipeline analog-to-digital converters (ADCs) is presented. A long calibration time is required in the final test to validate performance of these designs. To reduce total test time, optimized calibration technique and calibrated effective number of bits (ENOB) prediction from calibration coefficient will be presented. With the prediction technique, failed devices can be identified only without actual calibration. This technique reduces significant amount of time for the total test time.

To My parents

## ACKNOWLEDGEMENTS

This thesis would not have been possible without the support of many people. I would like to express my gratitude to Dr. Sule Ozev for giving me this research opportunity and her continuous support as well as my committee members: Dr. Jennifer Kitchen, Dr. Yu (Kevin) Cao.

I would like to express my appreciation to Jae Woong Jeong, Doo Hwang Chang and Deepak Mucatira for their assistance. Lastly, my deepest and special thanks should go to my family since they always have loved me, believed in me, supported me, and encouraged me in my study

# TABLE AND CONTENTS

|        |        | Pag                                      | e  |

|--------|--------|------------------------------------------|----|

| LIST   | OF TA  | BLESvii                                  | ii |

| LIST ( | OF FIG | URESi                                    | X  |

| СНАР   | TER    |                                          |    |

| 1      | INTRO  | DDUCTION                                 | 1  |

|        | 1.1    | Introduction                             | 1  |

|        | 1.2    | Motivation                               | 1  |

|        | 1.3    | Thesis Outline                           | 2  |

| 2      | BACK   | GROUND                                   | 3  |

|        | 2.1    | ADC Performance Metrics                  | 3  |

|        | 2.2    | Pipeline ADC                             | 4  |

|        |        | 2.2.1 Pipeline ADC Architecture          | 4  |

|        |        | 2.2.2 Mathematical Model of Pipeline ADC | 5  |

|        | 2.3    | Errors in Pipeline ADC                   | 7  |

|        | 2.4    | Kernel estimation                        | 8  |

| 3      | PROP   | OSED METHODOLOGY                         | 8  |

| 4      | RESU   | LTS                                      | 9  |

| 5      | CONC   | LUSION                                   | 9  |

| CHAPTER   |      |             | Page |

|-----------|------|-------------|------|

| 5.1       | Sumn | nary        | 19   |

|           | 5.2  | Future work | 19   |

| REFERENCE | ES   |             | 20   |

# LIST OF TABLES

| Table | Page                                                               |

|-------|--------------------------------------------------------------------|

| 3.1   | Stage calibration trip points setting requirements11               |

| 3.2   | Stage calibration coefficients                                     |

| 4.1   | Capacitor mismatch ratio for 1 <sup>st</sup> running13             |

| 4.2   | Capacitor mismatch ratio for 2 <sup>nd</sup> running14             |

| 4.3   | Capacitor mismatch ratio for 3 <sup>rd</sup> running14             |

| 4.4   | Actual vs. Calibrated SINAD and ENOB of 14-bit pipeline ADC16      |

| 4.5   | Average and Maximum difference of actual and predicted ENOB values |

# LIST OF FIGURES

| Figure                                              | Page |

|-----------------------------------------------------|------|

| 2.1 Block Diagram of a Pipeline ADC                 | 4    |

| 2.2 One stage of Pipeline ADC                       | 5    |

| 2.3 Transfer curve of a stage residue amplification | 6    |

| 2.4 Offset Error in a 3-bit ADC                     | 7    |

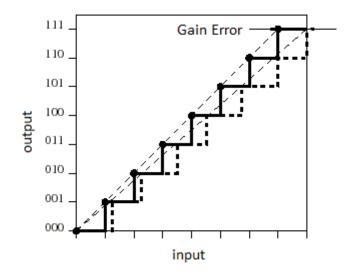

| 2.5 Gain Error in a 3-bit ADC                       | 7    |

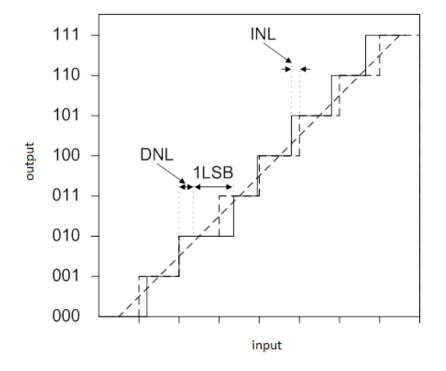

| 2.6 INL and DNL in 3-bit ADC                        | 8    |

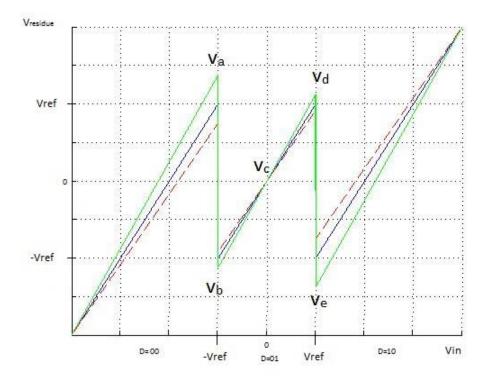

| 3.1 Trip points of stage calibration                | 11   |

| 4.1 Output of 1 <sup>st</sup> running               | 15   |

| 4.2 Output of 2 <sup>nd</sup> running               | 15   |

| 4.3 Output of 3 <sup>rd</sup> running               | 16   |

| 4.4 Actual and predicted ENOB                       | 17   |

| 4.5 Actual vs predicted ENOB                        | 17   |

### 1. INTRODUCTION

### 1.1 Introduction

Due to the rapid development of digital signal processors (DSP) and communication technology, Analog to Digital Converters (ADCs) became essential parts in various applications. However, in current technology scales, because of the requirement of high sensitivity and accuracy to fabrication and various interferences and noises from the manufacturing environments, calibration process became inevitable to generate reliable data conversion. Especially, digital calibration techniques are most popular considering digital circuits are self-error detectable, and synthesizable. Furthermore, a digitally-assisted design style becomes an increasing trend [1]. Digital calibration techniques have been popularly used in various ADC architectures such as pipeline ADCs [2], successive-approximation register (SAR) ADCs [3], and sigma-delta ADCs [4]. In the last decade, pipeline ADCs are widely employed because it has desirable speed, resolution with relatively low power consumption and small size. The ADC model used in this research is a 14-bit 1MS/s 1.5bit/stage pipeline ADC with 2-bit auxiliary ADC.

## 1.2 Motivation

In order to obtain higher reliability and accuracy in data conversion from ADC, calibration became an essential process. In addition, digital calibration overcomes the analog impairments like finite op-amp gain, op-amp offset, and capacitor mismatch. Several digital calibration techniques for pipeline ADCs [5-8] have proven its superior effect.

1

Testing the final performance of a digitally-calibrated ADC should be run after calibration. However, device testing and calibration process requires huge amount of time especially ADC testing due to its huge portion of data which has to be acquired to achieve its static and dynamic parameters. Effective number of bits (ENOB), in particular, is generally must be measured which represents the signal to noise ratio and distortion (SINAD). The most widely used method to calculate ENOB of ADCs [9] is to apply a sine wave to input and obtain output, then apply a coherent FFT plot to obtain SNR value. From the SNR value from the sine-wave test, use the formula for the conversion from SNR to ENOB, which is defined as

$$ENOB = \frac{SNR - 1.76}{6.02} \tag{1.1}$$

SNR unit is dB and ENOB is presented in bits. As mentioned above, ENOB calculation needs coherent FFT plotting which takes huge amount of time for calculation compare to obtaining only calibration coefficients. Consequently, I propose a digital calibration technique for pipeline ADC and a test methodology for reducing overall test time by acquiring predicted ENOB value from calibration coefficients in this thesis.

## 1.3 Thesis Outline

This thesis is organized as following. Background knowledge of performance parameters of ADCs are explained in Chapter2. In Chapter 3, the proposed test methodology of ENOB prediction from calibration coefficients is provided. The simulation results are presented in Chapter 4. At last, the conclusion and future work are given in Chapter 5.

#### 2. BACKGROUND

The basic knowledge of ADCs and performance of a pipeline ADC and kernel estimation technique will be presented in this chapter. The major parameters used to represent the overall performance of an ADC are explained in Section 2.1. Section 2.2 presents operation and structure of a general pipeline ADC. In Section 2.3, various errors occur in pipeline ADC will be given. Finally, in section 2.4, kernel estimation background will be presented.

### 2.1 ADC Performance Metrics

The most commonly used and one of the most important metrics for measuring the performance of an ADC is the signal-to-noise ratio (SNR). SNR is defined as the power ratio between the signal and the noise. SNR can be calculated easily. First, collect the output codes correspond to sinusoidal input and create a coherent FFT-plot from the output codes. Then, take the power level of the signal and comparing it to the total remaining power (except DC power). The equation for SNR calculation is shown below.

$$SNR_{dB} = 10log_{10} \left(\frac{P_{signal}}{P_{noise}}\right) = P_{signal,dB} - P_{noise,dB}$$

(2.1)

Also, SNR describes in terms of effective number of bits (ENOB). ENOB shows the overall accuracy of the ADC. The equation for ENOB is in Eq. (1). If there is quantization noise correlated to the input, a different conversion signal to noise ratio and distortion (SINAD) to ENOB should be considered. The equation for SINAD is shown below.

$$SINAD_{dB} = 10log_{10} \left( \frac{P_{signal}}{P_{noise} + P_{distortion}} \right) = P_{signal,dB} - P_{noise,dB} - P_{distortion,dB} (2.2)$$

3

For the conversion from SINAD to ENOB is almost the same as the conversion from SNR to ENOB. Instead of SNR use SINAD in the same equation.

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

(2.3)

2.2 Pipeline ADC

## 2.2.1 Pipeline ADC architecture

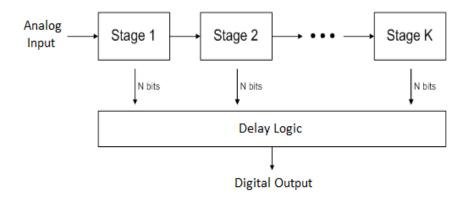

The pipeline ADCs are one of the most popular architecture in modern applications in advantage of its high resolution and relatively small size. A general pipeline ADC block diagram is described in Fig. 2.1. The ADC described in the block diagram has K stages and delay logic to synchronize the outputs from the each stage.

Fig. 2.1 Block Diagram of a Pipeline ADC

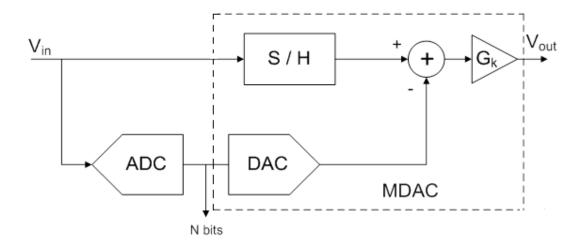

Each stage is consist of a low resolution typically 1 to 2.5 bit ADC and multiplying digital to analog converter (MDAC) which operates sample and hold(S/H) process, digital to analog conversion, and subtraction and amplification. One stage of pipeline ADC is shown in Fig. 2.2.

Fig. 2.2 One stage of Pipeline ADC

Each stage has identical structure and very straight forward function. The input voltage from previous stage is sampled and converted by a low resolution ADC to N bit digital code. Then, the converted code is again converted back to analog signal by DAC. The sampled input signal is subtracted by converted analog signal which is generated by the DAC. Finally, the subtracted value is amplified and sent to next stage. The signal sent to the next stage is also called residue signal or voltage. The digital output code of each stage will be added each other to acquire the final digital code of the ADC. All the stages uses the same clock, the same reference voltage, and the same gain.

## 2.2.2 Mathematical Model of Pipeline ADC

In this section, mathematical modeling for a pipeline ADC will be given. As explained in the previous section each stage of pipeline ADC has the same transfer function. Since, differential pipeline ADC is used in this thesis, the transfer function given below is for 1.5bit/stage pipeline ADC. Where V<sub>out</sub> is output voltage of the stage and  $D_{out}$  is 1.5bit digital output code of the stage. G is the gain of amplifier and in this case it is 2 and g consists of G - 1, so 1 in the ideal case.

$$V_{out} = G * V_{in} + k * g * V_{ref}$$

(2.4)

$$\mathbf{k} = \begin{cases} -1, & V_{in} > V_{ref} \\ 0, & V_{ref} > V_{in} > -V_{ref} \\ 1, & -V_{ref} > V_{in} \end{cases}$$

(2.5)

$$D_{out} = \begin{cases} 10, & V_{in} > V_{ref} \\ 01, & V_{ref} > V_{in} > -V_{ref} \\ 00, & -V_{ref} > V_{in} \end{cases}$$

(2.6)

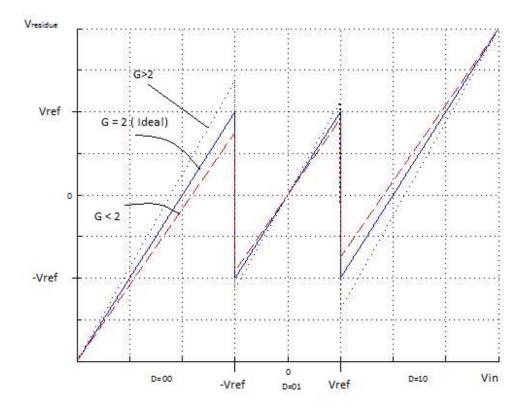

Fig 2.3 shows the transfer curve of each stage with the case of G>2, G=2(ideal), G<2.

Fig 2.3 Transfer curve of stage residue amplification

# 2.3 Errors in ADC

As the input and the corresponding output are directly related in ADC, errors in the conversion are easily noticeable and measureable as long as we know the input. General errors occur in ADC are offset error, gain error, and nonlinearity errors (INL and DNL).

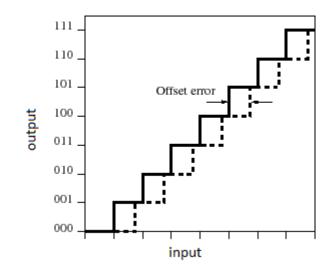

Fig. 2.4 Offset Error in a 3-bit ADC

Fig. 2.5 Gain Error in a 3-bit ADC

Fig. 2.4 shown above illustrates the offset error in a 3-bit ADC. The definition of the offset error is a constant difference between the ideal output and the actual output over the whole range of the ADC. Fig. 2.5 shows the gain error in a 3-bit ADC. Gain error is defined as the difference of the slope of the ideal output and the actual output. Offset error is related to a quantization step of the ADC. Gain error is usually expressed in a percentage unit. The expressions of offset error and gain error in N-bit ADC are given below. Where  $V_{ti}$  is i<sup>th</sup> transition voltage, respectively  $i = 1 \sim 2^{N}-1$ .

Offset Error<sub>LSB</sub> =

$$\frac{V_{t1,ideal} - V_{t1,actual}}{V_{LSB}}$$

(2.7)

Gain Error =

$$\left(\frac{V_{t(2^{N}-1),ideal} - V_{(2^{N}-1),ideal}}{V_{t(2^{N}-1),actual} - V_{(2^{N}-1),actual}}\right) * 100$$

(2.8)

Fig. 2.6 INL and DNL in 3-bit ADC

The most important static parameters in ADCs are integral nonlinearity error (INL) and differential nonlinearity error (DNL). A plot for INL and DNL is given in Fig 2.6. These parameters represent the accuracy and performance of an ADC and contain errors of nonlinearity, quantization, offset, and noise. Differential nonlinearity error (DNL) is the difference between a digital output step size of an ADC and a step size calculated by dividing whole range of the ADC by the digital code numbers. If the maximum DNL error value is smaller than 0.5 LSB, the ADC is guaranteed that is monotonic. Monotonic means the digital output code does not collapse when increasing input signal is given. The mathematical equation of DNL is given below.

$$V_{LSB} = \frac{V_{t(2^{N}-1)} - V_{t1}}{2^{N} - 1}$$

(2.9)

$$DNL_n = \frac{V_{t(n+1)} - V_{t(n)}}{V_{LSB}} - 1$$

(2.10)

$$INL_n = \sum_{i=1}^n DNL_n \tag{2.10}$$

As shown in Eq. 2.10, INL and DNL are directly connected.

#### 2.4 Kernel Estimation Method

A kernel estimation method [10], [11] is used for prediction in this research. Assume that  $x_i$ , i = 1, ..., n, is an independent and identically distributed random variables with an unknown density f. The basic kernel estimation is written as

$$\tilde{f}(x) = \frac{1}{nh} \sum_{i=1}^{n} K\left(\frac{x - x_i}{h}\right) = \frac{1}{n} \sum_{i=1}^{n} K_h(x - x_i)$$

(2.11)

Where  $K_h(t) = K(t/h)/h$ , h>0 is a smoothing parameter called bandwidth [12]. Kernel estimation is closely related to histograms. However, kernel estimation can be provided with better smoothness or continuity by employing a appropriate kernel. A range of kernel functions are uniform, triangular, bi-weight, tri-weight, Epanechnikov, normal, and others. Epanechnikov kernel is the most optimal in a minimum variance. The bandwidth of the kernel mentioned above is a parameter which has a strong influence to the estimated results. The most common this bandwidth parameter is termed the mean integrated squared error (MISE) is given as

$$MISE(\tilde{f}) = \int E\{\tilde{f}(x) - f(x)\}^2 dx \qquad (2.12)$$

With the assumption of f(x) follows a *d*-variate normal distribution.

$$f(x) = PDF(x) = \frac{1}{\sigma\sqrt{2\pi}}e^{-\frac{(x-\mu)^2}{2\sigma^2}}$$

#### 3 PROPOSED METHODOLOGY

In chapter 3, the proposed method of digital calibration and prediction of effective number of bits using calibration coefficient for pipeline ADC to reduce the static specification test time will be presented. The calibration technique used in this research is introduced in Section 3.1. Then, in Section 3.2, proposed prediction technique is described.

## 3.1 The Concept of a Foreground Digital Calibration

Foreground calibration scheme is to estimate errors due to component mismatch, finite gain, offset and other non-ideal effects [13]. The foreground calibration stars with the least significant stage and recursively proceeds backwards to the most significant stage. In this research, 14bit pipeline ADC with 2 bit auxiliary is used. Therefore, the 2 bit auxiliary ADC is used to calibrate  $14^{th}$  stage first, and the  $14^{th}$  stage is calibrated, it joins the 2 bit auxiliary ADC to calibrate the frontend  $13^{th}$  stage. This process goes on until  $1^{st}$  stage is calibrated. One complete digital calibration for all stage needs to be executed at the initial startup. Fig 3.1 and Table 3.1 illustrate how one stage is calibrated to generate the related calibration coefficient. Each stage calibration needs five trip points,  $V_a$ ,  $V_b$ ,  $V_c$ ,  $V_d$ ,  $V_e$ , and Table 3.1 shows how the analog input Vin and D need to be set in order to calculate their values. Once these five trip points' values are acquired, we can use the equation in Table 3.2 to get the necessary calibration coefficients for each stage. In the ideal case, all the calibration coefficients  $C_{1, n}$ ,  $C_{0, n}$ ,  $C_{-1, n}$  are zero. Where n is stage number, G is gain of each stage, ideally, G = 2.

Fig 3.1 Trip points of stage calibration

| Table 3.1 Stage   | 111 .1      |      | •      | •       | •               |

|-------------------|-------------|------|--------|---------|-----------------|

| Table 3 I Stare   | colibration | trin | nointe | cotting | roguiromonte    |

| 1 a D C D 1 O C C | Campianon   | un   | DOTINS | Setung  | ICUUIICIIICIIIS |

|                   |             |      | P      | ~       |                 |

| Trip Point     | V <sub>in</sub>   | D  |

|----------------|-------------------|----|

| Va             | -V <sub>ref</sub> | -1 |

| V <sub>b</sub> | -V <sub>ref</sub> | 0  |

| V <sub>c</sub> | 0                 | 0  |

| V <sub>d</sub> | V <sub>ref</sub>  | 0  |

| Ve             | V <sub>ref</sub>  | 1  |

| Calibration Coefficients | Equations                     | Values                        |

|--------------------------|-------------------------------|-------------------------------|

| C <sub>1, n</sub>        | $2^{n-1} - (V_d - V_e) + V_c$ | $2^n - G * V_{ref} + V_{os}$  |

| C <sub>0, n</sub>        | Vc                            | Vos                           |

| C <sub>-1, n</sub>       | $-2^{n-1}-(V_a - V_b) + V_c$  | $-2^n + G * V_{ref} + V_{os}$ |

Table 3.2 Stage calibration coefficients

## 3.3 The Concept of Kernel Estimation Based Adaptive Prediction

In this research, we used a kernel-based estimation approach [14], [15] for our adaptive prediction technique. Kernel estimation gives us to find the correlations between the Calibration Coefficients and ENOB values and update the joint probability distribution function (JPDF) after running training set. After the training process, the created probability distribution function (PDF) provides the most possible value of the correlated parameter. The kernel function is given in (3.1). Among the number of wellknown kernels, we chose the Gaussian distribution as kernel to be used. Using the Gaussian distribution kernel, equation (3.2) is the PDF estimated.

$$\int_{-\infty}^{\infty} K(x) dx = 1$$

(3.1)

$$\widehat{PDF}(s) = \frac{1}{n \prod h_j} \sum_{i=1}^n w_i \prod_j^M K\left(\frac{s_j - S_{i,j}}{h_j}\right)$$

(3.2)

Where *h* is the kernel width,  $S_i$  is a vector containing parameters of  $i^{th}$  device in the training set,  $w_i$  is kernel weight, *n* is the size of training set, and M is the number of

parameters which is number of calibration coefficients of each device. Kernel based PDF estimation basically adds kernels on each data in training set  $(S_i)$ . The kernel width *h* is adjustable to acquire the most suitable value. Equation (3.3) is the optimized width for the Gaussian kernel to minimize MISE.

$$h_j = \left(\frac{4}{d+2}\right)^{\frac{1}{d+4}} \sigma_j n^{-\frac{1}{d+4}}$$

(3.3)

Where *d* is number of dimensions and  $\sigma_j$  is standard deviation of the estimated parameters of *j*<sup>th</sup> specification in this paper the specification is the calibration coefficient.

#### 4 RESULTS

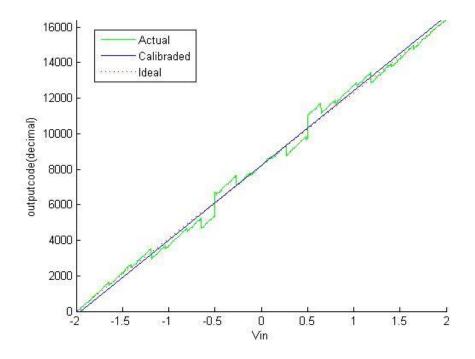

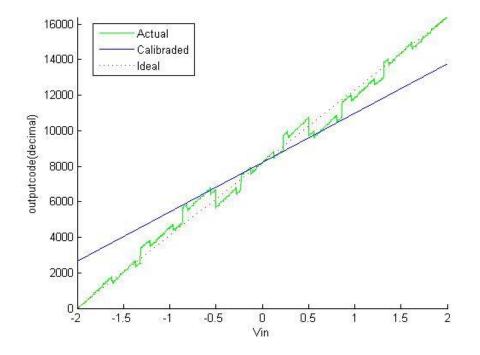

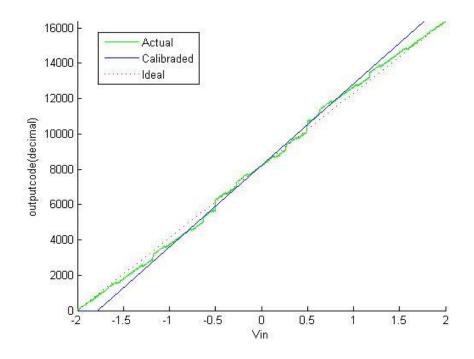

We have modeled a pipeline ADC in MATLAB and performed statistical simulations to verify our calibration and prediction methodology and mathematical equations we proposed. The model is considered that has offset error, capacitor mismatch. It is assumed that this pipeline ADC has less than ±30% capacitor mismatches. With the assumption, the variables have random values with normal distributions. A 14-stage, 1.5 bit per stage, 1Mega Sample per second pipeline ADC with 2-bit auxiliary ADC is modeled ADC. Table 4.1 to 4.3 shown below are capacitor mismatch ratios for each running and Fig. 4.1 to 4.3 are output plot of each running comparing actual, calibrated, and ideal output.

| Stage<br>Number   | Stage 1 | Stage 2 | Stage 3  | Stage 4  | Stage 5  | Stage 6  | Stage 7  |

|-------------------|---------|---------|----------|----------|----------|----------|----------|

| Mismatch<br>Ratio | 1.180   | 0.785   | 0.953    | 1.249    | 1.175    | 1.276    | 1.093    |

| Stage<br>Number   | Stage 8 | Stage 9 | Stage 10 | Stage 11 | Stage 12 | Stage 13 | Stage 14 |

| Mismatch<br>Ratio | 0.721   | 1.209   | 1.260    | 1.107    | 1.155    | 1.146    | 0.935    |

Table 4.1 Capacitor mismatch ratio for 1<sup>st</sup> running

| Stage<br>Number   | Stage 1 | Stage 2 | Stage 3  | Stage 4  | Stage 5  | Stage 6  | Stage 7  |

|-------------------|---------|---------|----------|----------|----------|----------|----------|

| Mismatch<br>Ratio | 0.837   | 1.248   | 0.791    | 1.196    | 1.023    | 1.298    | 0.747    |

| Stage<br>Number   | Stage 8 | Stage 9 | Stage 10 | Stage 11 | Stage 12 | Stage 13 | Stage 14 |

| Mismatch<br>Ratio | 0.966   | 0.764   | 1.277    | 0.703    | 1.165    | 1.190    | 1.221    |

Table 4.2 Capacitor mismatch ratio for 2<sup>nd</sup> running

Table 4.3 Capacitor mismatch ratio for 3<sup>rd</sup> running

| Stage<br>Number   | Stage 1 | Stage 2 | Stage 3  | Stage 4  | Stage 5  | Stage 6  | Stage 7  |

|-------------------|---------|---------|----------|----------|----------|----------|----------|

| Mismatch<br>Ratio | 1.212   | 1.073   | 0.911    | 1.008    | 0.941    | 0.746    | 0.844    |

| Stage<br>Number   | Stage 8 | Stage 9 | Stage 10 | Stage 11 | Stage 12 | Stage 13 | Stage 14 |

| Mismatch<br>Ratio | 0.774   | 0.810   | 0.844    | 0.950    | 0.731    | 1.242    | 1.267    |

Table 4.4 shows the SINAD and ENOB results comparing before and after calibration. This calibration provides approximately 60% to 83% improvements in ENOB.

Fig. 4.1 Output of 1<sup>st</sup> running

Fig. 4.2 Output of 2<sup>nd</sup> running

Fig. 4.3 Output of 3<sup>rd</sup> running

Table 4.4 Actual vs. Calibrated SINAD and ENOB of 14-bit pipeline ADC

|          | Actual    |            | Calib     | orated     | Improvement $(0/)$ |

|----------|-----------|------------|-----------|------------|--------------------|

|          | SINAD(dB) | ENOB(bits) | SINAD(dB) | ENOB(bits) | Improvement (%)    |

| $1^{st}$ |           |            |           |            |                    |

| $2^{nd}$ |           |            |           |            |                    |

| $3^{rd}$ |           |            |           |            |                    |

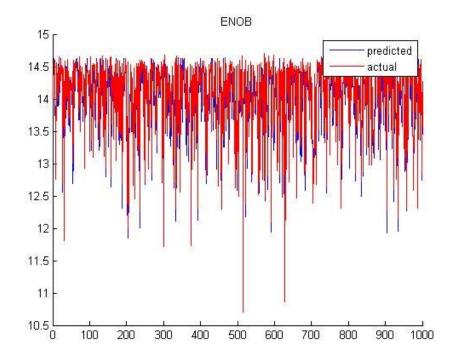

We made 1400 cases of gradually increasing capacitor mismatch training set for the prediction and ran 1000 randomly generated capacitor mismatch cases for comparing actual and predicted ENOB values. Fig 4.4 shows actual (red) and predicted (blue) ENOB values.

Fig 4.4 Actual and predicted ENOB

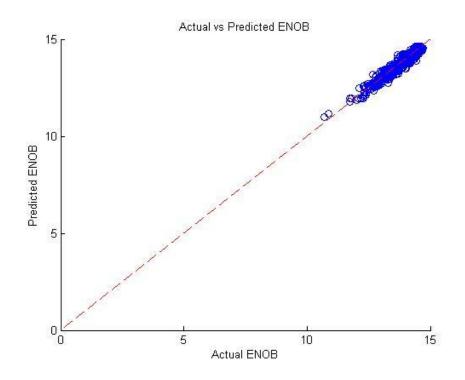

Fig 4.5 Actual vs predicted ENOB

Fig 4.5 illustrates actual (x-axis) versus predicted (y-aixs) ENOB values and Table 4.5 is brief comparison between actual and predicted ENOB values. It has maximum of 4.1156% difference in whole 1000 cases and average difference is less than 0.5%.

| Table 4.5 Average and Maximum diff | erence of actual and predicted ENOB values |

|------------------------------------|--------------------------------------------|

|------------------------------------|--------------------------------------------|

|         | Difference (%) |

|---------|----------------|

| Average | -0.4758        |

| Maximum | 4.1156         |

### 5 CONCLUSION

## 5.1 Summary

In this thesis, a novel methodology for digital calibration and ENOB prediction of pipeline ADC is presented. For the verification of the proposed method, mathematical model of the ADC and equations for kernel based estimation are derived. In the mathematical model, non-ideal parameters such as non-ideal operational amplifier, capacitor mismatch, comparator offset, and random noise are considered. The proposed calibration method is based on foreground digital calibration technique. The calibration method proposed in this thesis significantly reduces initial calibration process time and provides reliable result compare to conventional method. In addition, the kernel based estimation prediction method we proposed also reduces remarkably for post calibration testing time with highly accurate result.

## 5.2 Future work

Most of modern devices are made in mass production and especially ADCs with high speed sampling frequency and high resolution requires huge amount of time for testing. Therefore, the proposed prediction method can be extended to other parameters.

#### REFERENCES

- [1] B. Murmann, "Digitally-Assisted Analog Circuits," *IEEE Micro*, Vol. 26, no. 2, pp. 38-47, Mar.-Apr. 2006.

- X. Wang, and P. J. Hurst, S. H. Lewis, "A 12-Bit 20-Msample/s Pipelined Analog-to-Digital Converter with Nested Digital Background Calibration," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1799-1808, Nov. 2004.

- W. Liu, P. Huang, and Y. Chiu, "A 12 bit 22.5/45 MS/s3.0 mW 0.059mm<sup>2</sup> CMOS SAR ADC Achieving over 90 dB SFDR," in *ISSCC Dig. Tech. Papers*, 2010, pp. 380-381.

- S. -C. Lee and Y. Chiu, "Digital Calibration of Nonlinear Memory Errors in Sigma-Delta Modulators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 9, pp. 2462-2475, Sep. 2010.

- [5] Kang-Wei Hsueh, Yu-Kai Chou, Yu- Hsuan Tu, Yi-Fu Chen, Ya-Lun Yang, and Hung-Sung Li, "A 1V 11b 200MS/s pipelined ADC with digital background calibration in 65nm CMOS," in Proc. of 2008 Intl. Solid- State Circuits Conference (ISSCC2008), Feb, 2008.

- [6] E. Iroaga and B. Murmann, "A 12b, 75MS/s pipelined ADC using incomplete settling," IEEE J. of Solid-State Circuits, vol. 42, no. 4, pp. 748-756, Apr 2007.

- [7] J. McNeill, M. Coln, and B. Larivee, "A split-ADC architecture for deterministic digital background calibration of a 16bit 1 MS/s ADC," in Proc. of 2005 Intl. Solid-State Circuits Conf. (ISSCC2005), Feb. 2005.

- [8] J. Li and U.-K. Moon, "Background calibration techniques for multistage pipelined ADCs with digital redundancy," IEEE Trans. Circuits and Systems – II, Analog and Digital Signal Processing, vol. 50, no. 9, pp. 531-538, Sep. 2003.

- [9] S. Weaver, B. Hershberg, and Un-Ku Moon, "ENOB Calculation for ADCs with Input-Correlated Quantization Error Using a Sine-Wave Test," ICM 2010 pp. 5-8,

- [10] D. W. Scott, *Multivariate Density Estimation: Theory, Practice, and Visualization*. NewYork: Wiley, 2008.

- [11] H. –G. Stratigopoulos, S. Mir, and A. Bounceur, "Evaluation of analog/RF test measurements at the design stage," *IEEE Trans. Computer Aided Design Integrated Circuits Systems.*, Vol. 28, no. 4, pp. 582-590, Apr. 2009.

- B. W. Silverman, *Density Estimation for Statistics and Data Analysis*. London, U.K. Chapman & Hall, 1986

- [13] Wang Yu, Yang Haigang, Cheng Xin, Liu Fei, Yin Tao, "A Fast Foreground Digital Calibration Technique for Pipelined ADC," Journal of Electronics(China), Vol. 29, no. 5, pp. 445-450, Sep, 2012.

- [14] Ender Yilmaz, Sule Ozev, and Kenneth M. Butler, "Per-device Adaptive Test for Analog/RF Circuits Using Entropy-Based Process Monitoring," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 21, no. 6, Jun, 2013.

- [15] E. Yilmaz and S. Ozev, "Adaptive Test Elimination for Analog/RF Circuits," in *Proc. IEEE Design Autom. Conf.*, Jul. 2009, pp. 720-725.