# **Electromigration in Gold Interconnects**

by

Stephen Kilgore

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved November 2013 by the Graduate Supervisory Committee:

James Adams, Co-chair Dieter Schroder, Co-chair Craig Gaw Stephen Krause

ARIZONA STATE UNIVERSITY

December 2013

#### **ABSTRACT**

Electromigration in metal interconnects is the most pernicious failure mechanism in semiconductor integrated circuits (ICs). Early electromigration investigations were primarily focused on aluminum interconnects for siliconbased ICs. An alternative metallization compatible with gallium arsenide (GaAs) was required in the development of high-powered radio frequency (RF) compound semiconductor devices operating at higher current densities and elevated temperatures. Gold-based metallization was implemented on GaAs devices because it uniquely forms a very low resistance ohmic contact and gold interconnects have superior electrical and thermal conductivity properties. Gold (Au) was also believed to have improved resistance to electromigration due to its higher melting temperature, yet electromigration reliability data on passivated Au interconnects is scarce and inadequate in the literature. Therefore, the objective of this research was to characterize the electromigration lifetimes of passivated Au interconnects under precisely controlled stress conditions with statistically relevant quantities to obtain accurate model parameters essential for extrapolation to normal operational conditions.

This research objective was accomplished through measurement of electromigration lifetimes of large quantities of passivated electroplated Au interconnects utilizing high-resolution in-situ resistance monitoring equipment. Application of moderate accelerated stress conditions with a current density limited to 2 MA/cm² and oven temperatures in the range of 300°C to 375°C avoided electrical overstress and severe Joule-heated temperature gradients. Temperature coefficients of resistance (TCRs) were measured to determine accurate Joule-heated Au interconnect film temperatures.

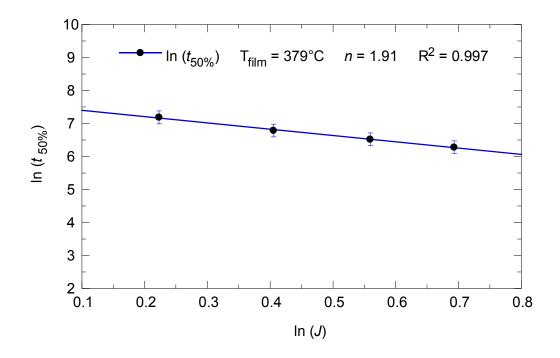

A failure criterion of 50% resistance degradation was selected to prevent thermal runaway and catastrophic metal ruptures that are problematic of open circuit failure tests. Test structure design was optimized to reduce resistance variation and facilitate failure analysis. Characterization of the Au microstructure yielded a median grain size of 0.91  $\mu$ m. All Au lifetime distributions followed lognormal distributions and Black's model was found to be applicable. An activation energy of 0.80  $\pm$  0.05 eV was measured from constant current electromigration tests at multiple temperatures. A current density exponent of 1.91 was extracted from multiple current densities at a constant temperature. Electromigration-induced void morphology along with these model parameters indicated grain boundary diffusion is dominant and the void nucleation mechanism controlled the failure time.

| his dissertation is dedicated to Professor Dieter Schroder and Charles Varker       |  |

|-------------------------------------------------------------------------------------|--|

|                                                                                     |  |

| or inspiring an inquisitive and disciplined erudition in semiconductor reliability. |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

|                                                                                     |  |

iii

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to express my sincerest appreciation for my doctoral advisor Professor Dieter K. Schroder for his guidance, timeless patience, and dedication during my graduate studies at Arizona State University. Dr. Dieter Schroder's work experience in the semiconductor industry and his desire to share his extensive knowledge were immensely important for this research. I want to express my gratitude to Professor James Adams for standing in as chair and providing guidance for completion of this dissertation in my final year. I am also very grateful for the support, guidance, and encouragement of my other doctoral committee members Professor Stephen Krause and Dr. Craig Gaw. Additionally, I would like to thank Professor Fernando Ponce for teaching me materials physics and for extending his kindness.

I express my utmost admiration and gratefulness to my former manager Charles Varker (Dan Noble Fellow) for his mentorship in semiconductor reliability physics while working at Motorola. It is a rare occurrence that a manager selflessly mentors in a hectic business environment, and therefore I am entirely indebted to Charles. It was through many years of technical discussions with Charles that I gained expertise in the field of metallization reliability. This dissertation research topic was inspired by my discussions with Charles Varker.

While working at Freescale Semiconductor (formerly Motorola) there have been several colleagues that have directly helped me and provided insight in the course of this research that deserve recognition. First, I want to recognize Darrell Hill and Haldane Henry for the gold interconnect test structure design support. I am very grateful to Adolfo Reyes for fostering a genuinely helpful attitude in supplying GaAs wafers that were tested in this electromigration study.

I express my gratitude to Phil Williams for teaching me real world statistics and for his persistent guidance with statistical software programs. In the support of the gold film characterization and failure analysis work, I express my thanks to Jake Schaper, Troy Clare, and Jake Hammet. Special thanks are extended to John Euler of QualiTau for his guidance and assistance with the electromigration equipment. I especially appreciate my friend Nick Rivette for his encouragement and diligence in developing data analysis macros. I want to thank Dr. Bishnu Gogoi, Dr. Jerry Nivison, and Dr. Gil Speyer for their friendship and review of this dissertation.

It is very important that I recognize my previous academic graduate mentors at the University of Illinois. I am greatly indebted to Dr. Mike Machesky, my master's advisor, for his exceptional mentorship that developed my scientific foundation upon which this doctoral graduate research was possible. I also want to recognize Dr. Tom Holm for his significant influence and guidance in publishing, especially for introducing me to the reference management software (EndNote) that was a beneficial aid for citing references in this dissertation. During this research, I have had several helpful discussions with Dr. Jim Lloyd on the theory of electromigration, with Professor Rolf Hummel on Au electromigration, and with Professor Paul Kohl on Au electrodeposition.

Most importantly, I sincerely express my love and affection for Lisa who has provided encouragement, patience, and assistance during the arduous time writing this dissertation while working full-time. I want to also thank my parents from whom I have learned self-reliance in my academic endeavors. It should be emphasized that writing this dissertation would have been an entirely lonely venture if not for my furry and steadfast companion Cinder.

# **TABLE OF CONTENTS**

|                  |                                                  | Page |  |

|------------------|--------------------------------------------------|------|--|

| LIST OF TABLESix |                                                  |      |  |

| LIST OF FIGURES  |                                                  |      |  |

| CHAPTER 1        | INTRODUCTION                                     | 1    |  |

| 1.1              | Background and Motivation                        | 1    |  |

| 1.2              | Research Objectives                              | 4    |  |

| CHAPTER 2        | ELECTROMIGRATION THEORY AND REVIEW               | 6    |  |

| 2.1              | Electromigration Fundamentals and Theory         | 6    |  |

| 2.2              | Electromigration in Interconnects                | 11   |  |

|                  | 2.2.1 Microstructure and Geometric Effects       | 12   |  |

|                  | 2.2.2 Alloying and Metallization Advancements    | 18   |  |

|                  | 2.2.3 Reliability Measurement Methods            | 22   |  |

|                  | 2.2.4 Failure Kinetic Models                     | 25   |  |

| 2.3              | Properties and Application of Gold Metallization | 30   |  |

|                  | 2.3.1 Properties of Gold                         | 30   |  |

|                  | 2.3.2 Application of Gold Metallization          | 34   |  |

| 2.4              | Review of Electromigration in Gold Films         | 38   |  |

| 2.5              | Gold Electromigration Review Summary             | 54   |  |

| CHAPTER 3        | EXPERIMENTAL METHODS                             | 56   |  |

| 3.1              | Test Structure Design                            | 56   |  |

| 3.2              | Gold Interconnect Fabrication                    | 63   |  |

| 3.3              | Assembly and Packaging                           | 66   |  |

| 3.4              | Electromigration Test System                     | 70   |  |

| 3.5              | Test Procedures and Methods                      | 74   |  |

|           |                                                            | Page      |

|-----------|------------------------------------------------------------|-----------|

| 3.6       | Test Structure Cross-Sectional Measurements                | 81        |

| 3.7       | Experimental Test Conditions                               | 83        |

| 3.8       | Statistical Methods and Data Analysis                      | 86        |

| 3.9       | Summary of Experimental Methods                            | 92        |

| CHAPTER 4 | EXPERIMENTAL RESULTS                                       | 93        |

| 4.1       | Interconnect Resistance Measurements                       | 93        |

|           | 4.1.1 Metal 1 Test Structure Resistance                    | 93        |

|           | 4.1.2 Via1 / Metal 1 Test Structure Resistance             | 99        |

| 4.2       | Temperature Coefficient of Resistance and Film Temperature | ıre . 102 |

| 4.3       | Resistance Degradation                                     | 108       |

| 4.4       | Electromigration Lifetimes                                 | 112       |

|           | 4.4.1 Early Failures                                       | 112       |

|           | 4.4.2 Test Structure Lifetimes                             | 116       |

| 4.5       | Electromigration Activation Energy                         | 119       |

| 4.6       | Current Density Exponent                                   | 128       |

| 4.7       | Gold Structure Characterization                            | 132       |

|           | 4.7.1 Gold Microstructure Analysis                         | 132       |

|           | 4.7.2 Gold Chemical Analysis                               | 138       |

| 4.8       | Failure Analysis                                           | 139       |

| CHAPTER 5 | DISCUSSION AND ANALYSIS                                    | 146       |

| 5.1       | Structure Resistance Variation                             | 146       |

| 5.2       | Resistance Degradation Characteristics                     | 150       |

| 5.3       | Electromigration Activation Energy                         | 159       |

| 5.4       | Electromigration Current Density Exponent                  | 167       |

| Pag                                                   | age |

|-------------------------------------------------------|-----|

| HAPTER 6 CONCLUSIONS AND SUGGESTED FUTURE WORK 17     | 172 |

| 6.1 Summary of Electromigration in Gold Interconnects | 172 |

| 6.2 Future Research Suggestions                       | 175 |

| EFERENCES17                                           | 176 |

# LIST OF TABLES

| Table | Page                                                                                |

|-------|-------------------------------------------------------------------------------------|

|       | Chapter 2                                                                           |

| 2.1   | Atomic properties and crystal lattice of gold                                       |

| 2.2   | Physical properties of gold compared to other conductor metals 31                   |

| 2.3   | Standard electrode potentials for common metals                                     |

| 2.4   | Required properties for metallizations in ICs                                       |

| 2.5   | Summary of the solute effects on the Au film failure site                           |

| 2.6   | Au electromigration results for various experimental methods55                      |

|       | Chapter 3                                                                           |

| 3.1   | Experimental stress conditions for Au M1 test structures (phase V) 85               |

| 3.2   | Experimental stress conditions for Au V1M1 test structures (phase $\mathrm{V}$ ) 85 |

|       | Chapter 4                                                                           |

| 4.1   | Au M1 test structure reference resistances and TCRs 104                             |

| 4.2   | TCRs and film temperatures determined by both methods                               |

| 4.3   | Normalized current density median Au electromigration lifetimes 131                 |

| 4.4   | ICP-OES analysis for trace elements within electroplated Au film 138                |

|       | Chapter 5                                                                           |

| 5.1   | Normalized Au M1 structure resistance mean and standard deviation . 148             |

| 5.2   | Comparison of activation energies for Au electromigration                           |

| 5.3   | Observed activation energies for various diffusion mechanisms 166                   |

| 5.4   | Comparison of current density exponents for Au electromigration 171                 |

# LIST OF FIGURES

| Figure    | Page                                                                         |  |

|-----------|------------------------------------------------------------------------------|--|

| Chapter 1 |                                                                              |  |

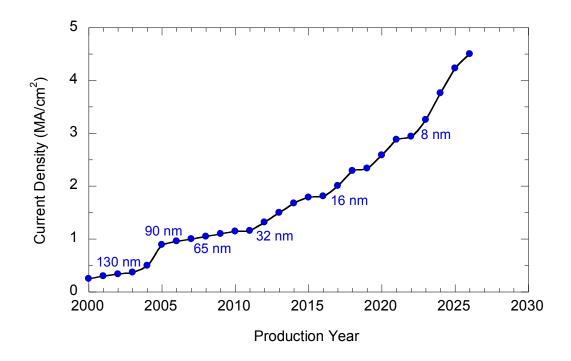

| 1.1       | Operational current density trend for advancing technology nodes2            |  |

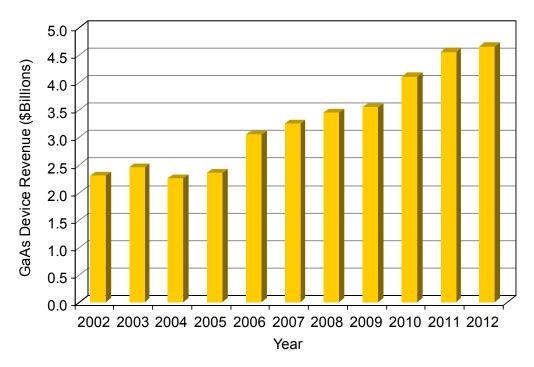

| 1.2       | Market revenue growth for GaAs devices                                       |  |

|           | Chapter 2                                                                    |  |

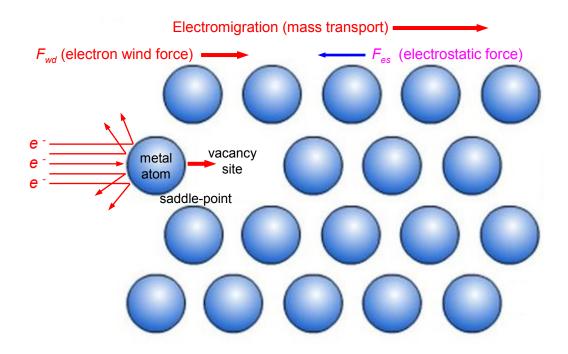

| 2.1       | Electric field forces acting upon metal atoms in a crystal lattice           |  |

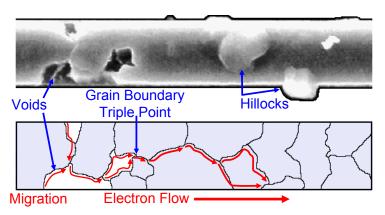

| 2.2       | Flux divergence at grain boundary triple points                              |  |

| 2.3       | Bamboo grained microstructure interconnect                                   |  |

| 2.4       | Blech length effect demonstrated on AI thin film segments                    |  |

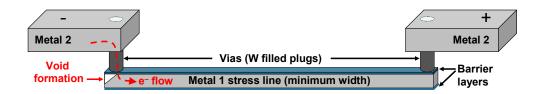

| 2.5       | Flux divergence at the W via / Al interconnect interface                     |  |

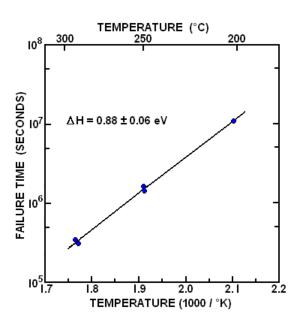

| 2.6       | Huntington and Grone's Au marker motion (v / J) versus 1 / T graph 39        |  |

| 2.7       | Gangulee and d'Heurle's failure times versus inverse temperature 42          |  |

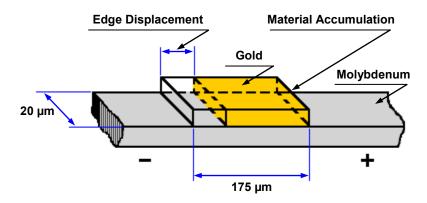

| 2.8       | Blech and Kinsbron's Au thin film structure configuration                    |  |

|           | Chapter 3                                                                    |  |

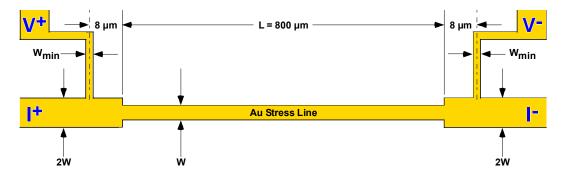

| 3.1       | NIST electromigration test structure schematic                               |  |

| 3.2       | A two-level metal via electromigration test structure illustration 58        |  |

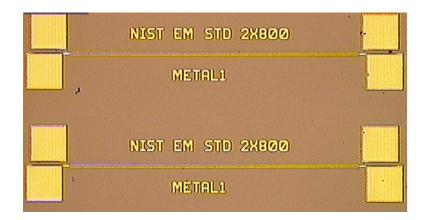

| 3.3       | Dual NIST line (2 μm wide by 800 μm long) test structures59                  |  |

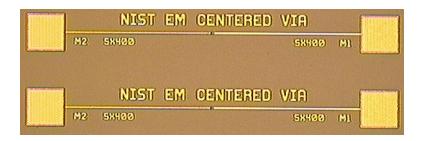

| 3.4       | Dual centered via (metal 1 / metal 2) test structures 60                     |  |

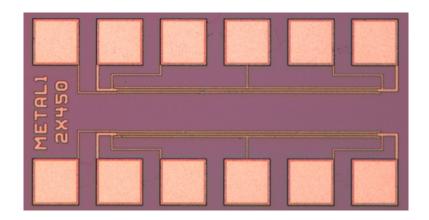

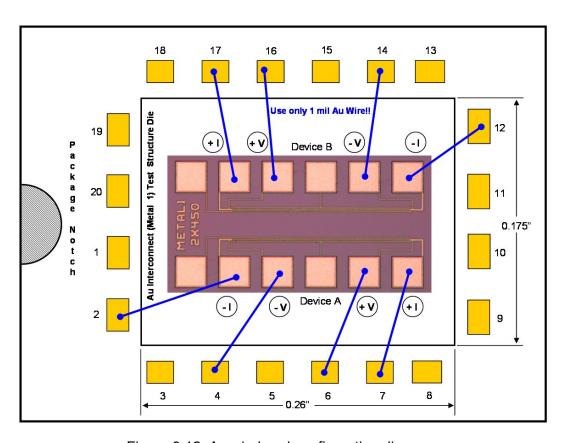

| 3.5       | Metal 1 line (2 μm wide by 450 μm long) test structure design 61             |  |

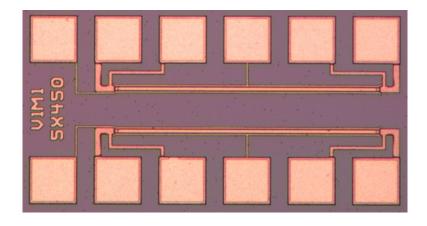

| 3.6       | Via1 / Metal 1 (5 $\mu$ m wide by 450 $\mu$ m long) test structure design 61 |  |

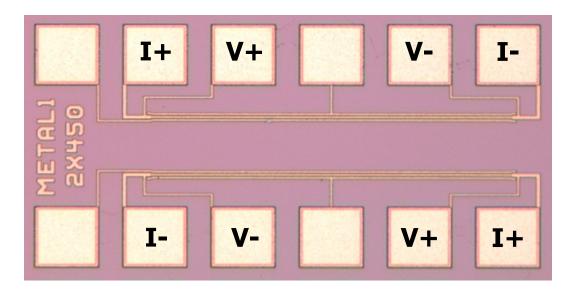

| 3.7       | Kelvin sensed test structure layout configuration 62                         |  |

| 3.8       | Semitool Equinox gold plating tool64                                         |  |

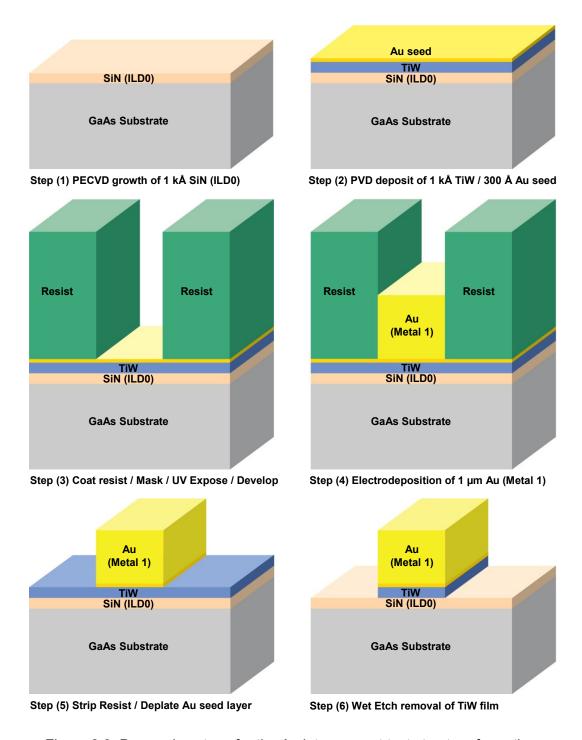

| 3.9       | Processing steps for the Au interconnect test structure formation 65         |  |

| Figure |                                                                                     | Page |

|--------|-------------------------------------------------------------------------------------|------|

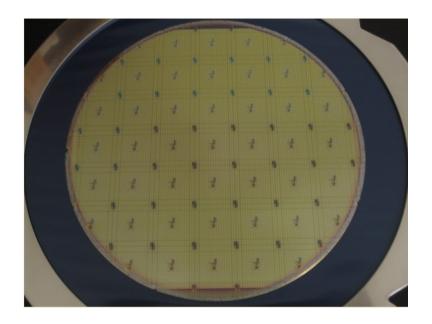

| 3.10   | Sawn GaAs wafer mounted on UV tape                                                  | 67   |

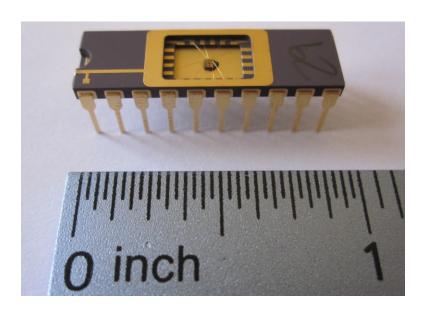

| 3.11   | Ceramic side-brazed 20-pin dual in-line package                                     | 68   |

| 3.12   | Au wirebond configuration diagram                                                   | 69   |

| 3.13   | QualiTau MIRA electromigration test systems                                         | 70   |

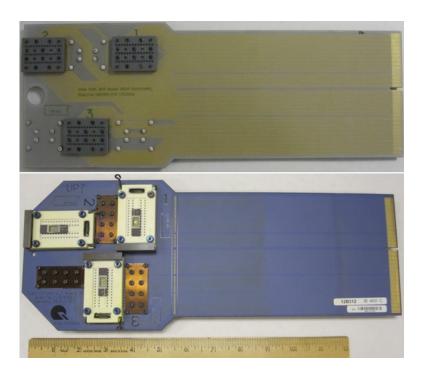

| 3.14   | Oven socket boards (350°C board above / 400°C board below)                          | 71   |

| 3.15   | Oven socket boards loaded into oven backplane                                       | 72   |

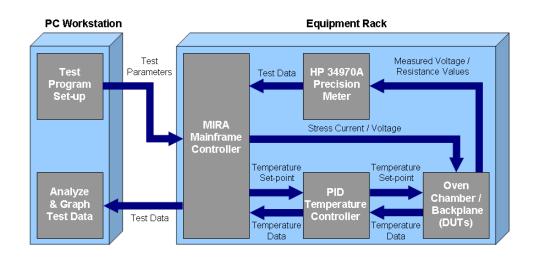

| 3.16   | QualiTau test system architecture block diagram                                     | 73   |

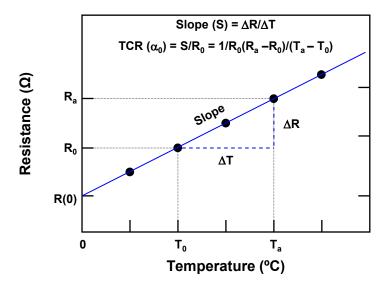

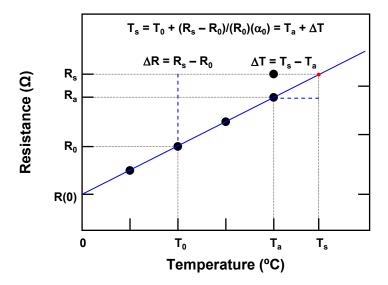

| 3.17   | Standard method for TCR determination                                               | 77   |

| 3.18   | Standard method for Joule-heated temperature determination                          | 78   |

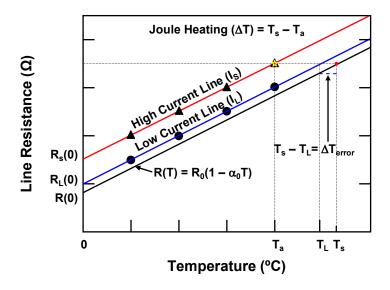

| 3.19   | Two-current method for Joule-heated temperature determination                       | 79   |

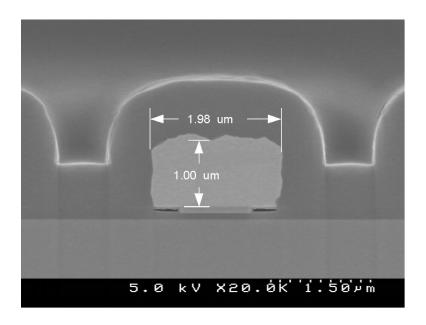

| 3.20   | Au M1 test structure line-width and thickness measurements                          | 81   |

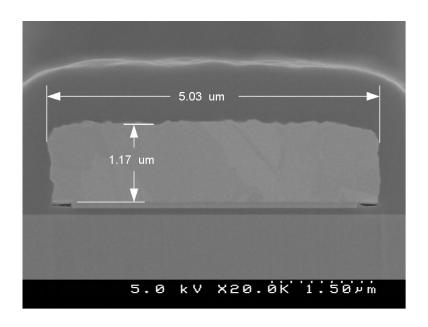

| 3.21   | Au V1M1 test structure line-width and thickness measurements                        | 82   |

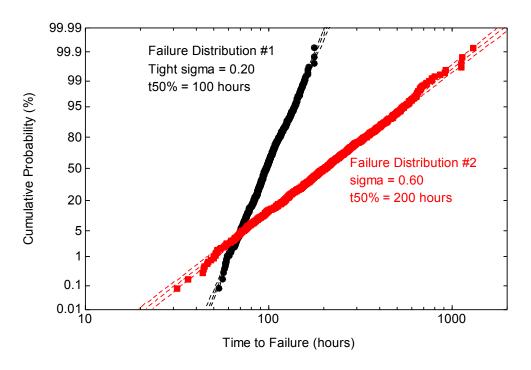

| 3.22   | Log-normal failure distributions with different sigma and $\it t_{\rm 50\%}$ values | 88   |

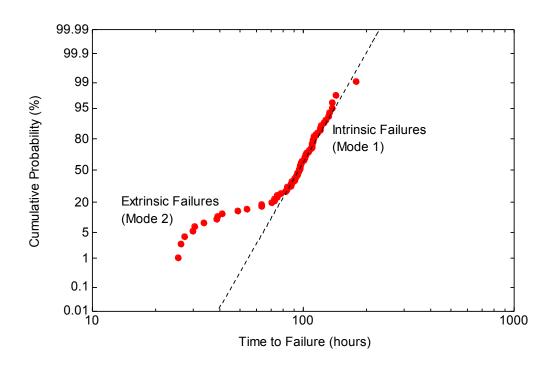

| 3.23   | Bi-modal failure distribution with intrinsic and extrinsic failure modes.           | 89   |

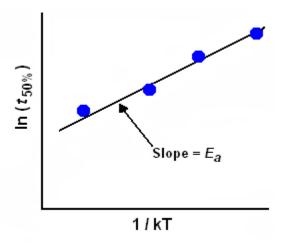

| 3.24   | $ln(t_{50\%})$ versus 1/kT data graph for extracting $E_a$ parameter                | 90   |

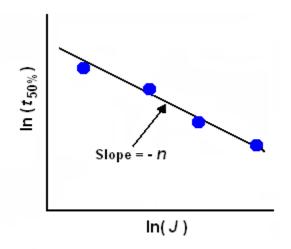

| 3.25   | $ln(t_{50\%})$ versus $ln(J)$ data graph for extracting $n$ parameter               | 91   |

|        | Chapter 4                                                                           |      |

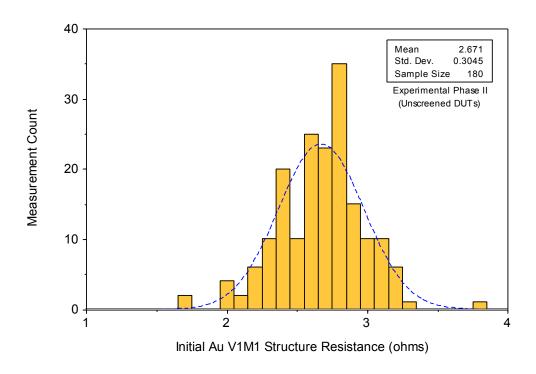

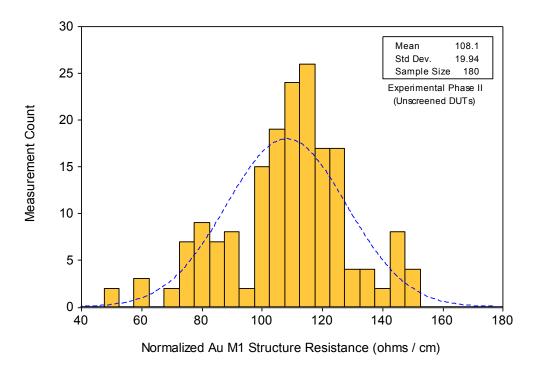

| 4.1    | Initial Au M1 test structure resistance distribution (phase II)                     | 94   |

| 4.2    | Screened Au M1 test structure resistance distribution (phase II)                    | 95   |

| 4.3    | Initial Au M1 test structure resistance distribution (phase V)                      | 96   |

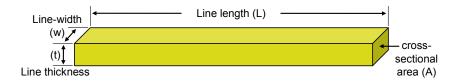

| 4.4    | Illustration of metal interconnect line structure dimensions                        | 97   |

| 4.5    | Initial Au V1M1 test structure resistance distribution (phase II)                   | 99   |

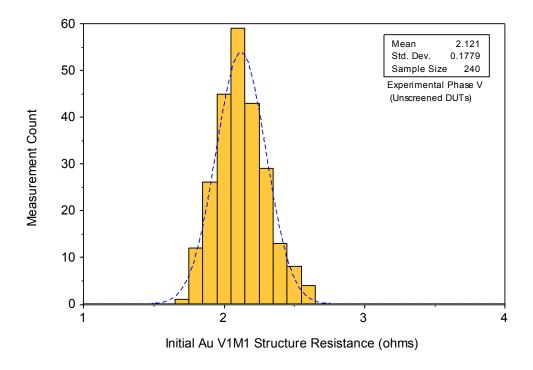

| 4.6    | Initial Au V1M1 test structure resistance distribution (phase V)                    | 100  |

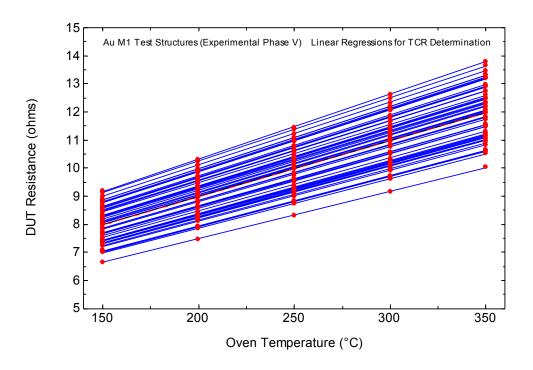

| 4.7    | Au M1 structure resistance versus oven temperature (phase V)                        | 102  |

| Figure | Page                                                                                        |

|--------|---------------------------------------------------------------------------------------------|

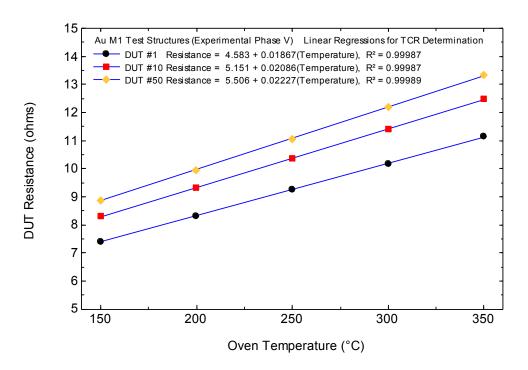

| 4.8    | Au M1 (DUTs #1, 10, & 50) structure resistance versus temperature 103                       |

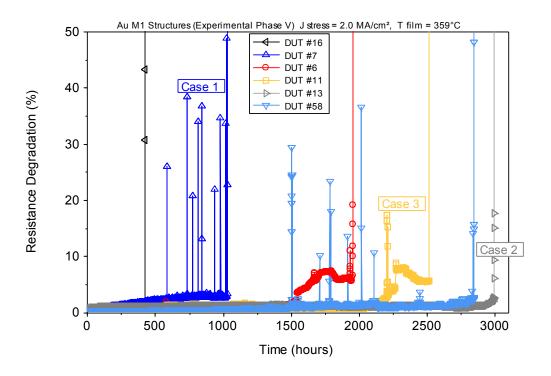

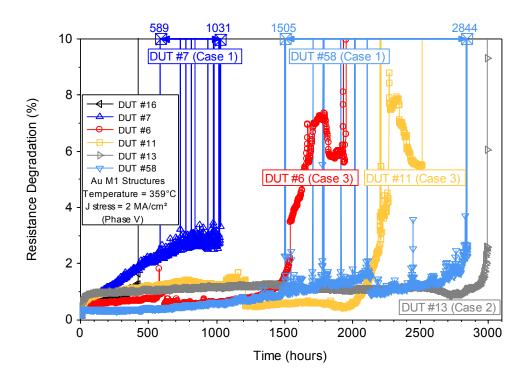

| 4.9    | Resistance degradation of Au M1 structures during electromigration 109                      |

| 4.10   | Resistance degradation of Au M1 structures with 10% scaled graph 111                        |

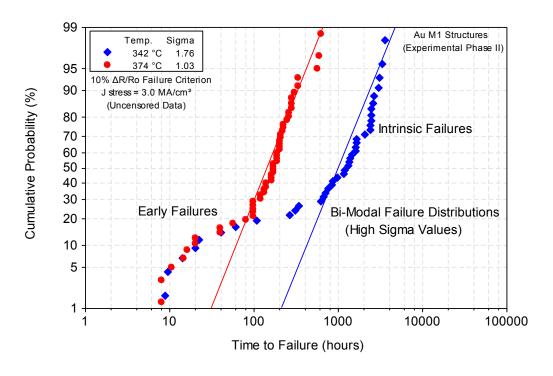

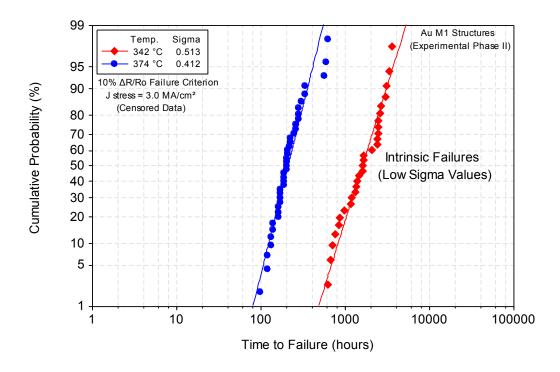

| 4.11   | Au electromigration lifetimes with a 10% failure criterion                                  |

| 4.12   | Intrinsic failure distributions after removal of early failures 114                         |

| 4.13   | Au electromigration lifetimes with a 50% failure criterion                                  |

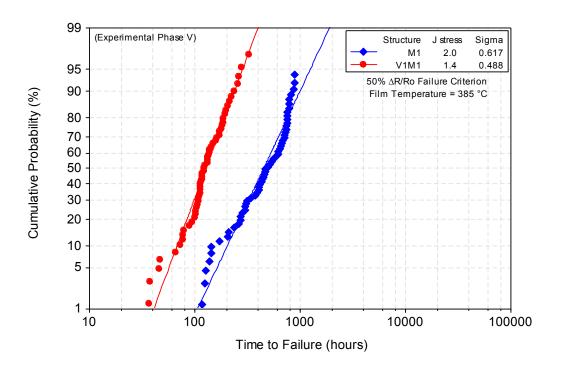

| 4.14   | Au M1 and V1M1 test structure electromigration lifetimes                                    |

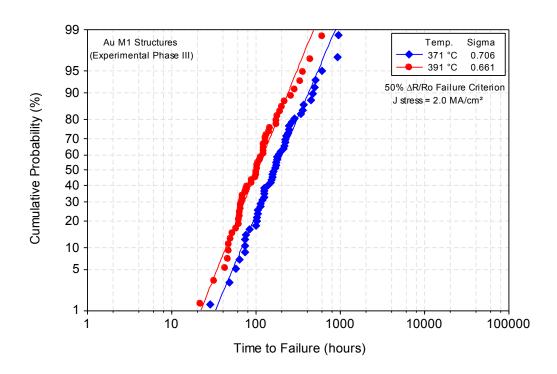

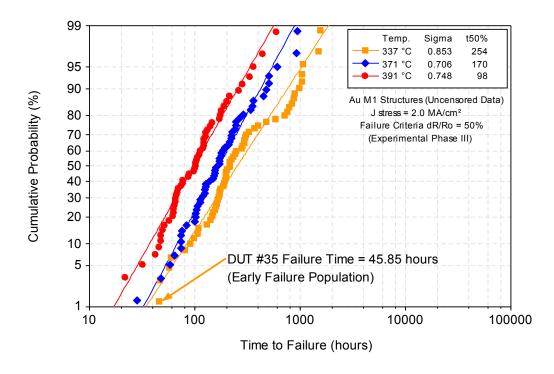

| 4.15   | Electromigration lifetimes for the Au M1 structures (phase III)                             |

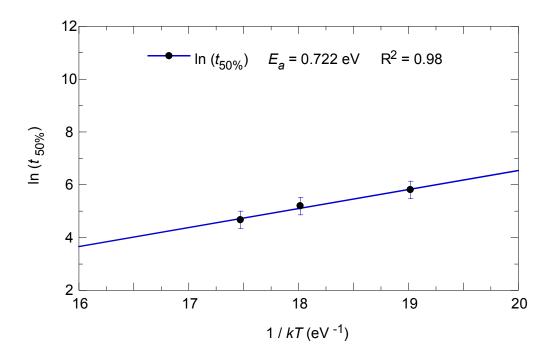

| 4.16   | Arrhenius plot of median Au M1 electromigration lifetimes (phase III) 121                   |

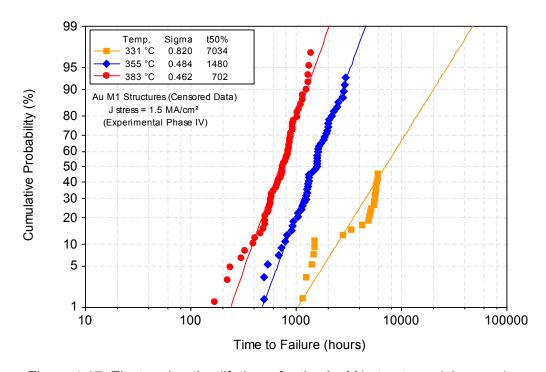

| 4.17   | Electromigration lifetimes for the Au M1 structures (phase IV)                              |

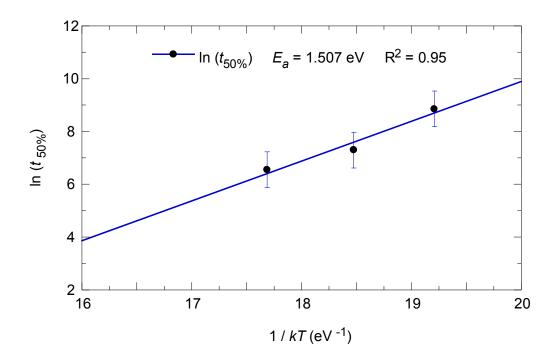

| 4.18   | Arrhenius plot of median Au M1 electromigration lifetimes (phase $\operatorname{IV})$ . 123 |

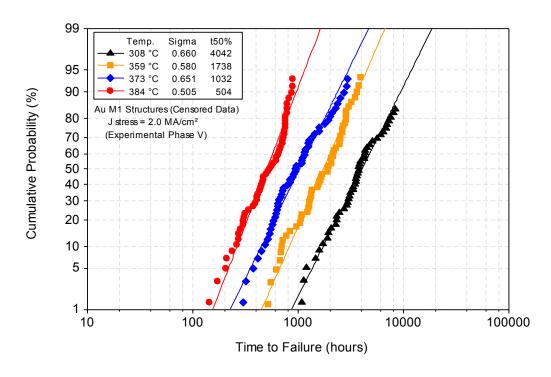

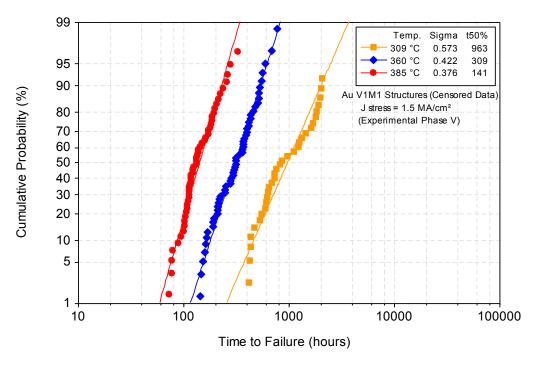

| 4.19   | Electromigration lifetimes for the Au M1 structures (phase V)                               |

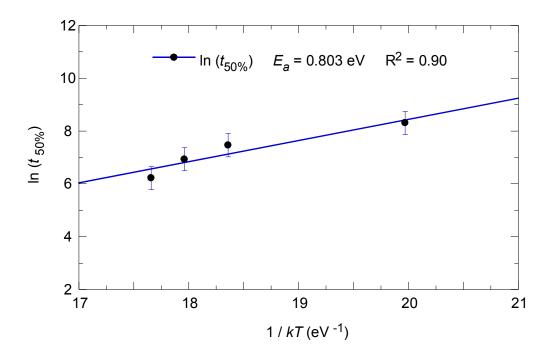

| 4.20   | Arrhenius plot of median Au M1 electromigration lifetimes (phase $\mathrm{V})125$           |

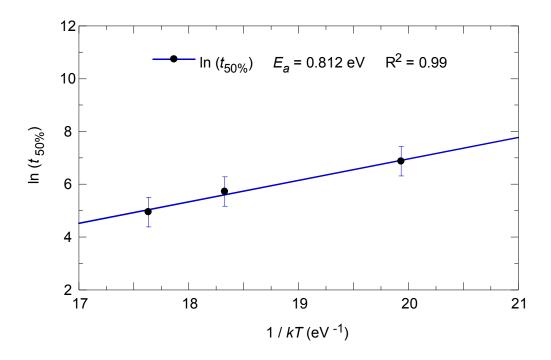

| 4.21   | Electromigration lifetimes for the Au V1M1 structures (phase V) 126                         |

| 4.22   | Arrhenius plot of median V1M1 electromigration lifetimes (phase $\mathrm{V}$ ) 127          |

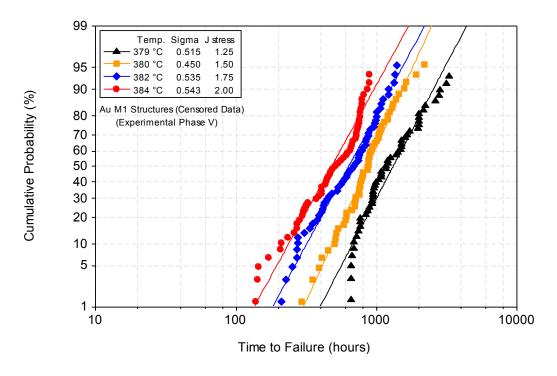

| 4.23   | Electromigration lifetimes for the Au M1 structures at different <i>J</i> 129               |

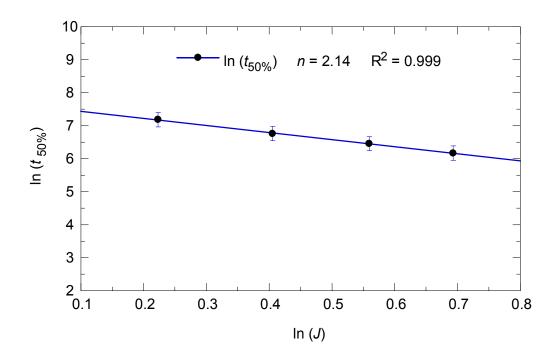

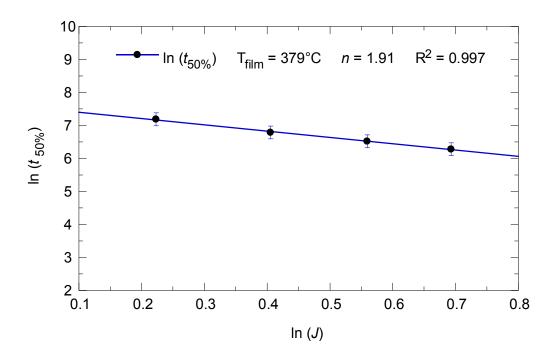

| 4.24   | In $(t_{50\%})$ versus In $(J)$ plot for non-normalized Au M1 median lifetimes 130          |

| 4.25   | In $(t_{50\%})$ versus In $(J)$ plot for normalized Au M1 median lifetimes 131              |

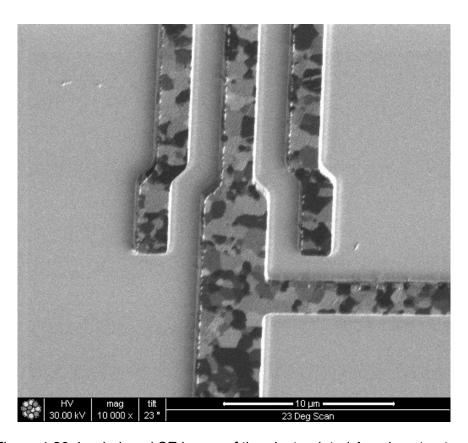

| 4.26   | Ion-induced SE image of the electroplated Au microstructure                                 |

| 4.27   | Lineal intercept method applied on the Au microstructure                                    |

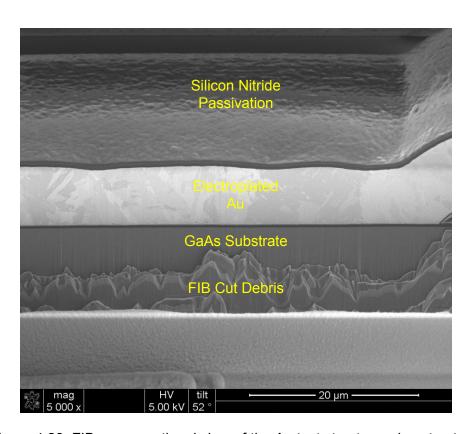

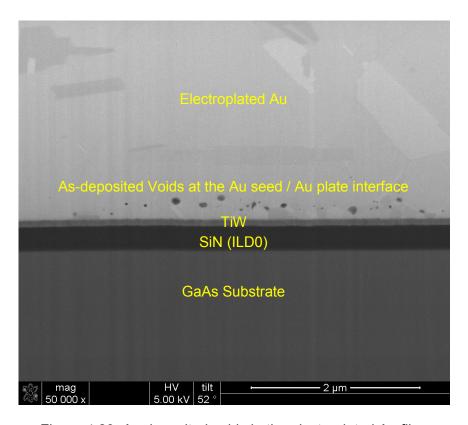

| 4.28   | FIB cross-sectional view of the Au test structure microstructure 136                        |

| 4.29   | As-deposited voids in the electroplated Au film                                             |

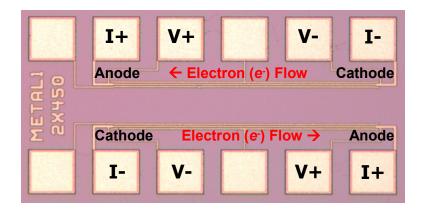

| 4.30   | Electron current flow direction on the Au M1 structures                                     |

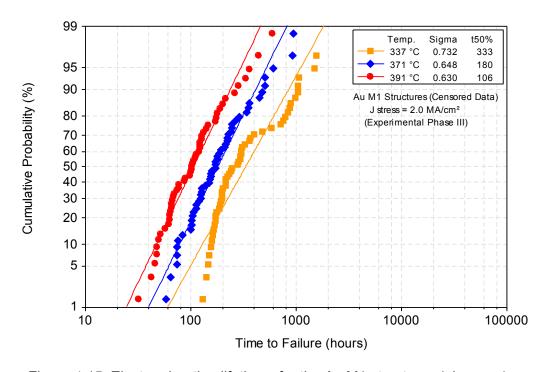

| 4.31   | Uncensored failure time data for the Au M1 structures (phase III) 140                       |

| Figure | Page                                                                       |

|--------|----------------------------------------------------------------------------|

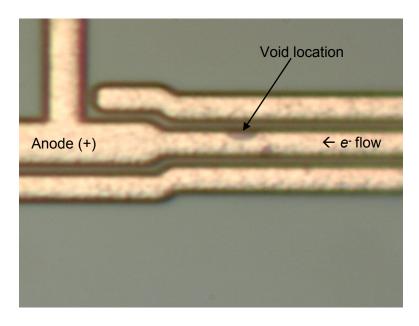

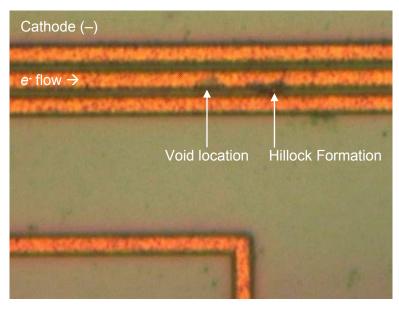

| 4.32   | Optical image of the early failure void location 141                       |

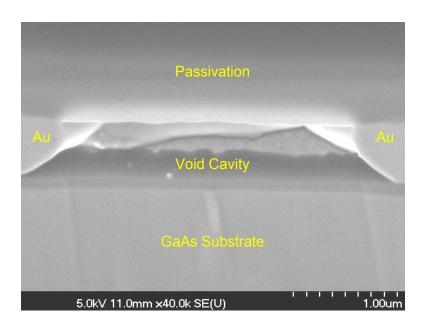

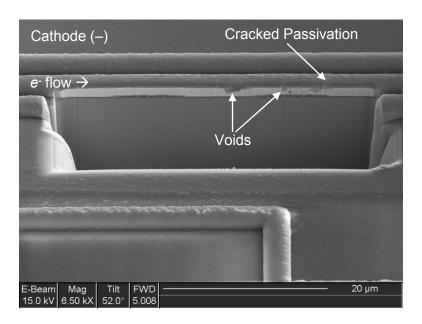

| 4.33   | SEM cross-sectional view of the early failure void                         |

| 4.34   | Optical image of a typical Au M1 electromigration failure void             |

| 4.35   | SEM image of typical Au electromigration-induced voids                     |

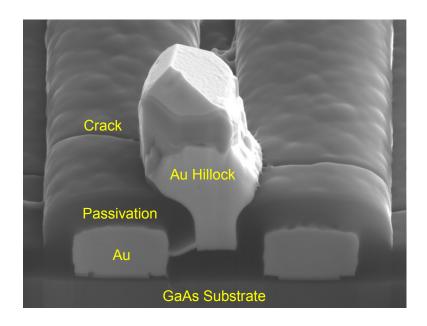

| 4.36   | SEM image of a large Au hillock formation                                  |

|        | Chapter 5                                                                  |

| 5.1    | Normalized Au M1 test structure resistance distribution (phase II) 147     |

| 5.2    | Normalized Au M1 test structure resistance distribution (phase V) 148      |

| 5.3    | Initial Au M1 structure resistance versus electromigration lifetime 149    |

| 5.4    | Au electromigration failure distributions with a 10% failure criterion 151 |

| 5.5    | Au M1 structure resistance traces scaled on a 10% $\Delta R/R_o$ graph 152 |

| 5.6    | Voltage (resistance) spikes for Al during electromigration testing 154     |

| 5.7    | Electromigration resistance characteristics of Cu interconnects 155        |

| 5.8    | As-deposited voids in the electroplated Au film                            |

| 5.9    | Au M1 structure early failure void location at the anode end 157           |

| 5.10   | SEM cross-sectional view of Au M1 structure early failure void 158         |

| 5.11   | Electromigration lifetimes for the Au M1 structures (phase V)              |

| 5.12   | Arrhenius plot of median Au M1 electromigration lifetimes (phase V) 163    |

| 5.13   | Electromigration lifetimes for the Au M1 structures at different J 169     |

| 5.14   | Natural logarithm of Au M1 median lifetimes versus current density 170     |

### CHAPTER 1 INTRODUCTION

In this chapter, the background of semiconductor microelectronics and the demand on integrated circuits in terms of performance and current density are reviewed. The significance of electromigration reliability for microelectronic interconnects is discussed along with a brief review of the expanding market for compound semiconductors. This chapter concludes with the defined research objectives for this dissertation.

### 1.1 Background and Motivation

Ever since the invention of the solid state bipolar transistor by Bardeen, Brattain, and Shockley at Bell Labs in 1947, semiconductor electronics have rapidly advanced in response to the proliferation of modern technology. A continuous increase in microelectronic integrated circuit (IC) complexity and density through miniaturization of device dimensions has enabled integration of over a billion transistors onto a single semiconductor microchip. This miniaturization scaling trend has produced higher performance ICs operating at increased power loads and elevated temperatures, thus posing material reliability challenges. As a result of ICs shrinking, metal interconnects have decreased in both line-width and thickness, causing resistance and current densities of the interconnections to substantially increase. Figure 1.1 exhibits the operational current density increase due to reduced interconnect dimensions, corresponding to the advancing technology generations (nodes). With higher current densities, Joule heating increases metal interconnect film temperatures hastening electromigration failures to be the predominant reliability hazard for ICs.

Figure 1.1 Operational current density trend for advancing technology nodes.

Electromigration in metal interconnects is the most pernicious failure mechanism in semiconductor ICs. A notorious example was an interrupted space mission launch at Cape Canaveral caused by the electromigration failure of a microelectronic chip inside the onboard computer, costing taxpayers 1.5 million dollars.<sup>2</sup> All semiconductor companies employ scientists and engineers to evaluate and monitor electromigration reliability of interconnect metallizations. Early electromigration investigations were focused primarily on aluminum interconnects for silicon-based ICs. Development of high-power radio frequency (RF) compound semiconductor devices that operate at higher current densities and elevated metal film temperatures required an alternative metallization that is compatible with GaAs substrates and improved electromigration reliability.

Gold-based metallization was implemented on GaAs devices because it uniquely forms a very low resistance ohmic contact and gold interconnects have superior electrical and thermal conductivity properties. Gold (Au) was also believed to have improved resistance to electromigration due to its higher melting point, yet electromigration reliability results on passivated electroplated Au interconnects are scarce and inadequate in the literature. The impetus for Aubased metallization used for interconnects (transmission-lines) in GaAs devices originated due to the formation of superior ohmic contacts, yet improved electromigration reliability was expected. However, more precisely controlled and statistically rigorous investigations are needed to quantify electromigration lifetimes of Au interconnects. The fast growth of the GaAs device market has motivated obtaining accurate Au electromigration model parameters for lifetime predictions. Figure 1.2 displays the growth of the GaAs market revenue.<sup>3</sup>

Figure 1.2 Market revenue growth for GaAs devices.

## 1.2 Research Objectives

The primary objective of this doctoral research was to investigate electromigration reliability of passivated electroplated Au thin film interconnects utilizing high-resolution in-situ resistance monitoring equipment. This research study applied precisely controlled stress conditions and statistically rigorous sample size experiments to determine accurate activation energies and current density exponents for Au interconnects. These electromigration model parameters were derived from log-normal based statistics and extracted from linear regressions of the Arrhenius and inverse relationships on natural log plots. The applicability of Black's empirical model was evaluated through the results of this investigation. Another objective was characterization of the electroplated gold test structure resistance, microstructure, and failure analysis of the electromigration wear-out mechanisms that caused the interconnect failures. In order to accomplish these objectives, successive experimental phases (I - V) were conducted to optimize both test structure design and experimental stress conditions.

This dissertation is organized into six chapters. Chapter 1 provides a brief motivation and background, along with the research objectives for electromigration in gold interconnects. Chapter 2 reviews the fundamental theory of electromigration, and the various effects, measurement methods, and models of electromigration in interconnects. Pertinent properties of gold that are essential to its use in microelectronic applications are succinctly given. This chapter concludes with a comprehensive review and critique of previous research investigations on electromigration in gold films.

Chapter 3 describes the experimental procedures and methods undertaken in this doctoral research. Full details on the test structure design, processing of the film layers, and the package assembly steps are specified. The electromigration test equipment, procedures, and experimental stress conditions as well as the data analysis methods are outlined. Chapter 4 presents the experimental results and data collected in this doctoral research. The measurement data of the resistance, film stress temperature, and degradation of the gold interconnects is presented. The electromigration failure lifetimes of gold interconnects as a function of temperature and current density are presented and used in the determination of the activation energy and current density exponent Characterization of the microstructure and electromigrationparameters. inducted void formation of the gold interconnects are also described. Chapter 5 contains discussion and analysis of the experimental results. Interpretation of early failures and comparison with previous investigations is also discussed. Chapter 6 summarizes and concludes the main results of this doctoral research along with suggestions for future work.

#### CHAPTER 2 ELECTROMIGRATION THEORY AND REVIEW

In this chapter, the basic theory and fundamental aspects of electromigration in metals are reviewed. The significance of electromigration as it pertains to the reliability of integrated circuit interconnects, as well as the pivotal advancements in the microelectronics manufacturing processes for inhibiting failures and improving metallization lifetimes are discussed. Gold thin film properties and applications in microelectronics are presented. In the final section, a comprehensive review of previous investigations into electromigration in gold thin films is summarized.

## 2.1 <u>Electromigration Fundamentals and Theory</u>

Electromigration is a phenomenon characterized by mass transport of metal atoms (or ions) under the influence of charge carriers (electrons) when an electric field is applied. This forced mass transport phenomenon was first observed in 1861 by Geradin, who discovered that molten alloys subjected to direct electric current showed segregation of its components. The first attempt to describe electromigration physically is attributed to Skaupy in 1914, who suggested the importance of the interaction between the metal atoms and the moving electrons. It was many years later in 1953, when two German scientists Seith and Wever conducted the first systematic experiments to measure the mass transport of Hume-Rothery alloys. This work was the first evidence for the driving force of electromigration. These marker motion experiments revealed that the driving force for electromigration was not solely influenced by the electrostatic force from the applied electric field, but also strongly depended on

the direction of motion of the electrons.<sup>4</sup> As a result of these empirical observations, Seith conceptualized that flowing electrons transferred momentum to atoms causing mass transport. This prompted a reemergence of the idea originated by Skaupy of "electron wind" as the driving force for electromigration. The idea of the "electron wind" as a momentum transfer driving force causing mass transport in metals subjected to an electric field established the theoretical foundation for electromigration.

Shortly following this theoretical development, mathematical formulations for the electromigration driving forces were derived by Fiks<sup>5</sup> in 1959 and Huntington and Grone<sup>6</sup> in 1961. Their electromigration driving force model was formulated from a semi-classical ballistic approach to explain the collision of the charge carriers with the metal ions to induce mass transport. According to this ballistic model, the electromigration driving force ( $F_{em}$ ) is composed of two distinct contributions. The first component arises from the interaction of the electric field on the charge of the migrating ion known as the direct electrostatic force ( $F_{es}$ ). The second component is due to the momentum transfer from flowing conduction electrons colliding with the metal ions, and is called the electron wind force ( $F_{wd}$ ). Therefore, the total effective electromigration driving force is expressed as

$$F_{em} = F_{es} + F_{wd} = (Z_{es} + Z_{wd})eE = Z_{eff}^*eE,$$

(2.1)

where  $Z_{es}$  is the charge number of the metal ion,  $Z_{wd}$  the charge number corresponding to the electron wind, e is the electronic charge, and E is the electric field. Combining the charge numbers yields the effective charge number  $Z_{eff}^*$  which is dimensionless and ranges<sup>7</sup> in value from  $10^{-1}$  to  $10^2$ .

Electromigration is basically a diffusion process under a driving force. Viewed microscopically, electromigration is a directed bias on the diffusive motion of metal atoms within a crystal lattice. Metal atoms vibrate within a crystal lattice due to thermal energy that allows atoms to diffuse (jump) out of the equilibrium lattice position to a saddle-point (halfway) position. During the process of an atomic jump out of the lattice equilibrium position under influence of the electromigration driving force, a metal atom in the saddle-point is impacted by a large number of electrons. In this manner, the momentum transfer biases the atomic jump in the direction of the electron flow.<sup>8</sup> Thus, the electromigration driving force generates mass transport of metal atoms and atomic diffusion in the direction of the electron wind. Figure 2.1 depicts the electric field forces that are acting upon metal atoms in a crystal lattice.

Figure 2.1 Electric field forces acting upon metal atoms in a crystal lattice.

The  $F_{\rm es}$  force due to the interaction between the ionic core of the atoms and the electric field is directed toward the negative electrode terminal and is not strongly dependent on the temperature. For most metals, the  $F_{\rm es}$  force is negligible in comparison to the  $F_{\rm wd}$  force that is acting in the opposite direction toward the positive terminal. This electron wind force has been reported to be an order of magnitude greater than the electrostatic force for gold, copper and aluminum. The portrayal of electromigration in Figure 2.1 is based on vacancy diffusion as the dominant mechanism in a metal lattice. However, it should be noted that similar biased atomic diffusive motion under an electric field occurs more predominantly at grain boundaries and interfaces in thin metal films. More details on these physical mechanisms are discussed later in this chapter.

The electromigration driving force creates an atomic flux  $(J_a)$  in the direction of the electron wind described by

$$J_a = N\mu F_{em}, (2.2)$$

where N is the atomic density and  $\mu$  is the atomic mobility. Substituting the electromigration driving force from Equation (2.1) into Equation (2.2), and expressing the electric field as the product of the current density (J) and the metal resistivity ( $\rho$ ), yields the following

$$J_a = N\mu Z_{\text{eff}}^* eE = N\mu Z_{\text{eff}}^* e\rho J. \tag{2.3}$$

According to the Einstein relation, the atomic mobility can be expressed in terms of the diffusion coefficient by

$$\mu = \frac{D}{kT},\tag{2.4}$$

where D is the diffusion coefficient for metal atoms, k is Boltzmann's constant, and T is the absolute temperature.

Substituting the Einstein relation for the atomic mobility into Equation (2.3), the atomic flux becomes

$$J_{a} = N \left(\frac{D}{kT}\right) Z_{\text{eff}}^{*} e \rho J. \tag{2.5}$$

Equation (2.5) can be expressed in terms of the metal ion drift velocity ( $v_d$ ) using the relationship  $v_d = \mu F_{em}$ . Inserting this relationship into Equation (2.5), and solving for the metal ion drift velocity, the expression converts to

$$V_d = \left(\frac{D}{kT}\right) Z_{\text{eff}}^* e \rho J. \tag{2.6}$$

In bulk metals such as metal wires (compared to thin metal films on insulating silicon substrates) applied electrical currents produce significant Joule heating, since thermal dissipation is considerably lower. Even at much lower current densities near 10<sup>4</sup> amps / cm<sup>2</sup>, bulk metals generate extremely elevated temperatures where electromigration wear-out is more rapid. Since electromigration is strongly temperature dependent, it is important to examine the diffusion coefficient relationship expressed as

$$D = D_0 \exp\left(-\frac{E_a}{kT}\right), \tag{2.7}$$

where  $D_o$  is the maximum diffusion coefficient at infinite temperature, and  $E_a$  is the activation energy for the diffusion process. Rearranging and substituting into Equation (2.6), the drift velocity equation becomes

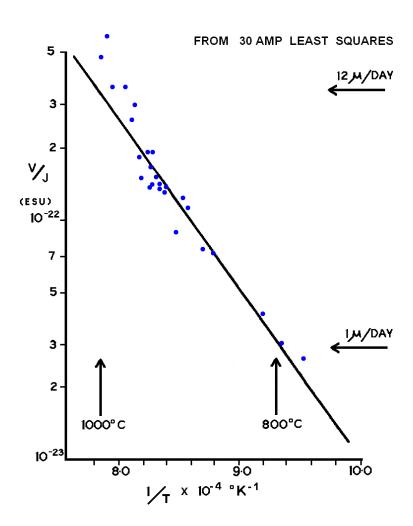

$$\left(\frac{v_d}{J}\right) = Z_{\text{eff}}^* e \rho \left(\frac{D_o}{kT}\right) \exp\left(-\frac{E_a}{kT}\right). \tag{2.8}$$

By plotting the natural logarithm of  $(v_d / J)$  versus the reciprocal of temperature, the electromigration  $E_a$  parameter can be obtained from experimental data.

## 2.2 Electromigration in Interconnects

Early experimentation on the electromigration phenomenon focused on diffusion in bulk metals. 6, 10 It was not until the late 1960's that research efforts abruptly changed focus due to observations that electromigration was the primary metallization wear-out failure mechanism for aluminum interconnects in integrated circuits (ICs). 11, 12 These observed electromigration failures threatened to halt microelectronic IC production and were initially referred to as the "cracked stripe" problem, since void growth extended across the metal lines causing electrical opens. Although the pernicious effect of electromigration was known for several years in bulk metals at higher temperatures, it came as a severe shock that IC thin film metal interconnects were susceptible to electromigration failures at much lower temperatures.

Explanation for this observed discrepancy is attributed to the distinguishing characteristics of thin metal films compared to bulk metals. Because IC thin metal interconnects are deposited on insulating silicon dioxide (SiO<sub>2</sub>) layers on silicon (Si) substrates that provide effective thermal conductivity for current-induced heat dissipation, significantly higher current densities can be attained while maintaining much lower film temperatures than allowed in bulk metal wires. Moreover, early IC aluminum interconnects were typically 1 to 2  $\mu$ m thick and 5 to 10  $\mu$ m wide, creating a large surface to volume ratio that promotes heat dissipation. Another characteristic of IC thin metal films is the fine grained polycrystalline microstructures that are formed by the evaporation deposition method. As a consequence of subjecting IC thin metal interconnects to current densities above  $10^6$  amps / cm², the electromigration damage phenomena and the preponderant role of grain boundary diffusion became evident.

### 2.2.1 Microstructure and Geometric Effects

Although electromigration in interconnects occurs as a combination of several different diffusion mechanisms including lattice, grain boundary, and interface, it has been found that grain boundary diffusion is the dominant pathway for mass transport. This is especially true in the case of thin metal interconnects composed of small-grained microstructures, which enables diffusion to occur rapidly along the abundant supply of grain boundaries. Electromigration failures in interconnects are caused either by void formation leading to open circuits or hillock extrusions leading to short circuits. Both of these electromigration failures are due to atomic flux divergence sites where more mass is transported out of a region (void) or where more mass is entering a region (hillock). Grain boundaries are a preferred nucleation site for voids and hillocks because flux divergence occurs in the junction of three grain boundaries. This junction is known as a grain boundary triple point. At these locations, more mass can be migrated along two grain boundaries leaving from a single grain boundary which causes localized mass depletion (voids).<sup>2</sup> Figure 2.2 illustrates a polycrystalline metal interconnect containing grain boundary triple points, where atomic flux divergence occurs leading to void and hillock formation.

Figure 2.2 Flux divergence at grain boundary triple points.

Numerous studies have carried out experimental work on grain boundary effects and geometric considerations for IC interconnect reliability. The results of the initial studies<sup>13-16</sup> showed that the activation energy of the mass transport for aluminum interconnects was in the range of 0.5 to 0.7 eV. In this activation energy range, the dominant mode of mass transport was determined to be grain boundary diffusion, since lattice diffusion exhibited at higher temperatures yields much larger  $E_a$  values<sup>10</sup> on the order of 1.4 eV. The significant influence of grain boundaries on the electromigration mechanism in interconnects necessitates a modification to the atomic flux expression in Equation (2.5). For ideal grain microstructures of equiaxed texture,<sup>4</sup> the atomic flux is represented by

$$J_{a} = N_{GB} \left( \frac{D_{GB}}{kT} \right) \left( \frac{\delta}{d} \right) Z_{GB}^{*} e \rho J, \qquad (2.9)$$

where  $\delta$  is the effective boundary width for mass transport, d is the average grain size, and GB subscripted parameters denote grain boundary diffusion.

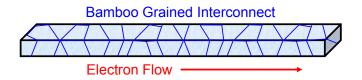

Since grain boundaries supply rapid pathways for atomic diffusion, efforts were taken to manipulate the grain size and microstructure of interconnects. It has been demonstrated that single crystal aluminum thin film conductors inhibit electromigration damage under current density and temperature conditions that would cause polycrystalline interconnects to fail. However, depositing single crystal interconnects in a high-volume manufacturing environment is not practical, whereas producing large grain microstructures by annealing films is manufacturable. Narrow line-width interconnects with recrystallized large metal grain sizes produce "bamboo-like" microstructures, where almost all grain boundaries are perpendicular to the current flow in the conducting line. Bamboo grained interconnects lack continuous grain boundaries that are parallel to the

electron flow, and therefore mass transport along these rapid diffusion pathways is blocked. A representation of a bamboo grained microstructure interconnect is shown in Figure 2.3. These bamboo grained microstructures have been found to be effective in improving the electromigration lifetimes of interconnects. Although bamboo microstructures improve interconnect lifetimes, electromigration failures still occur at the sparsely available grain boundary triple points and edge surfaces.

Figure 2.3 Bamboo grained microstructure interconnect.

An added enhancement for improving electromigration lifetimes of Al interconnects was discovered through the use of protective overcoating (passivation) layers. Deposition of  $SiO_2$  or phosphosilicate glass ( $P_2O_5$  -  $SiO_2$ ) passivation layers over Al interconnects were shown to improve electromigration lifetime by one to two orders of magnitude.<sup>21, 22</sup> Yet the reported high activation energy of 1.2 eV was rationalized as a reduction in surface diffusion. Conversely, another study did not observe this higher activation energy<sup>15</sup> and considered the reduced surface diffusion argument invalid, because grain boundary diffusion at nearly the same activation energy would still be dominant. A more recent explanation for increased lifetimes is that the restraining  $SiO_2$  passivation enables higher compressive stresses on the Al film, which retards electromigration and hillock extrusions.<sup>23</sup>

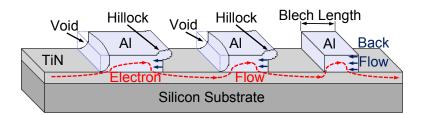

Another important factor of electromigration in interconnects is the buildup of a mechanical stress gradient within the metal line. During electromigration, atoms are depleted from the cathode end and accumulated on the anode end leading to a slight atomic density imbalance that creates a stress gradient along the AI line segment. Blech conducted electromigration experiments on varying lengths of AI lines deposited onto a refractory layer of titanium nitride (TiN). Through passing electrical current in the Blech test structure, electron flow is driven into the much lower resistivity AI film causing AI migration that depends on the current density and the length of the AI line segment. Figure 2.4 depicts the Blech length effect in AI thin film segments.

Figure 2.4 Blech length effect demonstrated on Al thin film segments.

It was found that the electromigration-induced stress gradient creates a backflow diffusion flux in the opposite direction to the electron wind atomic flux. If the stress gradient is allowed to increase without stress relief from electromigration damage in the form of voids and hillocks, it reaches a critical limit at which the backflow diffusion flux equals the electron wind atomic flux preventing electromigration. This stress-induced backflow that halts electromigration is known as the Blech effect.

Combining the stress-induced backflow flux with the electron wind atomic flux, the net atomic flux is expressed as

$$J_{net} = N(v_d - v_b) = N\left(\frac{D}{kT}\right) \left(Z_{eff}^* e \rho J - \Omega \frac{\Delta \sigma}{\Delta x}\right), \tag{2.10}$$

where  $\Omega$  is atomic volume and  $\Delta\sigma$  /  $\Delta x$  is stress gradient along the line. Blech established that a critical threshold value exists for which electromigration is averted and determined that it is related to the product of current density and the metal line length. When the electromigration driving force equals the generated backflow stress, a steady state is reached. It is defined as

$$Z_{\text{eff}}^{\star}e\rho J = \Omega \frac{\Delta \sigma}{\Delta x}.$$

(2.11)

Rearranging this steady state expression to solve for the critical threshold product gives

$$J_c L_{Blech} = \Omega \frac{\Delta \sigma}{Z_{eff}^* e \rho}.$$

(2.12)

It is surmised from this relationship that below the critical threshold product of current density  $J_c$  and line length  $L_{Blech}$ , the atomic mass transport ceases, thereby preventing electromigration damage. Moreover, for a given constant current density  $J_c$  there is a specific line length  $L_{Blech}$  below which electromigration failure will not occur. This specific line length is known as the Blech length and is typically around 50  $\mu$ m. It was also found by Blech<sup>24</sup> that Al lines entirely encased in SiN passivation exhibited decreased atomic mass transport and the critical threshold product increased. This threshold effect has very useful implications for the reliability of ICs because designers can lay out interconnect architectures that have significantly reduced electromigration risk by ensuring that the majority of lines are below the critical Blech length.

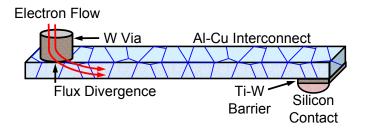

Despite lifetime improvements achieved with use of large grained bamboo microstructures and passivation encasement of interconnects, electromigration damage persists due to other sources of flux divergence. Electromigration-induced damage in interconnects is the result of sustained atomic or vacancy flux divergence. Other sources of flux divergence to be considered are temperature gradients and terminal material interfaces. High current operation of ICs generates Joule heating accompanied by temperature gradients in regions where interconnect line-widths abruptly change, thus posing a risk for electromigration. Additionally, multi-level metallization IC technology commonly uses refractory metal diffusion barriers and tungsten filled vias. Electron current flowing in the tungsten (W) via into the aluminum-copper (Al-Cu) interconnect creates flux divergence at the interface. A three-dimensional view of the W / Al interface where flux divergence occurs is shown in Figure 2.5. Electron flow causes Al atoms to migrate away from the W via bottom that are not backfilled by the immovable W atoms, thus creating flux divergence at the interface. Therefore, voids nucleate and grow at the via / interconnect interface and lead to electromigration failures.<sup>27</sup>

Figure 2.5 Flux divergence at the W via / Al interconnect interface.

# 2.2.2 Alloying and Metallization Advancements

Pure aluminum was originally the primary metallization used for IC interconnects because of its very low resistivity and compatibility with silicon processing. Al thin films can be deposited by evaporation or sputtering methods and exhibit good adhesion to inter-layer dielectric (ILD) films such as SiO<sub>2</sub>. Even though pure AI has several ideal properties for use in IC interconnects, it lacks superior electromigration reliability. Discovery of the beneficial effects of Cu contamination into Al thin films inadvertently occurred while investigating grain boundary mass transport. The addition of 4 wt. % of Cu into Al thin films was found to increase the electromigration lifetimes by a factor of 70 times.<sup>28</sup> It was revealed that failures occurred in Cu depleted areas and that Cu atoms migrate faster than Al atoms. Furthermore, it was suggested that the Cu doped Al films had the same intrinsic grain boundary diffusion mechanism, but the Cu in the grain boundaries retard electromigration. Alloying additions of silver or gold did not show the same increased lifetimes.<sup>29</sup> Also, it is known that the solubility of Cu in Al is only about 0.05 wt. % and that Al<sub>2</sub>Cu precipitates are observed to be distributed along grain boundaries. Electromigration lifetime enhancement due to alloying AI with Cu is postulated as a consecutive two step process. The first step consists of the preferential and sacrificial diffusion of Cu atoms occurring along grain boundaries until localized depletion is reached. Next, void formation commences in these Cu free regions of the Al conductor leading to open line failures. Although the activation energy was thought to be similar<sup>30</sup> to pure Al films, it was shown to be 0.2 - 0.3 eV higher<sup>31</sup> for the two-step kinetic failure process of Al(Cu) films. A comprehensive review of electromigration in Al and Al(Cu) interconnects is furnished by C. K. Hu and others.<sup>32</sup>

Additions into Al films of other alloying elements, such as magnesium and chromium, were proven to reduce the rate of electromigration.<sup>33</sup> While additions of magnesium showed substantially better lifetimes compared to Al(Cu) films, the resistivity of Al alloyed with 6 wt. % of Mg increased nearly twofold over pure Al making it less preferable as an electrical conductor. Furthermore, Al alloys containing magnesium are challenged with thermal process limitations because magnesium reacts with SiO<sub>2</sub> at high temperature.<sup>34</sup>

An alternative scheme for improving resistance against electromigration was the implementation of refractory metals for Al(Cu) interconnects. The refractory metal layer is typically deposited underneath the Al(Cu) film as a barrier layer, but also can be on top as a capping layer. One of the most common refractory metal layers used as a barrier layer for Al(Cu) metallization is titanium tungsten (TiW) with a stoichiometry of 10% Ti and 90% W. A TiW / Al(Cu) metallization stack shows median electromigration lifetimes two to ten times longer than Al(Cu) films alone. 35, 36 The TiW layer also acts as a diffusion barrier against junction spiking by being interposed between the Al film and the silicon contact.<sup>37</sup> Another barrier layer observed to enhance electromigration performance is titanium nitride (TiN), which by annealing can increase lifetimes by a factor of 2. Additional electromigration performance improvements were shown with the use of TiN anti-reflection coatings (ARC) deposited on top of the Al(Cu) alloy as a capping layer.<sup>38</sup> Specific refractory metals and silicides including Ti, W, WSi2, and MoSi2 as capping layers for Al metallization were shown to improve reliability for electromigration.<sup>39</sup> With the selection of metallizations for ICs, it is paramount that superior electrical conductivity and electromigration reliability properties are optimized.

As the trend in IC miniaturization decreased to the low submicron range for ultra large-scale integration (ULSI) devices, a new interconnection metal was sought that would possess higher reliability against electromigration damage. While Al(Cu) metallization served well for decades as an interconnect metal, its continual use in ULSI devices reached performance limitations. These limitations<sup>40</sup> are enumerated by additional interconnect levels necessary for ULSI devices, resistance-capacitance (RC) delays in signal transmission, and insufficient electromigration reliability in Al(Cu) lines with reduced dimensions possessing higher current densities. In addressing these limitations, copper metallization was proposed as a replacement for Al(Cu) in the early 1990's.<sup>41-47</sup>

Given that Cu has a much higher melting point (1083°C vs. 660°C) than AI, its atomic diffusion and thus its electromigration mass transport is expected to be slower at the same device operating temperature. Moreover, the resistivity of Cu compared to AI(Cu) (1.7  $\mu\Omega$ ·cm vs. 3.2  $\mu\Omega$ ·cm) is significantly lower providing faster signal propagation and shorter switching times, which in turn reduces the RC delay. With these ideal properties, Cu metallization was considered an attractive choice for IC interconnections. However, implementation of Cu as an interconnect material for silicon ICs has been fraught with challenges. These Cu challenges include higher susceptibility to corrosion, rapid diffusion in silicon causing contamination (poisoning) of device regions, difficulty of dry etching, and poor adhesion to silicon oxide dielectric films.<sup>48</sup> A lack of a suitable reactive ion etching (RIE) process for Cu prevented employment of the conventional subtractive etch process used for AI(Cu) interconnects. Thus, an entirely new integration scheme was required and developed for the transition to Cu metallization.

The Cu metallization integration scheme is considered an additive patterning or in-laid process known as the Damascene process. In this process the interconnect trench contour is first patterned into the underlying silicon oxide prior to Cu deposition. A thin layer of barrier metal such as tantalum (Ta) or tantalum nitride (TaN) is then deposited in the trench to surround and prevent Cu diffusion in the silicon device, which would cause deep-level traps. The trenches are overfilled with a thick Cu layer deposited by electrochemical deposition. A thin conductive seed layer is required so that Cu can be electroplated on its surface. Finally, chemical mechanical polishing (CMP) removes the excess Cu and planarizes the Cu metallization with the top of the silicon oxide layer. Further advancement is leveraged with the dual-damascene integration, which combines filling via holes and line trenches into one step, thus reducing the overall processing steps for a multi-level metallization IC.

High performance submicron complementary metal-oxide-semiconductor (CMOS) technology with six levels of planarized Cu interconnects was developed and first announced by Motorola<sup>49</sup> and IBM<sup>50</sup> in 1997. Characterization results of this multi-level Cu interconnect technology showed a significantly lower resistance (45% reduction) potentially translating into a 30% lower RC delay compared to equivalently scaled Al(Cu) technology. Furthermore, dual-damascene Cu metallization has demonstrated superior electromigration reliability allowing higher current density operation. Through direct experimental comparison, electromigration median lifetimes of Cu interconnects are about 100 times longer than that of Al(Cu) metallization.<sup>51</sup> More detailed reviews on Cu metallization reliability are given by Rosenberg,<sup>52</sup> Ogawa,<sup>53</sup> and Tu<sup>40</sup>.

### 2.2.3 Reliability Measurement Methods

Assurance that the electromigration reliability of interconnects at normal operating conditions exceeds the desired IC lifetime of 10 years requires accelerated testing. Accelerated testing involves the application of stresses of temperature and current density significantly above normal operation to expedite the electromigration failure mechanism and shorten tests to a practical timeframe. Stress temperatures from 200°C to 350°C and current densities in the range from 1 to 3 mega amps (MA) / cm² are typical for conventional electromigration tests. Electromigration lifetimes under accelerated stress conditions are measured to extract model parameters and to predict normal operating failure lifetimes. To accurately predict operational lifetimes by extrapolation requires that the same failure mechanism operates under both accelerated and normal stress conditions.

Measurement of electromigration-induced failures of interconnects has been approached by an array of different test methods. Conventional package-level tests and highly accelerated wafer-level tests distinguish the two main approaches for electromigration testing. Since conventional package-level tests are time consuming and require expensive ceramic packages, there has been a concerted attempt starting in the early 1980's to use highly accelerated wafer-level tests. The most notable fast electromigration wafer-level test methods include the standardized wafer-level electromigration accelerated test (SWEAT), breakdown energy of metal (BEM), and the wafer-level isothermal Joule-heated electromigration test (WIJET). Unfortunately, these fast wafer-level tests are plagued by substantial overstressing errors causing inaccurate lifetime predictions. These quick tests show merit for reliability monitoring of interconnect processing defectivity, but not for electromigration lifetime prediction. 54

Conventional package-level electromigration tests with application of a moderate stress acceleration level remain the best approach for accurately extracting model parameters and extrapolating interconnect lifetimes at normal operating conditions. There are three experimental measurement techniques of conventional package-level tests which have had widespread use for electromigration studies of interconnects.<sup>55</sup> The earliest of these three techniques is the median time to failure ( $t_{50\%}$ ) lifetime test. This technique is carried out by stressing several interconnect test structures at known current density and temperature until an electromigration-induced void traverses the entire line-width and ceases current flow, which then gets recorded as the interconnect failure time. All combined failure times yield a statistical spread with the median time to failure defined as the time at which 50% of the interconnect test structures have failed. A major drawback of this technique is that a constant temperature is not maintained because localized Joule heating occurs as the void size grows leading to thermal runaway and catastrophic failures.

Microscopic observation of void formation or edge displacement in metal lines as direct drift velocity measurement techniques have also been utilized for electromigration studies. <sup>56, 57</sup> The void formation technique requires a hole to be etched through the silicon die in order for transmission electron microscopy (TEM) images to be taken of the thin metal film during the test. These TEM images reveal the rate of void formation that determines the electromigration drift velocity. The edge displacement technique measures and relates the velocity of the metal film edge as it migrates to the average drift velocity for electromigration. A disadvantage of these techniques is the laborious test structure preparation and monitoring which prohibits a statistically relevant sample size for tests.

Another key limitation inherent with these techniques is the inability to evaluate interconnect structures with passivation film coatings. Actual IC interconnects are embedded within inter-layer dielectric (ILD) layers with a final passivation overcoat causing enhanced electromigration properties compared to the bare metal films necessary for these direct techniques. Lastly, enormous temperature gradients are generated in the suspended thin metal film samples.

The resistometric method for electromigration experiments has become the most popular technique currently practiced due to its ease of application and lack of major drawbacks. Introduction of the resistance monitoring technique was pioneered early on by Rosenberg<sup>13</sup> at IBM to examine the structural damage of interconnects during accelerated electromigration tests. This technique correlates the change in resistance to structural change caused by accumulation of electromigration-induced voids. The rate of resistance change ( $\Delta R/\Delta t R_o$ ) is considered to be proportional to the atomic drift velocity ( $v_d$ ) as follows

$$\frac{\Delta R}{\Delta t} \left( \frac{1}{R_o} \right) = A \exp \left( -\frac{E_a}{kT} \right) = \frac{v_d}{I_V}, \qquad (2.13)$$

where A is a pre-exponential factor and  $I_{v}$  is the metal segment length. Given this implicit relationship, activation energies between 0.5 to 0.7 eV for AI thin films were obtained by the resistometric technique, which are consistent with lifetime measurements.<sup>58</sup> This method is capable of measuring minute resistance change (< 1%) to detect tiny voids not directly observable by microscopic techniques, especially in the case of passivated interconnects. A further advantage is the ability to measure a large number of interconnects inside a constant temperature oven, thus avoiding the Joule heating inherent with other tests. Also, significant test time reduction can be achieved with this method.

### 2.2.4 Failure Kinetic Models

Accurate prediction of electromigration-induced failures in interconnects under normal operating conditions is of utmost importance for IC manufacturers. Therefore, development of a predictive model that represents the functional relationship between thin film failure kinetics and applied stresses driving the electromigration mechanism has been the central focus of many studies. Early attempts to reconcile theoretical models with experimental electromigration data were insufficient. Upon examination of Equation (2.6), it is ascertained that the electromigration failure time resulting from the drift velocity is proportional to the current density stress. However, actual empirical electromigration data for Al thin films showed an inverse square dependence on current density. theoretical models were not inclusive of several factors such as mechanical stress, chemical composition, and microstructural inhomogeneities which offers explanation for this discrepancy. With the discovery of the electromigrationinduced stress gradient as an important contributing factor that opposes the electron wind atomic flux, an advanced understanding of the electromigration mechanism emerged. A more comprehensive model is given in Equation (2.10) with addition of this stress-induced backflow flux that exists with blocking boundaries. Through inclusion of this opposing stress-induced backflow component, general resolution is attained for the earlier disparity between the theoretical model and the empirical results.<sup>59</sup>

Shortly after the electromigration reliability crisis emerged in the electronics industry, Jim Black at Motorola was methodically investigating electromigration failure kinetics. Black's pioneering research developed the first empirical model that predicts the electromigration lifetimes of interconnects under

steady state direct current. Black's empirical model established that electromigration mass transport failure kinetics are dependent on an Arrhenius relationship and are inversely proportional to the square of current density. This relationship has become known as Black's equation<sup>60</sup> which is given by

$$t_{50\%} = \frac{A}{J^n} \exp\left(\frac{E_a}{kT}\right), \tag{2.14}$$

where  $t_{50\%}$  is median time to failure of the tested interconnect population, A is a proportionality constant dependent on the metal, J is the current density,  $E_a$  is the activation energy, T is the absolute temperature, k is Boltzmann's constant, and n is the current density exponent equal to 2 according to Black. Black's equation is the most extensively utilized model for interconnect reliability evaluations 61 and has proven to be very instrumental for extrapolating the median time to failure of a group of identical interconnects under electromigration stress conditions to normal operating conditions. According to Black's study, the constant A is composed of factors that involve the cross-sectional area of the thin metal and characteristic material properties. Activation energies  $E_a$  were shown to depend upon the microstructure of the thin metal film with higher values for large grained Al films because of a reduction in grain boundaries contained within the line limiting low energy diffusion pathways. For a range of experimental current densities, Black determined a  $1/J^2$  relationship, although theoretical formulation for the electromigration driving force has a linear dependence on current density. Black's empirical<sup>14</sup> work was influential in establishing that electromigration failures exhibit an Arrhenius relationship with an inverse square current density dependence and that the failure time data closely follows a log-normal distribution.

More recent electromigration studies on a modern Al alloy metallization  $^{62}$  scheme incorporating refractory barriers extracted values for the current density exponent between 1 and 2, while for an advanced Cu metallization  $^{63}$  a current density exponent closer to n=1 was observed. Higher values (n>2) of the current density exponent are attributed to improper treatment of Joule heating effects. Since many electromigration results did not strictly follow a  $1/J^2$  relationship, Black's equation (Equation 2.14) took on a generalized formulation to allow for a variable current density exponent. Nearly two decades later, a few theoretical studies have promoted clarification for Black's inverse square dependence on current density and the lack thereof for other metallizations which considerably advanced the understanding of electromigration mechanisms.

A model developed by Shatzkes and Lloyd<sup>64</sup> considers concomitantly the opposing electromigration-induced mass transport and Fickian diffusion due to a concentration gradient. It is based on the condition of a semi-infinite metal line with perfectly blocking boundaries at one end such as in the real situation of a "bamboo" grain boundary. As the vacancy concentration at the blocking boundary reaches a critical concentration, a void can be nucleated. This model expresses the electromigration time to failure ( $t_f$ ) as

$$t_f = B \frac{T^2}{J^2} \exp\left(\frac{E_a}{kT}\right), \tag{2.15}$$

where B is a constant and  $E_a$  is the activation energy for grain boundary diffusion. It is notable this model yields a failure time that accounts for an inverse square dependence on current density and is similar to Black's model with the exception of the  $T^2$  term. Yet this model assumes failures are dominated by the void nucleation stage which is an incomplete portrayal of the entire failure process.

Simple pure Al films without refractory barrier layers as studied by Black are considered to have a significant portion of the electromigration failure time as void nucleation which soon afterward grows to an open circuit.<sup>59</sup> The void nucleation process is strongly influenced by electromigration-induced stresses that build up in the film. Electromigration failure times under a void nucleation dominant process exhibit a current density exponent dependence close to n = 2 that confirms Black's observation. Advanced metallizations that incorporate W vias with refractory barrier layers allow current passage to be sustained after the metal is entirely voided. As a result, the void growth process is a larger portion of the electromigration failure time. The void growth process is governed by ion drift velocity factors which translates into a linear n = 1 current density exponent dependence. Electromigration failure times are not exclusively nucleation or void growth controlled but considered to be a combination<sup>65</sup> of the two processes supporting fractional current density exponents (1 < n < 2).

A modification to Black's equation to delineate the electromigration failure time for the void nucleation and growth kinetics was proposed. This model recognizes two distinct kinetic processes involved in electromigration failures which are no longer a single function of the failure time but instead are the sum of two functions. In this model electromigration median time to failure ( $t_{50\%}$ ) is the sum of these two independent time components as follows

$$t_{50\%} = t_{nuc} + t_g = \left(\frac{AkT}{J} + \frac{B(T)}{J^2}\right) \exp\left(\frac{E_a}{kT}\right),$$

(2.16)

where  $t_{nuc}$  is time required for void nucleation and  $t_g$  is the time duration for growth of a void to become an open circuit. Constants A and B have geometric factors pertaining to the void size required to reach a line failure. As follows from

this extension to Black's model, the proportion of nucleation and growth is variable depending on the current density. For higher current densities, the growth kinetics proportionately account for more of the time to failure than at lower current densities. It is found that extrapolations to normal operating conditions using this nucleation and growth model under certain cases have roughly similar lifetime prediction to Black's equation. Nonetheless, Black's empirical model parameters ( $E_a$  and n) extracted at accelerated test conditions neglect pre-existing thermally induced stresses which are substantially lower under test conditions compared to normal operation conditions. This leads to an increased void nucleation (incubation) time that can produce a significant lifetime prediction inaccuracy. In spite of this error, the nucleation and growth model<sup>69</sup> generally predicts longer lifetimes, so the shorter lifetimes predicted by Black's power law equation are more conservative and therefore ensure a larger reliability margin from an engineering perspective.

Electromigration failure kinetics display a statistical nature influenced by metallization microstructure, barrier interfaces, and to a lesser extent defectivity. Analysis of electromigration failures has consistently been described by lognormal statistics because the data fit this distribution quite well. Applying lognormal analysis yields two important parameters, the median time to failure ( $t_{50\%}$ ) and the log-normal standard deviation or shape parameter ( $\sigma$ ) that characterizes the electromigration failure distribution. Using Black's model and log-normal statistics, the time to failure for an acceptable failure percentage (e.g., 0.01%) under normal operating conditions can be calculated. More details on the lognormal distribution and electromigration data analysis are covered in Chapter 3.

# 2.3 Properties and Application of Gold Metallization

## 2.3.1 Properties of Gold

Gold exists naturally in its elemental metallic state as nuggets or in veins of quartz deposits and displays a unique bright reddish yellow color. The chemical symbol for gold is Au derived from its Latin name *aurum*, which means "shining dawn". Gold has an atomic number of 79 (atomic nucleus has 79 protons) and an atomic mass of 196.97 grams / mol. Table 2.1 lists the atomic properties and lattice structure of gold.<sup>70</sup>

Table 2.1 Atomic properties and crystal lattice of gold.

| Gold Atomic               | Properties                                                          | Gold Crystal Lattice |

|---------------------------|---------------------------------------------------------------------|----------------------|

| Atomic Number:            | 79                                                                  | Face Centered Cubic  |

| Atomic Radius:            | 1.44 Å                                                              |                      |

| Atomic Volume:            | 10.2 cm <sup>3</sup> / mol                                          |                      |

| Atomic Mass:              | 196.97 gram / mol                                                   |                      |

| Electron Configuration:   | [Xe] 4f <sup>14</sup> 5d <sup>10</sup> 6s <sup>1</sup>              |                      |

| Oxidation (Common) State: | -1, +1, +2, (+3), +4, +5                                            |                      |

| Electronegativity:        | 2.54                                                                |                      |

| Ionization Energies:      | 1 <sup>st</sup> : 890.1 kJ / mol<br>2 <sup>nd</sup> : 1980 kJ / mol |                      |

Gold is a transition metal (d-block) in group 11 and period 6 of the periodic table with a face centered cubic (FCC) crystal lattice. Gold has the highest malleability and ductility of all metals making it suitable for wire bonding in microelectronics. One ounce of gold can be hammered into a thin sheet measuring 300 square feet.<sup>70</sup> This incredible malleability is due to the FCC crystal lattice of gold which is very apt for dislocation movement since it contains 12 possible slip systems that can operate during plastic deformation.<sup>71</sup> The color

of metals is derived from the dependence of its reflectivity upon the wavelength (energy) of incident light. For gold the reflectivity conditions for an intense absorption of light at the energy of 2.3 eV produces its characteristic bright reddish yellow color, fulfilled by electron transitions from the d-band to unoccupied positions in the conduction band.<sup>72</sup> Gold exists primarily in the univalent (+1) and trivalent (+3) oxidation states with the +3 oxidation state being the most common.

Table 2.2 Physical properties of gold compared to other conductor metals.

| Properties                                                | Gold    | Aluminum | Copper  | Silver  |

|-----------------------------------------------------------|---------|----------|---------|---------|

| Melting Point (°C)                                        | 1064    | 660      | 1085    | 961     |

| Boiling Point (°C)                                        | 2800    | 2519     | 2562    | 2210    |

| Density (g / cm <sup>3</sup> )                            | 19.30   | 2.7      | 8.96    | 10.5    |

| Electrical Resistivity (10 <sup>-8</sup> Ω·m)             | 2.21    | 2.65     | 1.67    | 1.59    |

| Thermal Conductivity (W / m·K)                            | 318     | 237      | 401     | 429     |

| Thermal Expansion Coefficient (µm·/ m·K)                  | 14.2    | 23.1     | 16.5    | 18.9    |

| Temperature Coefficient of Resistance (°C <sup>-1</sup> ) | 0.00372 | 0.00431  | 0.00404 | 0.00382 |

| Vicker Hardness (MPa)                                     | 216     | 167      | 369     | 251     |

| Modulus of Elasticity (GPa)                               | 78      | 70       | 119     | 83      |

| Heat of Fusion (kJ / mol)                                 | 12.55   | 10.71    | 13.26   | 11.28   |

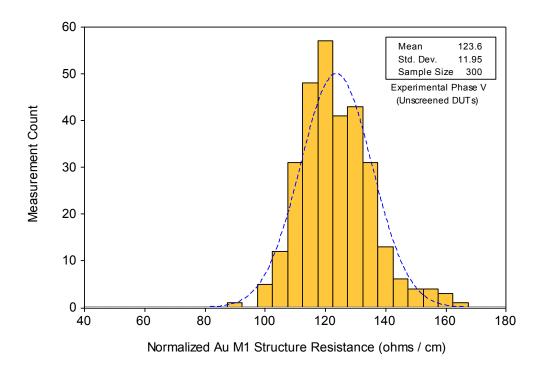

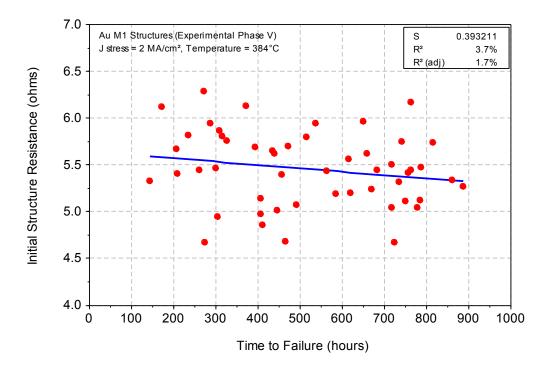

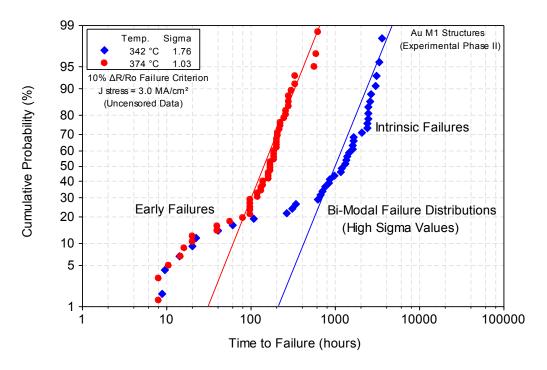

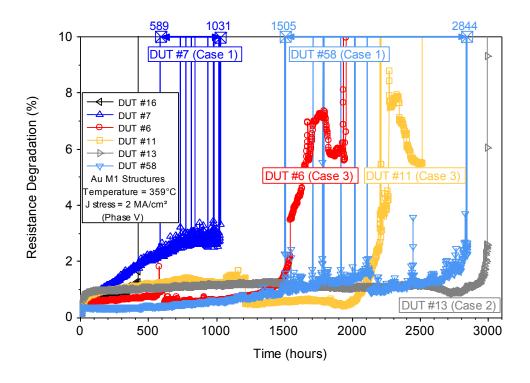

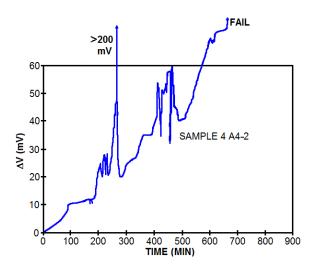

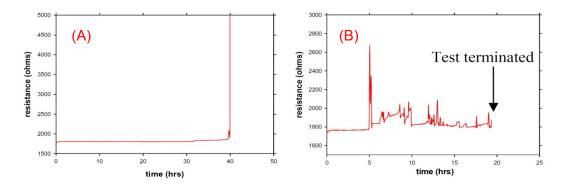

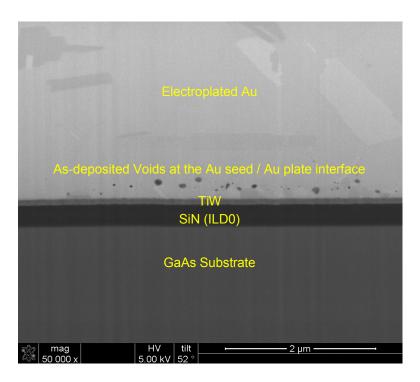

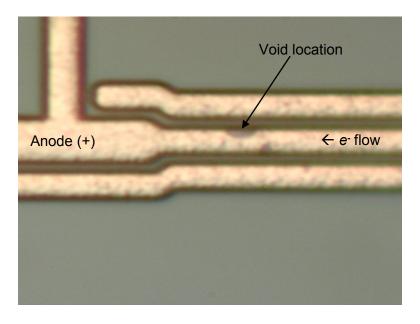

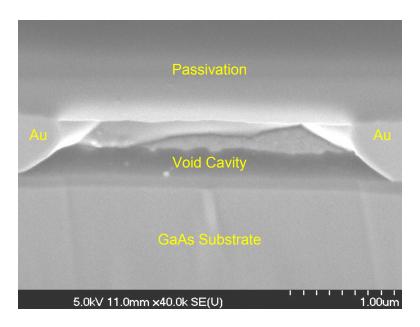

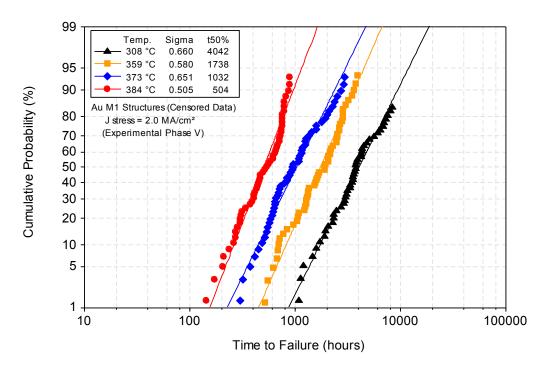

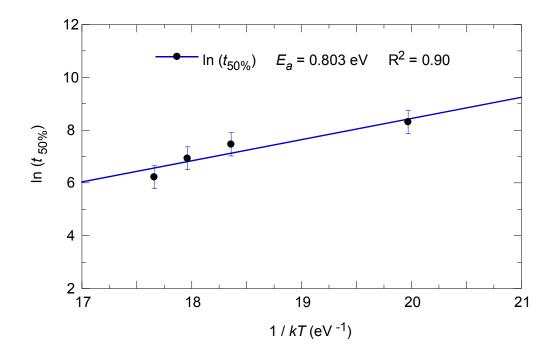

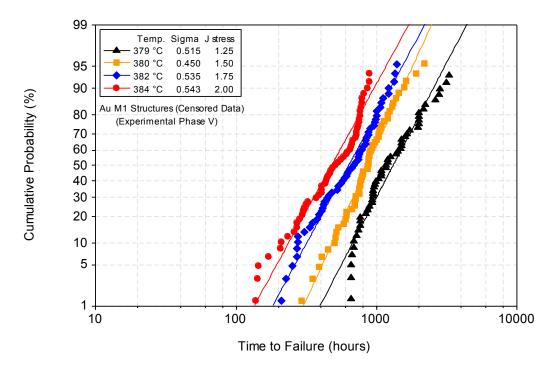

| Molar Heat Capacity (J / mol·K)                           | 25.42   | 24.20    | 24.44   | 25.35   |